ПЕРЕКРЕСТНАЯ ССЫЛКА НА СВЯЗАННЫЕ ЗАЯВКИ

Настоящая заявка испрашивает приоритет предварительной заявки США № 62/131,091, поданной 10 марта 2015, полное содержание которой включено в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к устройству памяти и способу управления им.

УРОВЕНЬ ТЕХНИКИ

В последние годы, стимулировалось развитие устройств памяти, использующих изменения значений сопротивления элементов (памяти с изменяемым сопротивлением), таких как магнитная память (MRAM), память с изменяемым сопротивлением (ReRAM) и память с изменяемым фазовым состоянием (PCRAM).

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

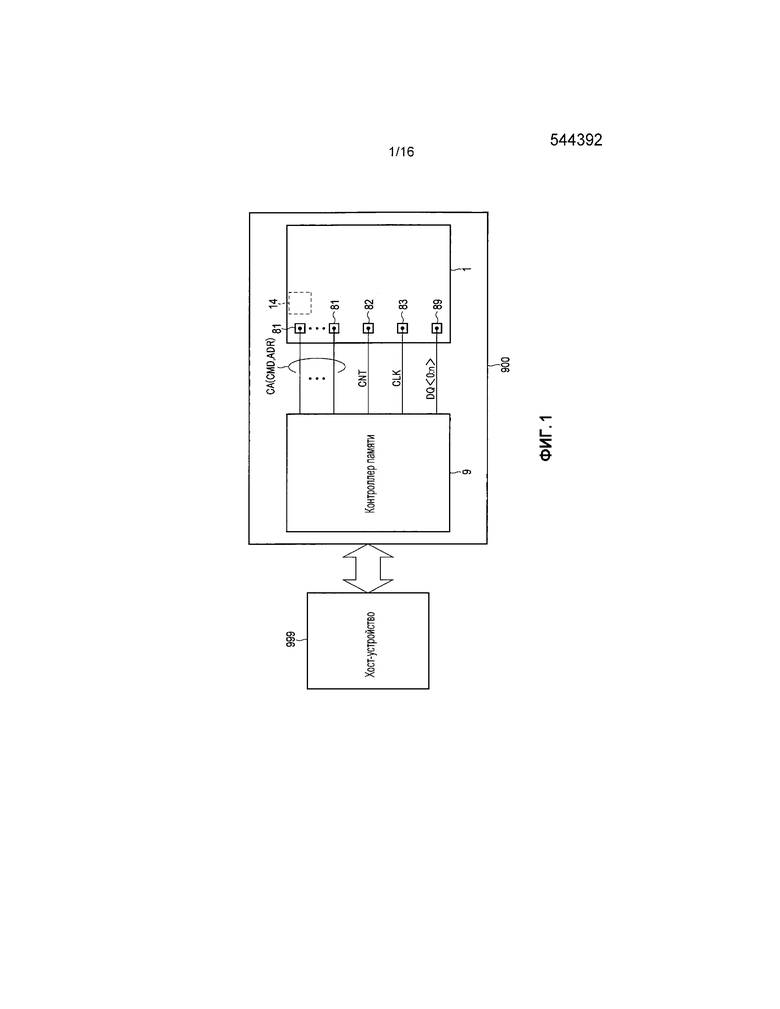

Фиг. 1 - схематичная диаграмма, изображающая общую конфигурацию системы, включающей в себя устройство памяти в вариантах осуществления;

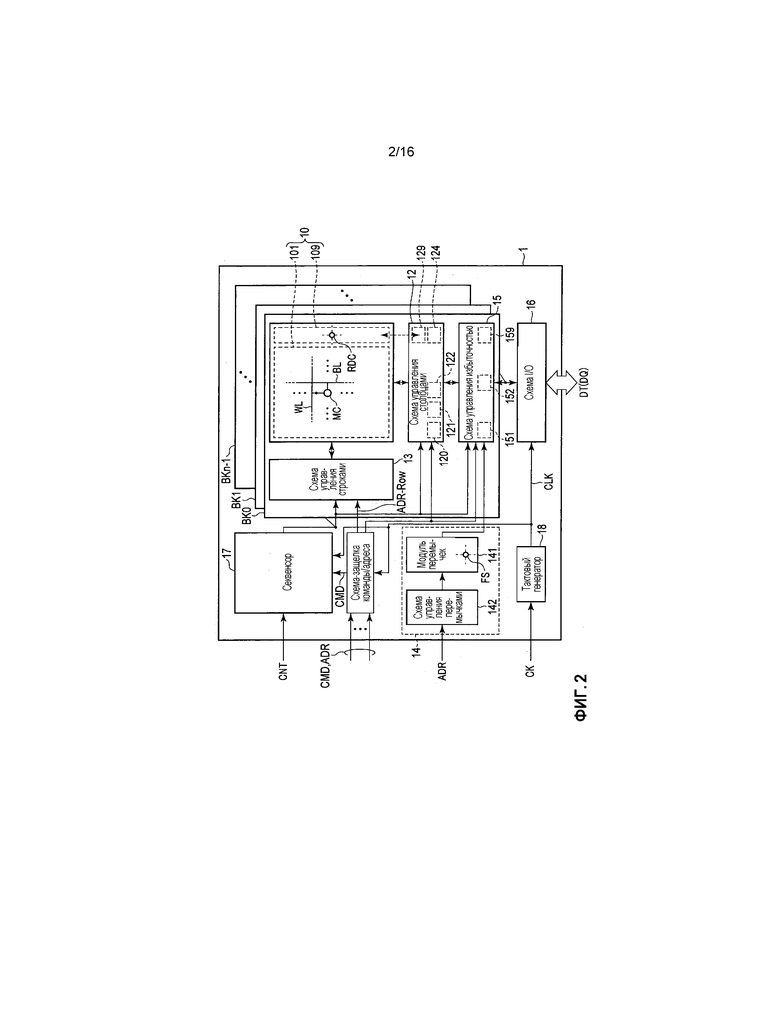

Фиг. 2 - схема, изображающая пример внутренней конфигурации устройства памяти в первом варианте осуществления;

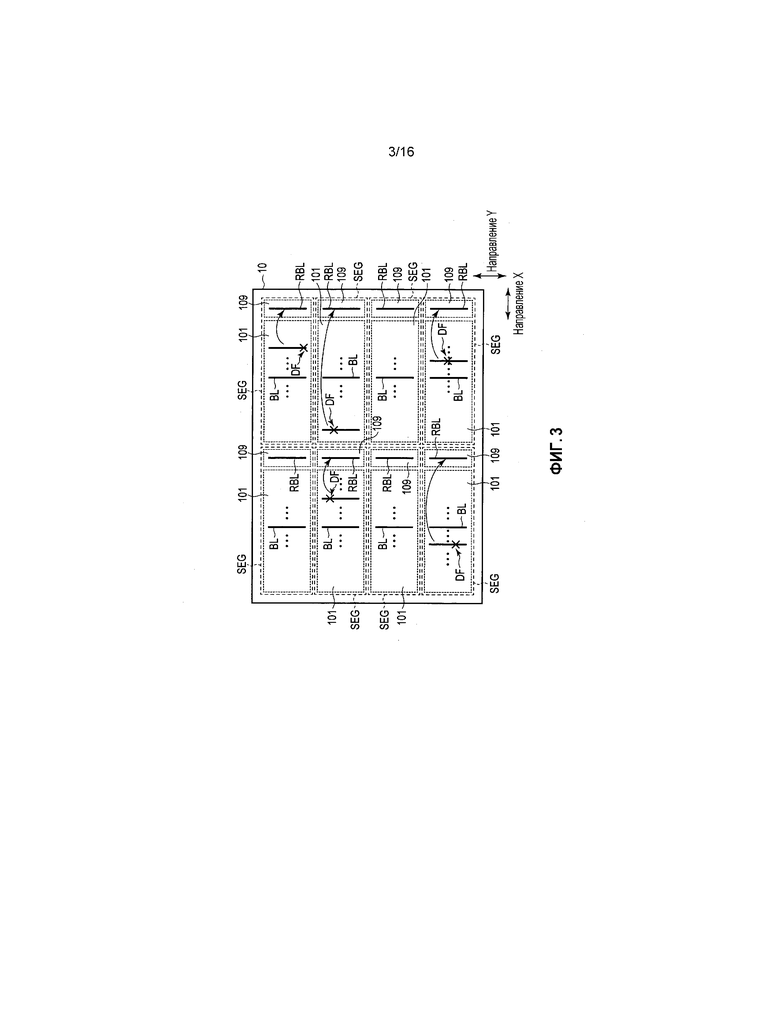

Фиг. 3 - схематичное представление, изображающее пример конфигурации массива ячеек памяти в устройстве памяти в первом варианте осуществления;

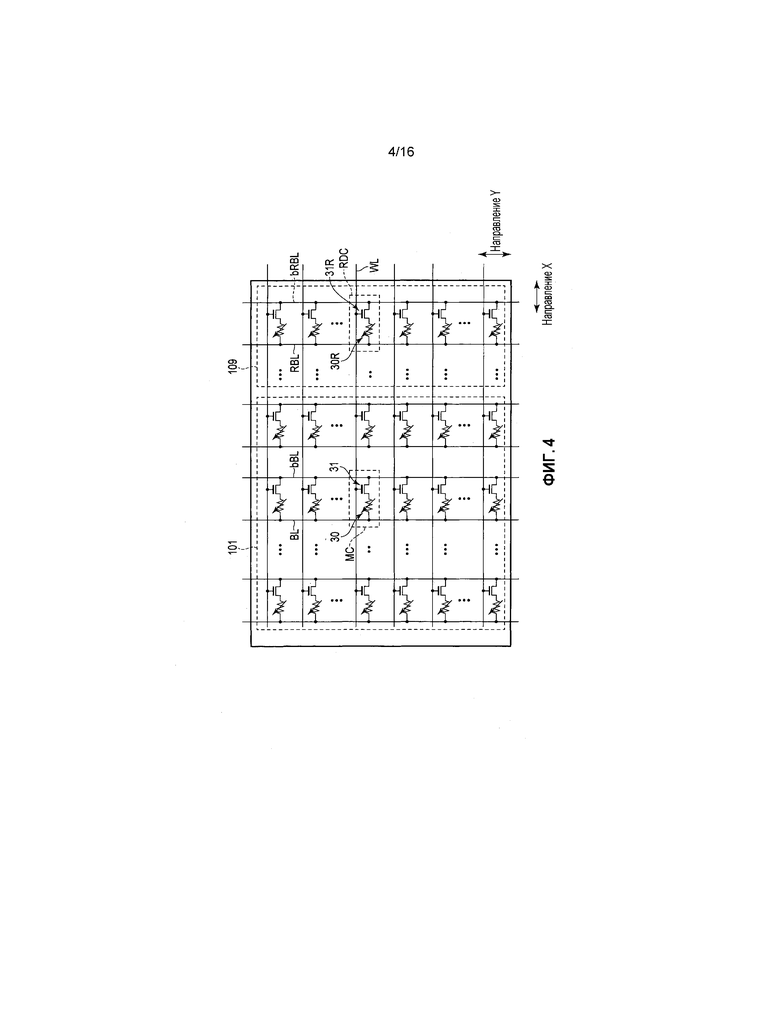

Фиг. 4 - схема, изображающая пример конфигурации массива ячеек памяти в устройстве памяти в первом варианте осуществления;

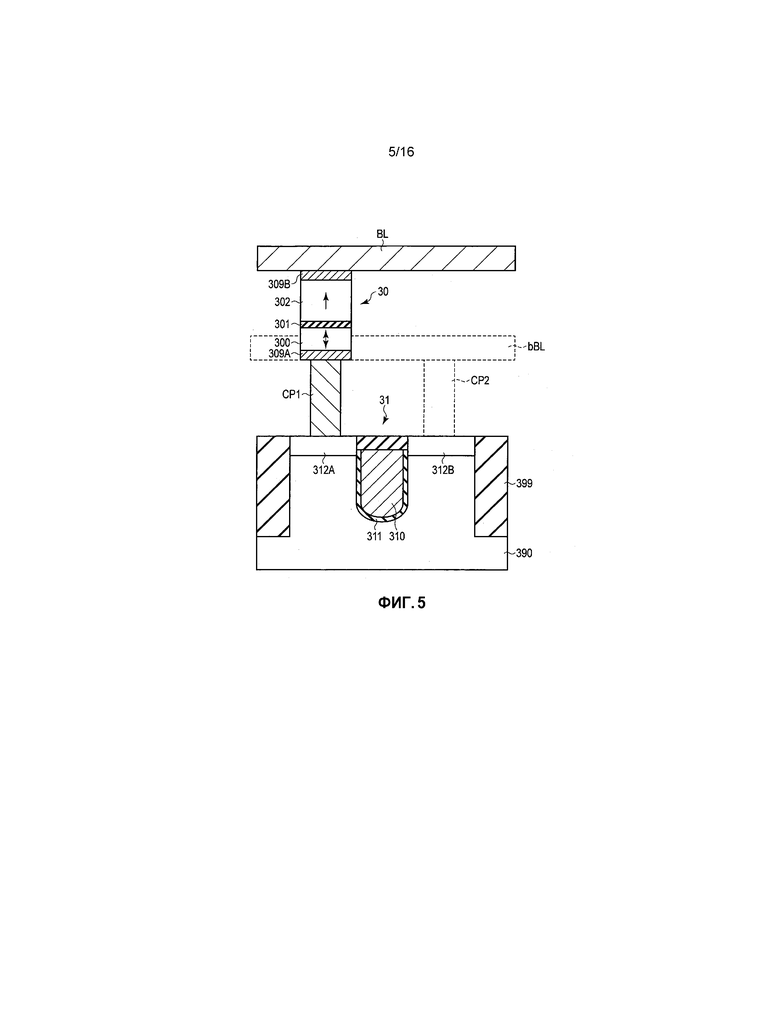

Фиг. 5 - схематичное представление, изображающее пример структуры ячейки памяти в устройстве памяти в первом варианте осуществления;

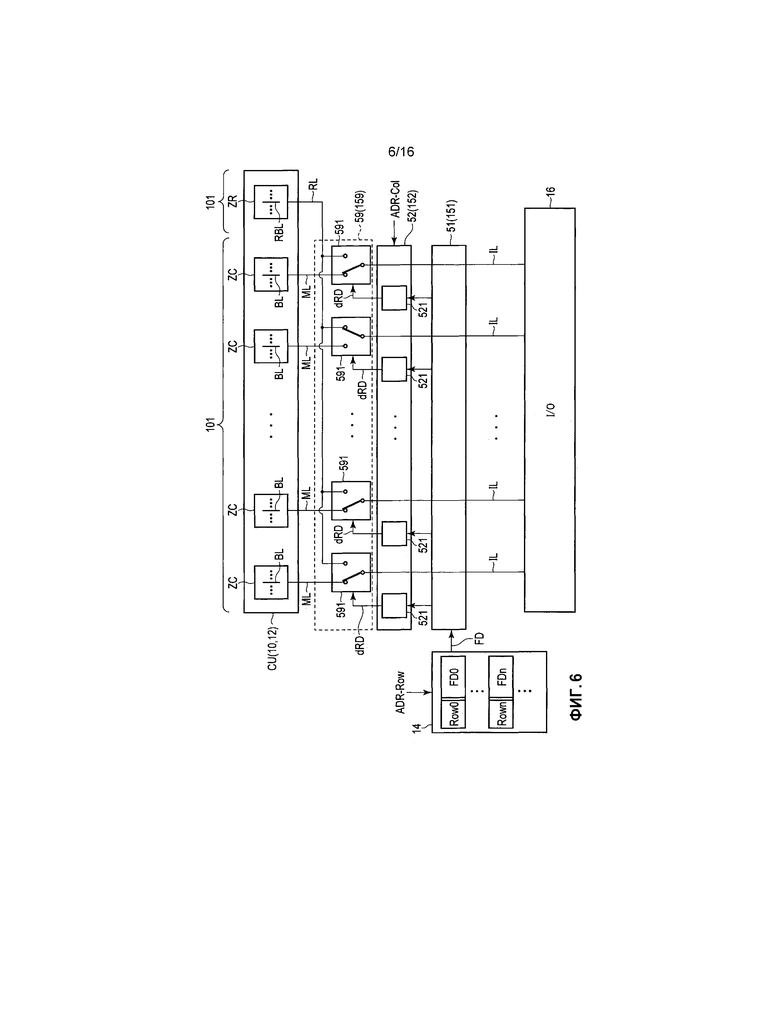

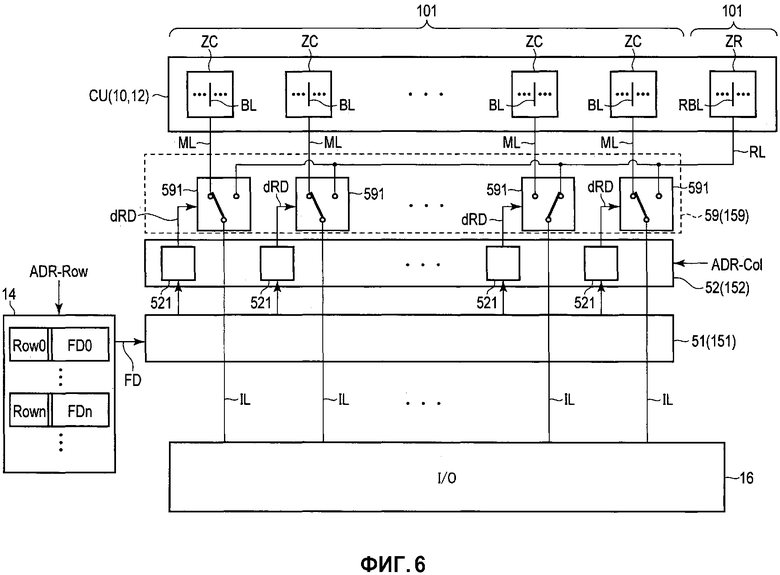

Фиг. 6 - схема, изображающая пример внутренней конфигурации устройства памяти в первом варианте осуществления;

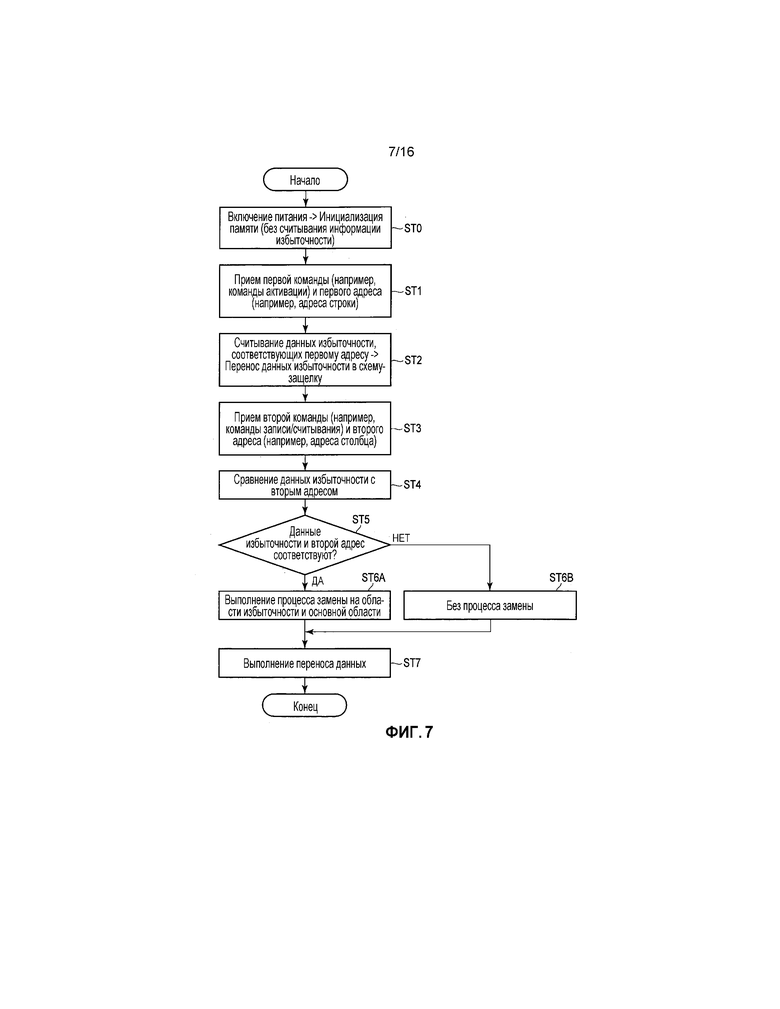

Фиг. 7 - блок-схема последовательности операций, иллюстрирующая пример работы устройства памяти в первом варианте осуществления;

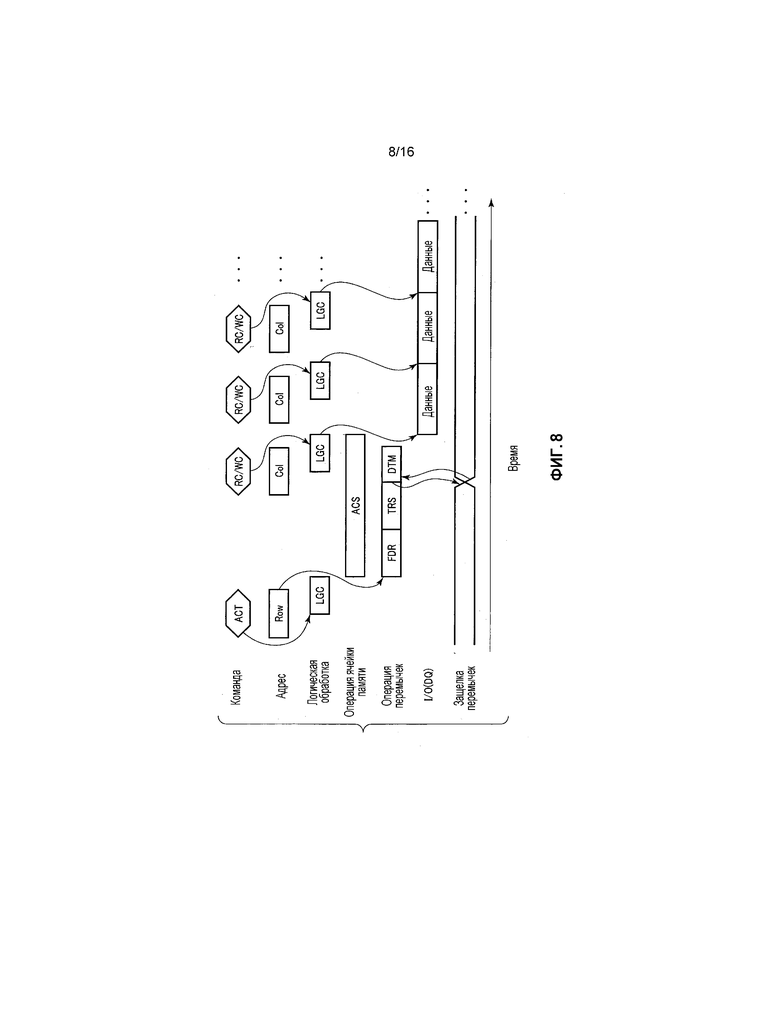

Фиг. 8 - временная диаграмма, иллюстрирующая пример работы устройства памяти в первом варианте осуществления;

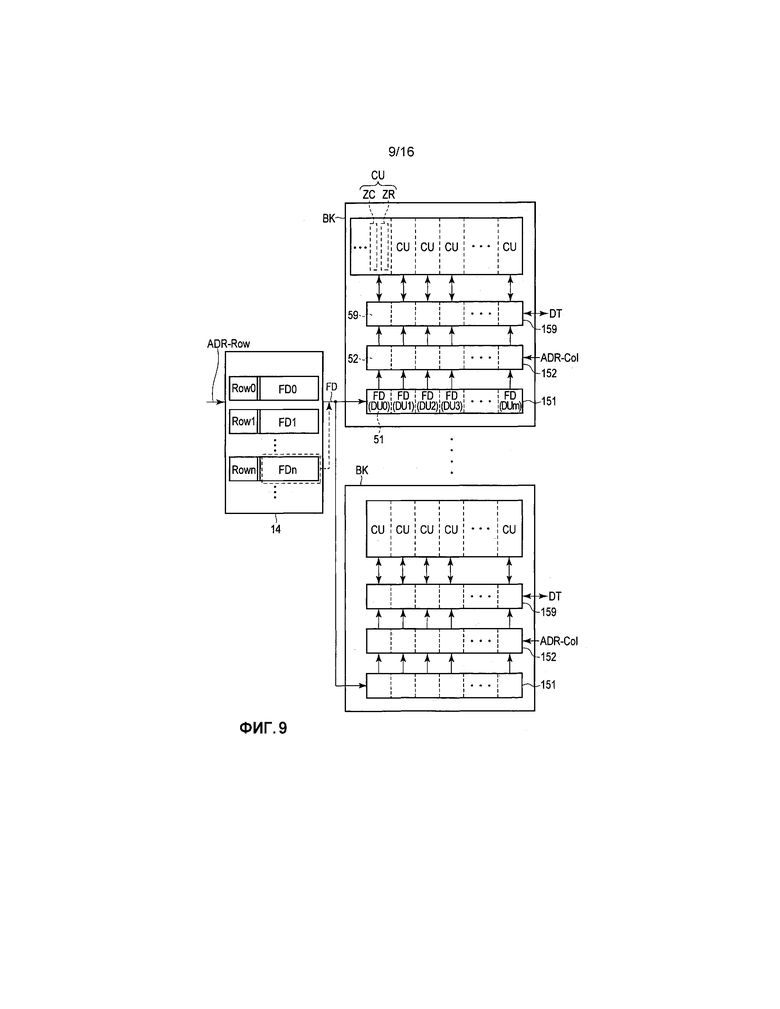

Фиг. 9 - схематичное представление, иллюстрирующее пример работы устройства памяти в первом варианте осуществления;

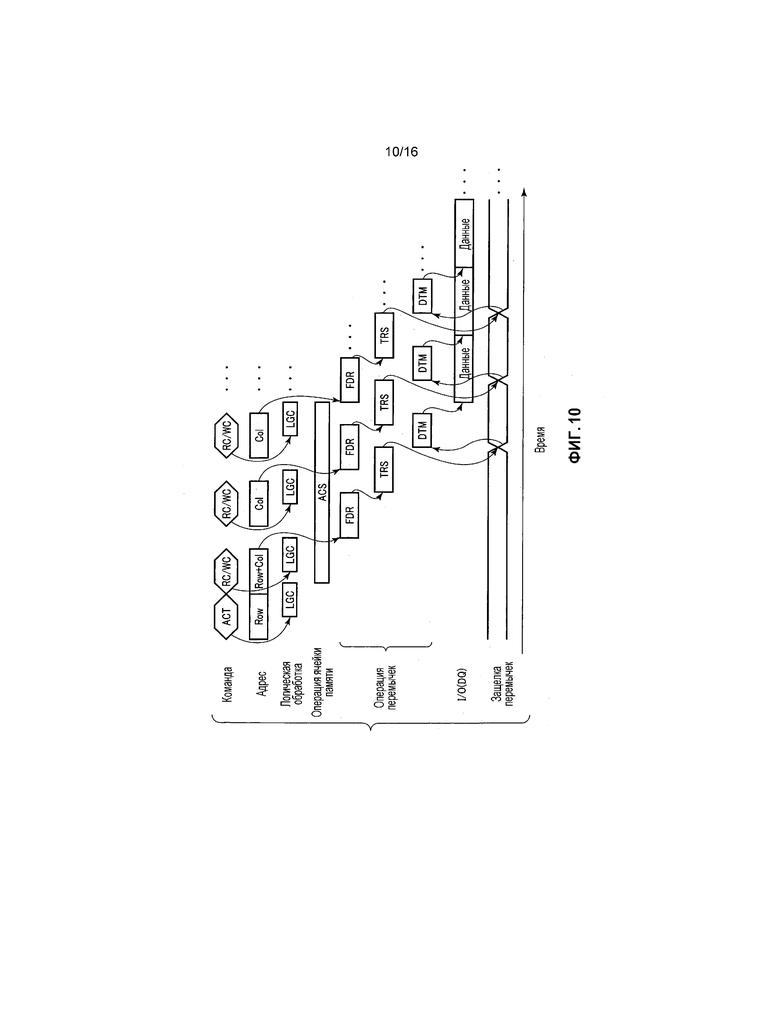

Фиг. 10 - временная диаграмма, иллюстрирующая пример работы устройства памяти во втором варианте осуществления;

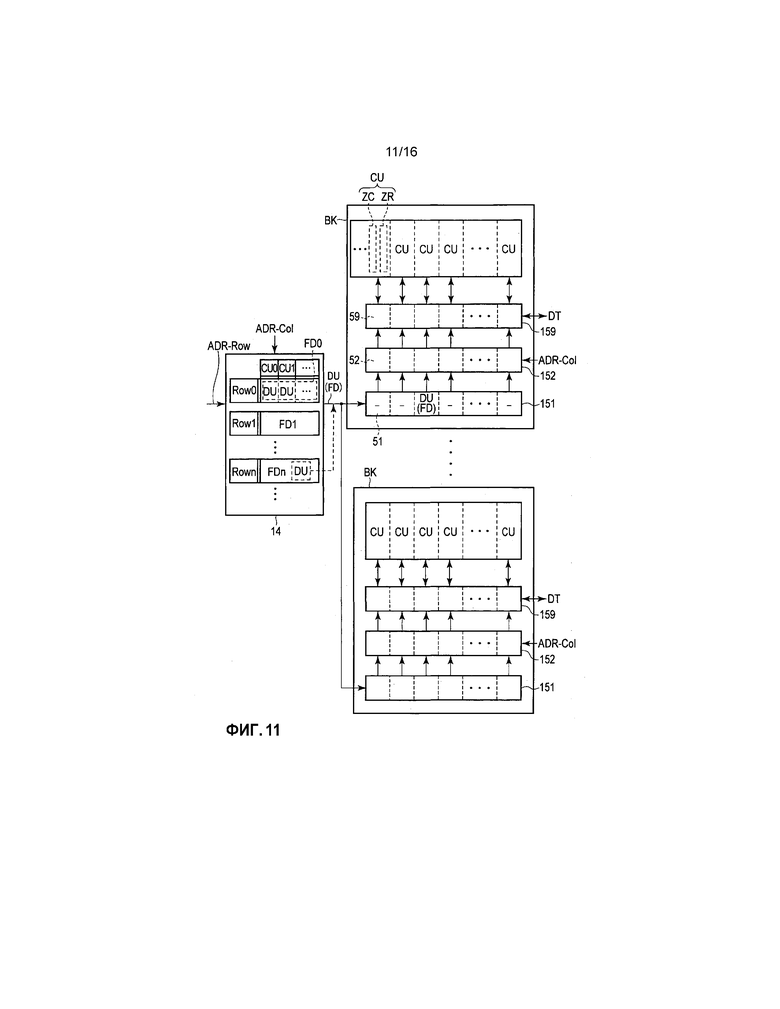

Фиг. 11 - схематичное представление, иллюстрирующее пример работы устройства памяти во втором варианте осуществления;

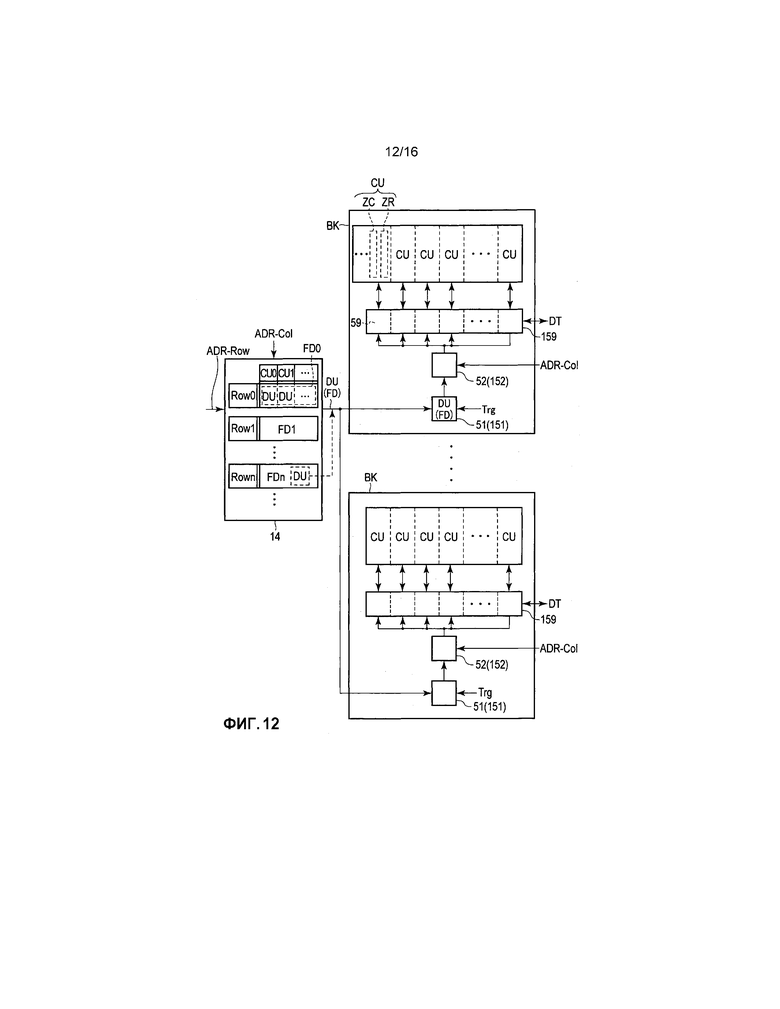

Фиг. 12 - схематичное представление, иллюстрирующее пример работы устройства памяти в третьем варианте осуществления;

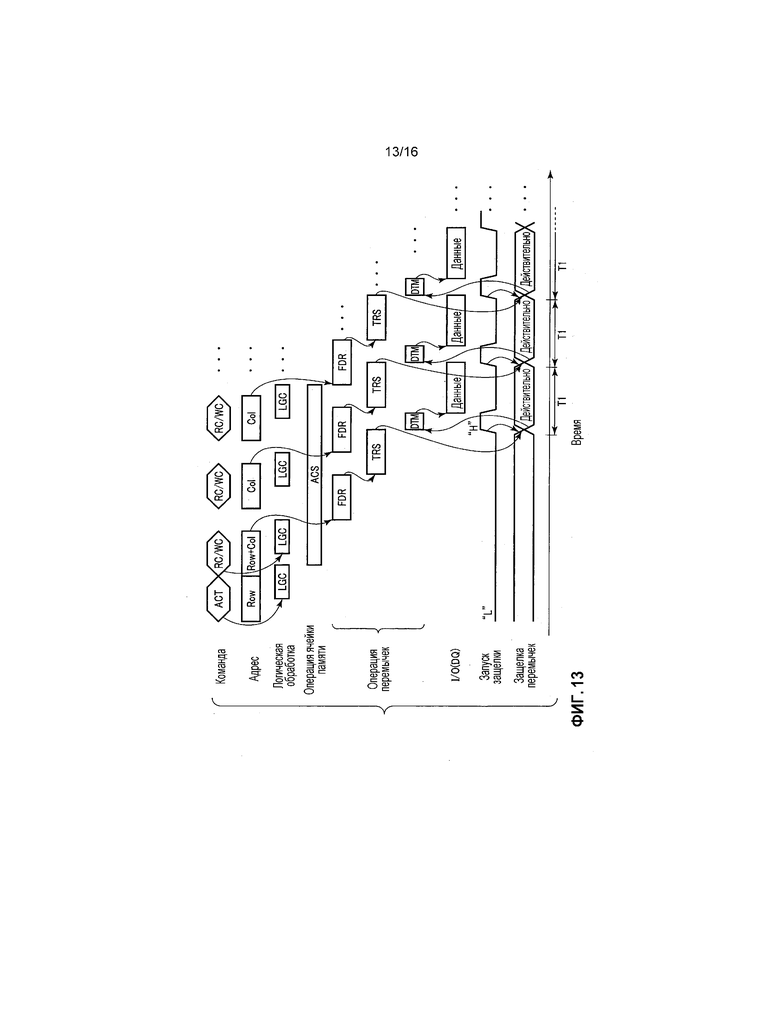

Фиг. 13 - временная диаграмма, иллюстрирующая пример работы устройства памяти в третьем варианте осуществления;

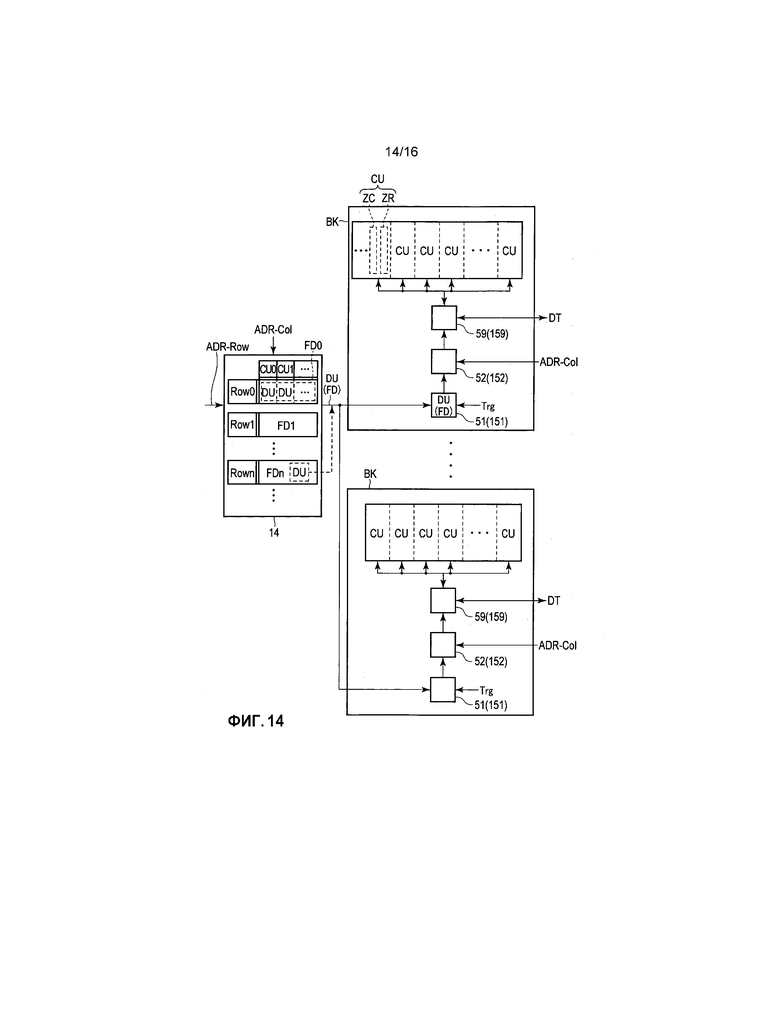

Фиг. 14 - схема, иллюстрирующая модификацию устройства памяти в третьем варианте осуществления;

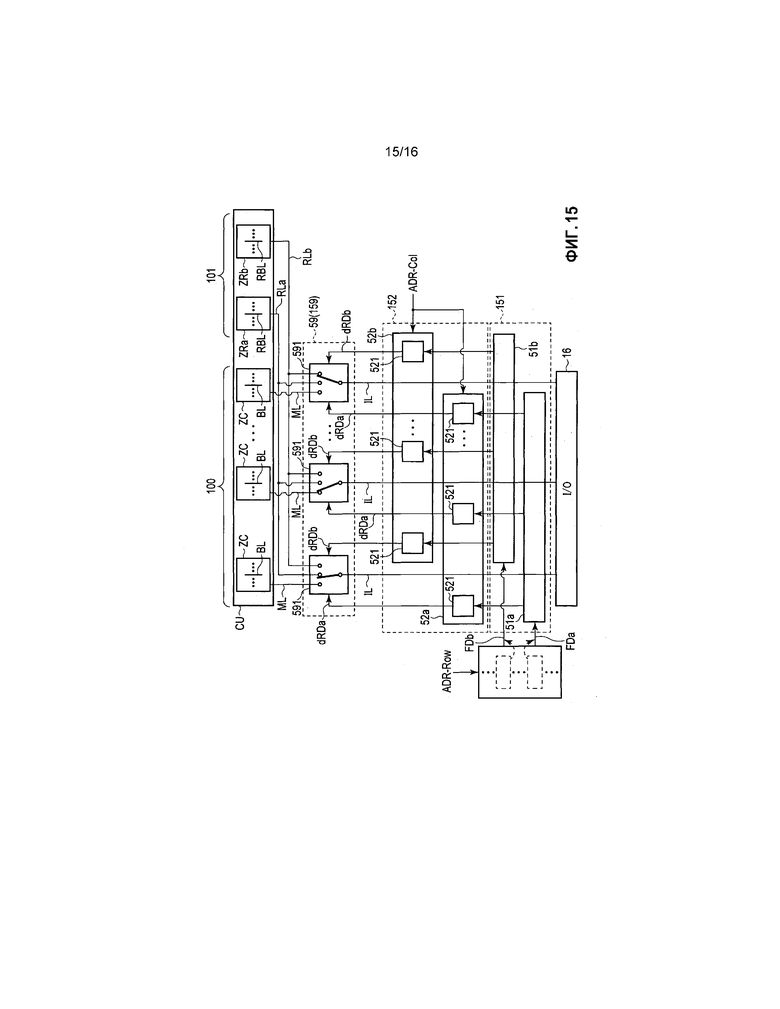

Фиг. 15 - схема, иллюстрирующая модификацию устройства памяти в вариантах осуществления; и

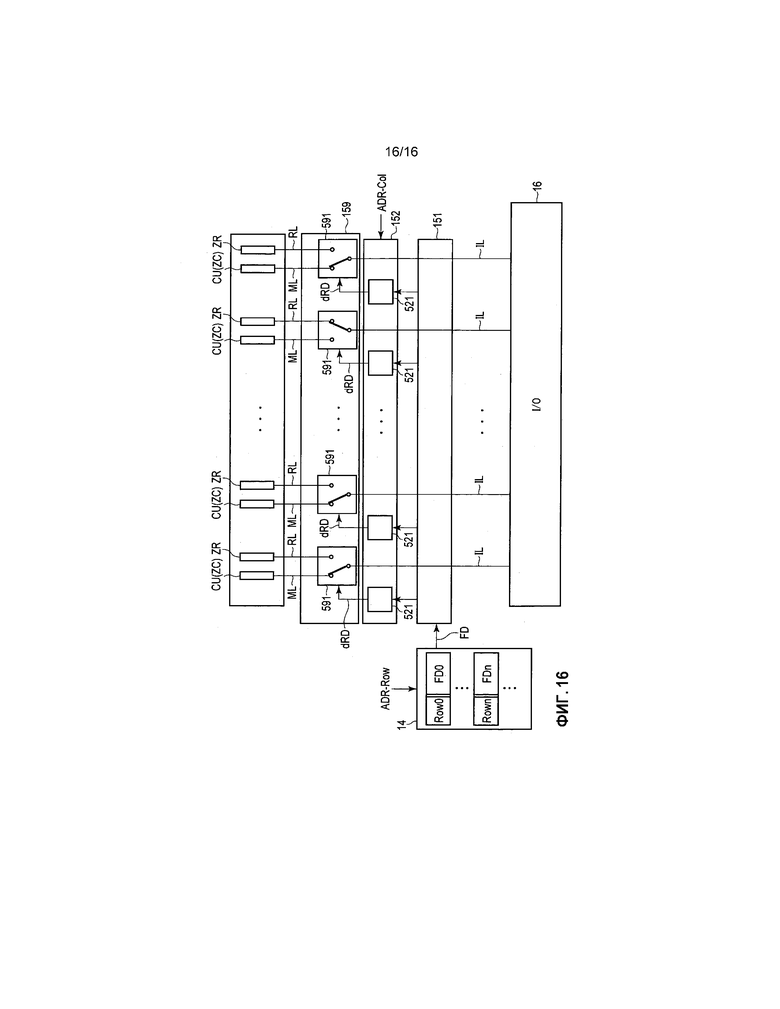

Фиг. 16 - схема, иллюстрирующая модификацию устройства памяти в вариантах осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

В общем, согласно одному варианту осуществления, устройство памяти включает в себя массив ячеек памяти, включающий в себя первый массив и второй массив; схему перемычек, выполненную с возможностью удерживать по меньшей мере одну часть первых данных, причем первые данные указывают адрес дефекта в первом массиве; и схему управления, выполненную с возможностью управления процессом замены на первом и втором массивах на основе первых данных. Когда подан первый адрес в первом направлении в первом массиве, схема перемычек переносит первые данные, соответствующие первому адресу, в схему управления, и когда подается второй адрес во втором направлении в первом массиве после того, как первые данные переданы в схему управления, схема управления осуществляет доступ к одному из первого и второго массивов на основе результата сравнения для второго адреса и первых данных.

[Варианты осуществления]

Устройства памяти в вариантах осуществления будут описаны со ссылкой на фиг. 1-16.

Элементы с одинаковыми функциями и конфигурациями в дальнейшем обозначаются одинаковыми ссылочными позициями, и повторяющиеся описания будут даваться по мере необходимости.

(1) Первый вариант осуществления

Со ссылкой на фиг. 1-9, будут описаны устройство памяти и способ управления им.

(a) Пример конфигурации

Фиг. 1 является схемой, изображающей общую конфигурацию системы памяти, включающей в себя устройство памяти в первом варианте осуществления.

Устройство 900 хранения связано с хост-устройством 999. Устройство 900 хранения и хост-устройство 999 передают данные с использованием, например, разъемов, беспроводной связи или Интернета.

Хост-устройство 999 запрашивает устройство 900 хранения для выполнения записи/стирания данных или считывания данных.

Устройство 900 хранения включает в себя устройство 1 памяти (например, память с изменяемым сопротивлением) в настоящем варианте осуществления и контроллер 9 памяти.

Память 1 с измененяемым сопротивлением в настоящем варианте осуществления связана с контроллером 9 памяти. Различные сигналы передаются и принимаются между памятью 1 с изменяемым сопротивлением и контроллером 9 памяти.

Контроллер 9 памяти выдает команду, указывающую запрос к памяти 1 с изменяемым сопротивлением для операции. Команда CMD представляет собой, например, сигнал, управляющий активацией межсоединения, или сигнал, управляющий считыванием данных или записью данных.

Контроллер 9 памяти подает в память 1 с изменяемым сопротивлением адрес ADR, указывающий цель для операции.

Контроллер 9 памяти подает в память 1 с изменяемым сопротивлением управляющий сигнал CNT, который позволяет управлять операцией памяти 1 с изменяемым сопротивлением, вместе с командой CMD и адресом ADR. Управляющий сигнал CNT включает в себя, например, сигнал разрешения тактирования, сигнал выбора чипа или сигнал стробирования данных и тому подобное.

Контроллер 9 памяти подает на память 1 с изменяемым сопротивлением внешний тактовый сигнал CK, который позволяет управлять операционной временной диаграммой для памяти 1 с изменяемым сопротивлением.

Данные DT передаются между контроллером 9 памяти и памятью 1 с изменяемым сопротивлением в соответствии с операцией, указанной командой CMD.

Память 1 с изменяемым сопротивлением выполняет операцию, запрашиваемую хост-устройством 999, на основе команды CMD и управляющего сигнала CNT от контроллера 9 памяти.

Память 1 с изменяемым сопротивлением включает в себя множество внешних соединительных выводов (терминалов) 81, 82, 83, 89, посредством которых сигналы передаются и принимаются. Внешние соединительные выводы 81-83, 89 представляют собой, например, контактные площадки. Внешние соединительные выводы 81-83, 89 могут быть штырьками или матрицами шариковых выводов.

Контактные площадки 81-83, 89 используются как часть интерфейса, который позволяет памяти 1 с изменяемым сопротивлением подключаться к контроллеру 9. Контактные площадки 81-83, 89 соединены с множеством командных/адресных линий CA, множеством линий DQ<0:n> данных или т.п., соответственно, в соответствии с функциями, назначенными контактным площадкам. Командные/адресные линии CA используются для передачи и приема команды CMD и адреса ADR. Линии данных (далее называемые линиями DQ) DQ<0:n> используются для передачи и приема данных. Линия управляющего сигнала используется для подачи управляющего сигнала CNT. Линия тактового сигнала используется для подачи тактового сигнала.

Множество контактных площадок (далее называемых контактными площадками CA) 81, которые разрешают передачу и прием команды CMD и адреса ADR, соединены с командными/адресными линиями CA.

Множество контактных площадок (далее называемых площадками DQ) 89, которые позволяют передавать и принимать данные, соединены с линиями DQ DQ<0:n>.

Контактная площадка 82, которая позволяет передавать и принимать управляющий сигнал, соединена с линией управляющего сигнала. Контактная площадка 83, которая позволяет принимать внешний тактовый сигнал, соединена с линией тактового сигнала.

Например, количество различных контактных площадок, предусмотренных в памяти 1 с изменяемым сопротивлением, определяется на основе спецификаций для памяти.

Фиг. 2 является схемой, изображающей пример конфигурации памяти с изменяемым сопротивлением в настоящем варианте осуществления.

Память 1 с изменяемым сопротивлением включает в себя множество банков BK (BK0, BK1, BKn-1).

Каждый из банков BK включает в себя массив 10 ячеек памяти, схему 12 управления столбцами и схему 13 управления строками.

Массив 10 ячеек памяти включает в себя множество ячеек МС памяти. Ячейки памяти соединены с числовыми линиями WL (word lines) и битовыми линиями BL (bit lines).

Массив 10 ячеек памяти включает в себя область 109 избыточности (резервирования).

Если дефектная ячейка памяти или дефектная битовая линия присутствует в области 101 в массиве 10 ячеек памяти, ячейки RDC памяти в области 109 избыточности используются вместо дефектной ячейки памяти и ячейки памяти, соединенной с дефектной битовой линией.

Для ясности описания, область 101, отличная от области 109 избыточности в массиве 10 ячеек памяти, упоминается далее как основная область 101. Основная область 191 используется главным образом в качестве области хранения для внешних данных. Кроме того, для ясности описания, ячейки памяти в области 109 избыточности далее упоминаются как ячейки RDC избыточности.

Схема 12 управления столбцами управляет столбцами в массиве 10 ячеек памяти.

Схема 12 управления столбцами включает в себя декодер 120 столбцов, схему 121 записи и схему 122 считывания.

Декодер 120 столбцов (схема переключения столбцов) представляет собой схему, которая позволяет осуществлять выбор из битовых линий BL. Схема 121 записи представляет собой схему, которая позволяет записывать данные в ячейку МС памяти. Схема 121 записи включает в себя схему источника/приемника, которая позволяет генерировать ток записи или напряжение записи. Схема 122 считывания представляет собой схему, которая позволяет считывать данные из ячейки МС памяти. Схема 122 считывания включает в себя усилитель считывания. Например, схема 12 управления столбцами включает в себя схему-защелку 124, которая временно удерживает данные из ячейки памяти.

Схема 12 управления столбцами включает в себя схему (далее упоминаемую как схема избыточности) 129 с усилителем считывания и переключателем столбцов, которая предусмотрена для ячеек RDC избыточности. Ячейки RDC избыточности и схема 129 избыточности рассматриваются как один набор (модуль) для замены дефекта.

Схема 13 управления строками управляет строками в массиве 10 ячеек памяти. Схема 13 управления строками включает в себя декодер строк (формирователь сигналов (драйвер) числовой линии), который позволяет осуществлять выбор из числовых линий WL.

Схема 14 перемычек имеет адрес дефекта в массиве 10 ячеек памяти (адрес блока, включающего в себя дефектную ячейку памяти/битовую линию) и информацию для управления избыточностью.

Схема 14 перемычек включает в себя модуль 141 перемычек (массив перемычек) и схему 142 управления перемычками.

Модуль 141 перемычек хранит по меньшей мере один адрес дефекта в массиве 10 ячейки памяти. Адрес дефекта записывается в модуль 141 перемычек на основе результатов тестирования памяти 1 с измененяемым сопротивлением.

Модуль 141 перемычек включает в себя множество элементов FS перемычек. Элементы FS перемычек упорядочены в виде массива в блоке 141 перемычек. Один элемент FS перемычки хранит 1-битовые данные. Разъединение или не-разъединение каждого из элементов FS перемычек устанавливается в зависимости от адреса дефекта, который необходимо сохранить.

Например, блок из множества элементов FS перемычек (блок перемычек) установлен в модуле 14 перемычек. Один блок перемычек имеет емкость хранения, которая позволяет хранить адрес дефекта, соответствующий одному блоку восстановления.

Например, элемент перемычки представляет собой электрически программируемый элемент перемычки (который далее упоминается как элемент электронной перемычки). Однако элемент перемычки может быть элементом перемычки, который может программироваться лазером (элемент пережигаемой лазером перемычки).

Площадь элемента электронной перемычки меньше площади элемента пережигаемой лазером перемычки. Таким образом, на определенной единичной площади, может быть установлено большее количество элементов электронных перемычек, чем количество элементов пережигаемых лазером перемычек. Когда используется элемент электронной перемычки, модуль 141 перемычек имеет увеличенную плотность хранения, что приводит к улучшению скорости восстановления дефектов в массиве 10 ячеек памяти.

Данные об адресах дефектов в блоке 141 перемычек в дальнейшем упоминаются как данные избыточности (или данные перемычек или данные адресов дефектов). Единица множества данных FD избыточности (от FD0 до FDn) упоминается как информация избыточности (или информация об адресах дефектов). n является натуральным числом, равным по меньшей мере 0.

Например, каждый фрагмент данных FD избыточности ассоциирован с адресом строки в массиве 10 ячеек памяти. Следовательно, одна часть данных FD избыточности может считываться на основе адреса строки. Кроме того, каждый фрагмент данных FD избыточности включает в себя адрес дефектной части относительно столбцов в массиве ячеек памяти. Данные FD избыточности включают в себя множество блоков данных, соответствующих блоку управления с определенным размером, установленным для столбцов в массиве ячеек памяти. Такие данные избыточности далее также упоминаются как данные избыточности столбцов.

Схема 142 управления перемычками управляет считыванием данных избыточности в блоке 141 перемычек и переносом считанных данных. Когда данные избыточности записываются в модуль 141 перемычек (перемычка пережигается), схема 142 управления перемычками управляет выбором целевых элементов перемычек записи, приложением напряжений к элементам перемычек и т.п.

Схема 142 управления перемычками принимает адрес ADR из контроллера 9 памяти. Схема 142 управления перемычками может, например, анализировать адрес ADR.

Например, как показано на фиг. 1, схема 14 перемычек (в частности, элементы перемычек) совместно обеспечены вблизи области, где расположены контактные площадки.

Схема 15 управления избыточностью использует информацию избыточности (адреса дефектов) из схемы 14 перемычек для управления операцией, выполняемой в области 109 избыточности. Например, схема 15 избыточности обеспечена в каждом банке ВК. Схема 15 избыточности обеспечена, например, между схемой 12 управления столбцами и схемой 16 I/O (ввода/вывода).

Схема 15 управления избыточностью включает в себя схему-защелку 151, схему 152 определения и схему 159 переключения.

Схема-защелка 151 временно удерживает данные FD избыточности, перенесенные из схемы 14 перемычек. Для пояснения описания, схема-защелка 151 далее упоминается как схема-защелка 151 перемычек.

Схема 152 определения сравнивает данные FD избыточности в схеме-защелке 151 перемычек с внешним адресом (например, адресом столбца), чтобы определить, следует ли заменить блок управления в основной области блоком управления в области избыточности. Для пояснения описания, схема 152 определения в дальнейшем упоминается как схема 152 определения замены.

Схема 159 переключения соединяет схему 16 I/O с одним из блоков управления в основной области и в области избыточности на основании результата определения из схемы определения замены. Для пояснения описания, схема 159 переключения далее упоминается как схема 159 переключателей замены.

Схема 16 I/O временно удерживает данные из массива 10 ячеек памяти и данные из контроллера 9 памяти. Схема 16 I/O принимает данные из массива 10 ячеек памяти через схему 12 управления столбцами и схему 15 управления избыточностью. Схема 16 I/O принимает данные из контроллера 9 памяти через линию DQ и контактную площадку DQ.

Схема-защелка 17 команды/адреса временно удерживает команду CMD и адрес ADR, поданные на контактную площадку 81 СА, и в определенное время переносит команду CMD и адрес ADR к каждой схеме в памяти 1. Схема-защелка 17 команды/адреса выводит команду CMD в задатчик последовательности (секвенсор) 19. Схема-защелка 17 команды/адреса выдает адрес ADR (ADR-Row, ADR-Col) в схему 13 управления строками, схему 12 управления столбцами и схему 142 управления перемычками. Адрес ADR контактной площадки 81 может быть подан непосредственно в схему 142 управления перемычками.

Схема 18 генерации тактовых импульсов генерирует внутренний тактовый сигнал CLK для внутренней части памяти 1 с изменяемым сопротивлением на основе внешнего тактового сигнала CK.

Секвенсор 19 управляет работой всей внутренней части памяти 1 с изменяемым сопротивлением на основе команды CMD и управляющего сигнала CNT от контроллера 9 памяти.

Внутренняя конфигурация массива ячеек памяти в памяти с изменяемым сопротивлением в настоящем варианте осуществления будет описана со ссылкой на фиг. 3-5.

Как показано на фиг. 3, массив 10 ячеек памяти включает в себя множество областей SEG управления. Области SEG управления далее упоминаются как сегменты SEG.

Фиг. 3 является схематичным представлением внутренней конфигурации массива ячеек памяти.

Сегмент SEG является областью, являющейся результатом логического деления. Сегмент SEG является областью, обозначенной адресом строки из нескольких битов и адресом столбца из нескольких битов.

Для упрощения описания, фиг. 3 иллюстрирует пример, в котором восемь сегментов SEG предусмотрены в массиве 10 ячеек памяти. В этом случае массив 10 ячеек памяти разделен на две логические области (блоки управления) в направлении X и четыре логические области (блоки управления) в направлении Y для установки сегментов SEG.

Сегмент SEG включает в себя основную область 101. Например, область 109 избыточности обеспечена в каждом сегменте SEG. Когда конфигурация избыточности столбцов применяется к массиву 10 ячеек памяти, область 109 избыточности обеспечивается в сегменте SEG, смежном с основной областью 101 в направлении X.

Фиг. 4 является схемой, изображающей пример схемной конфигурации массива ячеек памяти в памяти с изменяемым сопротивлением в настоящем варианте осуществления. Фиг. 4 иллюстрирует внутреннюю конфигурацию массива ячеек памяти путем выделения части внутренней области массива ячеек памяти.

Как показано на фиг. 4, в основной области 101 в массиве 10 ячеек памяти, множество ячеек MC памяти расположены вдоль направления X и направления Y.

Множество ячеек МС памяти, расположенных в направлении X, соединено с общей числовой линией WL.

Множество ячеек памяти MC, расположенных в направлении Y, соединено с общими битовыми линиями BL и bBL.

Одна числовая линия WL и две битовые линии BL и bBL пары битовых линий соединены с каждой из ячеек МС памяти.

Ячейка МС памяти включает в себя один элемент 30 памяти и один элемент 31 выбора.

Элемент 30 памяти представляет собой элемент изменения сопротивления. Элемент 30 изменения сопротивления в качестве элемента памяти может принимать множество значений сопротивления. Ассоциирование определенного значения сопротивления с данными позволяет элементу 30 изменения сопротивления удерживать данные, которые необходимо сохранить.

Элемент выбора 31 представляет собой полевой транзистор (далее называемый транзистором ячейки). Транзистор 31 ячейки включается для обеспечения ввода и вывода данных в ячейку MC и из ячейки МС памяти.

Например, один конец элемента 30 изменения сопротивления соединен с битовой линией BL, а другой конец элемента 30 изменения сопротивления соединен с одним концом пути тока (исток/сток) в транзисторе 31 ячейки. Другой конец пути тока в транзисторе 31 ячейки соединен с битовой линией bBL. Числовая линия WL соединена с затвором транзистора 31 ячейки.

Напряжение уровня Н (напряжение включения для транзистора ячейки) прикладывается к числовой линии WL для выбора ячеек МС памяти. В зависимости от операции, выполняемой на ячейке МС памяти, одна из двух битовых линий BL, bBL пары битовых линий устанавливается на высокий потенциал, тогда как другая битовая линия устанавливается на низкий потенциал.

Множество ячеек RDC избыточности расположено в области 109 избыточности. Ячейка RDC избыточности соединена с одной числовой линией WL и двумя битовыми линиями RBL, bBL пары битовых линий. Для пояснения описания, битовые линии RBL, bRBL, с которыми соединена ячейка RDC избыточности, упоминается как битовые линии RBL, bRBL избыточности.

Ячейка RDC избыточности, расположенная на той же прямой линии, на которой ячейка MC памяти расположена в направлении X, соединена с числовой линией WL, общей для ячейки MC памяти. Множество ячеек RDC избыточности, расположенных в направлении Y, соединены с общими битовыми линиями RBL, bRBL избыточности.

Ячейка RDC избыточности включает в себя один элемент 30 изменения сопротивления (элемент памяти) и транзистор 31 (элемент выбора) ячейки аналогично ячейке MC ячейки памяти.

Например, элементы 30, 31 ячейки RDC избыточности соединены с битовыми линиями RBL, bRBL избыточности и числовой линией WL, по существу, как и в случае отношений соединения между ячейкой МС памяти и битовыми линиями/числовой линией.

Ячейка RDC избыточности, соединенная с той же числовой линией WL, с которой соединена выбранная ячейка, включается в то же время, когда включается выбранная ячейка. В зависимости от операции, выполняемой в ячейке RDC избыточности, одна из двух битовых линий RBL, bRBL избыточности, соединенных с ячейкой RDC избыточности, устанавливается на высокий потенциал, тогда как другая битовая линия избыточности устанавливается на низкий потенциал.

Внутренняя конфигурация массива 10 ячеек памяти может быть массивом ячеек памяти перекрестного типа. В массиве ячеек памяти перекрестного типа, один конец ячейки памяти соединен с битовой линией, а другой конец ячейки памяти соединен с числовой линией.

Фиг. 5 является схематичным представлением, изображающим пример структуры ячейки памяти в памяти с изменяемым сопротивлением в настоящем варианте осуществления.

Как показано на фиг. 5, когда память с изменяемым сопротивлением представляет собой MRAM STT-типа (с переносом спинового момента), ячейка памяти включает в себя магниторезистивный элемент 30 в качестве элемента памяти.

Магниторезистивный элемент 30, используемый для MRAM, представляет собой элемент с магнитным туннельным переходом (MTJ). Магниторезистивный элемент 30 в дальнейшем упоминается как элемент MTJ.

Элемент 30 MTJ включает в себя, по меньшей мере, слой 300 хранения, опорный слой 302 и туннельный барьерный слой 301. Туннельный барьерный слой (например, пленка оксида магния) 301 находится между слоем 300 хранения и опорным слоем 302. Нижний электрод 309А предусмотрен под элементом 30 MTJ. Верхний электрод 309B предусмотрен над элементом 30 MTJ.

Слой 300 хранения и опорный слой 302 представляют собой магнитные слои с перпендикулярной магнитной анизотропией. Намагниченность (направление намагниченности) в слое 300 хранения и опорном слое 302 перпендикулярна к поверхности слоя (поверхности пленки). Направление намагниченности в слое 300 хранения является переменным, а направление намагничивания в опорном слое 302 является неизменным (фиксированное состояние).

Когда направление намагниченности в слое 300 хранения совпадает с направлением намагниченности в опорном слое 302 (когда элемент MTJ находится в состоянии параллельной ориентации намагниченности), элемент 30 MTJ имеет первое состояние сопротивления (первое значение сопротивления). Когда направление намагниченности в слое 300 хранения отличается от направления намагниченности в опорном слое 302 (когда элемент MTJ находится в состоянии антипараллельной ориентации намагниченности), элемент 30 MTJ имеет второе сопротивление (второе значение сопротивления). Значение сопротивления элемента 30 MTJ в первом состоянии сопротивления меньше, чем значение сопротивления элемента 30 MTJ во втором состоянии сопротивления.

Транзистор 31 ячейки представляет собой транзистор со структурой углубленного затвора.

Транзистор 31 ячейки имеет два диффузионных слоя 312А, 312В в качестве областей истока/стока транзистора 31 ячейки. Два диффузионных слоя 312А, 312В обеспечены в полупроводниковой области 390.

Электрод 310 затвора обеспечен между двумя диффузионными слоями 312А и 312В. Электрод 310 затвора углублен в канавке в полупроводниковой области 390. Изолирующая пленка 311 затвора обеспечена между электродом 310 затвора и полупроводниковой областью 390. Электрод 310 затвора простирается в направлении X и функционирует как числовая линия WL.

Верхний электрод 309B элемента 30 MTJ соединен с битовой линией BL через проходной штекер (не изображен на чертежах). Нижний электрод 309А элемента 30 MTJ соединен с диффузионным слоем 312А транзистора 31 ячейки через контактный штекер CP1. Диффузионный слой 312В транзистора 31 ячейки соединен с битовой линией bBL через контактный штекер CP2.

Ячейка RDC избыточности имеет ту же структуру, что и таковая у ячейки MC памяти.

Когда данные записываются в ячейку МС памяти, на элемент 30 MTJ подается ток записи. Ток записи протекает через элемент 30 MTJ для изменения направления намагниченности слоя 300 хранения. Изменение в относительной ориентации намагниченности между слоем 300 хранения и опорным уровнем 302, в свою очередь, изменяет значение сопротивления элемента 30 MTJ. В результате, данные записываются в ячейку МС памяти. В зависимости от записываемых данных (ʺ1ʺ или ʺ0ʺ), направление, в котором ток записи протекает между слоем 300 хранения и опорным слоем 302, управляется схемой 121 записи.

Магнитные свойства опорного слоя 302 управляются таким образом, чтобы предотвратить изменение направления намагниченности опорного слоя 302 током записи, когда ток записи подается на элемент 30 MTJ. Это обеспечивает опорный слой 302 с неизменным направлением намагниченности.

Считывание данных из ячейки МС памяти выполняется путем пропускания тока считывания через элемент 30 MTJ. Значение тока (или потенциал) узла считывания изменяется в соответствии с состоянием сопротивления элемента 30 MTJ. Определенное опорное значение и значение тока считываемого узла сравнивается с помощью усилителя считывания в схеме 122 считывания. В результате определяются данные, хранящиеся в элементе 30 MTJ.

Значение тока для тока считывания устанавливается на величину, которая не изменяет состояние сопротивления элемента 30 MTJ.

Память 1 с изменяемым сопротивлением в настоящем варианте осуществления может быть резистивной памятью (RERAM) или памятью с изменяемым фазовым состоянием (PCRAM). Следовательно, элемент 30 памяти может представлять собой элемент с изменяемым сопротивлением металл-оксидного перехода (например, элемент с пленкой оксида никеля или пленкой оксида титана) или элемент с изменяемым фазовым состоянием (например, элемент с халькогенидной пленкой).

Перенос данных в ячейку памяти, имеющую конфигурацию, показанную на фиг. 3-5, выполняется путем выбора (активации) из числовых линий и битовых линий на основе адреса.

Множество блоков доступа установлено для столбцов в массиве 10 ячеек памяти (или сегментов SEG). Блоки доступа, установленные для столбцов, далее упоминаются как блоки доступа к столбцам.

Множество блоков доступа установлено для строк в массиве 10 ячеек памяти (или сегментов SEG). Блоки доступа, установленные для строк, далее упоминаются как блоки доступа к строкам. Блок доступа к строкам упоминается, например, как страница и соответствует блоку, соответствующему одной числовой линии.

Ячейка памяти в основной области 101 выбирается как цель доступа с использованием блока доступа к строкам и блока доступа к столбцам на основе внешнего адреса.

Как показано на фиг. 3, дефект DF может возникать в ячейке МС памяти или в схеме, соединенной с битовой линией BL (например, усилителе считывания). Блок столбца, включающий в себя дефектную ячейку памяти, дефектную битовую линию и дефектную схему, в далее упоминается как дефектный столбец.

Дефектный столбец DF может препятствовать доступу к ячейке памяти.

Для восстановления такого дефектного столбца DF, ячейка RDC избыточности заменяется недоступной ячейкой памяти. Ячейка RDC избыточности выбирается в качестве альтернативы цели доступа к недоступной ячейке МС памяти. Набор из ячейки RDC избыточности, битовых линий избыточности и схемы избыточности упоминается как столбец избыточности. Для пояснения описания, набор из ячейки МС памяти, битовой линии и схемы столбца на стороне основной области 101 упоминается как основной столбец. Например, основной столбец представляет собой блок, включающий в себя по меньшей мере одну битовую линию.

Для процесса замены для дефектной ячейки памяти и ячейки RDC избыточности, в массиве 10 ячеек памяти установлен блок восстановления (набор из некоторого числа битовых линий), имеющий определенный размер. В массиве 10 ячеек памяти в конфигурации избыточности столбцов, множество блоков восстановления установлено для столбцов в массиве 10 ячеек памяти. Блоки восстановления являются блоками управления, установленными путем логического разделения массивов 10 ячеек памяти (сегментов SEG). Например, блок столбца, включающий в себя по меньшей мере одну битовую линию BL (по меньшей мере одну битовую линию RBL избыточности), является блоком восстановления (блоком замены дефектов).

В основной области 101, когда, например, блок CU доступа к столбцам включает в себя дефект DF, группа из по меньшей мере одной битовой линии, включающая в себя дефект DF (основной столбец), заменяется на группу (столбец избыточности) ZR битовых линий избыточности, которые идентичны по количеству битовым линиям, в качестве блока восстановления.

Фиг. 3 иллюстрирует пример, в котором одна битовая линия RBL избыточности заменяет одну битовую линию BL с дефектом DF в качестве блока восстановления для упрощения описания.

Как описано выше, дефектная часть в массиве 10 ячеек памяти (основной области 101) и схема управления столбцами восстанавливается элементом/схемой избыточности, применяемыми к памяти.

Количество блоков восстановления в массиве ячеек памяти (или сегментов, блоков доступа к столбцам) коррелирует с процентом дефектов в массиве ячеек памяти и количеством данных избыточности в памяти с изменяемым сопротивлением (количеством элементов перемычек). Когда количество блоков восстановления увеличивается, коэффициент восстановления дефектов улучшается. Однако количество перемычек существенно увеличивается пропорционально количеству блоков восстановления.

Процесс замены для дефектного столбца и столбца избыточности выполняется схемой 15 управления избыточностью.

Фиг. 6 является схемой, изображающей пример конфигурации схемы управления избыточностью в памяти с изменяемым сопротивлением в настоящем варианте осуществления. Фиг. 6 является схемой, иллюстрирующей внутреннюю конфигурацию схемы 15 управления избыточностью и отношения соответствия между массивом 10 ячеек памяти (например, сегментами SEG) и схемой 15 управления избыточностью.

Как описано выше, для массива 10 ячеек памяти (сегмента SEG) и схемы управления столбцами (например, усилителя считывания) установлен по меньшей мере один блок CU доступа к столбцам.

Фиг. 6 иллюстрирует один выделенный блок CU доступа к столбцам.

Дефектный столбец в блоке CU доступа к столбцам заменяется блоком ZR восстановления (столбцом избыточности) в области 109 избыточности с использованием блока восстановления (основного столбца) ZC в блоке CU доступа к столбцам.

Схема-защелка 151 перемычек включает в себя множество блоков-защелок 51. Блоки-защелки 51 включены в схему-защелку 151 перемычек в ассоциации с блоками CU доступа к столбцам. Блок-защелка 51 может удерживать данные с битовой длиной, указывающей адрес одного блока доступа к столбцам.

Схема-защелка 151 перемычек извлекает данные FD избыточности, соответствующие выбранному адресу строки, из массива 141 перемычек. Когда схема-защелка 151 перемычек извлекает данные избыточности, данные FD избыточности устанавливаются в действительное состояние в схеме 15 управления избыточностью.

Например, блок-защелка 51 имеет емкость хранения приблизительно 5 битов в соответствии с размером блока данных (данных избыточности в массиве ячеек памяти) в блоке CU доступа к столбцам.

Схема-защелка 151 перемычек может удерживать данные FD избыточности для одного блока доступа к строкам. Следовательно, в настоящем варианте осуществления, емкость хранения схемы-защелки 151 перемычек меньше, чем емкость хранения модуля 141 перемычек.

Схема 152 определения замены сравнивает предоставленный выбранный адрес столбца ADR-Col с данными FD избыточности в схеме-защелке 151 перемычек. На основании результата сравнения для адреса столбца ADR-Col и данных FD избыточности, схема 152 определения определяет, следует ли заменять основной столбец (дефектный столбец) на столбец избыточности.

Схема 152 определения замены включает в себя множество блоков 52 определения.

Блоки 52 определения обеспечены в схеме 152 определения замены в ассоциации с блоками восстановления (блоками замены) в блоке CU доступа к столбцам. Количество блоков 52 определения совпадает с количеством блоков-защелок 51. Блок 52 определения обращается к данным FD избыточности в схеме-защелке 51.

Например, блок 52 определения включает в себя множество арифметических схем (логических схем) 521 в ассоциации с блоками ZC восстановления основной стороны в блоке CU доступа к столбцам. Это позволяет выполнять определение, следует ли заменить дефектный столбец в основной области, в блоках восстановления.

В зависимости от того, соответствует ли выбранный адрес столбца ADR-Col адресу дефекта в данных избыточности в каждом блоке-защелке 51, арифметическая схема 521 управляет уровнем сигнала управляющего сигнала dRD.

Когда некоторая арифметическая схема 521 определяет, что выбранный адрес столбца ADR-Col соответствует данным FD избыточности, арифметическая схема 521 выдает управляющий сигнал на первом уровне сигнала (например, уровне H). Результат определения того, что выбранный адрес столбца ADR-Col соответствует данным FD избыточности, указывает, что основной столбец, соответствующий выбранному адресу столбца, является дефектным.

Когда выбранный адрес столбца ADR-Col не соответствует данным FD избыточности в блоке-защелке 51, арифметическая схема 521 выдает управляющий сигнал dRD на втором уровне сигнала (например, уровне L). Результат определения того, что выбранный адрес столбца ADR-Col не соответствует данным FD избыточности, указывает, что основной столбец, соответствующий выбранному адресу столбца, является нормальным (не дефектным).

На основе управляющего сигнала dRD из схемы 152 определения замены, схема 159 переключателей замены соединяет схему 16 I/O с межсоединением (внутренней линией данных) IL стороны основной области 101 или с межсоединением (линией данных избыточности) RL стороны области 109 избыточности.

Схема 159 переключателей замены включает в себя множество блоков 59 переключения.

Блоки 59 переключения предусмотрены в схеме 159 переключателей замены в ассоциации с блоками CU доступа к столбцам.

Количество блоков 59 переключения совпадает с количеством блоков 52 определения и количеством блоков-защелок 51.

Блок 59 переключения включает в себя множество переключателей 591 в ассоциации с блоками ZC восстановления основной стороны в блоке CU доступа к столбцам.

Каждый из переключателей 591 принимает управляющий сигнал dRD из арифметической схемы 521.

Переключатель 591 управляет соединением между схемой 16 I/O и столбцом ZR избыточности (области 109 избыточности) в соответствии с уровнем сигнала, соответствующим результату определения замены.

Когда управляющий сигнал dRD на первом уровне сигнала (например, уровне H) подается на переключатель 591, переключатель 591 соединяет линию RL данных избыточности со схемой 16 I/O.

Когда дефектный столбец присутствует в основной области 101, как описано выше, выполняется процесс замены для дефектного столбца и столбца избыточности. В настоящем примере, когда часть ZC в одном блоке CU доступа к столбцам содержит дефект DF, часть ZC, включающая в себя дефект DF, заменяется столбцом ZR избыточности.

Процесс замены позволяет переносить данные из столбца ZR избыточности в схему 16 I/O во время считывания данных. В качестве альтернативы, данные в схеме 16 I/O переносятся в столбец ZR избыточности во время записи данных.

Когда управляющий сигнал dRD на втором уровне сигнала подается на переключатель 591, переключатель 591 соединяет внутреннюю линию IL данных, соединенную с основным столбцом ZC, со схемой 16 I/O. Таким образом, перенос данных между основной областью 101 и схемой 16 I/O осуществляется без выполнения процесса замены.

Как описано выше, память 1 с изменяемым сопротивлением в настоящем варианте осуществления использует данные FD избыточности и схему 15 избыточности для обеспечения переноса данных в ячейку избыточности (столбец избыточности) вместо дефектной ячейки (дефектного столбца). Таким образом, память 1 с изменяемым сопротивлением в настоящем варианте осуществления позволяет восстанавливать дефекты в массиве 10 ячеек памяти.

На фиг. 6, для упрощения и пояснения описания, одна внутренняя линия IL данных соединена с каждым переключателем 591, и одна линия RL данных избыточности соединена с множеством блоков 591 переключения. Однако количество линий IL, RL данных, соединенных с одним переключателем 591, может быть изменено по мере необходимости в соответствии с конфигурацией по меньшей мере одного из блока доступа к столбцам и столбца избыточности (блока избыточности), установленного для массива ячеек памяти. В связи с этим количество переключателей 591, соответствующих одной арифметической схеме 521, может быть изменено по мере необходимости.

В операционной последовательности для памяти с изменяемым сопротивлением, команда, позволяющая активировать числовую линию (строку), и адрес числовой линии (адрес выбранной строки) передаются из контроллера 9 памяти в память 1 с изменяемым сопротивлением через вывод 81 CA как набор сигналов.

После того как память 1 с изменяемым сопротивлением получает команду и адрес для управления строкой, набор сигналов, включающий в себя команду, указывающую на операцию, выполняемую в ячейке памяти, и адрес битовой линии (адрес выбранного столбца), передается из контроллера 9 памяти в память 1 с изменяемым сопротивлением через вывод 81 CA.

В этом случае память 1 с изменяемым сопротивлением выполняет управление для строк в массиве ячеек памяти на основе адреса строки, а затем выполняет управление для столбцов в массиве ячеек памяти на основе адреса столбца.

В памяти 1 с изменяемым сопротивлением в настоящем варианте осуществления, схема 14 перемычек выводит в схему 15 управления избыточностью одну часть данных избыточности (данных, указывающих адрес дефекта) FD среди множества данных избыточности (информации избыточности) в схему 14 перемычек, который соответствует адресу ADR, предоставляемому извне (например, от контроллера памяти). Одна часть данных FD избыточности, которая должна быть выведена, выбирается на основе адреса ADR.

Например, схема 142 управления перемычками переносит, в схему-защелку 151 перемычек в схеме 15 управления избыточностью, одну часть данных FD избыточности среди множества данных избыточности, хранящихся в блоке 141 перемычек, который ассоциирован со всем или частью внешнего выбранного адреса ADR-Row строки, на основе выбранного адреса ADR-Row строки, предоставленного извне.

Память 1 с изменяемым сопротивлением в настоящем варианте осуществления переносит данные FD избыточности в схему-защелку 151 перемычек в течение периода от приема команды/адреса строки CMD, ADR до завершения обработки над строками в массиве 10 ячеек памяти (логической обработки).

Таким образом, память 1 с изменяемым сопротивлением в настоящем варианте осуществления может выполнять управление избыточностью без считывания всех данных избыточности в схеме 14 перемычек в схему-защелку 151 перемычек.

В результате, память с изменяемым сопротивлением в настоящем варианте осуществления позволяет уменьшить масштаб схемы (количество блоков-защелок) схемы-защелки 51 перемычек.

Кроме того, в памяти с изменяемым сопротивлением в настоящем варианте осуществления, схема-защелка 151 перемычек может иметь возможность сохранять объем данных в соответствии с количеством блоков доступа к столбцам, назначенных массиву ячеек памяти (или сегментам). Следовательно, память с изменяемым сопротивлением в настоящем варианте осуществления позволяет использовать модуль перемычек с высокой плотностью хранения, чтобы повысить эффективность восстановления без чрезмерного увеличения масштаба схемы для схемы-защелки 151 перемычек.

Как описано выше, память с изменяемым сопротивлением в настоящем варианте осуществления позволяет увеличить эффективность восстановления и позволяет уменьшить размер чипа.

(b) Пример работы

Пример работы устройства памяти (например, памяти с изменяемым сопротивлением) в первом варианте осуществления будет описан со ссылкой на фиг. 7-9. В этом отношении, пример работы устройства памяти в настоящем варианте осуществления будет описан с использованием фиг. 1-6, в дополнение к фиг. 7-9.

Фиг. 7 является блок-схемой последовательности операций, иллюстрирующей пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления. Фиг. 8 является временной диаграммой, иллюстрирующей пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления. Фиг. 9 является схематичным представлением, иллюстрирующим пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления.

Как показано на фиг. 7 и фиг. 8, при включении питания, память 1 с изменяемым сопротивлением (например, MRAM) в настоящем варианте осуществления выполняет операцию начальной настройки на основе информации о настройке от хост-устройства 999 и контроллера 9, предварительной зарядки межсоединений (например, битовых линий) внутри памяти 1 и т.п., без считывания данных избыточности в блоке 141 перемычек (ST0).

В соответствии с запросом от хост-устройства 999 для считывания данных или записи данных, контроллер 9 памяти передает команду активации CMD-ACT и адрес ADR в память 1 через контактную площадку 81 СА.

В настоящем варианте осуществления, адрес, переданный вместе с командой активации CMD-ACT, является адресом строки ADR-Row.

Память 1 по существу одновременно принимает команду активации CMD-ACT и адрес строки ADR-Row (этап ST1). Команда CMD-ACT и адрес ADR-Row вводятся в схему-защелку 17 команды/адреса. Схема-защелка 17 команды/адреса переносит команду CMD-ACT в секвенсор 19.

Секвенсор 19 выполняет логическую обработку LGC над командой CMD-ACT. Таким образом, секвенсор 19 распознает, что команда CMD-ACT является командой активации, и выполняет управление каждой схемой на основе команды CMD-ACT.

Адрес строки ADR-Row переносится из схемы-защелки 17 команды/адреса в схему 13 управления строками (декодер строк). Схема 13 управления строками (декодер строк) декодирует адрес строки ADR-Row. Таким образом, определяется адрес строки для доступа (выбранный адрес строки, страница). Секвенсор 19 выполняет управление на основе команды CMD-ACT для активации числовой линии WL, соответствующей выбранной странице.

Когда выбранная числовая линия активирована, ячейка МС памяти и ячейка RDC избыточности, соединенная с выбранной числовой линией, устанавливаются во включенное состояние, и ячейки MC, RDC становятся доступными.

Непрерывно или параллельно с вводом команды активации в определенный банк, команда активации CMD-ACT и адрес ADR-Row для другого банка могут быть приняты памятью 1.

Секвенсор 19 выполняет обработку доступа ACS на массиве 10 ячеек памяти на основе адреса строки ADR-Row. Таким образом, разрешаются ввод и вывод данных в массив 10 и из массива 10 ячеек памяти.

Параллельно с внутренней обработкой на массиве 10 ячеек памяти на основе команды CMD-ACT, память 1 выполняет операцию перемычки для процесса замены (этап ST2).

Адрес строки ADR-Row подается на схему 14 перемычек.

Схема 142 управления перемычками декодирует адрес строки ADR-Row. На основе декодированного адреса строки ADR-Row, схема 142 управления перемычками выполняет операцию считывания FDR данных FD избыточности в блоке 141 перемычек.

Как показано на фиг. 9, данные избыточности столбцов данных FD избыточности, ассоциированных с соответствующими блоками доступа к строкам в блоке 141 перемычек, которые соответствуют выбранному адресу строки ADR-Row, считываются из модуля 141 перемычек (этап ST2).

Например, схема 142 управления перемычками обращается к части выбранного адреса строки ADR-Row, которая указывает блок управления в строке (например, адресу, указывающему сегмент или адрес выбранной числовой линии), чтобы избирательно считывать данные избыточности в блоке 141 перемычек.

Схема 142 управления перемычками выполняет операцию переноса TRS данных избыточности в схему 15 управления избыточностью.

Например, считывание и перенос данных из модуля 141 перемычек на основе выбранного адреса строки может выполняться на множестве банков параллельно. Те же самые данные FD избыточности могут быть перенесены во множество банков. Кроме того, различные данные для соответствующих банков могут переноситься в соответствующие банки в соответствующее время.

Схема-защелка 151 перемычек извлекает данные FD избыточности.

Каждые данные FD избыточности удерживается блоком-защелкой, соответствующим блоку доступа к столбцам. Каждый блок-защелка 51 удерживает часть (блок данных) данных FD избыточности, которая соответствует блоку CU доступа к столбцам, соответствующему блоку-защелке. Каждый блок-защелка 51 удерживает блоки данных DU (от DU0 до DUm), включая различные адреса дефектных столбцов, m является натуральным числом, равным по меньшей мере 1.

Схема 152 определения замены подготавливает процесс определения для замены между дефектным столбцом и столбцом избыточности.

По прошествии определенного периода от момента передачи команды активации CMD-ACT, контроллер 9 памяти передает команду считывания RC (или команду записи) и адрес столбца (выбранный адрес столбца) ADR-Col в память 1.

Память 1 принимает команду считывания RC и адрес столбца ADR-Col (этап ST3).

Секвенсор 19 выполняет логическую обработку LGC по команде CMD-RC. Таким образом, секвенсор 19 распознает, что команда CMD-RC является командой считывания, и выполняет управление схемами для считывания данных.

Адрес столбца ADR-Col переносится в схему 12 управления столбцами (декодер 120 столбцов). Декодер 120 столбцов декодирует адрес столбца ADR-Col. Таким образом, битовая линия и схемы, указанные декодированным выбранным адресом столбца, активируются.

Декодированный выбранный адрес столбца ADR-Col переносится в схему 152 определения замены.

Схема 152 определения замены сравнивает адрес столбца ADR-Col с данными FD избыточности в схеме-защелке 151 перемычек (этап ST4). Схема 152 определения замены определяет, соответствует ли выбранный адрес столбца ADR-Col данным избыточности столбца, соответствующим выбранному адресу строки ADR-Row (этап ST5).

Каждый из блоков 52 определения выполняет процесс определения (логическую обработку) DTM над адресом столбца ADR-Col, предоставленным контроллером 9 памяти, и данными FD избыточности в соответствующем блоке-защелке 51.

Каждый блок 52 определения выводит управляющий сигнал dRD на основе результата сравнения для адреса столбца ADR-Col и данных избыточности в схему 159 переключателей избыточности.

Когда в определенной арифметической схеме 521 в блоке 52 определения, соответствующем основному столбцу цели доступа, выбранный адрес столбца ADR-Col совпадает с данными FD избыточности в блоке-защелке 51, арифметическая схема 521 выводит управляющий сигнал dRD на первом уровне (например, уровне H) на переключатель 591, соответствующий арифметической схеме 521.

Например, арифметическая схема 521 выполняет логическую обработку на той части адреса столбца ADR-Col и той части данных избыточности, которой соответствует арифметическая схема 521.

На основе первого уровня сигнала, переключатель 591 соединяет линию RL данных избыточности с внутренней линией IL данных.

Таким образом, столбец ZR избыточности в области 109 избыточности соединяется со схемой 16 I/O.

Основной столбец (дефектный столбец) в основной области 101, соответствующий переключателю 591, на который был подан первый уровень сигнала (уровень H), электрически отделяется от схемы 16 I/O блоком 59 переключателей.

Дефектный основной столбец ZC заменяется столбцом ZR избыточности в области 109 избыточности (этап ST6A).

Когда арифметическая схема 521 определяет, что адрес столбца ADR-Col не соответствует данным FD избыточности, арифметическая схема 521 выдает управляющий сигнал dRD на втором уровне (например, уровне L), отличающемся от первого уровня, на переключатель 591.

Когда управляющий сигнал dRD на втором уровне сигнала (L) подается на переключатель 591, переключатель 591 соединяет основную линию ML данных с внутренней линией IL данных. Таким образом, основной столбец ZC в основной области 101 соединяется со схемой 16 I/O.

Когда основной столбец ZC цели доступа, указанный выбранным адресом, определяется таким образом, что он не является дефектным столбцом (определяется как нормальный), процесс замены не выполняется (этап ST6B).

Как описано выше, когда дефектный столбец присутствует в блоке CU доступа к столбцам, часть блока CU доступа к столбцам, которая содержит дефект, заменяется столбцом избыточности.

После такого процесса замены (переключения соединения между линией данных и схемой I/O) выполняется перенос данных в блок доступа к столбцам (массив ячеек памяти) (этап ST7).

Когда команда CMD является командой считывания, данные только из основной области 101 или данные из основной области 101 и области 109 избыточности передаются в контроллер 9 памяти через схему 16 I/O в зависимости от того, соответствуют ли адрес столбца и данные избыточности.

Когда команда CMD является командой записи RC, внешние данные переносятся из схемы 16 I/O только в основную область 101 или в основную область 101 и область 109 избыточности в зависимости от того, соответствуют ли адрес столбца и данные избыточности.

В отношении одной команды активации CMD-ACT и одного адреса строки ADR-Row, множество команд считывания/записи и множество адресов столбцов ADR-Col подаются последовательно. Таким образом, переносится одна страница данных.

Вышеописанная операция завершает перенос данных между памятью с изменяемым сопротивлением и контроллером памяти.

В способе управления памятью с изменяемым сопротивлением в настоящем варианте осуществления, когда принимаются команда и адрес строки, одна часть данных избыточности, соответствующая адресу строки, из множества данных избыточности в модуле перемычек избирательно переносится в схему-защелку в схеме управления избыточностью, как описано выше. Затем процесс определения и процесс замены дефектного столбца в массиве ячеек памяти выполняются с использованием данных избыточности, соответствующих выбранному адресу строки и выбранному адресу столбца.

(C) Сущность изобретения

Для устройств памяти, таких как устройства памяти с изменяемым сопротивлением, стимулируется миниатюризация элементов (ячеек памяти) и увеличение плотности хранения. Для обеспечения высокого выхода годных изделий для устройств памяти, в устройствах памяти использовалось восстановление дефектов с использованием функции избыточности.

Однако, при увеличенной плотности хранения и миниатюризированных ячейках памяти, процент дефектов в устройстве памяти имеет тенденцию к увеличению. Таким образом, масштаб схемы для функции избыточности увеличивается, и, следовательно, скорость схемы для функции избыточности в устройстве памяти (чипе) не может не приниматься в расчет.

Кроме того, если устройство памяти, при включении питания в устройстве памяти, переносит данные избыточности, хранящиеся в схеме перемычек, в схему управления избыточностью, схема-защелка в схеме управления избыточностью сохраняет все данные избыточности в схеме перемычек и выполняет процесс замены. В этом случае схема управления избыточностью включает в себя схему-защелку с большой емкостью хранения, и масштаб (площадь в чипе памяти) схемы-защелки может увеличиться.

Более того, когда количество элементов избыточности увеличивается для улучшения скорости восстановления для дефектных ячеек, емкость хранения схемы перемычек имеет тенденцию к увеличению. Следовательно, в устройстве памяти масштаб схемы-защелки в схеме управления избыточностью имеет тенденцию к увеличению в соответствии с улучшением скорости восстановления для дефектных ячеек.

На основе адреса (например, адреса строки), подаваемого вместе с командой, память с изменяемым сопротивлением в настоящем варианте осуществления считывает данные избыточности, соответствующие указанному адресу, из множества данных избыточности (данных об адресах дефектных столбцов) в схему перемычек.

Считанные данные избыточности удерживаются схемой-защелкой перемычек в схеме управления избыточностью.

Память с изменяемым сопротивлением в настоящем варианте осуществления сравнивает данные избыточности, считанные на основе выбранного адреса строки, с выбранным адресом столбца, поданным после подачи выбранного адреса строки.

На основе результата сравнения для данных избыточности и адреса столбца, память с изменяемым сопротивлением в настоящем варианте осуществления определяет, следует ли выполнять процесс замены с использованием столбца избыточности (следует ли осуществлять доступ к столбцу избыточности).

Когда считывание данных избыточности из схемы перемычек выполняется в момент времени, когда запускается доступ к массиву ячеек памяти, как в настоящем варианте осуществления, данные избыточности, соответствующие целевому блоку (строке) управления доступом, могут быть исключительно перенесены в схему-защелку перемычек.

Таким образом, память с изменяемым сопротивлением в настоящем варианте осуществления позволяет уменьшить размер данных избыточности (адрес дефекта), удерживаемых схемой-защелкой 151 перемычек во время процесса замены. Следовательно, память с изменяемым сопротивлением в настоящем варианте осуществления позволяет уменьшить масштаб схемы для схемы-защелки 151 перемычек.

Например, в DRAM, существует короткий период от приема адреса строки (команды активации) до приема адреса столбца (команды считывания/записи) для достижения высокоскоростного доступа на основе спецификации для DRAM. Таким образом, DRAM испытывает трудности с обеспечением количества времени для считывания и переноса данных избыточности в схеме перемычек в течение периода от приема адреса строки до приема адреса столбца.

Память с изменяемым сопротивлением обычно имеет меньший размер страницы, чем DRAM. Например, MRAM обычно имеют больший размер усилителя считывания, чем DRAM. Следовательно, для определенной области (размера чипа) количество битовых линий обычно мало, и, кроме того, размер страницы обычно мал. Таким образом, память с изменяемым сопротивлением имеет больше адресов строк, чем DRAM, чтобы соответствовать емкости хранения на основе спецификации памяти. Увеличение числа адресов строк приводит к уменьшению числа адресов столбцов. Таким образом, память с изменяемым сопротивлением имеет уменьшенный объем информации для избыточности столбцов.

Структура ячейки памяти в памяти с изменяемым сопротивлением (например, MRAM) отличается от структуры ячейки памяти в DRAM. Кроме того, механизм считывания (конфигурация и управление схемой) памяти с изменяемым сопротивлением отличается от механизма считывания DRAM. Такие различия между памятью с изменяемым сопротивлением и DRAM могут обусловить увеличение времени управления для строк в массиве ячеек памяти в памяти с изменяемым сопротивлением.

Следовательно, память с изменяемым сопротивлением в настоящем варианте осуществления обеспечивает то, что время переноса данных перемычек (данных избыточности) в схему управления избыточностью гарантируется в течение периода от приема адреса строки до приема адреса столбца.

В результате, память с изменяемым сопротивлением в настоящем варианте осуществления обеспечивает выполнение переноса данных избыточности из схемы перемычек в схему управления избыточностью (схему-защелку перемычек) во время управления для строк в массиве ячеек памяти.

Память с изменяемым сопротивлением в настоящем варианте осуществления позволяет уменьшить количество схем-защелок для удерживания информации избыточности.

В результате устройство памяти в настоящем варианте осуществления позволяет достичь высокого выхода годных изделий и позволяет уменьшить размер чипа.

(2) Второй вариант осуществления

Устройство памяти и способ управления им будут описаны со ссылкой на фиг. 10 и фиг. 11.

Память с изменяемым сопротивлением в качестве устройства памяти в настоящем варианте осуществления отличается от памяти с изменяемым сопротивлением в первом варианте осуществления тем, что как адрес строки, так и адрес столбца используются для избирательного считывания данных избыточности, соответствующих адресам строки и столбца, из схемы перемычек в течение периода доступа к массиву ячеек памяти.

На фиг. 10 показана временная диаграмма, иллюстрирующая пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления. На фиг. 11 показано схематичное представление, иллюстрирующее пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления. Внутренняя конфигурация памяти с изменяемым сопротивлением в настоящем варианте осуществления по существу такая же, как внутренняя конфигурация памяти с изменяемым сопротивлением в первом варианте осуществления, и, таким образом, конкретное описание внутренней конфигурации памяти опущено.

Режимы работы (режимы доступа) памяти с изменяемым сопротивлением включают в себя режим, в котором адрес строки и адрес столбца выдаются по существу в одно и то же время.

Как описано выше, память 1 с изменяемым сопротивлением имеет больший адрес строки, чем DRAM. В результате, много битов используется для указания адреса строки. Кроме того, количество контактных площадок, используемых для передачи и приема команд и адресов, может быть определено на основе спецификации или стандарта для памяти. Таким образом, когда команда и адрес передаются из контроллера 9 памяти в память 1 одновременно, не все биты, указывающие на выбранный адрес строки, могут быть переданы или приняты одновременно. В этом случае контроллер 9 памяти передает адрес строки в память 1 с изменяемым сопротивлением во множестве разделенных фрагментов.

Кроме того, память 1 с изменяемым сопротивлением и контроллер памяти имеют больший адрес строки, чем DRAM, ввиду емкости хранения, основанной на спецификации/стандарте для памяти, но имеет меньший адрес столбца, чем DRAM. Следовательно, память с изменяемым сопротивлением и контроллер памяти используют несколько контактных площадок на основе спецификации для памяти, чтобы позволять передавать часть адреса строки одновременно с адресом столбца.

На основе такого режима работы и спецификации, память с изменяемым сопротивлением в настоящем варианте осуществления работает следующим образом.

Как показано на фиг. 10, в настоящем варианте осуществления, две разные команды CMD последовательно передаются и принимаются.

Из двух последовательных команд, одна команда CMD является командой активации CMD-ACT. Другая команда является командой считывания CMD-RC или командой записи CMD-WC. В настоящем варианте осуществления, последовательные команды указывают, что, во время логической обработки, выполняемой по одной команде (команде активации в настоящем примере), другая команда (команда считывания/записи в настоящем примере) передается и принимается.

Память 1 принимает команду активации CMD-ACT, а также принимает часть ADR-R1 выбранного адреса строки ADR-Row.

Память 1 принимает команду считывания CMD-RC (или команду записи CMD-WC), а также принимает оставшуюся часть ADR-R2 выбранного адреса строки ADR-Row и выбранного адреса столбца ADR-Col. Команда считывания CMD-RC и адреса ADR-R2, ADR-Col принимаются во время логической обработки LGC, выполняемой по команде активации CMD-ACT.

Выбранные адреса строки и столбца ADR-Row, ADR-Col переносятся в схему 142 управления перемычками.

Схема 142 управления перемычками выполняет операцию считывания FDR на данных FD избыточности на основе выбранных адресов ADR-Row, ADR-Col (всех или части адреса).

Как описано выше, данные FD избыточности, соответствующие блоку доступа к строкам, включает в себя множество блоков данных DU, соответствующих блокам доступа к столбцам.

Как показано на фиг. 11, один блок данных DU из множества блоков данных DU в выбранных данных FD избыточности выбирается на основе выбранного адреса столбца ADR-Col.

Таким образом, данные избыточности (блоки данных в данных избыточности), соответствующие как выбранному адресу строки ADR-Row, так и выбранному адресу столбца ADR-Col, считываются из модуля 141 перемычек.

Схема 142 управления перемычками выполняет операцию переноса TRS для переноса считанных данных FD избыточности в схему-защелку 151 перемычек в схеме 15 управления избыточностью.

Как показано на фиг. 11, в настоящем варианте осуществления, данные FD избыточности переносятся только в блок-защелку 51 для блока доступа к столбцам, соответствующего выбранному адресу столбца.

Блок 52 определения сравнивает данные избыточности (блок данных) в блоке-защелке 51 с выбранным адресом столбца ADR-Col, чтобы определить, следует ли выполнять процесс замены с использованием столбца ZR избыточности.

Блоки-защелки/блоки определения, не удерживающие данных избыточности, соответствуют невыбранным блокам доступа к столбцам. Следовательно, переключатель замены управляется таким образом, чтобы разрешить перенос данных основной области 101 в блоки-защелки/блоки определения, не удерживающие данных избыточности.

Затем, память с изменяемым сопротивлением в настоящем варианте осуществления выполняет перенос данных между массивом 10 ячеек памяти и схемой 16 I/O на основе результата процесса определения, как это имеет место в первом варианте осуществления.

Как описано выше, даже когда память с изменяемым сопротивлением последовательно принимает команду/адрес, данные избыточности для процесса замены могут быть перенесены из схемы 14 перемычек в схему-защелку 151 в течение периода доступа к массиву 10 ячеек памяти (до переноса данных в массив ячеек памяти).

Следовательно, устройство памяти во втором варианте осуществления создает эффекты, аналогичные эффектам первого варианта осуществления.

(3) Третий вариант осуществления

Устройство памяти в третьем варианте осуществления будет описано со ссылкой на фиг. 12-14.

Фиг. 12 является схематичным представлением, изображающим внутреннюю конфигурацию и пример работы памяти с изменяемым сопротивлением в качестве устройства памяти в настоящем варианте осуществления. Фиг. 13 является временной диаграммой, иллюстрирующей пример работы памяти с изменяемым сопротивлением в настоящем варианте осуществления.

Как показано на фиг. 12, когда данные избыточности в схеме-защелке перемычек считываются с использованием как выбранного адреса строки, так и выбранного адреса столбца, как в случае памяти с изменяемым сопротивлением во втором варианте осуществления, схема-защелка перемычек может удерживать адреса (данные перемычек) для одного блока доступа к столбцам.

В памяти 1 с изменяемым сопротивлением в настоящем варианте осуществления, схема-защелка 151X в схеме управления избыточностью имеет емкость хранения, которая позволяет удерживать данные (данные избыточности) с битовой длиной, указывающей один блок доступа к столбцам. Например, схема-защелка 151X перемычек включает в себя один блок-защелку 51, который может удерживать адреса для одного блока доступа к столбцам.

Управляющий сигнал Trg подается в блок-защелку (схему-защелку 151X перемычек).

Как описано выше, память с изменяемым сопротивлением в настоящем варианте осуществления использует выбранный адрес строки и выбранный адрес столбца для считывания данных перемычки (адрес дефекта в выбранном блоке доступа к столбцам), что позволяет дополнительно уменьшить масштаб схемы для схемы-защелки, временно удерживающей данные избыточности.

Когда обеспечен один блок-защелка 51, один блок 52 определения может быть обеспечен в схеме 152 определения замены.

Например, когда данные FD избыточности удерживаются блоком-защелкой 51, соответствующим блоку доступа к столбцам, как показано на фиг. 13, время извлечения для данных D избыточности в схеме-защелке 151X перемычек контролируется управляющим сигналом (далее упоминаемым как сигнал запуска защелки) Trg.

Например, блок-защелка 51 извлекает данные FD избыточности синхронно с временем, когда сигнал Trg запуска защелки переходит от уровня L к уровню H.

В течение периода T1 от начала извлечения данных FD избыточности в определенном цикле до тех пор, пока сигнал Trg запуска защелки в следующем цикле не перейдет с уровня L на уровень H, данные в блоке-защелке 51 находятся в действительном состоянии.

Перенос данных между блоком CU доступа к столбцам (основным столбцом/столбцом избыточности) и схемой 16 I/O выполняется в течение периода, когда данные FD избыточности, используемые для определения замены для переноса данных, находятся в действительном состоянии.

Как описано выше, для процесса замены для определенных данных избыточности, период переноса данных в массиве ячеек памяти не превышает период, пока данные избыточности действительны.

Например, процесс определения для данных FD избыточности и выбранного адреса столбца выполняется в течение периода, когда сигнал Trg запуска защелки находится на уровне H.

Таким образом, память с изменяемым сопротивлением в настоящем варианте осуществления может препятствовать перезаписи данных избыточности в блоке-защелке 51 во время процесса определения.

Фиг. 14 является схемой, изображающей модификацию памяти с изменяемым сопротивлением в настоящем варианте осуществления.

Когда обеспечены один блок-защелка 51 и один блок 52 определения, один блок 59 переключателей может быть обеспечен в схеме 159 переключателей, как показано на фиг. 14.

Даже когда, подобно блоку-защелке 51 и блоку 52 определения, обеспечен один блок 59 переключателей, память 1 с изменяемым сопротивлением позволяет реализовать определение избыточности и управление соединением с областью избыточности посредством операции, показанной на фиг. 13.

Следовательно, память в третьем варианте осуществления может создавать эффекты, подобные эффектам первого и второго вариантов осуществления.

(4) Модификация

Модификация устройства памяти (например, памяти с изменяемым сопротивлением) в вариантах осуществления будет описана со ссылкой на фиг. 15 и фиг. 16.

На фиг. 15 показана схема, иллюстрирующая модификацию памяти с изменяемым сопротивлением в вариантах осуществления.

Например, чтобы восстановить множество дефектов, которые не могут быть восстановлены с использованием одного блока восстановления, может быть предусмотрено множество столбцов ZR избыточности в одном блоке CU доступа к столбцам, как показано на фиг. 15.

В этом случае схема-защелка 151 перемычек включает в себя множество блоков-защелок 51 (51a, 51b) для одного блока CU доступа к столбцам.

Каждый блок-защелка 51 удерживает множество различных данных FDa, FDb (блок данных DU) избыточности в блоке доступа к столбцам. Различные данные FDа, FDb избыточности указывают разные адреса дефектов в блоке CU доступа к столбцам. Однако два фрагмента данных FDa, FDb избыточности представляют собой данные FDa, FDb избыточности столбцов, соответствующие общему выбранному адресу строки ADR-Row.

Когда два столбца избыточности (блока восстановления) обеспечены для одного блока CU доступа к столбцам, два блока-защелки 51 предусмотрены в ассоциации с одним блоком доступа к столбцам.

Блок-защелка 51 может удерживать данные избыточности (блок данных DU), избирательно считываемые на основе выбранного адреса строки и столбца ADR-Row и ADR-Col.

Схема 152 определения замены включает в себя множество блоков 52 (52a, 52b) определения для одного блока CU доступа к столбцам. Один блок 52 определения (52а, 52b) соответствует одному блоку-защелке 51 (51а, 51b).

Один блок 52 определения сравнивает одну часть данных FD избыточности с выбранным адресом столбца ADR-Col. Например, каждый отдельный блок 52a определения сравнивает одну часть данных FDa избыточности с выбранным адресом столбца ADR-Col для целевого блока восстановления. Каждый другой блок 52b определения сравнивает другую часть данных FDb избыточности с выбранным адресом столбца ADR-Col для целевого блока восстановления.

Схема 159 переключателей замены включает в себя множество переключателей 591 в блоке 59 переключателей.

Один переключатель 591 соединен с множеством блоков 52a, 52b определения, которые выполняют логическую обработку LGC на различных данных избыточности (части данных).

На один переключатель 591 подается множество результатов определения.

На основе управляющих сигналов dRDa, dRDb из блоков 52a, 52b определения, переключатель 591 соединяет схему 16 I/O с одним из основного столбца ZC и столбца ZR избыточности.

На основе двух различных управляющих сигналов (результатов определения для адреса), переключатель 591 соединяет одну из основной линии ML данных и линий RLa, RLb данных избыточности со схемой 16 I/O.

Например, когда уровнем сигнала для управляющего сигнала dRDa является уровень H, а уровнем сигнала для управляющего сигнала dRDb является уровень L, переключатель 591 соединяет линию RLa данных избыточности (столбец ZRa избыточности), включенную в две линии RLa, RLb данных избыточности, со схемой 16 I/O. Когда уровнем сигнала для управляющего сигнала dRDa является уровень L, а уровнем сигнала для управляющего сигнала dRDb является уровень H, переключатель 591 соединяет линию RLb данных избыточности (столбец ZRb избыточности) со схемой 16 I/O.

Когда оба управляющих сигнала dRDa, dRDb находятся на уровне L, переключатель 591 соединяет основную линию ML данных (основной столбец ZC) со схемой 16 I/O. Схема 152 определения замены предусмотрена для предотвращения установки обоих управляющих сигналов dRDa, dRDb на уровень H.

Как описано выше, память с изменяемым сопротивлением в настоящей модификации позволяет выполнить процесс замены множества дефектных столбцов в одном блоке доступа к столбцам на столбцы избыточности.

По меньшей мере три дефекта в блоке CU доступа к столбцам могут быть восстановлены на основании по меньшей мере трех данных избыточности.

Память с изменяемым сопротивлением в модификации, изображенной на фиг. 15, позволяет увеличить скорость восстановления дефектов в блоке доступа к столбцам.

Фиг. 16 является схемой, иллюстрирующей модификацию устройств памяти с изменяемым сопротивлением в вариантах осуществления.

Как показано на фиг. 16, например, блок CU доступа к столбцам может рассматриваться как блок восстановления.

В этом случае блок CU доступа к столбцам, включающий в себя дефектный столбец, заменяется столбцом ZR избыточности, имеющим ту же емкость хранения, что и емкость одного блока CU доступа к столбцам.

Схема 159 переключателей замены имеет множество переключателей 591.

Один переключатель 591 соответствует набору из одного блока CU доступа к столбцам и одного столбца ZR избыточности.

Кроме того, схема 152 определения замены содержит множество арифметических схем 521. Одна арифметическая схема 521 соответствует одному переключателю 591.

Схема-защелка 151 перемычек удерживает данные FD избыточности, избирательно считываемые на основе выбранного адреса строки ADR-Row, как это имеет место в первом варианте осуществления. Схема-защелка 151 перемычек может удерживать данные FD избыточности, избирательно считываемые на основе выбранных адресов строк и столбцов ADR-Row, ADR-Col.

На основе результата определения (результата сравнения для выбранного адреса столбца и данных избыточности) для процесса замены, выполняемого арифметической схемой 521, каждый переключатель 591 соединяет один из блоков CU доступа к столбцам и столбца ZR избыточности со схемой 16 I/O.

Когда выбранный адрес столбца ADR-Col является адресом дефекта, указанным данными FD перемычки, весь блок CU доступа к столбцам, соответствующий выбранному адресу столбца ADR-Col, заменяется столбцом ZR избыточности.

Как описано выше, память с изменяемым сопротивлением в настоящей модификации может выполнять процесс замены всего блока доступа к столбцам на столбец ZR избыточности.

Память с изменяемым сопротивлением, изображенная на фиг. 16, позволяет восстанавливать дефекты в массиве ячеек памяти, к которым применяется механизм избыточности столбцов, используя относительно простую конфигурацию схемы и управление.

Хотя были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений. Действительно, описанные здесь новые способы и системы могут быть воплощены во множестве других форм; кроме того, различные пропуски, замены и изменения в форме описанных здесь способов и систем могут быть сделаны без отклонения от сущности изобретений. Прилагаемые пункты формулы изобретения и их эквиваленты предназначены для охвата таких форм или модификаций, которые находятся в пределах объема и сущности изобретений.

Изобретение относится к устройствам памяти. Технический результат заключается в расширении арсенала средств того же назначения. Устройство памяти включает массив ячеек памяти, схему перемычек, схему управления, при этом когда подается первый адрес в первом направлении в первом массиве, схема перемычек переносит первые данные, соответствующие первому адресу, в схему управления, и когда подается второй адрес во втором направлении в первом массиве после того, как первые данные перенесены в схему управления, схема управления осуществляет доступ к одному из первого и второго массивов на основе результата сравнения для второго адреса и первых данных. 3 н. и 17 з.п. ф-лы, 16 ил.

1. Устройство памяти, содержащее:

массив ячеек памяти, включающий в себя первый массив и второй массив;

схему перемычек, выполненную с возможностью удерживать по меньшей мере одну часть первых данных, причем первые данные указывают адрес дефекта в первом массиве; и

схему управления, выполненную с возможностью управлять процессом замены на первом и втором массивах на основе первых данных,

при этом

когда подается первый адрес в первом направлении в первом массиве, схема перемычек переносит первые данные, соответствующие первому адресу, в схему управления, и

когда подается второй адрес во втором направлении в первом массиве после того, как первые данные перенесены в схему управления, схема управления осуществляет доступ к одному из первого и второго массивов на основе результата сравнения для второго адреса и первых данных.

2. Устройство памяти по п. 1, в котором

схема управления осуществляет доступ ко второму массиву, когда адрес дефекта соответствует второму адресу.

3. Устройство памяти по п. 1, в котором

схема управления осуществляет доступ к части в первом массиве, которая указана первым и вторым адресами, когда адрес дефекта не соответствует второму адресу.

4. Устройство памяти по п. 1, в котором

первый адрес подается с первой командой, и

первая команда представляет собой сигнал, который позволяет активировать первый набор блоков для первого направления в массиве ячеек памяти.

5. Устройство памяти по п. 1, в котором

второй адрес подается с второй командой и

вторая команда представляет собой сигнал, который позволяет выполнять считывание вторых данных из массива ячеек памяти или запись третьих данных в массив ячеек памяти.

6. Устройство памяти по п. 1, в котором

схема перемычек включает в себя массив перемычек, который хранит по меньшей мере одну часть первых данных,

схема управления включает в себя схему-защелку, которая удерживает первые данные, перенесенные из массива перемычек, и

емкость хранения схемы-защелки меньше, чем емкость хранения массива перемычек.

7. Устройство памяти по п. 1, в котором

первый массив включает в себя:

первое количество первых блоков управления, установленных для первого направления; и

второе количество вторых блоков управления, установленных для второго направления,

схема управления включает в себя схему-защелку, которая удерживает первые данные, и

схема-защелка включает в себя второе количество первых блоков-защелок.

8. Устройство памяти по п. 1, в котором

первый адрес представляет собой адрес строки в массиве ячеек памяти и

второй адрес представляет собой адрес столбца в массиве ячеек памяти.

9. Устройство памяти по п. 1, в котором

первый массив включает в себя ячейку памяти и

ячейка памяти включает в себя элемент памяти, выбранный из группы, состоящей из магниторезистивного элемента, элемента с переменным сопротивлением металл-оксидного типа и элемента с изменяемым фазовым состоянием.

10. Устройство памяти, содержащее:

массив ячеек памяти с первым массивом и вторым массивом;

схему перемычек, выполненную с возможностью удерживать по меньшей мере одну часть первых данных, причем первые данные указывают адрес дефекта в первом массиве;

схему-защелку, выполненную с возможностью удерживать первые данные, переносимые из схемы перемычек; и

схему управления, выполненную с возможностью управлять процессом замены на первом и втором массивах с использованием первых данных в схеме-защелке,

при этом

емкость хранения схемы-защелки меньше, чем емкость хранения схемы перемычек.

11. Устройство памяти по п. 10, в котором,

когда подается первый адрес в первом направлении в первом массиве, схема перемычек переносит первые данные, соответствующие первому адресу, в схему-защелку,

когда подается второй адрес во втором направлении в первом массиве после того, как первые данные перенесены, схема управления осуществляет доступ к одному из первого и второго массивов на основе результата сравнения для второго адреса и первых данных.

12. Устройство памяти по п. 10, в котором

схема управления выбирает одну часть первых данных на основе первого адреса в первом направлении в первом массиве и выбирает один блок данных среди множества блоков данных в выбранной одной части первых данных на основе второго адреса во втором направлении в первом массиве,

схема управления переносит выбранный блок данных в схему-защелку, и

схема управления осуществляет доступ к одному из первого и второго массивов на основе результата сравнения для второго адреса и выбранного блока данных.

13. Устройство памяти по п. 10, в котором

первый массив включает в себя:

первое количество первых блоков управления, установленных для первого направления первого массива; и

второе количество вторых блоков управления, установленных для второго направления первого массива, и

схема-защелка включает в себя блок-защелку, соответствующий одному из вторых блоков управления.