Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения в общем относятся к беспроводной связи, а более конкретно к декодированию беспроводных передач.

Уровень техники

Быстрое развитие услуг беспроводной связи, таких как широкополосный доступ в Интернет и потоковые мультимедийные приложения, приводит к возрастающей потребности в более высоких скоростях передачи данных. Совершенствование схем мультиплексирования, таких как мультиплексирование с ортогональным частотным разделением каналов (OFDM) и множественный доступ с ортогональным частотным разделением каналов (OFDMA), является важным для систем беспроводной связи следующего поколения. Это обусловлено тем фактом, что такие схемы могут предоставлять множество преимуществ, в том числе эффективность модуляции, эффективность использования спектра, гибкость (к примеру, обеспечение дифференцированного качества обслуживания) и сильную устойчивость к многолучевому распространению по сравнению с традиционными схемами модуляции с одной несущей.

OFDM- и OFDMA-системы зачастую используют сверточные кодеры в передающем устройстве, чтобы предусматривать коррекцию ошибок. При помощи сверточного кода m-битовая строка данных преобразуется в n битов, где m/n - это кодовая скорость. Декодеры, такие как декодеры Витерби, используются в приемном устройстве, чтобы декодировать принимаемые кодированные n битов, чтобы восстанавливать исходную m-битовую последовательность. Эта схема зачастую обеспечивает возможность корректного декодирования исходной m-битовой последовательности, даже если один или более из кодированных n битов не приняты корректно, тем самым приводя к уменьшению частоты ошибок по битам.

Тем не менее, при постоянно растущих требованиях к надежности и производительности беспроводных услуг всегда имеется необходимость непрерывно уменьшать частоты ошибок по битам.

Сущность изобретения

Один вариант осуществления предоставляет способ декодирования кодированных битов данных передачи по системе беспроводной связи. Способ, в общем, включает в себя формирование нескольких гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи, оценку нескольких гипотез посредством выполнения декодирования кодированных битов данных, при этом декодирование заключает в себе исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, и выбор, в качестве вывода, декодированных битов, соответствующих одной из гипотез.

Один вариант осуществления предоставляет приемное устройство для беспроводной связи. Приемное устройство, в общем, включает в себя внешний приемный каскад для приема беспроводной передачи и формирования набора кодированных битов, механизм гипотез для формирования нескольких гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи, и декодер, выполненный с возможностью оценивать гипотезы посредством выполнения операций декодирования, которые заключают в себе исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, и выбор, в качестве вывода, декодированных битов, соответствующих одной из гипотез.

Один вариант осуществления предоставляет устройство для беспроводной связи. Устройство, в общем, включает в себя средство для приема беспроводной передачи и формирования набора кодированных битов, средство для формирования нескольких гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи, и средство для оценки гипотез посредством выполнения операций декодирования, которые заключают в себе исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, и выбор, в качестве вывода, декодированных битов, соответствующих одной из гипотез.

Краткое описание чертежей

В качестве способа, которым вышеизложенные признаки настоящего изобретения могут подробно пониматься, более подробное описание изобретения, сущность которого вкратце приведена выше, может предоставляться в отношении вариантов осуществления, некоторые из которых проиллюстрированы на прилагаемых чертежах. Тем не менее, следует отметить, что прилагаемые чертежи иллюстрируют только типичные варианты осуществления этого изобретения и, следовательно, не должны считаться ограничением его объема, и изобретение может признавать другие в равной мере эффективные варианты осуществления.

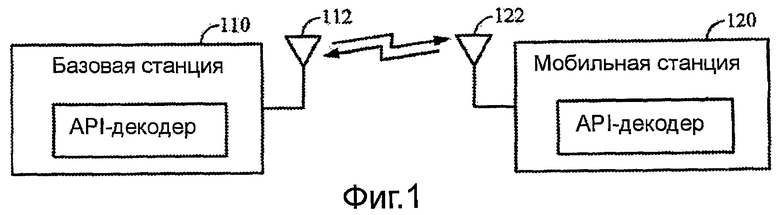

Фиг.1 иллюстрирует примерную систему в соответствии с вариантом осуществления настоящего изобретения.

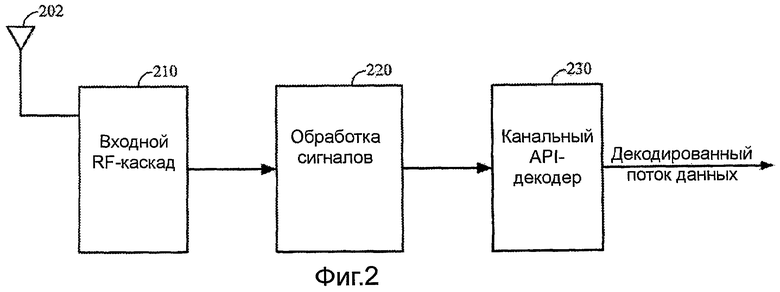

Фиг.2 является блок-схемой приемного устройства, допускающего априорное декодирование в соответствии с вариантом осуществления настоящего изобретения.

Фиг.3 является блок-схемой априорного декодера в соответствии с вариантом осуществления настоящего изобретения.

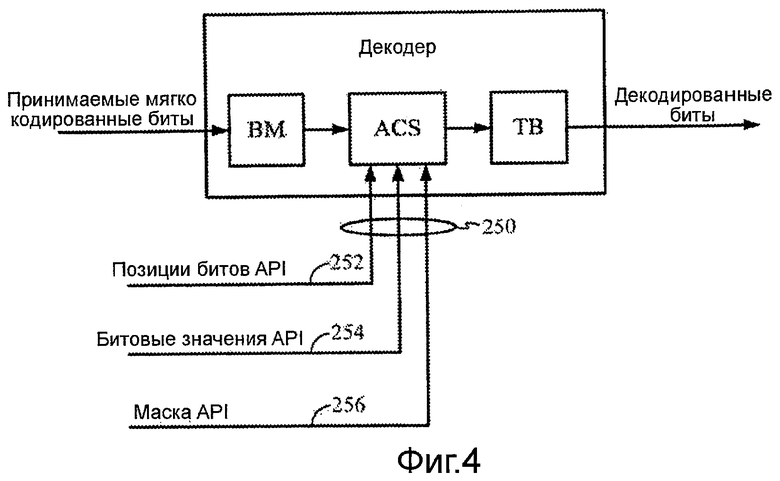

Фиг.4 является блок-схемой априорного декодера, иллюстрирующего пример битов априорной информации (API) в соответствии с вариантом осуществления настоящего изобретения.

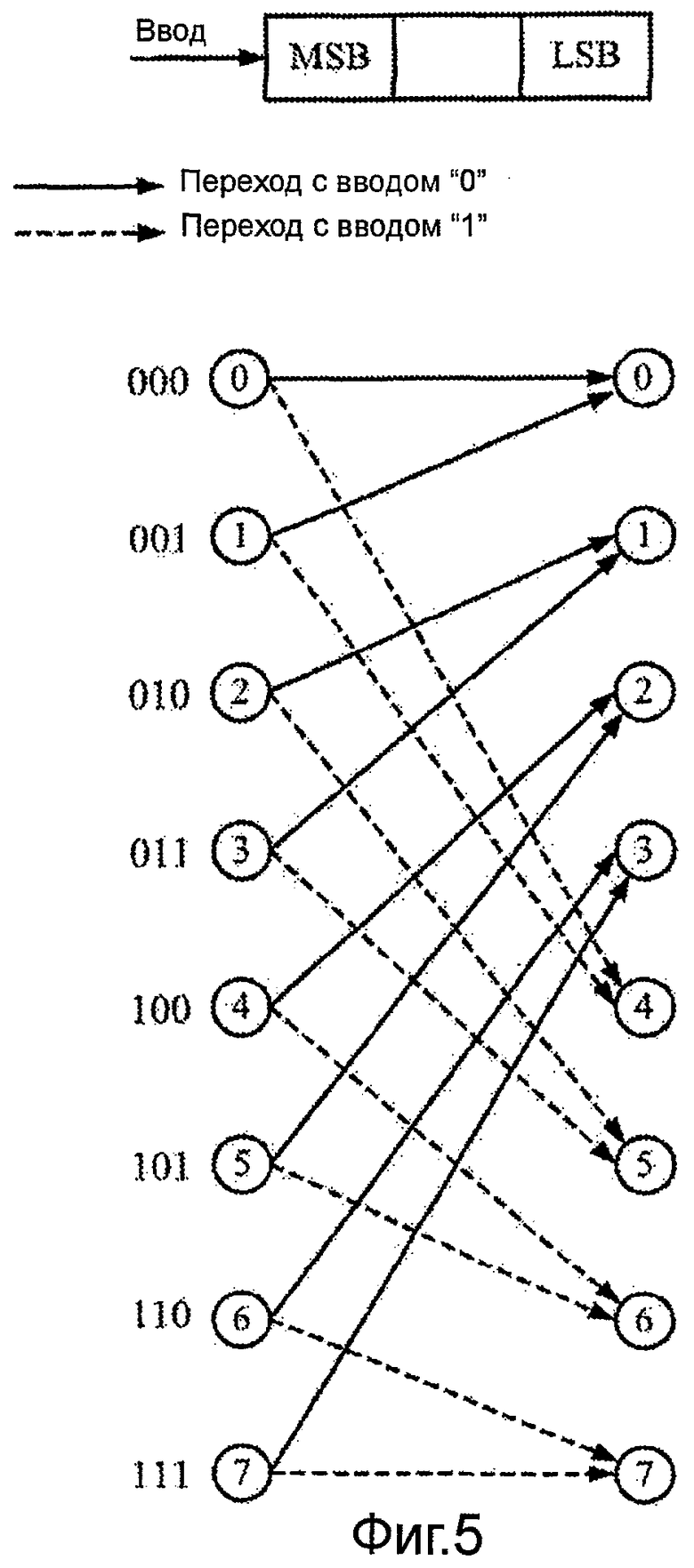

Фиг.5 иллюстрирует пример перехода состояния решетчатой схемы в соответствии с вариантом осуществления настоящего изобретения.

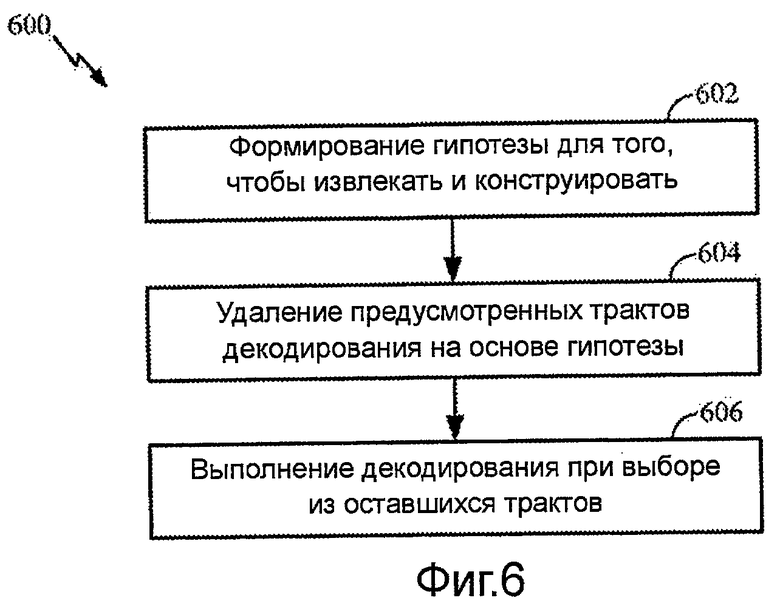

Фиг.6 является блок-схемой последовательности операций примерных операций для априорного декодирования в соответствии с вариантом осуществления настоящего изобретения.

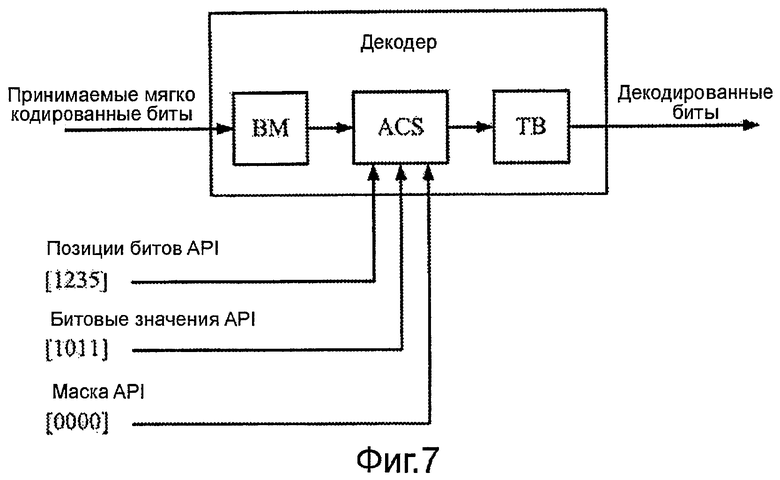

Фиг.7 иллюстрирует декодер по фиг.5 с примерными значениями битов априорной информации.

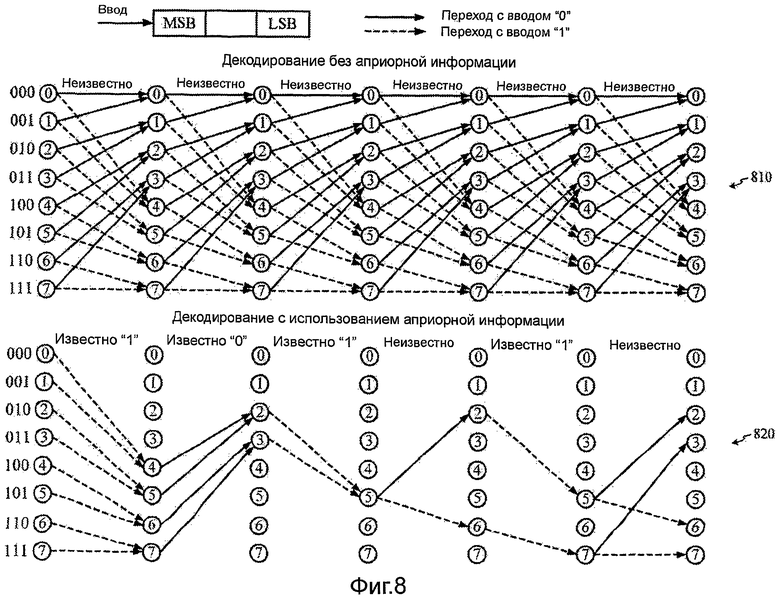

Фиг.8 иллюстрирует пример решетчатой схемы с полным набором трактов декодирования и набором трактов декодирования, который уменьшен на основе битов априорной информации, в соответствии с вариантом осуществления настоящего изобретения.

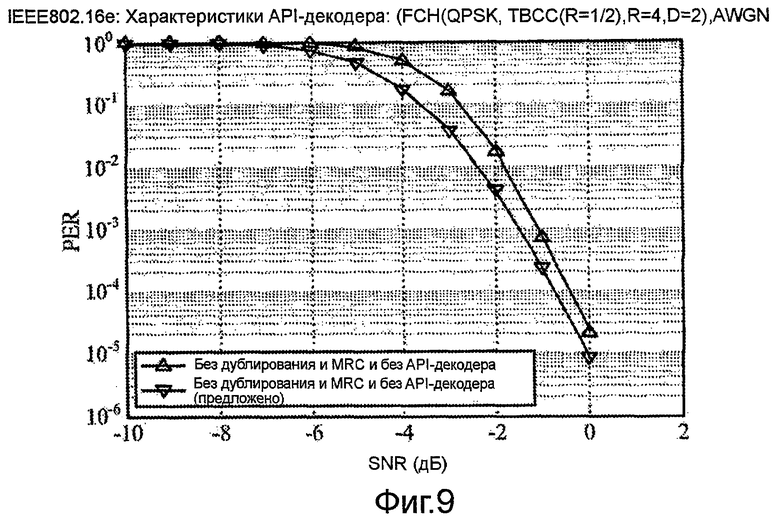

Фиг.9 иллюстрирует примерные результаты декодирования согласно первому набору априорной информации в соответствии с вариантом осуществления настоящего изобретения.

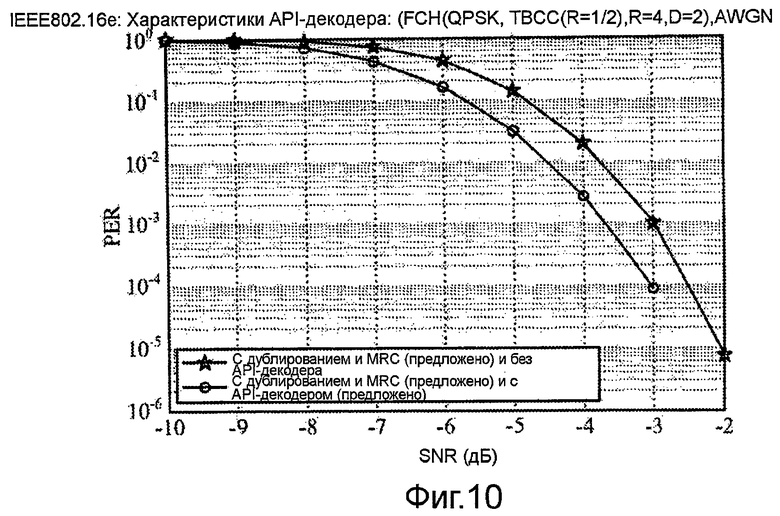

Фиг.10 иллюстрирует примерные результаты декодирования согласно первому набору априорной информации в соответствии с вариантом осуществления настоящего изобретения.

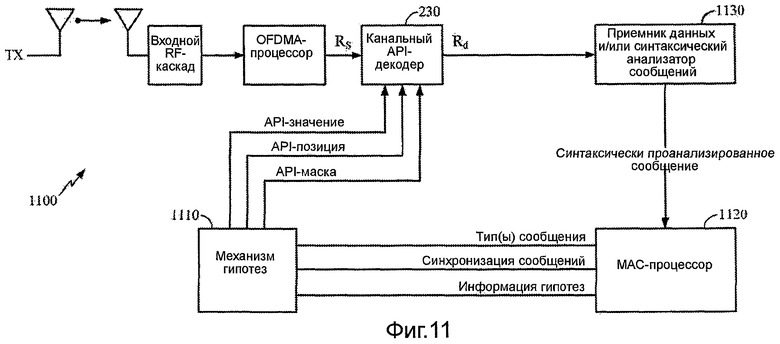

Фиг.11 является блок-схемой приемного устройства с априорным декодером и механизмом гипотез в соответствии с вариантом осуществления настоящего изобретения.

Фиг.12 является блок-схемой механизма гипотез в соответствии с вариантом осуществления настоящего изобретения.

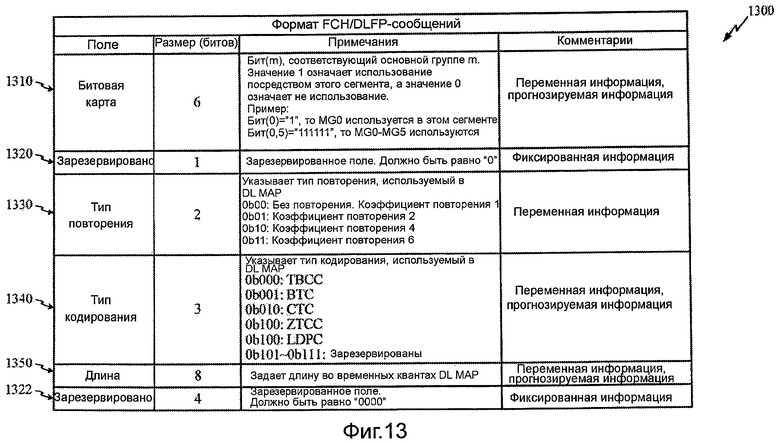

Фиг.13 иллюстрирует примерный формат сообщений, который может использоваться для того, чтобы формировать гипотезы декодирования на основе битов априорной информации.

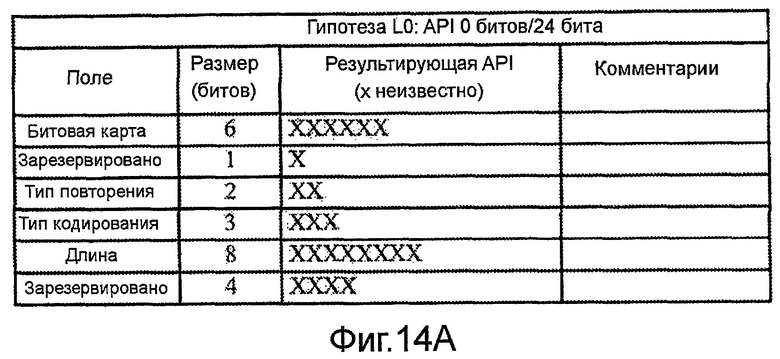

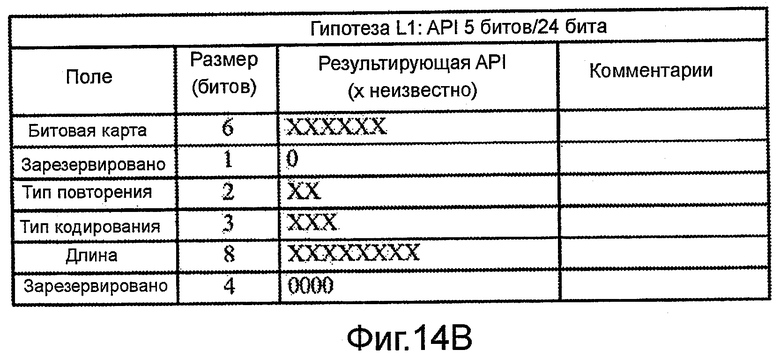

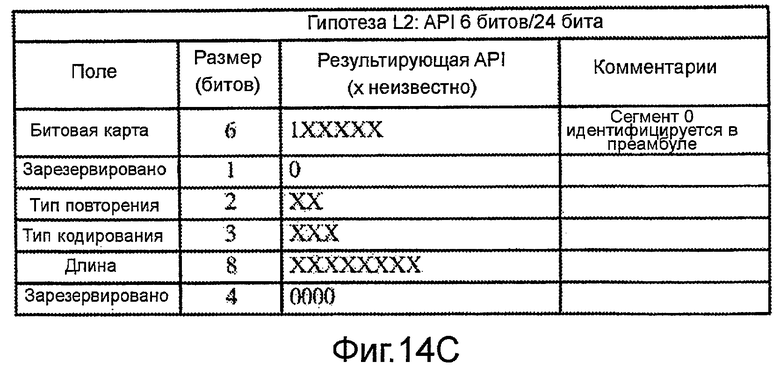

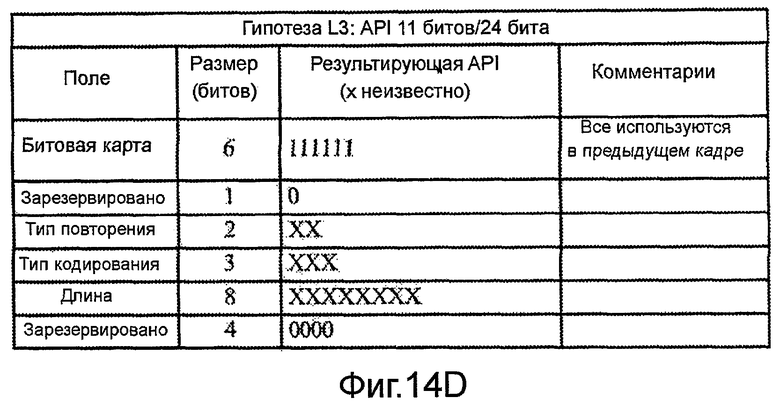

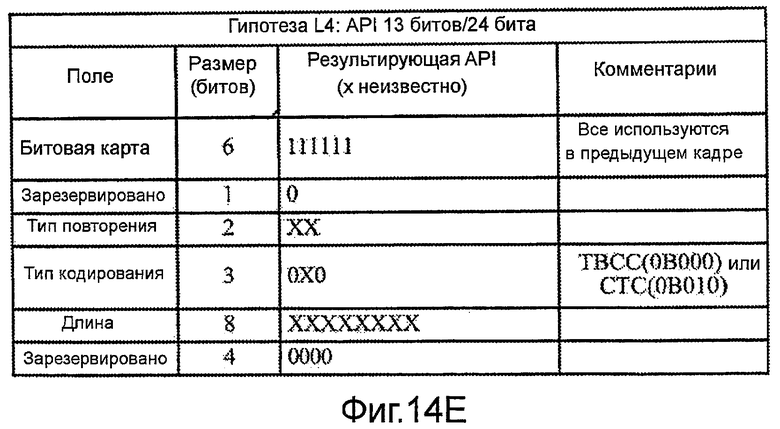

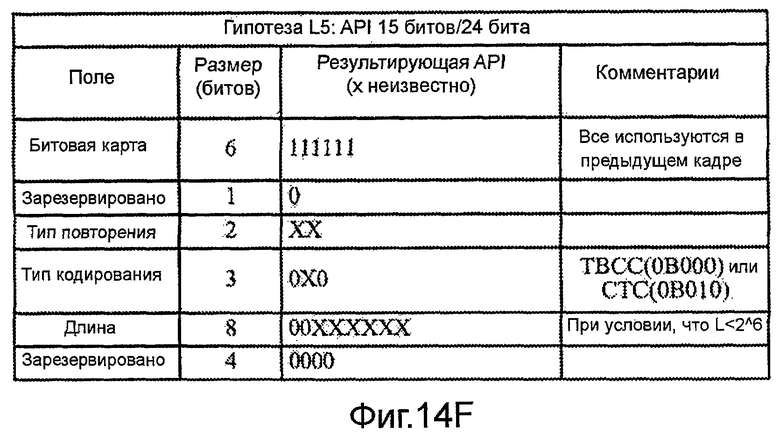

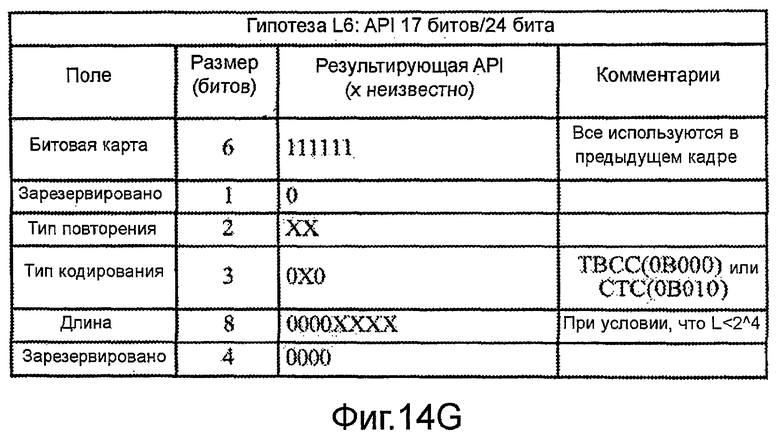

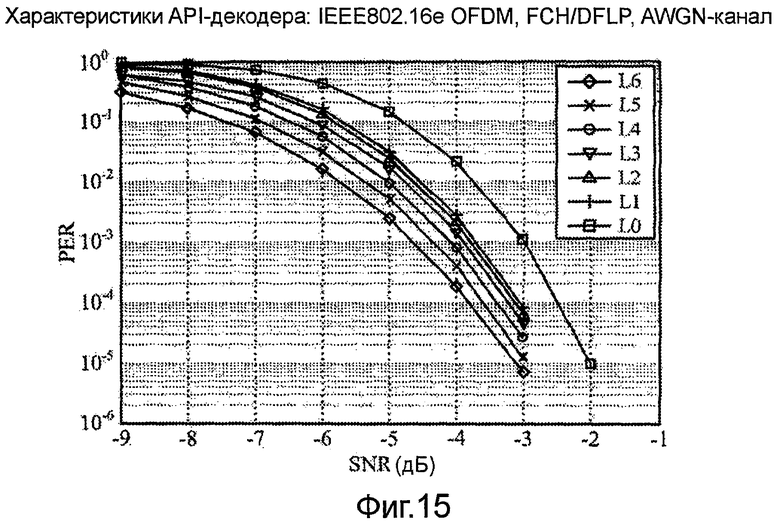

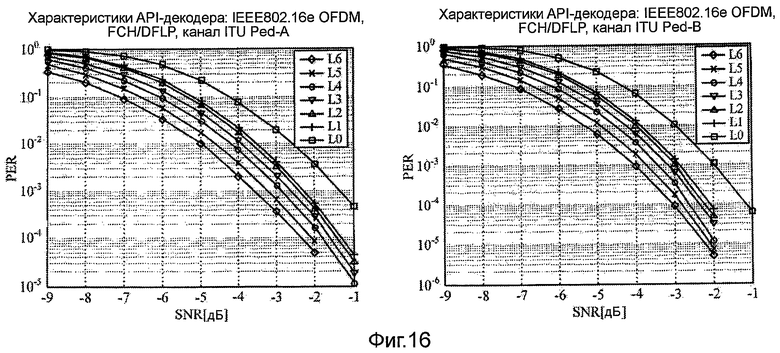

Фиг.14A-14G иллюстрируют различные гипотезы декодирования на основе битов априорной информации.

Фиг.15 иллюстрирует примерные результаты декодирования для различных API-гипотез в соответствии с вариантом осуществления настоящего изобретения.

Фиг.16 иллюстрирует примерные результаты декодирования для различных API-гипотез в соответствии с вариантом осуществления настоящего изобретения.

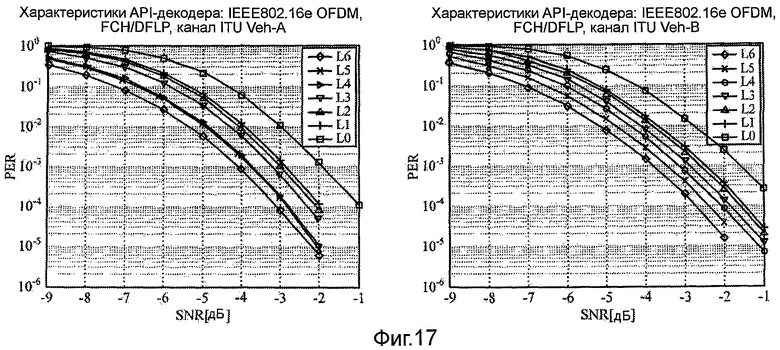

Фиг.17 иллюстрирует примерные результаты декодирования для различных API-гипотез в соответствии с вариантом осуществления настоящего изобретения.

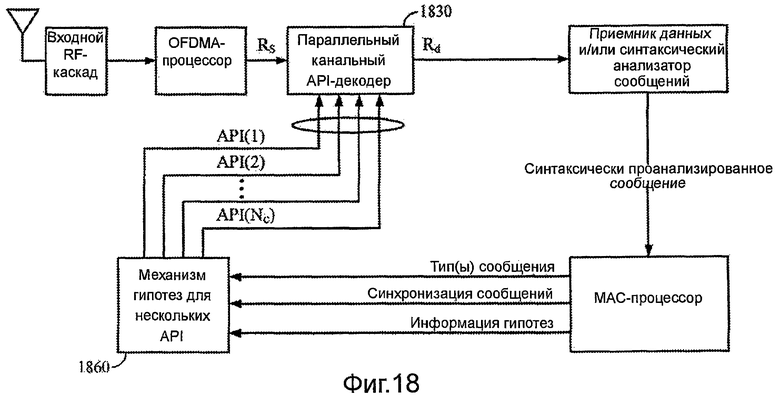

Фиг.18 иллюстрирует примерное приемное устройство, допускающее параллельную оценку нескольких гипотез декодирования.

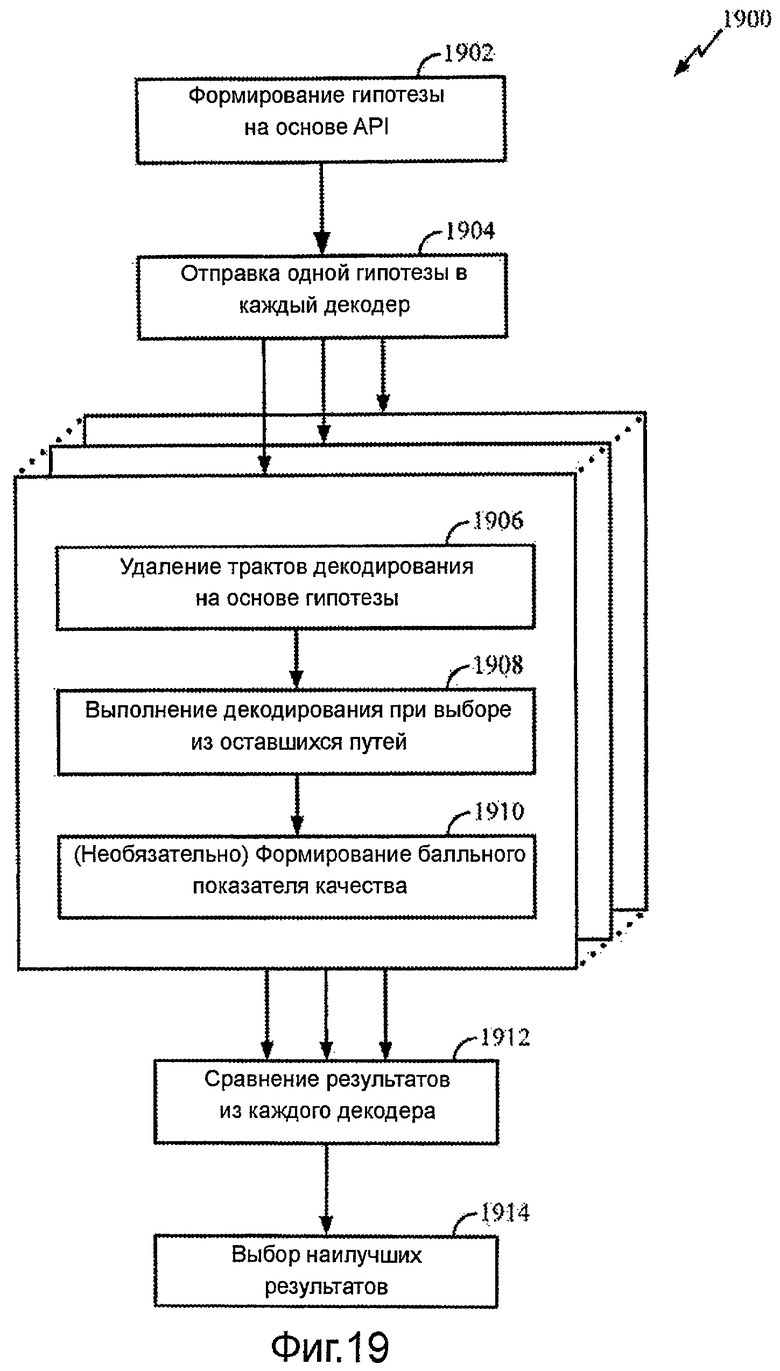

Фиг.19 иллюстрирует примерный процесс для параллельной оценки нескольких гипотез декодирования.

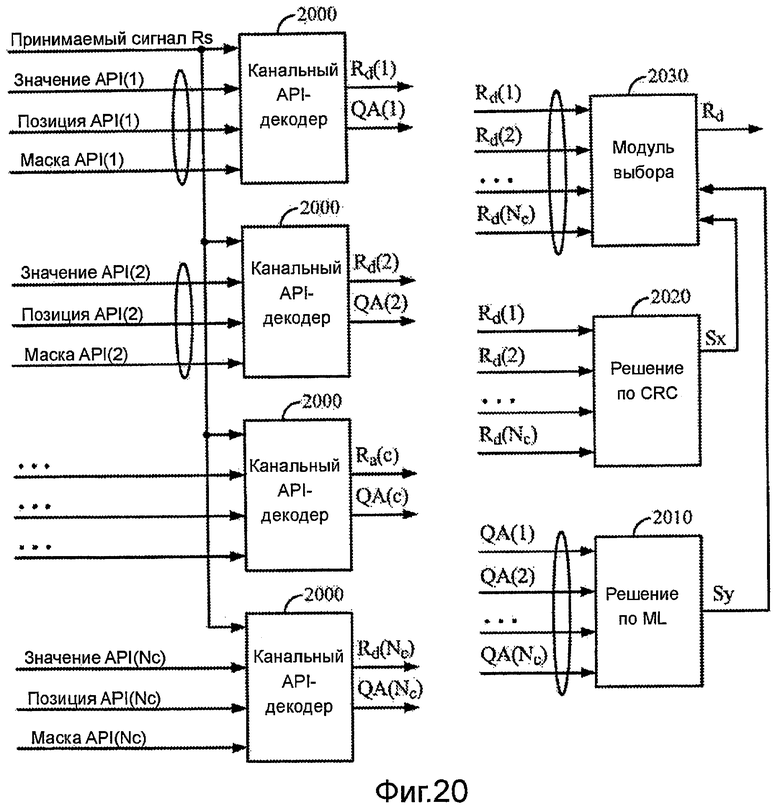

Фиг.20 иллюстрирует примерный декодер, допускающий параллельную оценку нескольких гипотез декодирования.

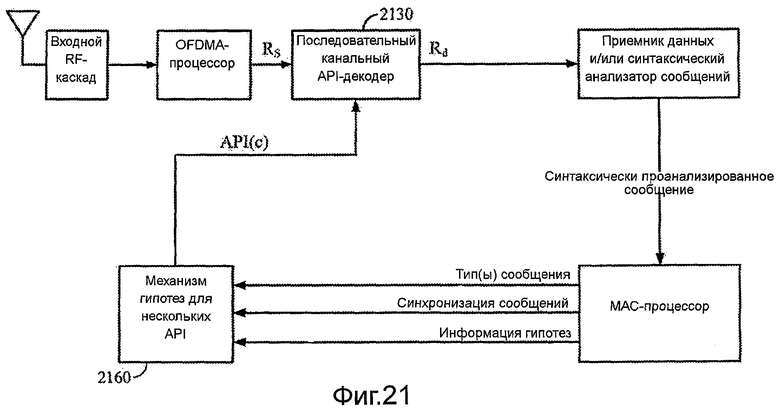

Фиг.21 иллюстрирует примерное приемное устройство, допускающее последовательную оценку нескольких гипотез декодирования.

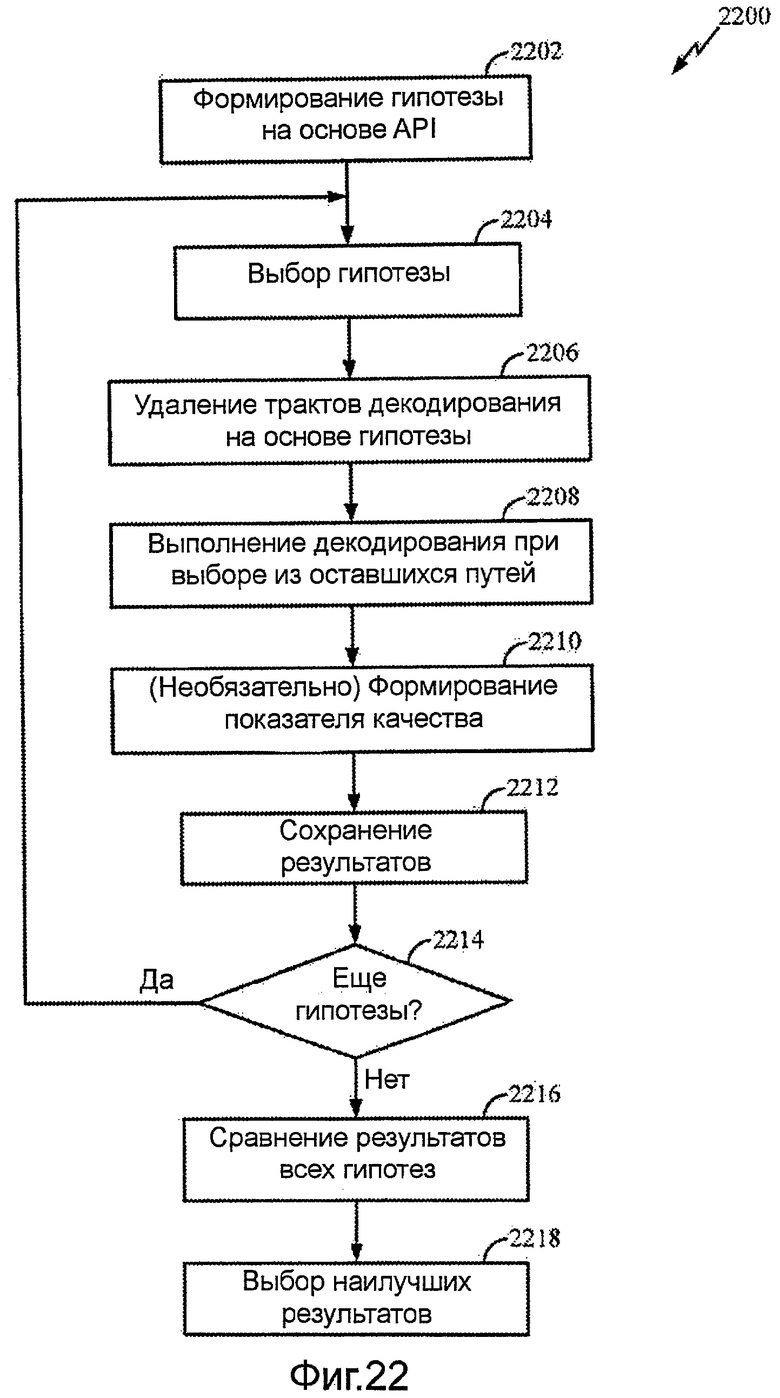

Фиг.22 иллюстрирует примерный процесс для последовательной оценки нескольких гипотез декодирования.

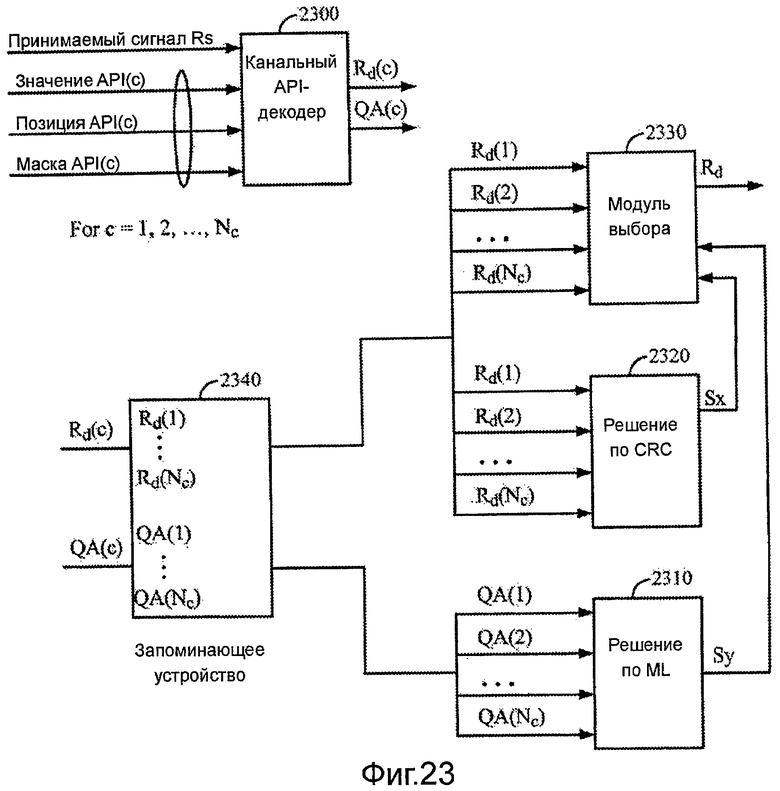

Фиг.23 иллюстрирует примерный декодер, допускающий последовательную оценку нескольких гипотез декодирования.

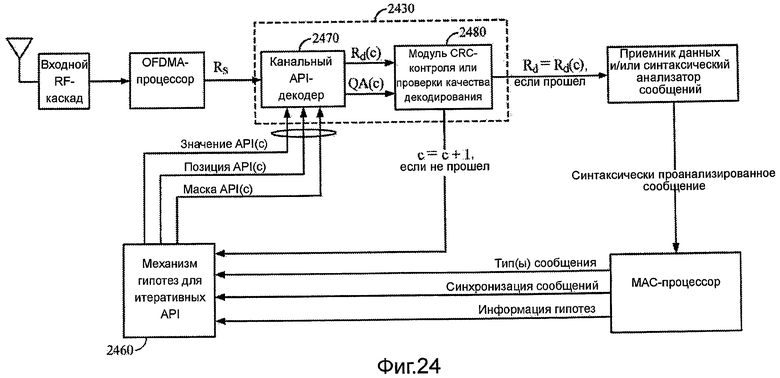

Фиг.24 иллюстрирует примерное приемное устройство, допускающее итеративную оценку нескольких гипотез декодирования.

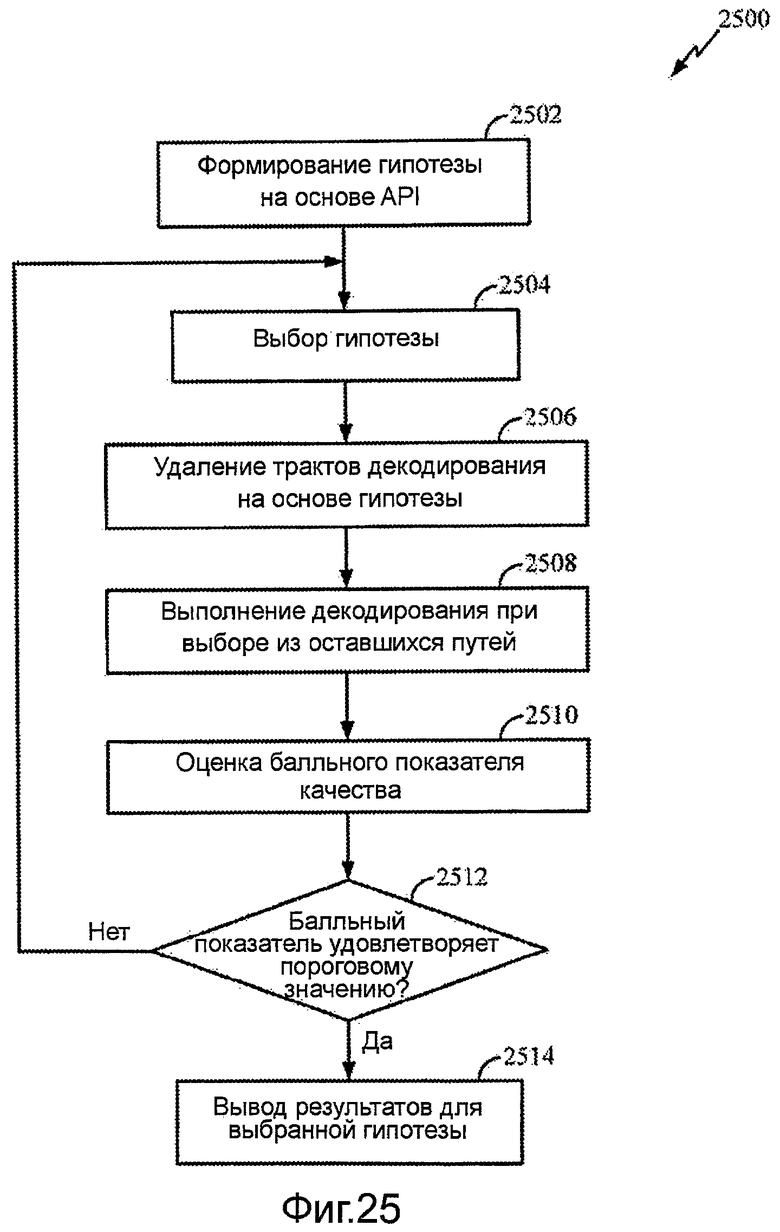

Фиг.25 иллюстрирует примерный процесс для итеративной оценки нескольких гипотез декодирования.

Подробное описание изобретения

Настоящее изобретение, в общем, предоставляет технологии и устройства для декодирования сверточно кодированных беспроводных передач с использованием априорной информации, касающейся передачи. Априорная информация может использоваться для того, чтобы эффективно уменьшать совокупность возможных декодированных потоков битов посредством исключения тех из них, которые включают в себя биты, которые являются несогласованными с априорной информацией. Посредством удаления этих "известных неправильных" трактов, которые приводят к ошибочным данным, декодированные частоты ошибок по битам могут снижаться в некоторых ситуациях.

При использовании в данном документе термин "априорная информация", в общем, упоминается как информация, известная заранее, к примеру информация, развивающаяся от известной или предполагаемой причины до обязательно связанного результата. Как подробнее описано ниже, примеры априорной информации, связанной с передачей, включают в себя известные информационные биты в определенных сообщениях. Примеры таких известных информационных битов включают в себя зарезервированные биты со значениями, указываемыми посредством стандарта, или биты, которые имеют известные или прогнозируемые значения на основе их значения в предыдущих передачах. Эти известные позиции битов и битовые значения (в данном документе называемые "API-значениями") могут использоваться в процессе декодирования для того, чтобы повышать производительность декодирования посредством исключения трактов, которые соответствуют значениям, которые отличаются от API-значений.

Примерное окружение

Фиг.1 иллюстрирует примерную систему, в которой варианты осуществления настоящего изобретения могут быть использованы для того, чтобы обрабатывать беспроводной сигнал от базовой станции 110 к мобильной станции 120. Базовая станция 110 может быть станцией беспроводной связи, установленной в стационарном местоположении, таком как вышка сотовой телефонной связи. Мобильная станция 120 может быть абонентским устройством (UE) любого подходящего типа, допускающим обмен данными с базовой станцией 110, к примеру переносным сотовым телефоном или мобильным устройством другого типа.

Базовая станция 110 и мобильная станция 120 могут обмениваться данными с помощью одной или более антенн 112, 122 и с помощью любой подходящей технологии беспроводной связи с применением схем модуляции, такой как мультиплексирование с ортогональным частотным разделением каналов (OFDM) и множественный доступ с ортогональным частотным разделением каналов (OFDMA). Для некоторых вариантов осуществления обмен данными между базовой и мобильной станцией может быть частично или полностью совместим с множеством стандартов института инженеров по электронике и радиотехнике (IEEE), таких как семейство стандартов IEEE 802.16 (стандарт общемировой совместимости широкополосного беспроводного доступа - WiMAX) и 802.20 (стандарт широкополосного беспроводного доступа для мобильных устройств - MBWA).

В некоторых вариантах применения базовая станция 110 может передавать данные в мобильную станцию по тому, что обычно упоминается как прямая линия связи, тогда как мобильная станция 120 передает данные в базовую станцию 120 по обратной линии связи. Как подробнее описано ниже, различные типы априорной информации могут быть доступными для передач по прямой и обратной линии связи. Эта априорная информация может включать в себя информацию, касающуюся синхронизации и содержимого определенных сообщений между базовой станцией 110 и мобильной станцией 120, которая может приводить к известности значения одного или более битов в передаче.

Технологии, описанные в данном документе, могут быть использованы при декодировании, выполняемом в базовой станции 110, мобильной станции 120 или в обеих из них. Как подробнее описано ниже, априорная информация о различных типах сообщений, передаваемых между базовой станцией 110 и 120, может использоваться для того, чтобы определять значение конкретных местоположений битов в передаче.

Фиг.2 иллюстрирует блок-схему примерных компонентов для одного варианта осуществления приемного устройства, допускающего прием передаваемых сигналов. Антенна 202 может принимать передаваемые сигналы из передающего устройства и отправлять их в радиочастотный (RF) входной каскад 210. Входной RF-каскад 210 может включать в себя любые подходящие схемы для приема передаваемых сигналов и подготовки их для обработки цифровых сигналов, такие как автоматическая регулировка усиления (AGC), блок быстрого преобразования Фурье (FFT), модуль оценки канала и модуль оценки отношения "мощность-несущей-к-помехам-и-шуму" (CINR).

Сигналы из входного RF-каскада 210 могут затем отправляться в блок 220 обработки сигналов, который может содержать любые подходящие схемы для освобождения поднесущей, обратного преобразования сигналов и т.п. Выводом блока 220 обработки сигналов является набор кодированных битов. Кодированные биты перенаправляются в канальный декодер 230, который может декодировать кодированные биты с использованием априорной информации о соответствующей передаче.

Априорное декодирование

Фиг.3 является блок-схемой декодера 230, допускающего выполнение операций декодера на основе априорной информации в соответствии с вариантом осуществления настоящего изобретения. Хотя проиллюстрированный пример показывает схему декодирования по Витерби в качестве примера, технологии априорного декодирования, представленные в данном документе, также могут применяться к другим типам схем декодирования, таким как турбокодирование/декодирование, кодирование/декодирование на основе разреженного контроля по четности (LDPC), RS-кодирование/декодирование, BCH-кодирование/декодирование и различные другие схемы.

В случае схем, которые используют систематические коды, кодированные биты могут включать в себя систематические биты (информацию до кодирования) и биты четности (избыточные биты, являющиеся результатом кодирования). Схема API-декодирования может применяться к систематическим битам. Другими словами, значения API-битов могут включать в себя известные значения систематических битов на основе конкретных используемых систематических кодов. Чтобы применять API для систем с использованием систематических кодов, биты принимаемых данных могут заменяться (известными/прогнозированными) значениями API-битов во входном каскаде декодера. Таким образом, вероятность успешного декодирования может увеличиваться при использовании API для систематических декодеров.

Декодер 230 включает в себя модуль 232 показателей ветвления, логическую схему 234 суммирования, сравнения и выбора (ACS) и модуль 236 обратного отслеживания (TB), чтобы формировать набор декодированных битов 246 из набора "мягко (или жестко)" кодированных/принимаемых битов 240. Модуль показателей ветвления, в общем, выполнен с возможностью вычислять показатели ветвления, которые представляют нормированные расстояния между принимаемым символом (набором битов) и символами в кодовом алфавите. ACS-модуль 234, в общем, компилирует данные показателей ветвления, чтобы формировать показатели для трактов декодирования (2K-1 трактов при условии длины кодового ограничения в K), и выбирает один из этих трактов декодирования в качестве оптимального. Результаты этих выборов записываются в запоминающее устройство модуля 236 обратного отслеживания, который восстанавливает тракт из сохраненных решений. Набор декодированных битов затем может быть сформирован на основе переходов восстановленного тракта.

Один или более из компонентов декодера могут управляться посредством набора API-битов 250, чтобы предотвращать выбор трактов декодирования, которые соответствуют битовым значениям, которые являются несогласованными с априорной информацией. Другими словами, API-биты 250 могут содержать достаточную информацию, чтобы указывать конкретные значения ("0" или "1"), которые являются известными для определенных местоположений битов в последовательности декодируемых битов. Любая битовая строка, которая имеет значение, отличное от значения, указываемого в API-битах 250, не является допустимой декодированной битовой строкой. Таким образом, декодер может удалять тракты декодирования, соответствующие этим недопустимым битовым строкам, из рассмотрения во время выбора тракта.

Как проиллюстрировано на фиг.4, для некоторых вариантов осуществления ACS-модуль 234 может управляться посредством API-битов 250, чтобы исключать тракты декодирования, которые соответствуют недопустимым декодированным битовым строкам. Во время работы ACS API-биты 250 могут использоваться для того, чтобы уменьшать конкретные переходы тракта декодирования, которые соответствуют кодированным битовым значениям, которые являются несогласованными с API-значениями.

API-биты 250, в общем, включают в себя достаточную информацию для того, чтобы идентифицировать один или более битов в декодированной битовой строке, которые имеют битовые значения, которые являются известными (или прогнозируемыми) на основе априорной информации, и, дополнительно, то, чему равны эти битовые значения. Фактический формат, в котором передается эта информация, может меняться в зависимости от различных вариантов осуществления и согласно фактическим схемам реализации.

Например, для некоторых вариантов осуществления API-биты 250 могут включать в себя три типа информации: индикатор относительно позиций 252 битов, битовые значения 254 и, необязательно, биты 256 API-маски. Позиции 252 битов могут предоставлять индикатор относительно местоположений битов (в рамках кодированной последовательности), которые имеют известные значения, при этом битовые значения 254 предоставляют фактические известные значения ("0" или "1") кодированного бита. Фиг.7, подробно описанная ниже, предоставляет иллюстрацию с примерными значениями для позиций битов, битовых значений и битов маски согласно этому формату.

Позиции 252 API-битов могут идентифицировать позиции битов, которые соответствуют позиции известного/прогнозированного кодированного бита в решетчатой структуре. Согласно одному варианту осуществления позиции 252 API-битов могут явно идентифицировать позиции битов, которые имеют известные значения, при этом все другие позиции битов считаются "неизвестными". Соответствующее битовое значение "0" или "1" в битовых значениях 254 тем самым может использоваться для того, чтобы идентифицировать допустимые переходы в решетчатой структуре и эффективно удалять тракты декодирования, заключающие в себе недопустимые переходы.

Например, фиг.5 иллюстрирует пример перехода состояния решетчатой структуры с 3-битовыми состояниями. Проиллюстрированный пример предполагает кодовую скорость 1/2 и K=4 (с 3-битовым, K-1, регистром состояния). Сплошные стрелки указывают переходы состояния, соответствующие входному биту "0", тогда как пунктирные стрелки указывают переходы состояния, соответствующие входному биту "1". Согласно API-декодированию, переходы состояния, которые соответствуют входным битам, которые являются несогласованными с известными значениями, могут исключаться из рассмотрения, тем самым эффективно исключая все тракты, включающие в себя эти переходы, из конечного выбора.

В качестве примера, если известное значение API-бита для этого состояния равно "0", переходы состояния со сплошными линиями должны оцениваться, в то время как переходы состояния с пунктирными линиями не должны вычисляться, поскольку они являются частью недопустимых трактов, которые не должны рассматриваться для выбора. Как описано выше, эти переходы могут эффективно исключаться при следующем переходе посредством задания значения показателя состояния равным значению наихудшего случая. В дополнение к сокращению частоты ошибок по битам посредством исключения недопустимых трактов из выбора, исключение числа переходов на основе значений API-битов также может сокращать число вычислений в ACS-модуле.

Для некоторых вариантов осуществления маскирующая функция может быть реализована посредством использования битов 256 API-маски, чтобы идентифицировать позиции битов, значение API-бита которых должно игнорироваться. Такая маскирующая функция может быть полезной и добавлять гибкость, например, когда стандарт изменяется, приводя к тому, что ранее известное битовое значение становится неизвестным. Задание бита маски может предоставлять простой механизм, чтобы эффективно приспосабливать такие изменения. Маскирующая функция также может быть реализована посредством обработки позиций 252 API-битов так, чтобы удалять идентификационные данные позиции бита, которая более не имеет известного значения, тем самым предоставляя альтернативу изменению значения в значении битовой маски и/или вообще исключая необходимость значения битовой маски.

Фиг.6 иллюстрирует примерный процесс 600 для API-декодирования. Процесс начинается, на этапе 602, посредством формирования гипотезы на основе априорной информации. На этапе 604 удаляются тракты декодирования, которые приводят к битовым значениям, несогласованным со значениями API-битов гипотезы. В завершение, на этапе 606, декодирование выполняется на основе выбора одного из оставшихся трактов.

При использовании в данном документе термин "гипотеза", в общем, упоминается как конкретный набор API-битов, например, указывающий позиции битов с известными значениями и задающий значения для этих битов. Как подробнее описано ниже, для некоторых вариантов осуществления отдельная логическая схема (упоминаемая в данном документе как "механизм гипотез") может предоставляться, чтобы формировать одну или более гипотез, например, на основе информации сообщений из MAC-процессора.

Фиг.7 иллюстрирует один пример гипотезы для 6-битового потока, применяемой к API-декодеру. Проиллюстрированная гипотеза указывает, через значения позиций API-битов [1 2 3 5], что значения API-битов присутствуют в позициях битов 1, 2, 3 и 5 для использования при декодировании. Согласно проиллюстрированной схеме соответствующие значения API-битов [1 0 1 1] указывают, что битовые значения для битов в этих позициях следующие: бит 1=1, бит 2=0, бит 3=1 и бит 5=1. Для некоторых вариантов осуществления могут использоваться битовые значения API-маски [0 0 0 0], которые указывают, что маскирующая функция не применяется ни к одному из битов. С другой стороны, чтобы исключать бит из API-декодирования, бит маски может задаваться, например, равным [0 0 0 1], чтобы маскировать позицию бита 5, приводя к фактическим битовым значениям [1 0 1 X].

Конечно, функциональность API-маски также может быть реализована посредством управления значениями позиций API-битов. В качестве примера, позиция бита 5 также может эффективно маскироваться посредством удаления 5 из значений позиций битов, приводя к значениям позиций битов [1 2 3], с соответствующими значениями API-битов [1 0 1]. В этой схеме позиции API-битов могут эффективно маскироваться без необходимости отдельной структуры данных для значений маски.

В альтернативной схеме могут использоваться только значения API-битов и соответствующие значения API-маски. В качестве примера, можно предположить, что все позиции в битовой последовательности используются для API-декодирования, например, по умолчанию или посредством специального индикатора относительно всех позиций битов в значении позиции API (к примеру, [1 2 3 4 5 6]). В любом случае, значения API-маски могут использоваться для того, чтобы идентифицировать позиции битов, которые не имеют соответствующих значений API-битов. Например, значение API-маски [0 0 0 1 0 1] может использоваться, где значения "1" указывают, что значения API-битов, соответствующие позициям битов 4 и 6, должны игнорироваться, приводя к соответствующим значениям API-битов [1 0 1 X 1 X].

Фиг.8 иллюстрирует то, как значения API-битов гипотезы, показанной на фиг.7, могут применяться для того, чтобы сокращать число трактов декодирования, рассматриваемых в ходе декодирования. Верхняя схема 810 показывает все возможные тракты через схему, которые должны рассматриваться в традиционной схеме декодирования, которая предполагает, что все входные биты являются неизвестными. Как проиллюстрировано посредством нижней схемы 820, тем не менее, схема API-декодирования выполняет поиск в значительно сокращенном числе трактов, исключая число переходов трактов на основе использования известных значений API-битов.

Сокращение трактов на основе значений API-битов может поясняться посредством прохождения по схеме 820 слева направо. Известные API-значения для соответствующих переходов перечисляются наверху. Для первого перехода битовое значение - это известное "1", приводя к удалению переходов трактов, указанных сплошными линиями, соответствующих нулевому входному биту. Это приводит к переходам на узлы 100b, 101b, 110b и 111b состояния.

Второй переход соответствует известному битовому значению "0", приводя к удалению переходов трактов, указанных пунктирными линиями. Это приводит к переходам на узлы 010b и 011b состояния. Третий переход соответствует известному битовому значению "1", приводя к удалению переходов трактов, указанных сплошными линиями. Это приводит к переходам на один узел 101b состояния.

Битовое значение для четвертого перехода, тем не менее, является неизвестным. Следовательно, оба возможных тракта перехода оцениваются. Это приводит к переходам на узлы 010b и 110b состояния. Пятый переход соответствует известному битовому значению "1", приводя к удалению переходов трактов, указанных сплошными линиями. Это приводит к переходам на узлы 101b и 111b состояния. Битовое значение для шестого перехода снова является неизвестным. Следовательно, оба возможных тракта переходов оцениваются, приводя к переходам на узлы 010b и 110b состояния из узла 101b состояния и переходам на узлы 011b и 111b состояния из узла 111b состояния.

Показатели ветвления для этих оставшихся трактов могут оцениваться, чтобы выбирать оптимальный тракт и формировать соответствующий набор декодированных битов. Посредством исключения трактов декодирования, которые соответствуют недопустимым битовым последовательностям, частоты ошибок по битам/пакетам могут снижаться с использованием API-декодирования, причем большие снижения ожидаются в более зашумленных окружениях.

Фиг.9 является примерным графиком частоты ошибок по пакетам (PER) в зависимости от отношения "сигнал-шум" (SNR) для моделированного декодирования сообщения заголовка управления кадром (FCH)/префикса кадра нисходящей линии связи (DLFP) стандарта IEEE 802.16e. Этот тип сообщения содержит 24-битовую информацию. Из них 5 битов являются зарезервированными битами, которые должны быть заданы равными нулю согласно стандарту. В моделированном примере эти 5 зарезервированных битов используются в качестве априорной информации, с известными битовыми значениями в "0" в соответствующих местоположениях в 24-битовой строке. Моделирование также предполагает модуляцию и кодирование следующим образом: QPSK, TBCC (r=1/2), с коэффициентом повторения 4 и коэффициентом дублирования 2 и предполагает комбинирование с максимальным отношением для повторений (MRC) на приемной стороне (RX).

Как проиллюстрировано, схема API-декодирования демонстрирует повышенную производительность относительно традиционной схемы декодирования в AWGN-окружениях. Например, схема API-декодирования демонстрирует усиление примерно в 0,6 дБ при PER 10-2 в AWGN-канале по сравнению с традиционным декодированием (без учета API).

Фиг.10 является схемой, аналогичной фиг.9, но соответствующее моделирование предполагает как комбинирование с максимальным отношением для повторений (MRC), так и дублирование на приемной стороне (RX). Как проиллюстрировано, в этом примере схема API-декодирования демонстрирует приблизительное усиление в 0,75 дБ при PER 10-2 в AWGN-канале по сравнению со случаем без схемы API-декодирования.

Механизм гипотез

Как описано выше, для некоторых вариантов осуществления механизм гипотез может предоставляться, чтобы формировать "гипотезы", каждая из которых включает в себя набор значений API-битов, чтобы использовать при выполнении API-декодирования. В зависимости от конкретной реализации механизм гипотез может формировать одну гипотезу или несколько гипотез, которые могут отличаться тем, какие биты имеют известные значения, а также тем, чему равны эти известные значения битов. Оценка нескольких гипотез может быть полезной, например, когда имеется только ограниченное число допустимых битовых комбинаций для данной последовательности.

Фиг.11 иллюстрирует схему приемного устройства 1100, которое включает в себя API-декодер 230 и механизм 1110 гипотез. Как проиллюстрировано, механизм 1110 гипотез может принимать информацию, касающуюся сообщения от процессора 1120 управления доступом к среде (MAC), и формирует значения API-битов (гипотезу) для использования посредством API-декодера 230. API-декодер 230 начинает декодировать принимаемые мягко (или жестко) кодированные биты Rs с использованием значений API-битов, предоставленных посредством механизма 1110 гипотез. API-декодер 230 выводит декодированные биты Rd данных, которые доставляются в синтаксический анализатор 1130 сообщений.

Если синтаксический анализатор 1130 сообщений обнаруживает, что декодированные биты предназначены для данного типа сообщения, сообщение синтаксически анализируется и доставляется в процессор 1120 MAC (управление доступом к среде). MAC-процессор 1120 может выступать в качестве типа анализатора протоколов, анализирующего принимаемые данные, например, в попытке определять то, каким является следующий возможный тип сообщения, и то, какой должна быть синхронизация.

В качестве примера, MAC-процессор 1120 может распознавать первое входящее сообщение (или данные) как FCH/DLFP-сообщение, после которого следует преамбула нисходящей линии связи. В некоторых случаях MAC-процессор 1120 может использовать определенную информацию из предыдущего кадра, например, чтобы определять кодовую скорость, длину сообщения или некоторый другой параметр. MAC-процессор 1120 может предоставлять эту информацию в механизм 1110 гипотез, который должен использовать ее для того, чтобы извлекать известные битовые значения (или прогнозированные битовые значения) для конкретных местоположений битов и формировать API-информацию, чтобы перенаправлять в API-декодер.

Фиг.12 иллюстрирует примерный механизм 1110 гипотез, который может использоваться для того, чтобы формировать гипотезы декодирования на основе априорной информации и информации сообщений, предоставленной посредством MAC-процессора 1120. Как проиллюстрировано, механизм гипотез принимает индикатор относительно типа сообщения и включает в себя логическую схему 1210, чтобы извлекать соответствующее сообщение(я), обозначенное посредством типа сообщения, и формат сообщения(й) анализируется посредством логической схемы 1220 формата.

Для некоторых вариантов осуществления, в дополнение к местоположениям битов с фиксированными/известными битовыми значениями (такими как зарезервированные биты, заданные равными известному значению согласно стандарту), гипотезы могут быть сформированы с помощью информации, которая является прогнозируемой. В качестве примера, битовая информация может быть прогнозируемой на основе значения из ранее принятого сообщения (к примеру, тип кодирования практически никогда не изменяется между сообщениями).

Таким образом, логическая схема 1230 классификации может классифицировать битовую информацию в данном сообщении, по меньшей мере, на три категории: фиксированная информация, прогнозируемая информация и переменная информация. Фиксированная (известная) информация, в общем, упоминается как информация, которая является фиксированной, так что она является известной на 100% из начальной стадии или некоторых битовых значений, которые являются известными при некоторых условиях (к примеру, после проверки результатов декодирования связанных сообщений). Например, декодированные результаты сообщений, касающихся данных, которые должны быть декодированы, такие как сообщения или данные, о которых известно, что они размещаются перед данными, которые должны быть декодированы, могут анализироваться, и API-информация может извлекаться из проанализированных данных.

Прогнозируемая информация может включать в себя информацию, которая может быть прогнозируемой при определенных условиях или допущениях, так что она может предоставлять различные варианты значений или битовые комбинации для набора из одного или более битов. Различные варианты значений могут быть включены в различные гипотезы. Например, прогнозируемая информация может включать в себя определенную информацию, прогнозируемую при определенных условиях или допущениях, или информацию, которая является прогнозируемой после проверки результатов декодирования связанных сообщений.

Переменная информация, в общем, включает в себя информацию, которая является неизвестной или которую слишком трудно прогнозировать, так что она, в общем, не используется в качестве значений API-битов (к примеру, значения позиций API-битов для этих местоположений битов могут быть заданы равными "0"). После классификации информационных битов логическая схема 1240 формирования гипотез по API и доставки API механизма гипотез может формировать набор или наборы значений API-битов (где каждый набор соответствует гипотезе) с помощью классифицированной информации. Например, логическая схема 1240 может формировать строки из местоположений, битовых значений и масок API-битов, которые должны выводиться в декодер 230.

Схема API-декодирования, представленная в данном документе, может применяться к множеству различных типов сообщений. Например, API-декодирование может применяться к сообщениям (FCH)/префикса кадра нисходящей линии связи (DLFP), как описано ниже, обычным сообщениям DL MAP, сжатым сообщениям DL MAP, сообщениям UL MAP, сообщениям запроса полосы пропускания (BW-REQ), сообщениям запроса на выбор начального диапазона (IRNG-REQ) и т.д.

Сообщение 1300 заголовка управления кадром (FCH)/префикса кадра нисходящей линии связи (DLFP), как проиллюстрировано на фиг.13, предоставляет хороший пример различных битов информации, которая может быть классифицирована как фиксированная, прогнозируемая и переменная. Формат и содержимое FCH-сообщения задается в OFDMA-стандарте IEEE 802.16e. DLFP является содержимым FCH-канала. DLFP - это структура данных, передаваемая в начале каждого кадра, и она содержит информацию, касающуюся текущего кадра, и преобразуется в FCH. Следовательно, успешное декодирование DLFP очень важно для того, чтобы обрабатывать весь кадр. Классификация некоторых битов может изменяться со временем, например, после перехода из состояния начального обнаружения на обнаружение первого кадра сообщения.

В качестве примера, поле 1310 битовой карты включает в себя 6 битов, где каждый бит указывает то, используется или нет соответствующая группа сообщений посредством сегмента. В состоянии начального обнаружения эти биты являются неизвестными. Тем не менее, после начального декодирования и идентификации сегмента сообщения, по меньшей мере, один из битов должен быть идентифицирован (к примеру, при условии, что первый бит группы сообщений используется, API-биты="1XXXXX"). Дополнительно, в обычном рабочем режиме мобильная станция может прогнозировать все 6 из битов при условии, что базовая станция отправляет битовую карту, идентичную битовой карте предыдущего кадра.

Как описано выше, биты зарезервированных полей 1320 и 1322 должны оставаться фиксированными до тех пор, пока в стандарт не вносятся изменения. В отличие от этого, 2 бита поля 1330 типа повторения трудно прогнозировать, и они могут изменяться между кадрами.

3-Битовое поле 1340 типа кодирования может быть классифицировано по-разному и использовано для того, чтобы формировать ряд различных гипотез. Например, без наложения каких-либо условий на типы кодирования 3-битовое поле может обрабатываться как переменное. Тем не менее, с помощью априорной информации некоторые из этих битов могут обрабатываться как фиксированные. Например, если известно, что текущая версия WiMAX поддерживает только два типа кодирования, TBCC(0b000) и CTC(0b010), первый и третий биты могут обрабатываться как известные битовые значения "0" (API-биты="0b0X0").

Хотя 8-битовое поле 1350 длины может варьироваться между кадрами, некоторые из битов могут быть классифицированы другими способами. В качестве примера, отсутствие наложения ограничения на все 8 битов поля длины должно быть переменным. Тем не менее, в большинстве случаев длина DL-MAP составляет менее 2^7, так что MSB может быть прогнозирован как равный "0" (API-биты="0b0XXXXXXX"). Хотя это прогнозирование может не быть истинным, снижение достигаемой частоты ошибок по битам может перевешивать все потери производительности, обусловленные необходимостью повторно декодировать с помощью различной гипотезы. Более активные гипотезы также могут быть сформированы аналогичным образом, например, при условии, что длина составляет менее 2^6 (API-биты="0b00XXXXXX") или менее 2^4 (API-биты="0b0000XXXX").

Фиг.14A-14G иллюстрируют примеры нескольких гипотез API-декодирования для FCH/DLFP-сообщения на основе информации и возможных классификаций и предположений, описанных выше. Гипотезы упоминаются как имеющие различные уровни (L0-L6), которые, в общем, представляют то, насколько "активной" является гипотеза, на основе числа битов, которые обрабатываются как имеющие известные битовые значения.

Ссылаясь сначала на фиг.14A, гипотеза L0 соответствует случаю отсутствия значений API-битов (отсутствия гипотезы), как в случае первого сообщения в каждом кадре. Другими словами, поскольку сообщение не декодировано, отсутствует информация сообщений, которая может использоваться для того, чтобы формировать API-значения. Фиг.14B иллюстрирует гипотезу первого уровня (L1) только с зарезервированными битовыми значениями, используемыми в гипотезе.

Фиг.14C иллюстрирует гипотезу L2, которая включает в себя зарезервированные битовые значения плюс битовое значение битовой карты (группа сообщений, указываемая в первом кадре), используемое в гипотезе. Фиг.14D иллюстрирует гипотезу L3, которая, относительно гипотезы L2, добавляет оставшиеся битовые значения битовой карты, которые использованы в предыдущем кадре.

Фиг.14E иллюстрирует гипотезу L4, которая, относительно гипотезы L3, добавляет битовые значения поля кодирования, которые являются общими для поддерживаемых типов кодирования TBCC и CTC. Фиг.14F иллюстрирует гипотезу L5, которая, относительно гипотезы L4, добавляет верхние два бита поля длины на основе допущения, что длина составляет менее 2^6. Фиг.14G иллюстрирует гипотезу L6, которая, относительно гипотезы L5, добавляет еще два бита поля длины на основе допущения, что длина составляет менее 2^4.

Битовые значения для каждой из этих гипотез могут использоваться посредством API-декодера для того, чтобы сокращать число трактов декодирования, которые соответствуют ошибочным данным, способом, описанным выше. Конечно, гипотезы, показанные на фиг.14B-14G, являются только примерными. Дополнительно, хотя проиллюстрированные гипотезы постепенно становятся более активными и включают в себя большее число известных битовых значений, специалисты в данной области техники должны признавать, что другие гипотезы могут быть сформированы с использованием различных комбинаций битовых значений, показанных в этих примерах.

Как описано выше, значения API-битов согласно этим различным гипотезам могут использоваться посредством API-декодера для того, чтобы удалять тракты декодирования, которые соответствуют ошибочным данным. Поскольку различные гипотезы имеют различные значения API-битов, производительность декодирования может варьироваться между гипотезами. Фиг.15-17 показывают примерные графики, которые иллюстрируют варьирования производительности между различными гипотезами для различных каналов.

Фиг.15 показывает результаты моделирования API-декодирования для различных гипотез L0-L6 в канале аддитивного белого гауссова шума (AWGN). В моделировании предполагается, что все гипотезы являются корректными (другими словами, предполагается, что значения API-битов совпадают с фактическими кодированными битовыми значениями).

Как проиллюстрировано, гипотезы с большим количеством API-битов дают в результате лучшую производительность (уменьшенные частоты ошибок по битам). Фиг.16 показывает аналогичные результаты для API-декодирования при использовании различных гипотез для каналов ITU Ped-A и Ped-B. Фиг.17 показывает аналогичные результаты для API-декодирования при использовании различных гипотез для каналов ITU Veh-A и Veh-B.

Хотя вышеприведенное описание направлено на варианты осуществления настоящего изобретения, другие и дополнительные варианты осуществления изобретения могут быть разработаны без отступления от его объема, и его объем определяется посредством нижеприведенной формулы изобретения.

Способы обработки нескольких гипотез

Как пояснено выше, механизм гипотез формирует гипотезу битовых значений на основе как фиксированной, так и прогнозируемой априорной информации. Механизм гипотез может использовать прогнозируемую информацию, чтобы формировать несколько (Nc) гипотез посредством допущения различных комбинаций битовых значений. Чтобы повышать производительность, может быть желательным обрабатывать несколько гипотез. Соответственно, декодер может исследовать несколько доставляемых гипотез. Таким образом, число обработанных гипотез может равняться числу доставляемых гипотез, Nc. Если имеется несколько обработанных гипотез, только самая точная гипотеза может выбираться.

В некоторых вариантах осуществления принимаемое сообщение может содержать поле контроля циклическим избыточным кодом (CRC) или другой аналогичный тип контрольного поля. Для сообщений, в которых отсутствует CRC, критерии выбора могут быть основаны на накопленной вероятности (или накопленном расстояния) на конечной стадии декодирования. Для сообщений, которые имеют CRC, критерии выбора могут быть основаны либо на результатах CRC-контроля, либо на накопленной вероятности.

Предусмотрено несколько способов, которые могут быть использованы для того, чтобы оценивать несколько гипотез. Эти способы могут включать в себя параллельную, последовательную и итеративную оценку. Чтобы реализовывать способ параллельной оценки, множество декодеров используется, где каждый декодер обрабатывает одну или более из Nc API-гипотез.

Напротив, последовательные и итеративные способы декодирования могут использовать один декодер, чтобы обрабатывать одну гипотезу за раз. При последовательном способе декодер обрабатывает все гипотезы в контуре, который имеет длину Nc, тогда как при итеративном способе декодер обрабатывает последовательность гипотез до тех пор, пока он не находит одну гипотезу, которая удовлетворяет заранее определенному пороговому значению критериев выбора.

В некоторых вариантах осуществления число гипотез может превышать число процессоров. В таких вариантах осуществления может быть использован гибридный способ, при котором каждый процессор работает параллельно, но каждый процессор оценивает несколько гипотез последовательно или итеративно.

Фиг.18 иллюстрирует схему приемного устройства, которая включает в себя параллельный API-декодер 1830 и механизм 1860 гипотез, который формирует несколько гипотез.

Как проиллюстрировано, механизм 1860 гипотез может формировать Nc различных гипотез, каждая из которых имеет различный набор значений API-битов API(1)-API(Nc), на основе информации сообщений, принимаемой из MAC-процессора. Механизм гипотез может формировать несколько гипотез, например, на основе различных предположений, используемых для того, чтобы прогнозировать битовые значения. Как описано выше, некоторые из гипотез могут считаться более активными, чем другие, например, на основе числа битовых значений, которые являются прогнозированными.

Декодер 1830 декодирует принимаемые биты Rs с использованием значений API-битов различных гипотез, фактически многократно параллельно декодируя принимаемые биты посредством применения различных гипотез. После оценки нескольких гипотез декодер 1830 может выводить декодированные биты Rd данных, полученные с помощью гипотезы, определенной как наилучшая на основе некоторого типа критериев выбора.

Фиг.19 иллюстрирует примерный процесс 1900 для параллельной оценки нескольких гипотез. Процесс 1900 может описываться со ссылкой на фиг.20, которая иллюстрирует примерный вариант осуществления параллельного декодера 1830, имеющего множество API-декодеров 2000, размещаемых параллельно.

Процесс начинается, на этапе 1902, посредством формирования множества гипотез на основе априорной информации. На этапе 1904 каждая гипотеза может отправляться в один из декодеров 2000. Как проиллюстрировано на фиг.20, каждая гипотеза может включать в себя типы информации, описанные выше (к примеру, битовые значения, местоположения битов и/или битовые маски), которые должны использоваться посредством декодера при декодировании принимаемых битов Rs.

Каждый декодер выполняет API-декодирование, на этапах 1906 и 1908, удаление трактов декодирования на основе значений API-битов соответствующей гипотезы и выбор из оставшихся трактов, чтобы формировать набор декодированных битов Rd. На этапе 1910 каждый декодер может формировать показатель качества (QA), который может использоваться для того, чтобы выбирать наилучшую гипотезу, например, в случае если декодированное сообщение не включает в себя CRC. Если сообщение фактически содержит CRC, отдельный показатель качества может формироваться или не формироваться. На этапе 1912 результаты декодирования из каждого декодера сравниваются, и на этапе 1914 результаты, полученные с помощью наилучшей гипотезы, выбираются.

Как проиллюстрировано на фиг.20, если декодируемое сообщение содержит CRC, результаты декодирования могут сравниваться посредством выполнения CRC-контроля с помощью CRC-логической схемы 2020. CRC-логическая схема 2020 может формировать вывод (Sx), идентифицирующий гипотезы с декодированными результатами, которые имеют совпадающий CRC. Вывод Sx может использоваться для того, чтобы управлять логической схемой 2030 выбора, которая выступает в качестве мультиплексора, чтобы выводить соответствующие декодированные результаты.

В качестве альтернативы CRC-контролю (к примеру, если декодированное сообщение не имеет CRC), показатель качества может использоваться для того, чтобы выбирать наилучшую гипотезу. Показателем качества может быть, например, значение вероятности или накопленного расстояния. Логическая схема 2010 решений по ML может оценивать показатель качества из каждого декодера, формируя вывод (Sy), идентифицирующий гипотезу с декодированными результатами, которые имеют наилучший показатель качества (к примеру, наименьшее накопленное расстояние или наибольшую вероятность). Вывод Sy может использоваться для того, чтобы управлять логической схемой 2030 выбора, чтобы выводить соответствующие декодированные результаты.

Фиг.21 иллюстрирует схему приемного устройства, которая включает в себя последовательный API-декодер 2130 и механизм 2160 гипотез, который формирует несколько гипотез.

Как проиллюстрировано, механизм 2160 гипотез может формировать Nc различных гипотез и последовательно выводить эти гипотезы в декодер 2130. Например, как проиллюстрировано, механизм 2160 гипотез может выводить значения API-битов API(c) в декодер 2130, где c = от 1 до Nc.

Декодер 2130 декодирует принимаемые биты Rs с использованием значений API-битов различных гипотез, фактически многократно последовательно декодируя принимаемые биты посредством применения различных гипотез. После оценки нескольких гипотез декодер 2130 может выводить декодированные биты Rd данных, полученные с помощью гипотезы, определенной как наилучшая на основе некоторого типа критериев выбора.

Фиг.22 иллюстрирует примерный процесс 2200 для последовательной оценки нескольких гипотез. Процесс 2200 может описываться со ссылкой на фиг.23, которая иллюстрирует примерный вариант осуществления последовательного декодера 2130, имеющего один API-декодер 2300 для многократного последовательного декодирования набора принимаемых битов Rs на основе значений API-битов различных гипотез.

Процесс начинается, на этапе 2202, посредством формирования множества гипотез на основе априорной информации. На этапе 2204 одна из гипотез с битовыми значениями API(c) выбирается, чтобы отправляться в декодер 2130 для использования при декодировании принимаемых битов.

Декодер выполняет API-декодирование, на этапах 2206 и 2208, удаление трактов декодирования на основе значений API-битов и выбор из оставшихся трактов, чтобы формировать набор декодированных битов Rd. На этапе 2210 декодер может формировать показатель качества (QA), который может использоваться для того, чтобы выбирать наилучшую гипотезу, например, в случае если декодированное сообщение не включает в себя CRC. Как описано выше, если сообщение фактически содержит CRC, отдельный показатель качества может формироваться или не формироваться. На этапе 2212 результаты декодирования и балльный показатель качества (если сформирован) сохраняются в запоминающем устройстве 2340 для последующей оценки.

Если имеются дополнительные гипотезы, как определено на этапе 2214, операции 2204-2212 повторяются. После того как процесс выполнен для каждой гипотезы, результаты гипотез сравниваются, на этапе 2216, и результаты, полученные с помощью наилучшей гипотезы, выбираются, на этапе 2218.

Как проиллюстрировано на фиг.23, результаты Rd(c) декодирования и показатель QA(c) качества, если сформирован, для каждой из гипотез могут извлекаться из запоминающего устройства 2340 и оцениваться, чтобы определять наилучшую гипотезу. Как проиллюстрировано, схема, аналогичная показанной на фиг.20, может использоваться для того, чтобы выводить идентификационные данные наилучшей гипотезы на основе CRC (Sx) 2320 и/или показателя 2310 качества (Sy), чтобы управлять логической схемой 2330 выбора так, чтобы выводить соответствующие декодированные результаты.

Фиг.24 иллюстрирует схему приемного устройства, которая включает в себя итеративный API-декодер 2430 и механизм 2460 гипотез, который формирует несколько гипотез.

Как и для механизма 2160 гипотез по фиг.21, механизм 2460 гипотез может формировать Nc различных гипотез и последовательно выводить эти гипотезы в декодер 2430. Как и для декодера 2130 по фиг.21, декодер 2430 может использовать один декодер 2470 для того, чтобы декодировать принимаемые биты Rs с использованием значений API-битов API(c) различных гипотез, фактически многократно последовательно декодируя принимаемые биты посредством применения различных гипотез.

Тем не менее, вместо оценки каждой возможной гипотезы и сравнения выводимых результатов декодер 2430 может сравнивать результаты каждой гипотезы с пороговыми критериями выбора. После того как гипотеза оценена с результатами, которые удовлетворяют критериям выбора, соответствующие биты декодированных данных могут выводиться без оценки оставшихся гипотез.

Фиг.25 иллюстрирует примерный процесс 2500 для итеративной оценки нескольких гипотез. Процесс 2500 может выполняться, например, посредством компонентов, показанных на фиг.24.

Процесс начинается, на этапе 2502, посредством формирования множества гипотез на основе априорной информации. На этапе 2504 одна из гипотез с битовыми значениями API(c) выбирается, чтобы отправляться в декодер 2430 для использования при декодировании принимаемых битов. Декодер выполняет API-декодирование, на этапах 2506 и 2508, удаление трактов декодирования на основе значений API-битов и выбор из оставшихся трактов, чтобы формировать набор декодированных битов Rd.

Вместо ожидания до тех пор, пока все гипотезы не оценены, и сравнения результатов, как на фиг.22, результаты, полученные для выбранной гипотезы, оцениваются (в рамках контура) на этапах 2510-2512. Как проиллюстрировано, декодер 2430 может включать в себя логическую схему 2480, чтобы определять то, удовлетворяет или нет набор декодированных битов критериям выбора. Например, логическая схема 2480 может выполнять CRC-контроль и/или сравнивать показатель качества с заранее определенным пороговым значением.

Если критерии выбора не удовлетворяются (к примеру, CRC-контроль не показывает соответствие или показатель качества падает ниже порогового значения), операции 2504-2512 могут повторяться, чтобы оценивать другую гипотезу. Тем не менее, если критерии выбора удовлетворяются, результаты, полученные с помощью текущей гипотезы, выбираются, на этапе 2514.

Порядок, в котором различные гипотезы оцениваются в этом итеративном подходе, может варьироваться. Например, для некоторых вариантов осуществления более активные гипотезы (с большим числом известных/прогнозированных битовых значений) могут оцениваться до менее активных гипотез. Для некоторых вариантов осуществления менее активные гипотезы могут оцениваться до более активных гипотез. Для некоторых вариантов осуществления некоторый другой тип критериев может использоваться для того, чтобы определять порядок, в котором гипотезы выбираются для оценки.

Специалисты в данной области техники должны признавать, что различные технологии для оценки нескольких гипотез могут варьироваться или, в некоторых случаях, комбинироваться. Например, как описано выше, параллельные и последовательные технологии могут комбинироваться, чтобы параллельно оценивать множество гипотез, когда имеется больше гипотез, чем параллельных декодеров.

При использовании в данном документе термин "определение" охватывает широкий спектр действий. Например, "определение" может включать в себя расчет, вычисление, обработку, извлечение, исследование, поиск (к примеру, поиск в таблице, базе данных или другой структуре данных), обнаружение и т.п., и наоборот. Также "определение" может включать в себя прием (к примеру, прием информации), осуществление доступа (к примеру, осуществление доступа к данным в запоминающем устройстве) и т.п. Кроме того, "определение" может включать в себя разрешение, выбор, отбор, установление и т.п., и наоборот.

Информация и сигналы могут быть представлены с помощью любой из множества различных технологий. Например, данные, инструкции, команды, информация, сигналы и т.п., которые могут упоминаться по всему описанию выше, могут быть представлены посредством напряжений, токов, электромагнитных волн, магнитных полей или частиц, оптических полей или частиц либо любой комбинации вышеозначенного.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с настоящим раскрытием сущности, могут быть реализованы или выполнены с помощью процессора общего назначения, процессора цифровых сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторной логической схемы, дискретных аппаратных компонентов либо любой комбинации вышеозначенного, предназначенной для того, чтобы выполнять описанные в данном документе функции. Процессором общего назначения может быть микропроцессор, но в альтернативном варианте процессором может быть любой доступный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть реализован как комбинация вычислительных устройств, к примеру комбинация DSP и микропроцессора, множество микропроцессоров, один или более микропроцессоров вместе с ядром DSP либо любая другая аналогичная конфигурация.

Этапы способа или алгоритма, описанные в связи с настоящим раскрытием сущности, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, приводимом в исполнение посредством процессора, либо в комбинации вышеозначенного. Программный модуль может постоянно размещаться в любой форме носителя хранения данных, который известен в данной области техники. Некоторые примеры носителей хранения данных, которые могут использоваться, включают в себя запоминающее устройство типа RAM, флеш-память, запоминающее устройство типа ROM, запоминающее устройство типа EPROM, запоминающее устройство типа EEPROM, регистры, жесткий диск, съемный диск, CD-ROM и т.д. Программный модуль может содержать одну инструкцию или множество инструкций и может быть распределен по нескольким различным сегментам кода, по различным программам и по нескольким носителям хранения данных. Носитель хранения данных может быть соединен с процессором так, что процессор может считывать информацию и записывать информацию на носитель хранения данных. В альтернативном варианте, носитель хранения данных может быть встроен в процессор.

Способы, раскрытые в данном документе, содержат один или более этапов или действий для осуществления описанного способа. Этапы и/или действия способа могут меняться друг с другом без отступления от объема формулы изобретения. Другими словами, если конкретный порядок этапов или действий не указывается, порядок и/или использование конкретных этапов и/или действий может модифицироваться без отступления от объема формулы изобретения.

Описанные функции могут быть реализованы в аппаратных средствах, программном обеспечении, микропрограммном обеспечении или в любой комбинации вышеозначенного. Если реализованы в программном обеспечении, функции могут сохраняться как одна или более инструкций на машиночитаемом носителе информации. Носителями хранения могут быть любые доступные носители информации, к которым можно осуществлять доступ посредством компьютера. В качестве примера, но не ограничения, эти машиночитаемые носители информации могут содержать RAM, ROM, EEPROM, CD-ROM или другое устройство хранения на оптических дисках, устройство хранения на магнитных дисках или другие магнитные устройства хранения, либо любой другой носитель информации, который может быть использован для того, чтобы переносить или сохранять требуемый программный код в форме инструкций или структур данных, и к которому можно осуществлять доступ посредством компьютера. Диск (disk) и диск (disc) при использовании в данном документе включают в себя компакт-диск (CD), лазерный диск, оптический диск, универсальный цифровой диск (DVD), гибкий диск и диск Blu-Ray®, при этом диски (disk) обычно воспроизводят данные магнитно, тогда как диски (disc) обычно воспроизводят данные оптически с помощью лазеров.

Программное обеспечение или инструкции также могут передаваться по среде передачи. Например, если программное обеспечение передается из веб-узла, сервера или другого удаленного источника с помощью коаксиального кабеля, оптоволоконного кабеля, "витой пары", цифровой абонентской линии (DSL) или беспроводных технологий, таких как инфракрасные, радиопередающие и микроволновые среды, то коаксиальный кабель, оптоволоконный кабель, "витая пара", DSL или беспроводные технологии, такие как инфракрасные, радиопередающие и микроволновые среды, включены в определение среды передачи.

Дополнительно, следует принимать во внимание, что модули и/или другие соответствующие средства для выполнения способов и технологий, описанных в данном документе, могут быть загружены и/или иначе получены посредством мобильного устройства и/или базовой станции при соответствующих условиях. Например, такое устройство может быть связано с сервером, чтобы упрощать передачу средства для осуществления способов, описанных в данном документе. Альтернативно, различные способы, описанные в данном документе, могут предоставляться через средство хранения (к примеру, оперативное запоминающее устройство (RAM), постоянное запоминающее устройство (ROM), физический носитель хранения данных, такой как компакт-диск (CD) или гибкий диск и т.д.), так что мобильное устройство и/или базовая станция могут получать различные способы при подключении или предоставлении средства хранения для устройства. Кроме того, любая другая подходящая технология для предоставления способов и технологий, описанных в данном документе, для устройства может быть использована.

Следует понимать, что формула изобретения не ограничена точной конфигурацией и компонентами, проиллюстрированными выше. Различные модификации, изменения и варьирования могут осуществляться в компоновке, работе и подробностях способов и устройств, описанных выше, без отступления от объема формулы изобретения.

Хотя вышеприведенное описание направлено на варианты осуществления настоящего изобретения, другие и дополнительные варианты осуществления изобретения могут быть разработаны без отступления от его объема, и его объем определяется посредством нижеприведенной формулы изобретения.

Изобретение относится к беспроводной связи, а более конкретно к способу и устройству для декодирования кодированных битов данных передачи системе беспроводной связи. Набор априорных битовых значений, соответствующих известным битовым значениям кодированных битов данных, может быть сформирован. Тракты декодирования, которые соответствуют битам декодированных данных, которые являются несогласованными с априорными битовыми значениями, могут удаляться из возможных трактов декодирования для рассмотрения, и осуществляется декодирование кодированных битов данных посредством выбора тракта декодирования из оставшихся трактов декодирования для возможных трактов декодирования, которые не удалены. Несколько гипотез, каждая из которых соответствует различному набору априорных битовых значений, могут оцениваться, при этом декодированные данные для гипотезы выбираются на основе вывода оценки для дополнительной обработки. Технический результат - обеспечение возможности уменьшения частоты ошибок по битам при декодировании кодированных битов данных передачи. 4 н. и 24 з.п. ф-лы, 31 ил.

1. Способ декодирования кодированных битов данных передачи беспроводной связи, содержащий этапы, на которых:

формируют множество гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи;

оценивают множество гипотез посредством выполнения декодирования кодированных битов данных, при этом декодирование заключает в себе этап, на котором исключают наборы декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез; и

выбирают, в качестве вывода, декодированные биты, соответствующие одной из гипотез.

2. Способ по п.1, в котором оценка множества гипотез содержит этап, на котором:

параллельно оценивают множество гипотез посредством выполнения декодирования кодированных битов данных с использованием множества декодеров, каждый из которых использует битовые значения, указываемые посредством различной гипотезы.

3. Способ по п.1, в котором оценка множества гипотез содержит этап, на котором:

последовательно оценивают множество гипотез посредством многократного выполнения декодирования кодированных битов данных с использованием одного декодера, чтобы декодировать битовые значения кодированных битов, каждый раз указываемые посредством различной гипотезы.

4. Способ по п.3, в котором последовательная оценка множества гипотез содержит этап, на котором оценивают некоторые, но не все, гипотезы.

5. Способ по п.1, дополнительно содержащий этапы, на которых:

сравнивают результаты, полученные посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез; и

выбирают, в качестве вывода, декодированные биты, соответствующие одной из гипотез, на основе сравнения.

6. Способ по п.5, в котором сравнение результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез, содержит этап, на котором:

сравнивают, по меньшей мере, одно из значений накопленного расстояния и значений вероятности.

7. Способ по п.5, в котором сравнение результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез, содержит этап, на котором сравнивают контрольные поля.

8. Способ по п.1, в котором исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, содержит этап, на котором удаляют, из набора возможных трактов декодирования, тракты декодирования, которые соответствуют битам декодированных данных, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотезы.

9. Приемное устройство для беспроводной связи, содержащее:

входной каскад приемного устройства для приема беспроводной передачи и формирования набора кодированных битов;

механизм гипотез для формирования множества гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи; и

декодер, выполненный с возможностью оценки гипотез посредством выполнения операций декодирования, которые заключают в себе исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, и выбор, в качестве вывода, декодированных битов, соответствующих одной из гипотез.

10. Приемное устройство по п.9, в котором декодер выполнен с возможностью декодирования кодированных битов посредством удаления, из совокупности возможных трактов декодирования, трактов декодирования, которые соответствуют битам декодированных данных, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотезы, и выбора тракта декодирования из оставшихся трактов декодирования для возможных трактов декодирования, которые не удалены.

11. Приемное устройство по п.9, в котором декодер содержит множество схем декодирования, предоставляющих возможность параллельной оценки множества гипотез.

12. Приемное устройство по п.9, в котором декодер выполнен с возможностью последовательной оценки множества гипотез посредством многократного выполнения декодирования кодированных битов данных, при этом декодирование выполняется с использованием битовых значений, каждый раз указываемых посредством различной гипотезы.

13. Приемное устройство по п.9, дополнительно содержащее запоминающее устройство для сохранения результатов декодирования с использованием битовых значений, указываемых посредством различных гипотез.

14. Приемное устройство по п.9, в котором декодер последовательно оценивает множество гипотез посредством оценки гипотез до тех пор, пока не получаются результаты декодирования, которые удовлетворяют заданным критериям.

15. Приемное устройство по п.9, дополнительно содержащее:

логическую схему сравнения для сравнения результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез; и

логическую схему выбора для выбора, в качестве вывода, декодированных битов, соответствующих одной из гипотез, на основе вывода, сформированного посредством логической схемы сравнения.

16. Приемное устройство по п.15, в котором логическая схема сравнения сравнивает, по меньшей мере, одно из значений накопленного расстояния и значений вероятности для результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез.

17. Устройство для беспроводной связи, содержащее:

средство для приема беспроводной передачи и формирования набора кодированных битов;

средство для формирования множества гипотез, причем каждая гипотеза указывает набор битовых значений кодированных битов данных, которые являются известными или прогнозированными на основе априорной информации, касающейся передачи или связанной передачи; и

средство для оценки гипотез посредством выполнения операций декодирования, которые заключают в себе исключение наборов декодированных битов, которые являются несогласованными с битовыми значениями, указываемыми посредством гипотез, и выбор, в качестве вывода, декодированных битов, соответствующих одной из гипотез.

18. Устройство по п.17, в котором средство для оценки гипотез содержит множество средств для декодирования, предоставляющих возможность параллельной оценки множества гипотез.

19. Устройство по п.17, в котором средство для оценки гипотез содержит средство последовательного декодирования для последовательного декодирования множества гипотез.

20. Устройство по п.19, дополнительно содержащее:

средство для сохранения параметров качества, указывающих качество результатов декодирования, полученных с помощью различных гипотез; и

средство для выбора результатов, соответствующих наивысшему качеству декодирования, на основе сохраненных параметров качества.

21. Устройство по п.19, дополнительно содержащее:

средство для сравнения результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез; и

средство для выбора, в качестве вывода, декодированных битов, соответствующих одной из гипотез, на основе сравнения.

22. Устройство по п.21, в котором средство для сравнения результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез, содержит

средство для сравнения, по меньшей мере, одного из значений накопленного расстояния и значений вероятности.

23. Машиночитаемый носитель информации, имеющий набор инструкций, сохраненных на нем, для декодирования кодированных битов данных передачи беспроводной связи, причем набор инструкций содержит:

инструкции для формирования набора априорных битовых значений, соответствующих известным битовым значениям кодированных битов данных;

инструкции для удаления, из совокупности возможных трактов декодирования, трактов декодирования, которые соответствуют битам декодированных данных, которые являются несогласованными с набором априорных битовых значений; и

инструкции для декодирования кодированных битов данных посредством выбора тракта декодирования из оставшихся трактов декодирования для возможных трактов декодирования, которые не удалены.

24. Машиночитаемый носитель информации по п.23, в котором инструкции для оценки гипотез содержат множество средств для декодирования, предоставляющих возможность параллельной оценки множества гипотез.

25. Машиночитаемый носитель информации по п.23, в котором инструкции для оценки гипотез содержат средство последовательного декодирования для последовательного декодирования множества гипотез.

26. Машиночитаемый носитель информации по п.25, дополнительно содержащий:

инструкции для сохранения параметров качества, указывающих качество результатов декодирования, полученных с помощью различных гипотез; и

инструкции для выбора результатов, соответствующих наивысшему качеству декодирования, на основе сохраненных параметров качества.

27. Машиночитаемый носитель информации по п.23, дополнительно содержащий:

инструкции для сравнения результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез; и

инструкции для выбора, в качестве вывода, декодированных битов, соответствующих одной из гипотез, на основе сравнения.

28. Машиночитаемый носитель информации по п.27, в котором инструкции для сравнения результатов, полученных посредством операций декодирования с использованием битовых значений, указываемых посредством различных гипотез, содержат:

инструкции для сравнения, по меньшей мере, одного из значений накопленного расстояния и значений вероятности.

| Установка для размораживания блоков творога | 1987 |

|

SU1463207A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ПЕРЕДАННЫХ ИНФОРМАЦИОННЫХ СИГНАЛОВ ПОСЛЕ ПРОХОЖДЕНИЯ ИХ ЧЕРЕЗ КАНАЛ СВЯЗИ | 2001 |

|

RU2214690C2 |

| US 2007089037 A1, 19.04.2007 | |||

| US 2003009724 А1, 09.01.2003 | |||

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

Авторы

Даты

2012-05-27—Публикация

2008-07-17—Подача