Настоящее изобретение относится к цифровой вычислительной технике, а именно к высокоскоростным коммуникационным системам для высокопроизводительных многопроцессорных вычислительных систем с распределенной обработкой информации. Данное устройство предназначено, в частности, для применения при построении многопроцессорных вычислительных систем с распределенной архитектурой, используемых, в том числе, в бортовых вычислительных комплексах.

В качестве аналога из уровня техники известно устройство с параллельным коммуникационным интерфейсом [авт.свид. СССР №1211747. Устройство для сопряжения процессоров в многопроцессорной вычислительной системе / Горбачев С.В., Сакун Л.И. Заявлено 04.07.1984. Опубл. бюл. №6, 1986], содержащее блок передачи данных, блок приема данных, блок управления, блок определения готовности приемников, блок выделения приоритетного запроса.

В силу параллельного характера используемого коммуникационного интерфейса он имеет громоздкую физическую реализацию, так как кроме линий синхронизации содержит большое число линий приема и передачи данных. Возникающие проблемы со сдвигом по фазе синхросигнала и битов данных на множестве линий данных из-за их физической неоднородности приводят к тому, что известный параллельный интерфейс может использоваться на ограниченных расстояниях (до нескольких метров) и имеет ограниченное быстродействие. Таким образом, недостаток этого устройства состоит в ограниченной области применения, что вызвано ограничениями по длине и быстродействию, а также из-за большого энергопотребления при использовании параллельной синхронизации. Соответствующие ограничения присутствуют и в отношении надежности устройства.

Ближайшим аналогом к заявляемому устройству является устройство коммуникационного интерфейса [patent GB №91304711.4. Int. Cl.5 H04L 1/00. Communication interface for serial transmission of variable length data tokens / Priority 25.05.90, №9011700. Data of filing 24.05.91. Data of publication 27.11.91. Bulletin 91/48 of European Patent Office. Publication number 0458648 A2] для использования в коммуникационной системе, соединяющей как минимум два компьютера, причем устройство коммуникационного интерфейса, содержащее блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными входами блока управления и одноименными выходами блока приема данных, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства и соединен с одноименным входом блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, входы данных и стробирования которого являются соответственно входами данных и стробирования интерфейса устройства с каналом приема информации, выходы данных и стробирования интерфейса устройства с каналом выдачи информации являются соответственно выходами данных и стробирования блока выдачи данных, вход синхронизации выдачи данных которого является входом синхронизации выдачи данных системного интерфейса устройства, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, вход сброса системного интерфейса устройства является входом сброса блока управления, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, формирователь символа, блок DS-кодирования символа, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выход которого соединен с входом информационного символа блока арбитража выдачи символов, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком которого являются соответственно одноименными выходами блока выдачи данных, вход запроса на выдачу символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход сброса которого является входом сброса блока выдачи данных и соединен с входами сброса формирователя символа, блока DS-кодирования символа и буфера выдачи данных, вход готовности передачи данных которого соединен с одноименным выходом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом локальной синхронизации блока выдачи данных, выходы данных и стробирования которого являются одноименными выходами блока DS-кодирования символа, вход полного кода символа которого соединен с одноименным выходом формирователя символа; блок приема данных содержит первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь в параллельный код, буфер приема данных, дешифратор преобразованного кода, причем вход локальной синхронизации блока приема данных является входом синхронизации буфера приема данных и дешифратора преобразованного кода, выходы ошибки кодировки символа и подтверждение приема символа управления потоком которого являются одноименными выходами блока приема данных, выход данных для приема которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности данных для приема которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, информационный вход которого соединен с выходом данных дешифратора преобразованного кода, выход подтверждения приема информационного символа которого соединен с одноименным входом буфера приема данных и является одноименным выходом блока приема данных, вход сброса которого является входом сброса дешифратора преобразованного кода и соединен с входом сброса буфера приема данных, вход данных блока приема данных соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход стробирования блока приема данных соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

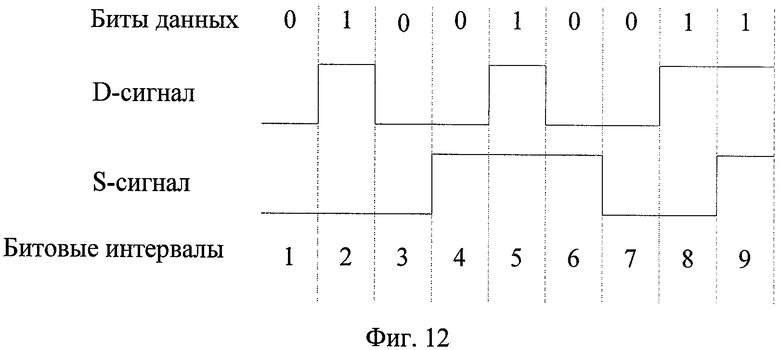

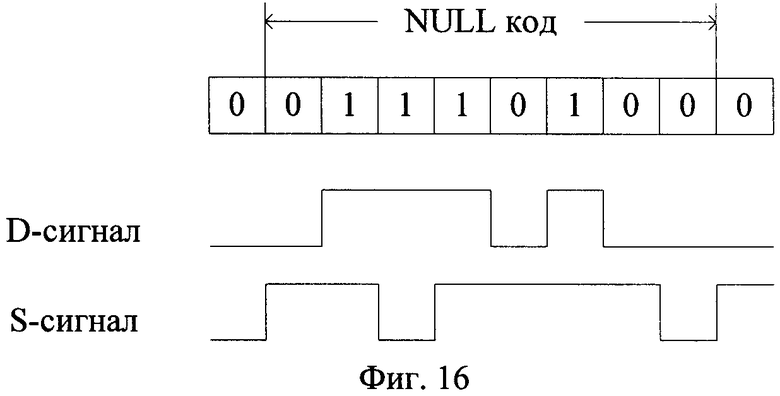

В данном устройстве использование DS-кодирования позволяет несколько снизить энергопотребление без снижения скоростных характеристик по сравнению с ранее известными аналогами за счет того, что в один момент времени может происходить изменение только одного сигнала, либо на линии стробирования S, либо на линии данных D коммуникационного интерфейса. Используемый в устройстве способ DS-кодирования характеризуется тем, что сигналы данных на линии данных D являются последовательным потоком битов данных, представляющих собой последовательность изменений сигнала только когда биты данных изменяют свое значение, в то время как сигнал строба на линии стробирования S изменяет значение только на границе битов в те моменты, когда сигнал данных не изменяет свое состояние, таким образом, исключая одновременные изменения в последовательном потоке сигналов данных и стробов. В блоке приема данных путем объединения D-сигнала и S-сигнала по функции ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR) формируется синхросигнал, изменяющий свое состояние в каждом битовом интервале, что позволяет его использование для приема сигналов данных с линии данных D и дальнейшей обработки битовых данных в устройстве коммуникационного интерфейса.

Недостатком этого устройства по-прежнему остается ограниченное быстродействие и относительно высокое энергопотребление. Это связано с тем, что все элементы устройства работают на одной локальной частоте, на которой осуществляется как выдача битовых данных, так и их прием, и последующее распознавание символа данных. Поэтому возможность повышения быстродействия устройства значительно ограничивается из-за пропорционального роста энергопотребления элементов всего устройства. При этом в домене формирования синхросигнала для приема битов данных имеет место эффект «завала фронтов» синхросигнала, поскольку он вырабатывается по функции XOR из сигналов с входных линий D и S коммуникационного интерфейса. В силу большой протяженности этих линий (порядка нескольких метров) они обладают значительными паразитными емкостями и индуктивностями, которые вызывают завал фронтов D- и S-сигналов. С другой стороны, формируемый в приемнике устройства синхросигнал имеет длинный путь (clock path), так как вырабатывается на основе D- и S-сигналов, поступающих из передатчика другого устройства через коммуникационный канал, что ограничивает возможность уменьшения периода изменения сигналов. Эти причины не позволяют повысить скорость передачи данных и существенно ограничивают быстродействие всего устройства коммуникационного интерфейса. В свою очередь, наличие в схеме устройства синхросигналов с продолжительным временем перехода от одного уровня к другому, в течение которого происходит дополнительное рассеивание энергии на триггерах и логических элементах, приводит к излишнему росту энергопотребления. Это сужает область применения устройства и, в частности, ограничивает использование в бортовых системах и для встраиваемых применений. Это также приводит к тому, что соответствующие ограничения присутствуют и в отношении надежности устройства.

Техническим результатом предлагаемого изобретения является расширение области применения устройства за счет снижения энергопотребления и обеспечения возможности повышения быстродействия путем минимизации числа триггеров и других элементов устройства, работающих на частоте передачи данных, более высокой по сравнению с локальной частотой, а также вследствие устранения завала фронтов синхросигнала при приеме битов данных и повышения скорости распознавания символов данных из потока принимаемых битов данных. Также имеет место в качестве технического результата возможность относительного повышения надежности устройства.

Технический результат достигается тем, что в предложенном устройстве коммуникационного интерфейса, содержащем блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными входами блока управления и одноименными выходами блока приема данных, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства и соединен с одноименным входом блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, входы данных и стробирования которого являются соответственно входами данных и стробирования интерфейса устройства с каналом приема информации, выходы данных и стробирования интерфейса устройства с каналом выдачи информации являются соответственно выходами данных и стробирования блока выдачи данных, вход синхронизации выдачи данных которого является входом синхронизации выдачи данных системного интерфейса устройства, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, вход сброса системного интерфейса устройства является входом сброса блока управления, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, формирователь символа, блок DS-кодирования символа, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выход которого соединен с входом информационного символа блока арбитража выдачи символов, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком которого являются соответственно одноименными выходами блока выдачи данных, вход запроса на выдачу символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход сброса которого является входом сброса блока выдачи данных и соединен с входами сброса формирователя символа, блока DS-кодирования символа и буфера выдачи данных, вход готовности передачи данных которого соединен с одноименным выходом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом локальной синхронизации блока выдачи данных, выходы данных и стробирования которого являются одноименными выходами блока DS-кодирования символа, вход полного кода символа которого соединен с одноименным выходом формирователя символа; блок приема данных содержит первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь в параллельный код, буфер приема данных, дешифратор преобразованного кода, причем вход локальной синхронизации блока приема данных является входом синхронизации буфера приема данных и дешифратора преобразованного кода, выходы ошибки кодировки символа и подтверждение приема символа управления потоком которого являются одноименными выходами блока приема данных, выход данных для приема которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности данных для приема которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, информационный вход которого соединен с выходом данных дешифратора преобразованного кода, выход подтверждения приема информационного символа которого соединен с одноименным входом буфера приема данных и является одноименным выходом блока приема данных, вход сброса которого является входом сброса дешифратора преобразованного кода и соединен с входом сброса буфера приема данных, вход данных блока приема данных соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход стробирования блока приема данных соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, введено соединение входа локальной синхронизации системного интерфейса устройства с входами локальной синхронизации блока управления, блока управления потоком данных, блока приема данных, блока выдачи данных, вход разрешения передачи символов управления потоком которого соединен с одноименным выходом блока управления, выход ошибки рассоединения блока приема данных соединен с одноименным входом блока управления и является выходом ошибки рассоединения системного интерфейса устройства, выход установления соединения системного интерфейса устройства является выходом установления соединения блока приема данных и соединен с одноименным входом блока управления, причем в блок приема данных введены блок формирования сигналов, детектор рассоединения, блок преобразования кода, детектор начала приема и блок перехода временного домена, в блок выдачи данных введен буфер передачи символов, вход локальной синхронизации которого соединен с входом локальной синхронизации блока выдачи данных, вход разрешения передачи символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход синхронизации выдачи данных блока выдачи данных является одноименным входом буфера передачи символов и соединен с входами синхронизации формирователя символа и блока DS-кодирования символа, вход сброса блока выдачи данных соединен с одноименным входом буфера передачи символов, выход готовности передачи символов которого соединен с одноименным входом блока арбитража выдачи символов, выходы записи и символов которого соединены соответственно с одноименными входами буфера передачи символов, выход которого соединен с информационным входом формирователя символа, выходы длины символа и записи длины символа которого соединены соответственно с одноименными входами блока DS-кодирования символа, выход готовности передачи символа которого соединен с одноименными входами формирователя символа и буфера передачи символов; выход ошибки рассоединения блока приема данных является выходом детектора рассоединения, управляющий вход которого соединен с выходом признака изменения уровня первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с входом синхронизации блока формирования сигналов и входом синхронизации детектора начала приема, выход корректировки фронта синхросигнала которого соединен с одноименным входом блока формирования сигналов, вход разрешения синхронизации которого соединен с одноименным выходом детектора начала приема и является выходом установления соединения блока приема данных, информационный выход и выход готовности преобразователя в параллельный код соединены соответственно с одноименными входами блока перехода временного домена, информационный выход и выход разрешения которого соединены соответственно с информационным входом и входом разрешения блока преобразования кода, выходы параллельного кода слова данных и разрядности слова данных которого соединены соответственно с одноименными входами дешифратора преобразованного кода, выход числа дешифрируемых битов которого соединен с одноименным входом блока преобразования кода, вход синхронизации которого соединен с входами синхронизации блока перехода временного домена, детектора рассоединения, детектора начала приема и входом локальной синхронизации блока приема данных, вход данных которого соединен с входом сигнала данных блока формирования сигналов и с информационным входом детектора начала приема, вход сброса блока приема данных соединен с управляющим входом детектора начала приема и с входами сброса детектора рассоединения, блока преобразования кода и блока формирования сигналов, выход битов данных которого соединен с одноименным входом преобразователя в параллельный код, вход синхронизации которого соединен с выходом сигнала синхронизации блока формирования сигналов.

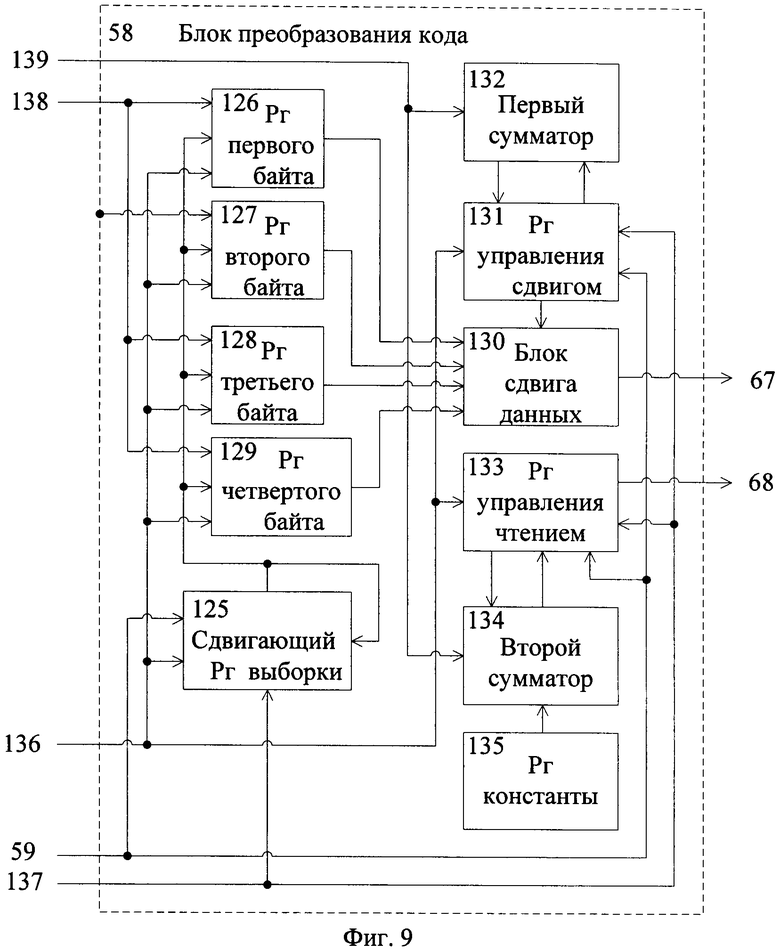

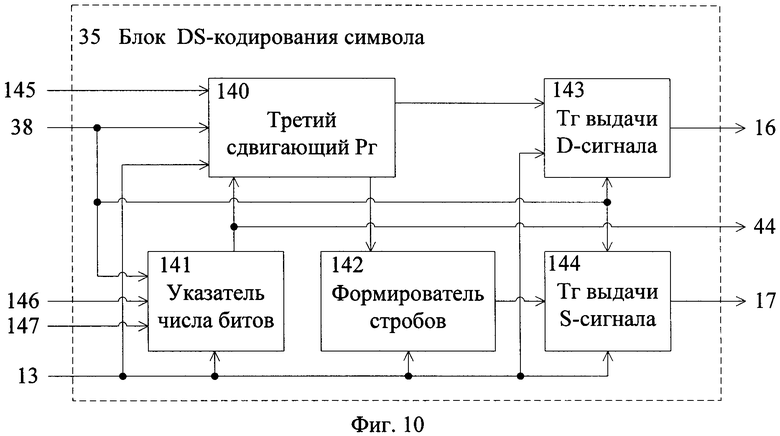

Предпочтительно, блок формирования сигналов содержит триггер первого бита, триггер второго бита, регистр выделенных сигналов, первый триггер деления частоты, второй триггер деления частоты, первый элемент НЕ, второй элемент НЕ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом синхронизации регистра выделенных сигналов и является выходом сигнала синхронизации блока формирования сигналов, вход синхронизации которого соединен с одноименными входами триггеров первого и второго битов, первого и второго триггеров деления частоты, вход сигнала данных блока формирования сигналов соединен с входами данных триггеров первого и второго битов, вход разрешения синхронизации блока формирования сигналов является входом разрешения регистра выделенных сигналов, входы первого и второго битов соединены соответственно с выходами триггеров первого и второго битов, выход регистра выделенных сигналов является выходом битов данных блока формирования сигналов, вход корректировки фронта синхросигнала которого является первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом первого триггера деления частоты и с входом первого элемента НЕ, выход которого соединен с входом данных первого триггера деления частоты, вход сброса которого является входом сброса блока формирования сигналов и соединен с одноименным входом второго триггера деления частоты, выход которого соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом второго элемента НЕ, выход которого соединен с входом данных второго триггера деления частоты. Блок преобразования кода содержит сдвигающий регистр выборки, регистр первого байта, регистр второго байта, регистр третьего байта, регистр четвертого байта, блок сдвига данных, регистр управления сдвигом, первый сумматор, регистр управления чтением, второй сумматор, регистр константы, выход которого соединен с первым входом сложения второго сумматора, выход которого соединен с информационным входом регистра управления чтением, выход состояния которого соединен со вторым входом сложения второго сумматора, вход вычитания которого является входом числа дешифрируемых битов блока преобразования кода и соединен с первым входом сложения первого сумматора, второй вход сложения которого соединен с выходом состояния регистра управления сдвигом, информационный вход которого соединен с выходом первого сумматора, управляющий выход регистра управления сдвигом соединен с управляющим входом блока сдвига данных, выход которого является выходом параллельного кода слова данных блока преобразования кода, вход сброса которого соединен с одноименными входами регистра управления сдвигом, регистра управления чтением и сдвигового регистра выборки, вход синхронизации которого является входом синхронизации блока преобразования кода и соединен с одноименными входами регистров первого, второго, третьего и четвертого байтов, регистра управления сдвигом и регистра управления чтением, выход разрядности слова данных которого является одноименным выходом блока преобразования кода, вход разрешения которого соединен с разрешающими входами регистра управления сдвигом, регистра управления чтением и сдвигающего регистра выборки, выход которого соединен с собственным последовательным входом, с входами выборки регистров первого, второго, третьего и четвертого байтов, информационные входы которых соединены с информационным входом блока преобразования кода, выходы регистров первого, второго, третьего и четвертого байтов соединены соответственно с первым, вторым, третьим и четвертым информационными входами блока сдвига данных.

Предлагаемое изобретение предназначено для организации высокоскоростного обмена информацией между процессорными узлами или компьютерами по дуплексному последовательному коммуникационному каналу, образованному симплексными каналами выдачи и приема информации, и может быть использовано при создании высокопроизводительных многопроцессорных вычислительных систем для применения в широких областях, требующих пониженного энергопотребления и повышения быстродействия. В предлагаемом техническом решении обеспечивается возможность для повышения скорости передачи данных через коммуникационный канал, то есть выдачи и приема данных в устройстве коммуникационного интерфейса при одновременном ограничении роста энергопотребления за счет разделения всех элементов устройства на два временных домена. Первый временной домен, в который включены элементы устройства, осуществляющие подготовку выдаваемых символов данных и обработку принимаемых символов данных, работает на частоте локальной синхронизации устройства. Второй временной домен включает элементы устройства, непосредственно осуществляющие выдачу и работающие на частоте выдачи данных в коммуникационный интерфейс, а также элементы устройства, непосредственно обеспечивающие прием битов данных и работающие на частоте принимаемых сигналов из коммуникационного интерфейса. Для повышения пропускной способности коммуникационного интерфейса частота выдачи данных может быть увеличена в несколько раз по сравнению с частотой локальной синхронизации. Поскольку в данном техническом решении имеется возможность минимизировать число триггеров, работающих на максимальной частоте передачи данных, то это способствует снижению потребляемой мощности по сравнению с прототипом при одинаковых значениях скорости передачи данных. Уменьшение задержек при приеме данных за счет формирования внутренних синхросигналов без завала фронтов и одновременного выделения двух смежных битов из входной линии данных способствует увеличению скорости приема данных и снижению потребляемой мощности. Возможность декодирования из последовательности принимаемых битов данных более одного символа за один такт локальной частоты обеспечивает повышение скорости приема данных и способствует выравниванию скорости приема со скоростью выдачи бит данных. Это является одним из факторов, способствующих снижению частоты локальной синхронизации по отношению к частоте выдачи данных, что приводит к уменьшению энергопотребления при обеспечении возможности одновременного увеличения скорости передачи битов данных в коммуникационном канале по сравнению с прототипом. Таким образом, данное устройство может быть эффективно использовано для создания распределенных бортовых вычислительных комплексов, а также в различных встраиваемых применениях. Отдельные элементы устройства могут быть реализованы стандартными средствами из данной области техники, при этом только системное решение, предложенное в рамках настоящего изобретения, позволяет достигнуть соответствующего технического результата.

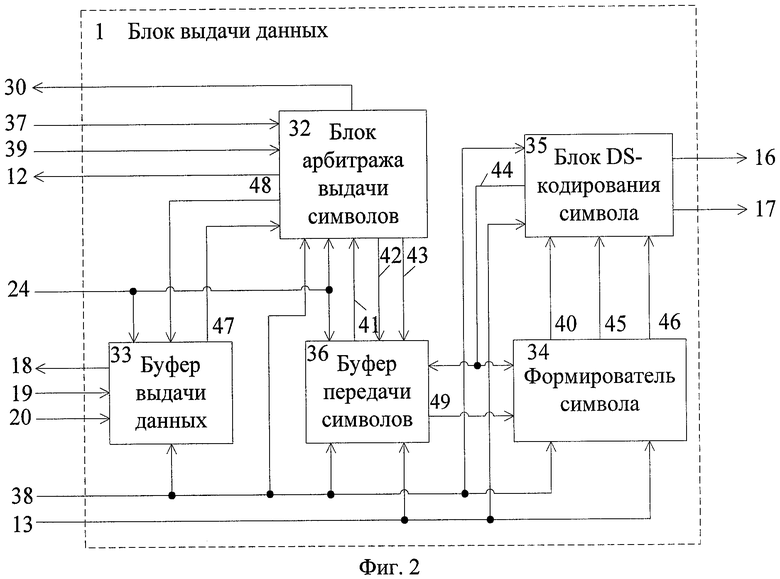

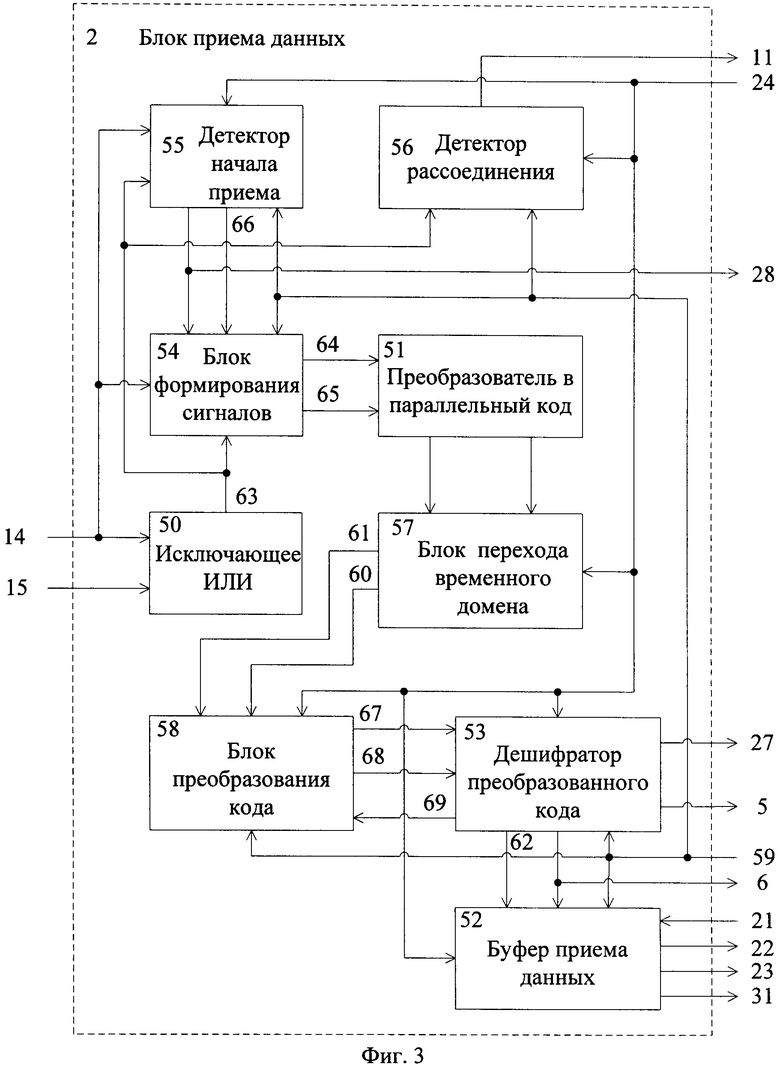

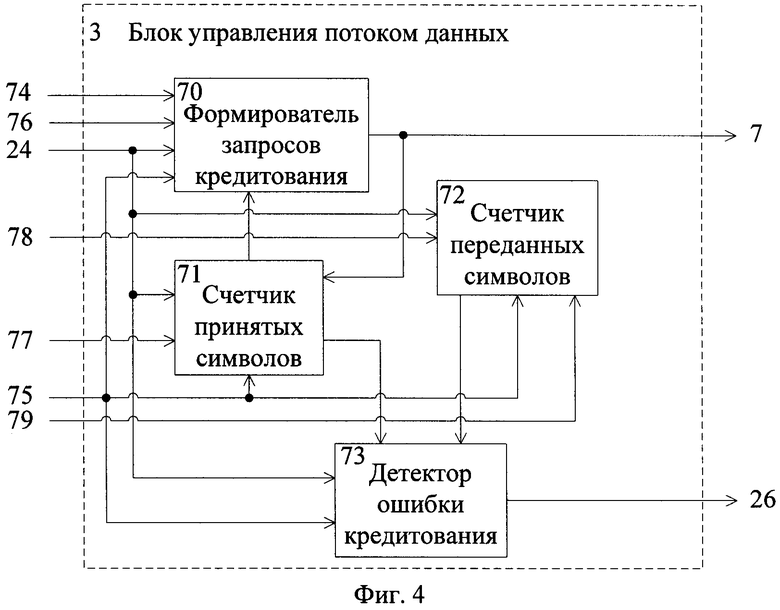

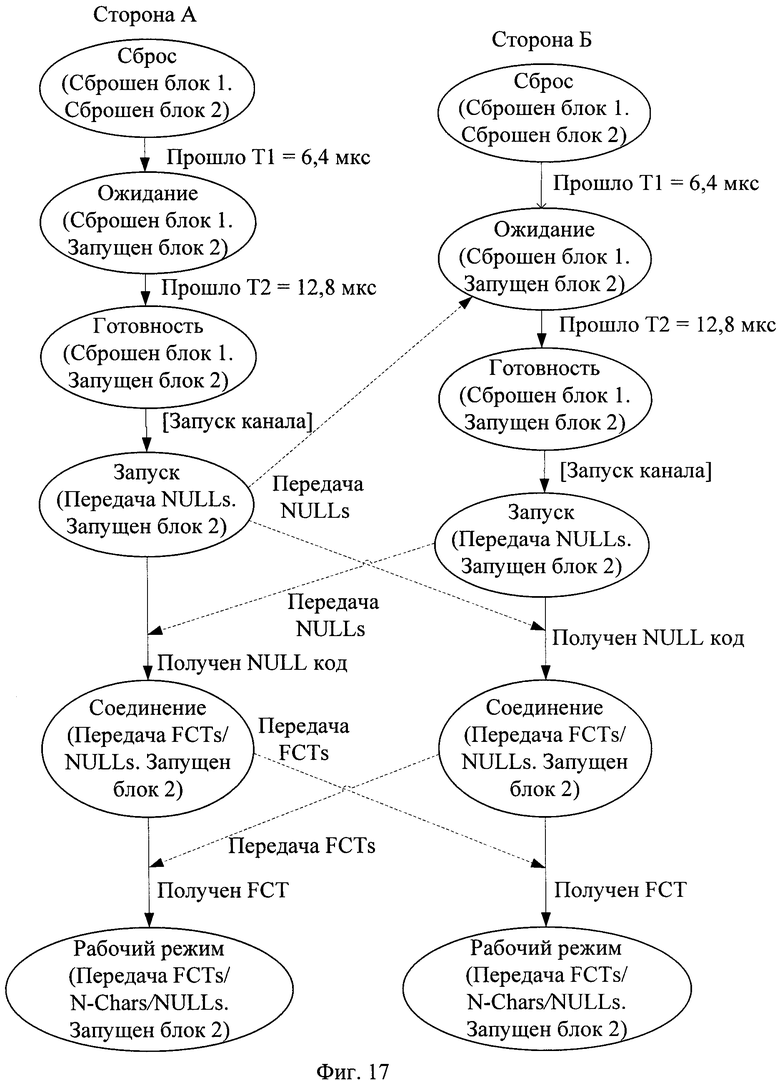

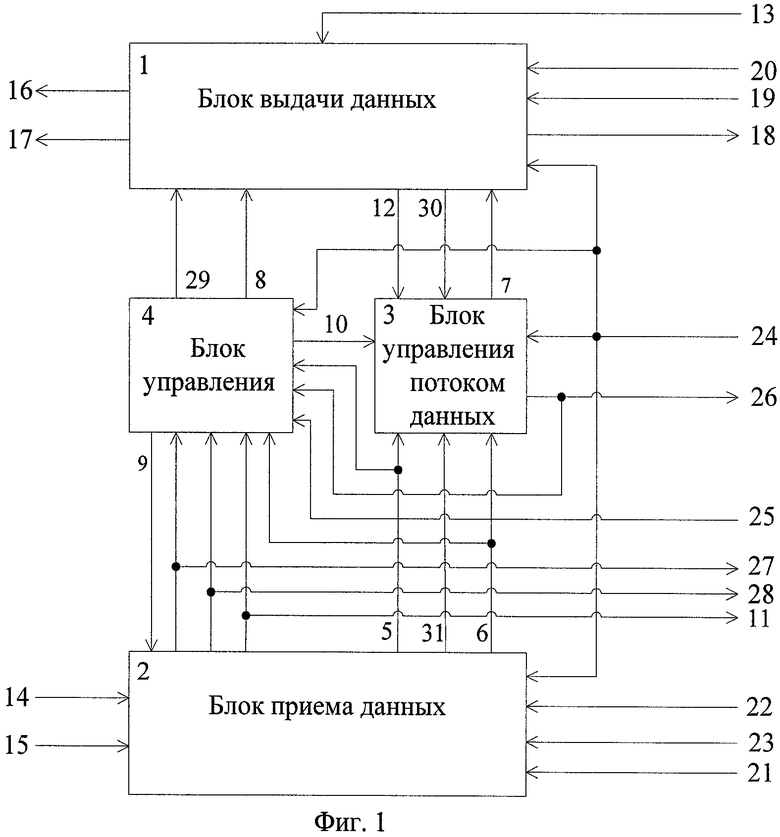

Детально сущность данного технического решения поясняется описанием со ссылками на чертежи, где на фиг.1 представлена структурная схема устройства, на фиг.2 - функциональная схема блока выдачи данных, на фиг.3 - функциональная схема блока приема данных. На фиг.4 и фиг.5 представлены возможные варианты реализации функциональных схем блока управления потоком данных и блока управления. На фиг.6 показана функциональная схема блока формирования сигналов. На фиг.7 приведена возможная реализация функциональной схемы детектора начала приема. На фиг.8 приведен пример реализации детектора рассоединения. На фиг.9 приведена структура блока преобразования кода. На фиг.10 представлена возможная реализация структуры блока DS-кодирования символа. На фиг.11 приведен граф машины состояния, описывающий режимы функционирования устройства. На фиг.12 показаны временные диаграммы, поясняющие правила формирования при DS-кодировании D- и S-сигналов в коммуникационном интерфейсе устройства. На фиг.13 показаны временные диаграммы, поясняющие работу блока формирования сигналов. На фиг.14 показаны временные диаграммы, поясняющие работу детектора рассоединения. На фиг.15 показаны области смежных символов, охватываемые битами контроля символа. На фиг.16 показаны сигналы данных и стробирования в момент запуска устройства. На фиг.17 проиллюстрирован пример графа переходов при инициализации взаимодействия через коммуникационный канал между двумя устройствами.

Как показано на фиг.1, предлагаемое устройство содержит блок 1 выдачи данных, блок 2 приема данных, блок 3 управления потоком данных, блок 4 управления, выход 5 подтверждения приема символа управления потоком, выход 6 подтверждения приема информационного символа, выход 7 запроса на выдачу символа управления потоком, первый выход 8 сброса, второй выход 9 сброса, третий выход 10 сброса, выход 11 ошибки рассоединения, выход 12 готовности выдачи символа управления потоком, вход 13 синхронизации выдачи данных, входы 14 данных и 15 стробирования, выходы 16 данных и 17 стробирования, выход 18 готовности выдачи данных, вход 19 записи, вход 20 данных для выдачи, вход 21 чтения данных, выход 22 данных для приема, выход 23 готовности данных для приема, вход 24 локальной синхронизации, вход 25 сброса, выход 26 ошибки кредитования, выход 27 ошибки кодировки символа, выход 28 установления соединения, выход 29 разрешения передачи символа управления потоком, выход 30 подтверждения выдачи информационного символа, выход 31 разрешения приема данных.

Блок 1 выдачи данных содержит (см. фиг.2) блок 32 арбитража выдачи символов, буфер 33 выдачи данных, формирователь 34 символа, блок 35 DS-кодирования символа, буфер 36 передачи символов, выход 30 подтверждения выдачи информационного символа, вход 37 разрешения передачи символа управления потоком, вход 38 сброса, выходы 16 данных и 17 стробирования, вход 39 запроса на выдачу символа управления потоком, выходы 12 готовности выдачи символа управления потоком и 18 готовности выдачи данных, входы 19 записи и 20 данных для выдачи, входы 13 синхронизации выдачи данных и 24 локальной синхронизации, выход 40 полного кода символа, выход 41 готовности передачи символов, выход 42 записи, выход 43 символа, выход 44 готовности передачи символа, выход 45 длины символа, выход 46 записи длины символа, выход 47 буфера 33 выдачи данных, выход 48 готовности передачи данных, выход 49 буфера 36 передачи символов.

Блок 2 приема данных содержит (см. фиг.3) первый элемент 50 ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь 51 в параллельный код, буфер 52 приема данных, дешифратор 53 преобразованного кода, блок 54 формирования сигналов, детектор 55 начала приема, детектор 56 рассоединения, блок 57 перехода временного домена, блок 58 преобразования кода, входы 14 данных и 15 стробирования, выход 27 ошибки кодировки символа, выходы 22 данных для приема и 23 готовности данных для приема, вход 21 чтения данных, выход 11 ошибки рассоединения, вход 24 локальной синхронизации, вход 59 сброса, информационный выход 60, выход 61 разрешения, выход 62 данных, выход 63 признака изменения уровня, выход 64 битов данных, выход 65 сигнала синхронизации, выход 28 установления соединения, выход 66 корректировки фронта синхросигнала, выход 67 параллельного кода слова данных, выход 68 разрядности слова данных, выход 69 числа дешифрируемых битов, выход 5 подтверждение приема символа управления потоком, выход 6 подтверждения приема информационного символа, выход 31 разрешения приема данных.

Блок 3 управления потоком данных содержит (см. фиг.4) формирователь 70 запросов кредитования, счетчик 71 принятых символов, счетчик 72 переданных символов, детектор 73 ошибки кредитования, вход 74 разрешения приема данных, вход 75 сброса, вход 76 готовности выдачи символа управления потоком, вход 24 локальной синхронизации, вход 77 подтверждения приема информационного символа, вход 78 подтверждения приема символа управления потоком, вход 79 подтверждения выдачи информационного символа, выход 7 запроса на выдачу символа управления потоком, выход 26 ошибки кредитования.

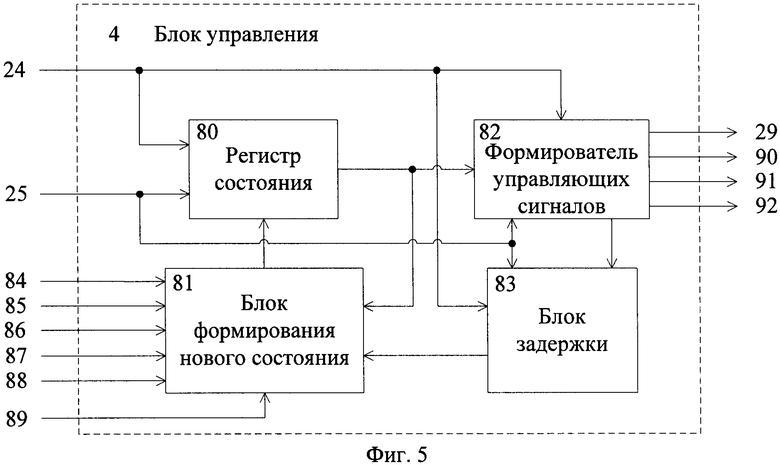

Блок 4 управления содержит (см. фиг.5) регистр 80 состояния, блок 81 формирования нового состояния, формирователь 82 управляющих сигналов, блок 83 задержки, вход 24 локальной синхронизации, вход 25 сброса, вход 84 установления соединения, вход 85 ошибки кредитования, вход 86 ошибки рассоединения, вход 87 ошибки кодировки символа, первый выход 90 сброса, второй выход 91 сброса, третий выход 92 сброса, вход 88 подтверждения приема символа управления потоком, вход 89 подтверждения приема информационного символа, выход 29 разрешения передачи символа управления потоком.

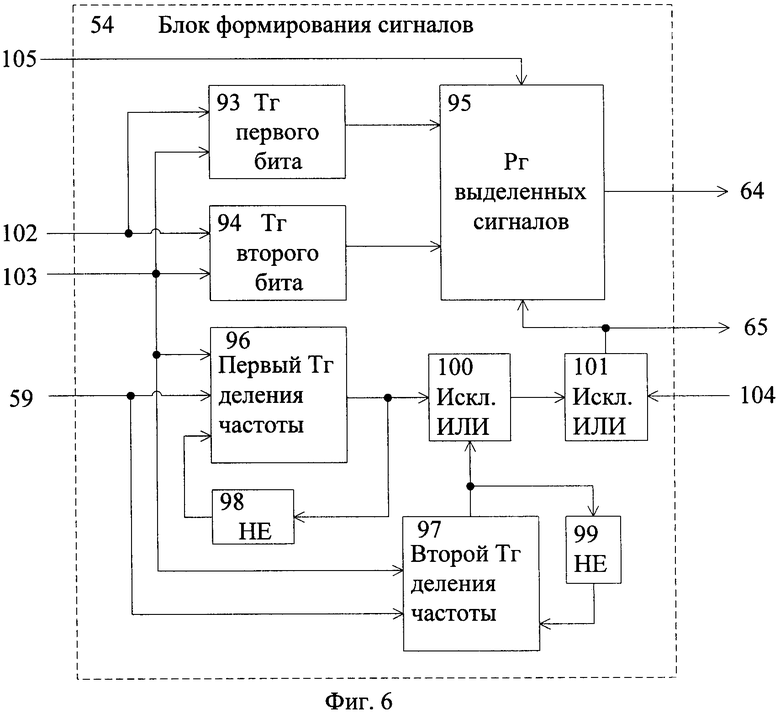

Блок 54 формирования сигналов содержит (см. фиг.6) триггер 93 первого бита, триггер 94 второго бита, регистр 95 выделенных сигналов, первый триггер 96 деления частоты, второй триггер 97 деления частоты, первый элемент 98 НЕ, второй элемент 99 НЕ, второй элемент 100 ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент 101 ИСКЛЮЧАЮЩЕЕ ИЛИ, вход 59 сброса, вход 102 сигнала данных, вход 103 синхронизации, вход 104 корректировки фронта синхросигнала, вход 105 разрешения синхронизации, выход 64 битов данных, выход 65 сигнала синхронизации.

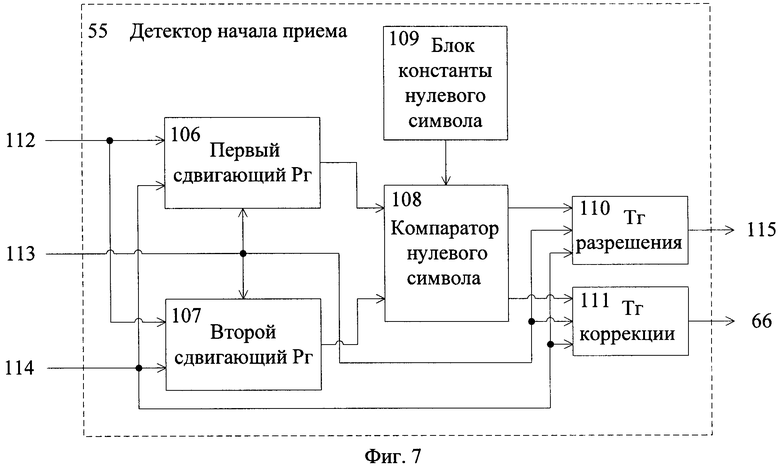

Детектор 55 начала приема содержит (см. фиг.7) первый сдвигающий регистр 106, второй сдвигающий регистр 107, компаратор 108 нулевого символа, блок 109 константы нулевого символа, триггер 110 разрешения, триггер 111 коррекции, информационный вход 112, вход 113 синхронизации, управляющий вход 114, выход 115 разрешения синхронизации, выход 66 корректировки фронта синхросигнала.

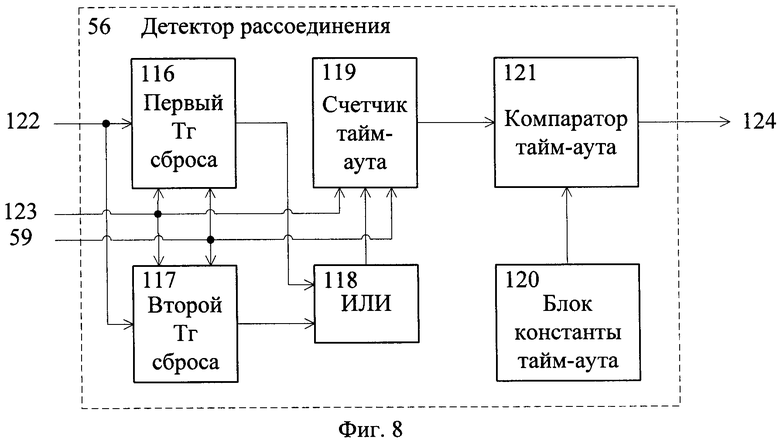

Детектор 56 рассоединения содержит (см. фиг.8) первый 116 и второй 117 триггеры сброса, счетчик 119 тайм-аута, компаратор 121 тайм-аута, блок 120 константы тайм-аута, элемент 118 ИЛИ, триггер 266 ошибки, вход 59 сброса, управляющий вход 122, вход синхронизации 123, выход 124 детектора.

Блок 58 преобразования кода содержит (см. фиг.9) сдвигающий регистр 125 выборки, регистр 126 первого байта, регистр 127 второго байта, регистр 128 третьего байта, регистр 129 четвертого байта, блок 130 сдвига данных, регистр 131 управления сдвигом, первый сумматор 132, регистр 133 управления чтением, второй сумматор 134, регистр 135 константы, вход 59 сброса, вход 136 синхронизации, вход 137 разрешения, информационный вход 138, вход 139 числа дешифрируемых битов, выход 67 параллельного кода слова данных, выход 68 разрядности слова данных.

Блок 35 DS-кодирования символа содержит (см. фиг.10) третий сдвигающий регистр 140, указатель 141 числа битов, формирователь 142 строба, триггер 143 выдачи D-сигнала, триггер 144 выдачи S-сигнала, вход 38 сброса, вход 145 полного кода символа, вход 146 длины символа, вход 147 записи длины символа, вход 13 синхронизации выдачи данных, выход 16 данных, выход 17 стробирования, выход 44 готовности передачи символа.

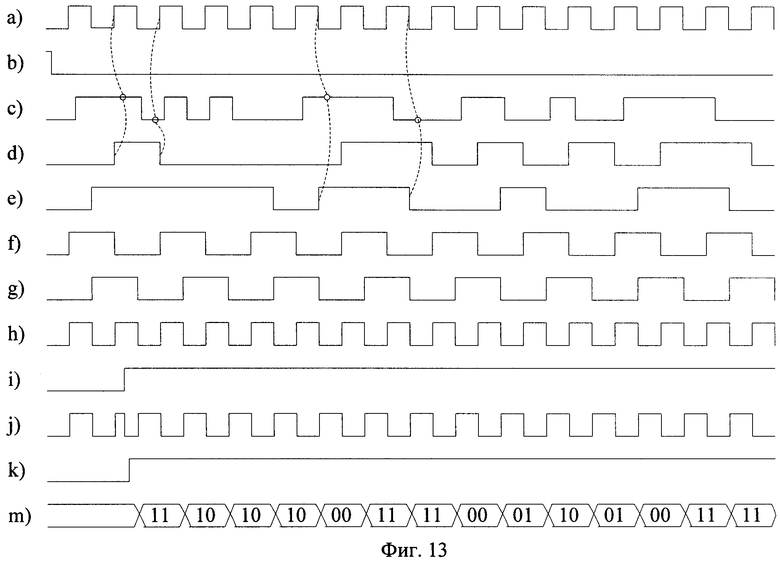

На временных диаграммах (см. фиг.13) для блока 54 формирования сигналов показано: а - изменение сигнала на входе 102 синхронизации, b - состояние сигнала на входе 59 сброса, с - изменение сигнала на входе 101 сигнала данных, d - изменение состояния выхода триггера 93 первого бита, е - изменение состояния выхода триггер 94 второго бита, f - изменение сигнала на выходе первого триггера 96 деления частоты, g - изменение сигнала на выходе второго триггера 97 деления частоты, h - состояние сигнала на выходе второго элемента 100 ИСКЛЮЧАЮЩЕЕ ИЛИ, i - изменение сигнала на входе 103 корректировки фронта синхросигнала, j - изменение сигнала на выходе 65 сигнала синхронизации, k - состояние сигнала на входе 105 разрешения синхронизации, m - состояние сигнала на выходе 64 битов данных.

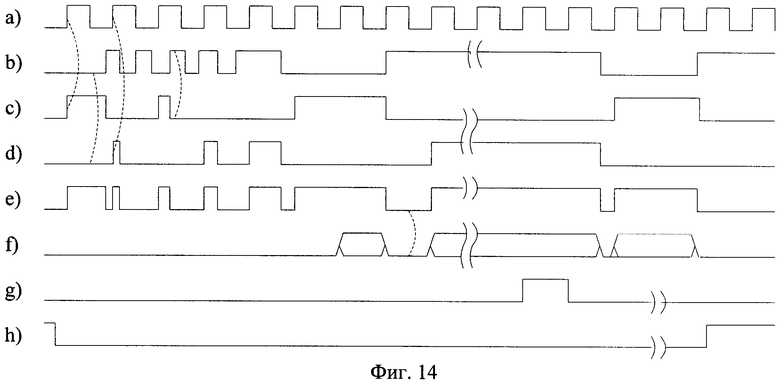

На временных диаграммах (см. фиг.14) для детектора 56 рассоединения показано: а - изменение сигнала на входе 123 синхронизации детектора, b - состояние сигнала на управляющем входе 122 детектора, с - изменение сигнала на выходе первого триггера 116 сброса, d - изменение состояния выхода второго триггера 117 сброса, е - изменение состояния выхода элемента 118 ИЛИ, f - изменение сигнала на выходе счетчика 119 тайм-аута, g - состояние сигнала на выходе 124 детектора, h - состояние сигнала на входе 59 сброса детектора.

Блок 1 выдачи данных предназначен для формирования и выдачи в коммуникационный интерфейс символов данных из пакетных данных, поступающих через вход данных для выдачи, соединенного с одноименным входом 20 устройства, являющимся частью системного интерфейса с хост-системой (компьютером), а также управляющих символов по требованию, поступающему с выхода 7 запроса на выдачу символа управления потоком блока 3 управления потоком данных на одноименный вход блока. Вход 19 записи системного интерфейса устройства является одноименным входом блока 1 выдачи данных, выход готовности выдачи данных которого является одноименным выходом 18 системного интерфейса устройства. Выход 18 и вход 19 системного интерфейса предназначены для реализации стандартного механизма записи пакетных данных в блок 1 выдачи данных из хост-системы. Запись пакетных данных в блок 1 тактируется с его входа синхронизации, соединенного с входом 24 локальной синхронизации системного интерфейса устройства. Выходы 12 готовности выдачи символа управления потоком и 30 подтверждения выдачи информационного символа блока 1 соединены с одноименными входами блока 3 управления потоком данных и предназначены для реализации механизма кредитования, необходимого для организации передачи и приема данных через коммуникационный интерфейс без переполнения буферов приема у взаимодействующих устройств. Блок 1 выдачи данных обеспечивает DS-кодирование символов данных, управляющих символов и кодов и их передачу на выходы 16 данных и 17 стробирования коммуникационного интерфейса устройства. Выдача данных осуществляется со скоростью, определяемой частотой синхросигнала с входа синхронизации выдачи данных блока 1, соединенного с одноименным входом 13 системного интерфейса устройства.

Блок 2 приема данных обеспечивает инициализацию соединения и получение битового потока от другого устройства через входы 14 данных и 15 стробирования коммуникационного интерфейса устройства, декодирование принятых сигналов и выделение из потока битов символов данных и их передачи в хост-систему через выход данных для приема, являющийся одноименным выходом 22 системного интерфейса устройства. Выход готовности данных для приема блока 2 приема данных является одноименным выходом 23 системного интерфейса устройства, вход 21 чтения данных которого является одноименным входом блока 2 приема данных. Блок 2 приема данных обеспечивает извещение блока 3 управления потоком данных через выход 5 приема символа управления потоком, соединенный с одноименным входом блока 3, о приеме управляющего символа управления потоком и через выход 6 подтверждения приема информационного символа, соединенный с одноименным входом блока 3, о получении извне информационного символа. Блок 2 приема данных обеспечивает формирование сигналов ошибок и выдачу их через выход ошибки рассоединения, соединенный с одноименным входом блок 4 управления и являющийся выходом 11 системного интерфейса устройства, и через выход ошибки кодировки символа, соединенный с одноименным входом блок 4 управления и являющийся выходом 27 системного интерфейса устройства. Выход установления соединения блока 2 приема данных, соединенный с одноименным входом блока 4 управления и являющийся одноименным выходом 28 системного интерфейса устройства, предназначен для передачи сигнала об обнаружении контрольной последовательности битов, принятой из коммуникационного интерфейса от другого устройства. Выход 31 разрешения приема данных блока 2 приема данных, соединенный с одноименным входом блока 3 управления потоком данных, предназначен для извещения о наличии достаточного свободного пространства в буфере приема данных.

Блок 3 управления потоком данных предназначен для реализации механизма кредитования, необходимого при обмене пакетными данными в дуплексном режиме между двумя устройствами через коммуникационные интерфейсы с двунаправленным каналом, соединяющим эти два устройства, с учетом ограниченного объема буферной памяти для приема данных, имеющейся у каждого устройства в блоке 2 приема данных. Выход 7 запроса на выдачу символа управления потоком блока 3 управления потоком данных, соединенный с одноименным входом блока 1 выдачи данных, предназначен для инициализации выдачи блоком 1 выдачи данных управляющего символа управления потоком, подтверждающего наличие в блоке 2 приема данных свободного буферного пространства, необходимого для приема определенного числа символов данных. В описываемом устройстве величина кредита, предоставляемого при выдаче одного символа управления потоком, принята равной восьми. Выход ошибки кредитования блока 3 управления потоком данных соединен с одноименным входом блока 4 управления и является одноименным выходом 26 системного интерфейса устройства. Блок 3 управления потоком данных тактируется с входа синхронизации, соединенного с входом 24 локальной синхронизации системного интерфейса устройства.

Блок 4 управления предназначен для отслеживания состояния устройства при поступлении из блока 2 приема данных сигналов об изменении его статуса и выработки управляющих сигналов под воздействием машины состояний и сигнала начальной установки с входа сброса, соединенного с входом 25 сброса системного интерфейса устройства. Выход 29 разрешения передачи символа управления потоком блока 4 управления соединен с одноименным входом блока 1 выдачи данных и предназначен для извещения о том, что машина состояния блока 4 управления перешла в режим, разрешающий выдачу символов управления потоком. Первый 8, второй 9 и третий 10 выходы сброса блока 4 управления соединены с входами сброса соответственно блока 1 выдачи данных, блока 2 приема данных и блока 3 управления потоком данных и предназначены для их перевода в начальное состояние. Тактирование блока 4 управления осуществляется с входа синхронизации, являющегося входом 24 локальной синхронизации системного интерфейса устройства.

В блоке 1 выдачи данных буфер 33 выдачи данных (см. фиг.2) предназначен для промежуточного хранения пакетных данных, поступающих на вход данных для выдачи буфера 33, соединенный с одноименным входом 20 блока 1 выдачи данных. Представление информации в пакете данных, поступающем из системного интерфейса устройства на этот вход блока 1 выдачи данных, показано в табл.1. Буфер 33 выдачи данных обеспечивает их выдачу вместе с запросом на передачу с выхода 47, соединенного с входом информационного символа блока 32 арбитража выдачи символов, по мере его готовности. Выход готовности выдачи данных буфера 33 выдачи данных, являющийся одноименным выходом 18 блока 1 выдачи данных, предназначен для уведомления о возможности буферизации очередного байта данных, которая осуществляется при подаче сигнала записи на вход записи буфера 33 выдачи данных, являющийся входом 19 записи блока 1 выдачи данных. Буферизация данных обеспечивается при тактировании с входа синхронизации буфера 33 выдачи данных, соединенного с входом 24 локальной синхронизации блока 1 выдачи данных, вход 38 сброса которого соединен с входом сброса буфера 33 выдачи данных и предназначен для его инициализации.

Блок 32 арбитража выдачи символов предназначен для регулирования формирования и порядка выдачи символов данных, управляющих символов и управляющих кодов по требованиям от блока 3 управления потоком данных в зависимости от заданного приоритета. С входа 39 запроса на выдачу символа управления потоком блока 1 выдачи данных, соединенного с одноименным входом блока 32, поступает требование выдачи управляющего символа управления потоком. Выход 48 готовности передачи данных блока 32 арбитража выдачи символов, соединенный с одноименным входом буфера 33 выдачи данных, предназначен для управления темпом поступления данных из буфера 33 для формирования внутреннего кода символов данных в блоке 32. Внутреннее кодирование загружаемых в буфер 36 символов показано в табл.2. Вход 37 разрешения передачи символа управления потоком блока 1 выдачи данных, являющийся одноименным входом блока 32 арбитража выдачи символов, предназначен для первоначального разрешения выдачи символов управления потоком после установления соединения с другим устройством. Выход готовности выдачи символа управления потоком блока 32, являющийся одноименным выходом 12 блока 1 выдачи данных, предназначен для извещения блока 3 управления потоком о возможности выдачи очередного символа управления потоком. Выход подтверждения выдачи информационного символа, являющийся одноименным выходом 30 блока 1 выдачи данных, предназначен для извещения блока 3 управления потоком о выдаче очередного информационного символа с целью управления кредитным счетчиком переданных символов. Выход 43 символа блока 32 арбитража выдачи символов, соединенный с входом символа буфера 36 передачи символов, и выход 42 записи блока 32, соединенный с входом записи буфера 36, обеспечивают загрузку необходимой информации о выдаваемом символе в буфер 36 передачи символов. Код типа символа сопровождается дополнительным битом (xor_bit), получаемым в блоке 32 как результат операции XOR над всеми битами выдаваемого символа. Кроме того, как показано в табл.2, тип символа данных сопровождается самим байтом данных. Тактирование блока 32 арбитража выдачи символов осуществляется с входа синхронизации, соединенного с входом 24 локальной синхронизации блока 1 выдачи данных, вход 38 сброса которого соединен с входом сброса блока 32 и предназначен для его инициализации.

Буфер 36 передачи символов предназначен для минимизации задержек при выдаче сформированных символов и кодов в канал и обеспечивает буферизацию очередных k (в описываемой реализации устройства k=4) символов, подготовленных для выдачи блоком 32 арбитража выдачи символов. Загрузка кода типа символов вместе с дополнительным битом и байтом данных для символа данных в буфер 36 обеспечивается по разрешающему сигналу на выходе 41 готовности передачи символа буфера 36, соединенного с одноименным входом блока 32 арбитража выдачи символов, при наличии тактирования на входе локальной синхронизации буфера 36, соединенного с одноименным входом 24 блока 1 выдачи данных. Выход 49 буфера 36 передачи символов соединен информационным входом формирователя 34 символа. Считывание кода типа символов из буфера 36 в формирователь 34 символа тактируется с входа синхронизации выдачи данных, являющегося одноименным входом 13 блока 1 выдачи данных, вход 38 сброса которого соединен с входом сброса буфера 36 и предназначен для его инициализации.

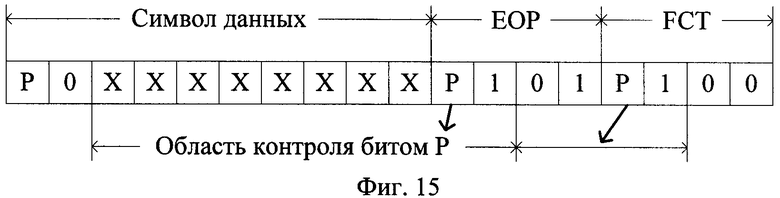

Формирователь 34 символа предназначен для образования полного кода символов в соответствии с типом символа, который считывается из буфера 36 передачи символов, и добавления бита контроля символа на четность. Форматы символов, передаваемых через коммуникационный интерфейс, приведены в табл.3. Бит контроля добавляется во все символы данных и управляющие символы для определения ошибок передачи по каналу. Бит контроля охватывает часть предыдущего символа (8 бит данных для символа данных или 2 бита кода для управляющего символа), бит контроля текущего символа и флаг управления текущего символа, как показано на фиг.15. Бит контроля символа выполняет проверку нечетности, его значение устанавливается таким образом, чтобы количество единиц в области, охватываемой этим битом (включая сам бит контроля), было нечетным. Полный код символа передается с выхода 40 полного кода символа формирователя 34 на одноименный вход блока 35 DS-кодирования символа, а его длина - с выхода 45 длины символа формирователя 34 на одноименный вход блока 35 DS-кодирования символа. Выход 46 записи длины символа соединен с одноименным входом блока 35. Считывание символов в блок 35 тактируется с входа синхронизации формирователя 34, являющегося входом 13 синхронизации выдачи данных блока 1 выдачи данных, вход 38 сброса которого соединен с входом сброса формирователя 34 и предназначен для его инициализации.

Блок 35 DS-кодирования символа обеспечивает кодированное представление полного кода символа, загружаемого из формирователя 34, в виде DS-кода, представляющего собой последовательность сигналов данных (D-сигналов), совпадающих по уровню с соответствующими битами данных и выдаваемых через выход данных, являющийся выходом 16 данных блока 1 выдачи данных, и сопровождающих их сигналов стробирования (S-сигналов), изменяющих свое состояние всякий раз, когда очередной D-сигнал не изменяет свое состояние по сравнению с предыдущим (см. фиг.12), и выдаваемых через выход стробирования, являющийся выходом 17 стробирования блока 1 выдачи данных.

Считывание очередного символа в формирователь 34 и из него в блок 35 обеспечивается при наличии сигнала на выходе 44 готовности передачи символа блока 35 DS-кодирования символа, соединенного с одноименными входами буфера 36 передачи символов и формирователя 34 символа. Сигнал на выходе 44 блока 35 свидетельствует о его готовности к получению следующего символа для последующего DS-кодирования и выдачи в канальный интерфейс. DS-кодирование символов и их выдача тактируется с входа синхронизации блока 35, являющегося входом 13 синхронизации выдачи данных блока 1 выдачи данных, вход 38 сброса которого соединен с входом сброса блока 35 и предназначен для его инициализации.

В блоке 2 приема первый элемент 50 ИСКЛЮЧАЮЩЕЕ ИЛИ (см. фиг.3) из входных сигналов данных, поступающих на первый вход, являющийся входом 14 данных блока 2 приема данных, и на второй вход, являющийся входом 15 стробирования блока 2 приема данных, обеспечивает формирование синхропоследовательности с изменением уровня сигнала в каждом битовом интервале, которая выдается на выход 63 признака изменения уровня, соединенный с входами синхронизации блока 54 формирования сигналов и детектора 55 начала приема и с управляющим входом детектора 56 рассоединения.

Блок 54 формирования сигналов предназначен для выработки внутренних синхроимпульсов на выходе 65 сигнала синхронизации, который соединен с входом синхронизации преобразователя 51 в параллельный код, и для формирования из последовательности сигналов данных, поступающих на одноименный вход с входа 14 данных блока 2 приема данных, двух смежных битов данных, которые одновременно выдаются на выход 64 битов данных, соединенный с одноименным входом преобразователя 51 в параллельный код.

Преобразователь 51 в параллельный код предназначен для формирования параллельного байтового кода данных, который формируется путем последовательного запоминания значений очередных двух битов данных, поступающих на вход битов данных, при наличии синхросигналов на входе синхронизации. Информационный выход преобразователя 51 в параллельный код соединен с одноименным входом блока 57 перехода временного домена. Выход готовности преобразователя 51, соединенный с одноименным входом блока 57, подтверждает окончание формирования очередного байта данных.

Блок 57 перехода временного домена обеспечивает разграничение двух временных доменов блока 2 приема данных, первый из которых работает на частоте принимаемых из коммуникационного интерфейса сигналов данных и стробирования, а второй домен - на частоте локальной синхронизации, задаваемой на входе 24 локальной синхронизации блока 2 приема данных из системного интерфейса устройства. Вход 24 локальной синхронизации блока 2 является входом синхронизации блока 57 перехода временного домена. Информационный выход 60 блока 57 перехода временного домена соединен с информационным входом блока 58 преобразования кода. Сигнал на выходе 61 разрешения блока 57, соединенном с одноименным входом блока 58 преобразования кода, информирует о наличии выдаваемого байта данных на информационном выходе 60.

Детектор 55 начала приема предназначен для начального запуска блока 2 приема данных при обнаружении стартовой последовательности битов (управляющего кода NULL, см. табл.3) на своем информационном входе, являющемся входом 14 данных блока 2 приема данных, вход 59 сброса которого является управляющим входом детектора 55. Выход 66 корректировки фронта синхросигнала детектора 55 начала приема соединен с одноименным входом блока 54 формирования сигналов. Выход разрешения синхронизации детектора 55 начала приема соединен с одноименным входом блока 54 формирования сигналов и является выходом 28 установления соединения блока 2 приема данных.

Детектор 56 рассоединения предназначен для определения превышения установленной величины задержки между изменениями сигнала на выходе 63 признака изменения уровня первого элемента 50 ИСКЛЮЧАЮЩЕЕ ИЛИ. При этом событии на выходе детектора 56, соединенном с выходом 11 блока 2 приема данных, устанавливается сигнал ошибки рассоединения. Детектор 56 тактируется через вход синхронизации, который соединен с входом 24 локальной синхронизации блока 2 приема данных, вход 59 сброса которого соединен с входом сброса детектора 56 рассоединения и предназначен для его инициализации.

Блок 58 преобразования кода обеспечивает накопление байтов, принятых с информационного выхода 60 блока 57 перехода временного домена при наличии сигнала на выходе 61 разрешения того же блока, и формирование из них k-байтового слова данных, которое в параллельном виде поступает на выход 67 параллельного кода слова данных, соединенный с одноименным входом дешифратора 53 преобразованного кода. Как показано на фиг.8, для блока 58 преобразования кода принято значение k=4. Выход 68 разрядности слова данных блока 58 соединен с одноименным входом дешифратора 53 преобразованного кода и предназначен для передачи двоичного кода, информирующего о числе действительно принятых и готовых к обработке бит 32-разрядного кода слова данных. В соответствии с информацией о числе действительно принятых и готовых к декодированию бит 32-разрядного кода данных, поступающей на вход числа дешифрируемых битов блока 58, последний обеспечивает сдвиг 32-разрядного слова данных на соответствующее число битов с тем, чтобы младшие разряды этого кода содержали очередные принятые биты еще не дешифрированных данных. Блок 58 преобразования кода тактируется с входа синхронизации, соединенного с входом 24 локальной синхронизации блока 2 приема данных, и переводится в начальное состояние по сигналу с входа сброса, соединенного с входом 59 сброса блока 2 приема данных.

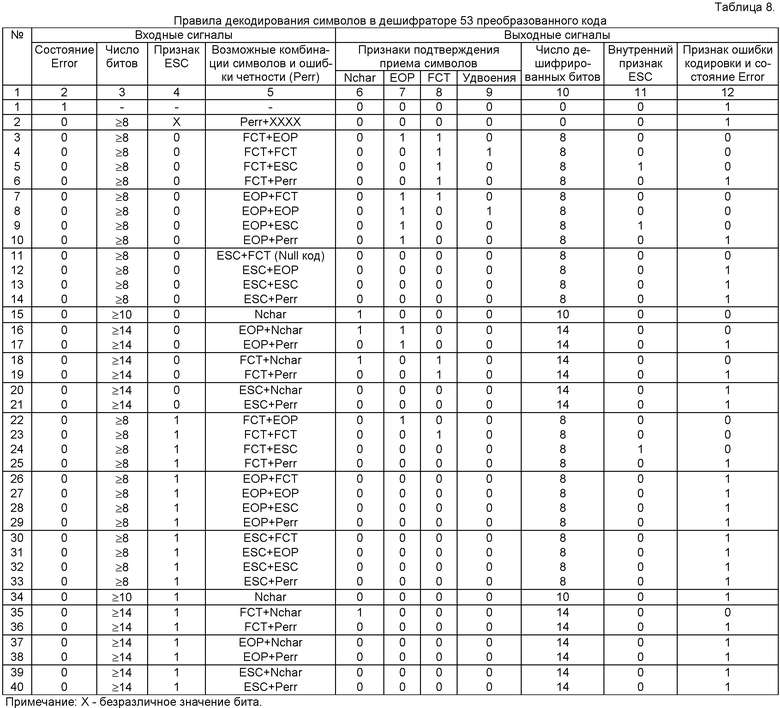

Дешифратор 53 преобразованного кода предназначен для распознавания в 32-разрядном коде, поступающем на его вход параллельного кода слова данных, символов данных, управляющих символов и кодов в соответствии с кодированием, показанным в табл.3, и выделении из них информационных и канальных символов.

Символы, передаваемые через коммуникационный интерфейс, подразделяются на канальные и информационные символы. К информационным символам относятся символ данных (Nchar) и символ конца пакета (ЕОР). Канальные символы (FCT, ESC) вместе с управляющим кодом NULL предназначены для управления состоянием коммуникационного канала и в системный интерфейс не передаются. NULL код предназначен для сохранения активности коммуникационного канала и постоянно передается, если канал не занят передачей других символов. Выход 62 данных дешифратора 53 преобразованного кода соединен с информационным входом буфера 52 приема данных и предназначен для передачи восьми битов данных, выделенных в дешифраторе 53 из Nchar, в буфер 52 приема данных. Выход подтверждения приема информационного символа дешифратора 53, соединенный с одноименным входом буфера 52 приема данных и являющийся одноименным выходом 6 блока 2 приема данных, предназначен для передачи следующих сигналов: признака подтверждения приема Nchar, признака подтверждения приема ЕОР и признака удвоения. Признак удвоения уточняет, принят один или два управляющих символа в одном такте (в данном случае - два символа ЕОР). Выход 69 числа дешифрируемых битов дешифратора 53 преобразованного кода соединен с одноименным входом блока 58 преобразования кода. Выход подтверждения приема символа управления потоком дешифратора 53, являющийся одноименным выходом 5 блока 2 приема данных, предназначен для выдачи признака подтверждения приема FCT, а также признака удвоения, который уточняет, принят ли один или подряд два управляющих символа в одном такте (в данном случае - двух символов FCT). Выход ошибки кодировки символа дешифратора 53 является одноименным выходом 27 блока 2 приема данных и обеспечивает выдачу сигнала о выявленной ошибке в кодировании символа в принятых данных. Дешифратор 53 преобразованного кода тактируется с входа синхронизации, соединенного с входом 24 локальной синхронизации блока 2 приема данных, и переводится в начальное состояние по сигналу с входа сброса, соединенного с входом 59 сброса блока 2 приема данных.

Буфер 52 приема данных предназначен для промежуточного запоминания принятых пакетов данных, поступающих на его информационный вход, при наличии разрешающей комбинации сигналов на входе подтверждения приема информационного символа. На выходе данных для приема буфера 52 приема данных, являющемся одноименным выходом 22 блока 2 приема данных и составной частью системного интерфейса устройства, обеспечивается побайтная выдача пакетов данных, разделенных признаками конца пакета. Разрешение записи в буфер 52 приема данных обеспечивается при наличии на входе подтверждения приема информационного символа хотя бы одного установленного в единицу управляющего флага (признака ЕОР или признака Nchar). Управляющие флаги, а именно, признак Nchar, предназначенный для уведомления о том, являются ли младшие восемь битов кода данных на информационном входе действительными пакетными данными, и признак ЕОР, указывающий, что байт данных, записанный в предыдущую ячейку буфера, является последним в пакете, также запоминаются в каждой ячейке памяти буфера 52. Выдача данных из буфера 52 приема данных обеспечивается по принципу «первым принят, первым считан» в сопровождении сигнала готовности данных на выходе готовности данных для приема, являющемся одноименным выходом 23 блока 2 приема данных, и при наличии установленного сигнала чтения данных на входе чтения буфера 52, являющегося входом 21 чтения данных блока 2 приема данных. Выход разрешения приема данных буфера 52 приема данных, являющийся одноименным выходом 31 блока 2 приема данных, индицирует о наличии определенного числа свободных ячеек в нем (в описываемом варианте - не менее восьми) и предназначен для управления механизмом кредитования. Буфер 52 приема данных тактируется по восходящему фронту синхросигнала с входа синхронизации, соединенного с входом 24 локальной синхронизации блока 2 приема данных, и переводится в начальное состояние по сигналу с входа сброса, соединенного с входом 59 сброса блока 2 приема данных.

В блоке 3 управления потоком данных (см. фиг.4) формирователь 70 запросов кредитования предназначен для выработки сигнала запроса на выдачу FCT символа на выходе 7 запроса на выдачу символа управления потоком блока при наличии разрешающих сигналов на входах 76 готовности выдачи символа управления потоком и 74 разрешения приема данных блока и в зависимости от состояния счетчика 71 принятых символов. Вход 74 разрешения приема данных блока 3 является первым входом формирователя 70. Вход 76 готовности выдачи символа управления потоком блока 3 является вторым входом формирователя 70. Выход состояния счетчика 71 принятых символов блока 3 является третьим входом формирователя 70. Вход 24 локальной синхронизации блока 3, соединенный с входами синхронизации формирователя 70 запросов кредитования, счетчика 71 принятых символов, счетчика 72 переданных символов и детектора 73 ошибки кредитования, обеспечивает синхронизацию их работы на локальной частоте. Вход 75 сброса блока 3 предназначен для установки исходного нулевого состояния и соединен с входами сброса формирователя 70 запросов кредитования, счетчика 71 принятых символов счетчика 72 переданных символов и детектора 73 ошибки кредитования. Счетчик 71 принятых символов обеспечивает формирование двоичного кода, определяющего число информационных символов, которые разрешается принять в данном устройстве. Первый управляющий вход счетчика 71, соединенный с выходом формирователя 70 запросов кредитования, предназначен для увеличения состояния счетчика 71 на восемь при выдаче сигнала запроса на выдачу символа управления потоком. Второй управляющий вход счетчика 71, являющийся входом 77 подтверждения приема информационного символа блока 3, предназначен для уменьшения на единицу содержимого счетчика 71 при принятии каждого информационного символа. Для этого с входа 77 блока 3 на второй управляющий вход счетчика 71 подаются два сигнала: признак приема Nchar и признак удвоения. Изменение состояния счетчика 71 принятых символов под воздействием управляющих сигналов осуществляется по фронту синхросигналов, поступающих со входа 24 локальной синхронизации блока 3 на вход синхронизации счетчика 71. Выход ошибки счетчика 71 соединен с первым информационным входом детектора 73 ошибки кредитования и предназначен для формирования сигнала ошибки при попытке уменьшения состояния счетчика ниже предельно допустимого значения. Счетчик 72 переданных символов обеспечивает формирование двоичного кода, определяющего число информационных символов, которые разрешается передать из данного устройства. Первый управляющий вход счетчика 72, являющийся входом 78 подтверждения приема символа управления потоком блока 3, предназначен для увеличения состояния счетчика 72 на восемь при приеме каждого символа управления потоком. С входа 78 блока 3 на первый управляющий вход счетчика 72 подаются два сигнала: признак приема FCT и признак удвоения. Второй управляющий вход счетчика 72, являющийся входом 70 подтверждения выдачи информационного символа блока, предназначен для уменьшения на единицу содержимого счетчика 72 переданных символов. Изменение состояния счетчика 72 переданных символов при подаче управляющих сигналов осуществляется по фронту синхросигналов. Выход ошибки счетчика 72 соединен со вторым информационным входом детектора 73 ошибки кредитования и предназначен для формирования сигнала ошибки при попытке увеличения состояния счетчика выше предельно допустимого значения. Детектор 73 ошибки кредитования обеспечивает формирование объединенного сигнала ошибки кредитования на своем выходе, являющемся выходом 26 ошибки кредитования блока.

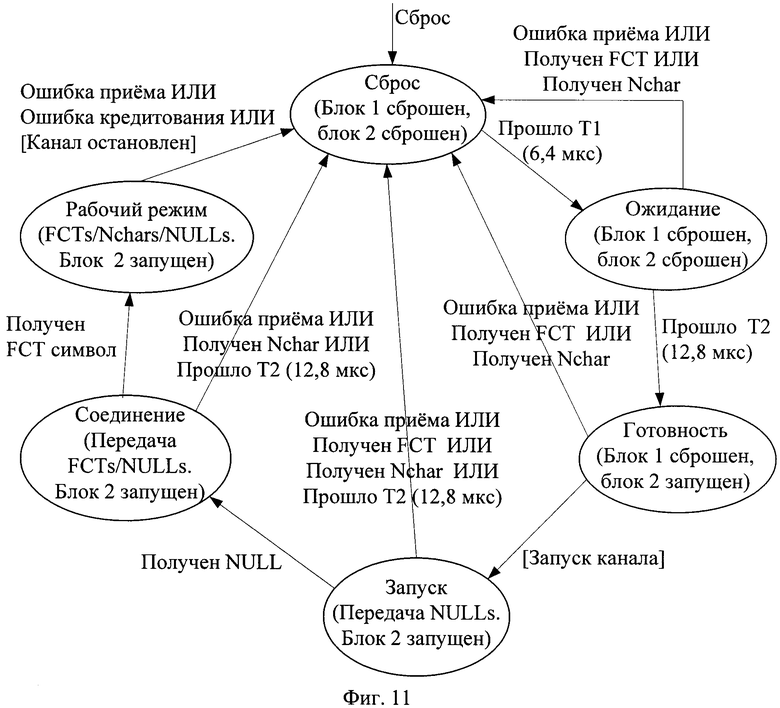

В блоке 4 управления (см. фиг.5), реализующем машину состояний, регистр 80 состояния предназначен для оперативного запоминания и контроля состояния фаз работы устройства. Фактически регистр 80 состояния является памятью машины состояний, которая реализуется блоком 4 управления. Регистр может быть доступен как на чтение, так и на запись для хост-системы (на фиг.5 не показано). Заполнение регистра выполняется побитно по сигналам от блока 2 приема данных или процессорного узла. Примерный формат регистра 80 состояния приведен в табл.4. Блок 81 формирования нового состояния предназначен для реализации логики машины состояний, выполняющей функцию автомата, переходящего под воздействием входных сигналов в различные состояния. Формирователь 82 управляющих сигналов обеспечивает выработку управляющих сигналов, с помощью которых машина состояний переводит блок 1 выдачи данных, блок 2 приема данных, и блок 3 управления потоком данных в исходные состояния, позволяя таким образом обеспечить корректную работу устройства в целом. Блок 83 задержки предназначен для формирования тайм-аутов, необходимых для правильного функционирования машины состояний при установлении и поддержании соединения с удаленной стороной через коммуникационный интерфейс.

Из показанной на фиг.11 примерной реализации графа машины состояний видна необходимость в реализации двух тайм-аутов Т1 и Т2. Например, в реализованном макете устройства выбраны следующие величины тайм-аутов: T1=6,4 мкс, Т2=12,8 мкс. Вход 24 локальной синхронизации блока 4 управления соединен с входами синхронизации регистра 80 состояния, формирователя 82 управляющих сигналов и блока 83 задержки. Вход 25 сброса блока 4 управления соединен с входами сброса регистра 80 состояния, формирователя 82 управляющих сигналов и блока 83 задержки. Вход 84 установления соединения блока 4 управления является первым входом блока 81 формирования нового состояния. Вход 85 ошибки кредитования блока 4 управления является вторым входом блока 81 формирования нового состояния. Вход 86 ошибки рассоединения блока 4 управления является третьим входом блока 81 формирования нового состояния. Вход 87 ошибки кодировки символа блока 4 управления является четвертым входом блока 81 формирования нового состояния. Вход 88 подтверждения приема символа управления потоком блока 4 управления является пятым входом блока 81 формирования нового состояния. Вход 89 подтверждения приема информационного символа блока 4 управления является шестым входом блока 81 формирования нового состояния, выход которого соединен с входом записи битов состояния регистра 80 состояния. Выход регистра 80 состояния соединен с управляющим входом формирователя 82 управляющих сигналов и с входом состояния блока 81 формирования нового состояния. Первый управляющий выход формирователя 82 управляющих сигналов соединен с входом блока 83 задержки, выход которого соединен с седьмым входом блока 81 формирования нового состояния. Второй управляющий выход формирователя 82 управляющих сигналов является выходом 29 разрешения передачи символа управления потоком блока 4 управления. Третий управляющий выход формирователя 82 является первым выходом 90 сброса блока 4 управления. Четвертый выход формирователя 82 является вторым выходом 91 сброса блока 4 управления. Пятый выход формирователя 82 является третьим выходом 92 сброса блока 4 управления.

В блоке 54 формирования сигналов (см. фиг.6) триггеры 93 первого бита и 94 второго бита предназначены для фиксации двух очередных смежных сигналов данных, поступающих на вход 101 сигнала данных блока 54 формирования сигналов, соединенный с входами данных триггеров 93 первого бита и 94 второго бита. Вход синхронизации блока 54 формирования сигналов соединен с одноименными входами триггеров 93 первого и 94 второго битов и первого 96 и второго 97 триггеров деления частоты, причем в триггеры 93 и 96 сигнал с их входов данных записывается по восходящему фронту синхросигнала, а в триггеры 94 и 97 сигнал с их входов данных записывается по падающему фронту синхросигнала. Выходы триггеров 93 первого и 94 второго битов соединены соответственно с входами первого и второго битов регистра 95 выделенных сигналов. Регистр 95 выделенных сигналов обеспечивает запоминание значений двух смежных битов данных, которые выделены из входных сигналов на входе 14 данных блока 2 приема данных. Вход 105 разрешения синхронизации блока 54 формирования сигналов, являющийся входом разрешения регистра 95 выделенных сигналов, предназначен для разрешения записи в него битов данных. Первый 96 и второй 97 триггеры деления частоты обеспечивают формирование двух внутренних синхросигналов, интервал между восходящими фронтами которых соответствует битовому интервалу между входными сигналами данных. Вход сброса блока 54 формирования сигналов соединен с входами сброса первого 96 и второго 97 триггеров деления частоты, которые предназначены для их сброса в исходное нулевое состояние. Выходы первого 96 и второго 97 триггеров деления частоты соединены соответственно с первым и вторым входами второго элемента 100 ИСКЛЮЧАЮЩЕЕ ИЛИ. Кроме того, имеется обратная связь выходов этих триггеров 96 и 97 соответственно через первый 98 и второй 99 элементы НЕ со своими входами данных. Второй элемент 100 ИСКЛЮЧАЮЩЕЕ ИЛИ предназначен для формирования внутренней синхропоследовательности с частотой, равной частоте принимаемых сигналов. Выход второго элемента 100 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом третьего элемента 101 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является входом 103 корректировки фронта синхросигнала блока 54 формирования сигналов. Третий элемент 101 ИСКЛЮЧАЮЩЕЕ ИЛИ обеспечивает формирование скорректированной последовательности синхросигналов, которая предназначена для фиксации выделяемых битов данных из принятых сигналов. Выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом 65 сигнала синхронизации блока 54 формирования сигналов и соединен с входом синхронизации регистра 95 выделенных сигналов, выход которого является выходом 64 битов данных блока 54 формирования сигналов.

В детекторе 56 рассоединения (см. фиг.7) первый 116 и второй 117 триггеры сброса обеспечивают через элемент 118 ИЛИ перевод счетчика 119 тайм-аута в нулевое состояние после изменения сигнала на управляющем входе 122 детектора 56 рассоединения при нулевом и единичном уровнях этого сигнала соответственно. Счетчик 119 тайм-аута предназначен для определения величины временного интервала между каждыми двумя соседними изменениями сигнала на управляющем входе 122 детектора 56 рассоединения. Компаратор 121 тайм-аута обеспечивает формирование сигнала ошибки рассоединения на выходе 124 детектора 56 рассоединения при совпадении двоичного кода на выходе счетчика 119 тайм-аута с предельно допустимым значением, хранящимся в блоке 120 константы тайм-аута. Управляющий вход 122 детектора 56 рассоединения соединен с входом сброса первого триггера 116 сброса и с инверсным входом сброса второго триггера 117 сброса. Входы синхронизации первого 116 и второго 117 триггеров сброса соединены с входом синхронизации счетчика 119 тайм-аута и с входом 123 синхронизации детектора 56 рассоединения. Вход 59 сброса детектора 56 рассоединения соединен с входами начальной установки первого 116 и второго 117 триггеров сброса и синхронным входом сброса счетчика 119 тайм-аута и предназначен для их сброса в нулевое состояние. Выходы первого 116 и второго 117 триггеров сброса соединены соответственно с первым и вторым входами элемента 118 ИЛИ, выход которого соединен с инверсным входом синхронного сброса счетчика 119 тайм-аута. Наличие нулевого уровня на этом входе обеспечивает перевод счетчика 119 тайм-аута в нулевое состояние при поступлении восходящего фронта сигнала локальной синхронизации на его вход синхронизации. Наличие высокого уровня на инверсном входе синхронного сброса обеспечивает разрешение инкрементирования счетчика 119 тайм-аута по каждому фронту синхросигнала (см. фиг.16). Выход счетчика 119 тайм-аута соединен с первым входом компаратора 121 тайм-аута, второй вход которого соединен с выходом блока 120 константы тайм-аута. Выход компаратора 121 тайм-аута является выходом 124 детектора 56 рассоединения.

В блоке 58 преобразования кода (см. фиг.8) сдвигающий регистр 125 выборки предназначен для выделения одного из четырех регистров 126, 127, 128 и 129, в который должна осуществляться запись очередного принятого байта данных с информационного входа 291 блока 58 преобразования кода. Выход сдвигающего регистра 125 выборки соединен с собственным последовательным входом, с входами выборки регистров первого 126, второго 127, третьего 128 и четвертого 129 байтов. Регистры первого 126, второго 127, третьего 128 и четвертого 129 байтов предназначены для хранения очередных четырех байтов последовательно принятых входных данных. Информационные входы регистров первого 126, второго 127, третьего 128 и четвертого 129 байтов соединены с информационным входом 138 блока 58 преобразования кода, выходы регистров 126, 127, 128 и 129 соединены соответственно с первым, вторым, третьим и четвертыми информационными входами блока сдвига данных. Блок 130 сдвига данных обеспечивает выдачу на выход 67 параллельного кода слова данных блока 58 преобразования кода еще необработанных битов данных из четырехбайтового кода, хранящегося в четырех регистрах 126, …, 129, для их последующей дешифрации. Регистр 131 управления сдвигом предназначен для определения текущего положения в четырехбайтовом коде первого необработанного бита, с которого начинается выдача битов данных через блок 130 сдвига данных. Выход регистра 131 управления сдвигом соединен с управляющим входом блока 130 сдвига данных. Выход состояния регистра 131 управления сдвигом соединен со вторым входом сложения первого сумматора 132. Первый сумматор 132 обеспечивает вычисление нового положения первого необработанного бита путем сложения двоичного кода текущей позиции и числа дешифрируемых битов с одноименного входа 139 блока 58 преобразования кода. Выход первого сумматора 132 соединен с информационным входом регистра 131 управления сдвигом. Регистр 133 управления чтением предназначен для формирования двоичного кода, указывающего на выходе разрядности слова данных количество действительных битов в слове данных, выдаваемых из блока сдвига данных для последующей дешифрации. Выход разрядности слова данных регистра 131 управления чтением является одноименным выходом 68 блока 58 преобразования кода. Выход состояния регистра 133 управления чтением соединен со вторым входом сложения второго сумматора 134. Второй сумматор 134 обеспечивает вычисление нового значения двоичного кода числа принятых и необработанных битов данных, то есть количества действительных битов в слове данных, путем прибавления к текущему состоянию регистра 133 константы «8» из регистра 135 константы при каждой записи очередного принятого байта данных в один из регистров 126…128 и вычитания двоичного кода числа дешифрируемых битов, поступающего с входа 139 числа дешифрируемых битов блока 58 преобразования кода. Выход второго сумматора 134 соединен с информационным входом регистра 133 управления чтением. Вход 59 сброса блока 58 преобразования кода соединен с одноименными входами сдвигающего регистра 125 выборки, регистра 131 управления сдвигом и регистра 133 управления чтением и предназначен для формирования начального состояния этих регистров. Вход 136 синхронизации блока 58 преобразования кода соединен с одноименными входами сдвигающего регистра 125 выборки, регистров первого 126, второго 127, третьего 128 и четвертого 129 байтов, регистра 131 управления сдвигом и регистра 133 управления чтением и предназначен для тактирования этих регистров. Вход 137 разрешения блока 58 преобразования кода соединен с разрешающими входами сдвигающего регистра 125 выборки, регистра 131 управления сдвигом и регистра 133 управления чтением и предназначен для разрешения записи в эти регистры только при наличии новых принятых байтов данных.

Блок 35 S-кодирования символа (см. фиг.10) осуществляет формирование сигналов стробирования S, сопровождающих сигналы данных D. Правила формирования сигнала стробирования при DS-кодировании представлены в табл.5.

Входящий в состав блока 35 третий сдвигающий регистр 140 предназначен для преобразования параллельного кода полного символа в последовательный, который побитно формируется на его информационном выходе. Информационный вход регистра 140 является входом 145 полного кода символа блока 35 DS-кодирования символа. Третий сдвигающий регистр 140 тактируется с входа синхронизации, являющегося входом 13 синхронизации блока 35 DS-кодирования символа, и переводится в начальное нулевое состояние по сигналу с входа сброса, являющегося входом 38 сброса блока 35. Выход смежных битов третьего сдвигающего регистра 140, соединенный с информационным входом формирователя 142 строба, обеспечивает одновременную выдачу двух смежных битов данных. Указатель 141 числа битов предназначен для отслеживания длины последовательности битов, входящих в состав одного символа и поступающих из третьего сдвигающего регистра 140 на информационный выход. Информационный вход указателя 141 числа битов является входом 146 длины символа блока 35 DS-кодирования символа. Длина символа представлена в виде двоичного кода, определяющего число битов следующего подготовленного к выдаче символа. Вход 147 записи длины символа блока 35 является входом загрузки указателя 141 числа битов. Выход указателя 141 числа битов соединен с входом загрузки третьего сдвигающего регистра 140 и является выходом 44 готовности блока 35 DS-кодирования символа. Указатель 141 числа битов тактируется с входа синхронизации, являющегося входом 13 синхронизации блока 35 DS-кодирования символа, и переводится в начальное состояние по сигналу с входа сброса, являющегося входом 38 сброса блока 35. Формирователь 142 строба предназначен для выработки последовательности сигналов стробирования, которые в соответствии с правилами формирования строба в способе DS-кодирования битов сопровождают выдачу битов данных символа по выделенной линии в виде сигнала стробирования (S-сигнала). Формирователь 142 строба тактируется с входа синхронизации, являющегося входом 13 синхронизации блока 35 DS-кодирования символа. Триггер 143 выдачи D-сигналов предназначен для формирования последовательности сигналов данных и их выдачи с выхода, являющегося выходом 16 данных устройства. Триггер 144 выдачи S-сигналов предназначен для формирования последовательности сигналов стробирования, сопровождающих сигналы данных, и их выдачи с выхода, являющегося выходом 17 стробирования устройства. Информационные входы триггеров 143 и 144 соединены соответственно с информационным выходом третьего сдвигающего регистра 140 и с выходом формирователя 142 строба. Входы сброса триггеров выдачи 143 и 144 соединены с входом сброса 38 блока 35 и предназначены для их сброса в исходное нулевое состояние. Входы синхронизации триггеров выдачи 143 и 144 сигналов соединены с входом 13 синхронизации 35 DS-кодирования символа и определяют частоту выдачи данных.

Устройство коммуникационного интерфейса работает следующим образом. Основной задачей устройства является обеспечение обмена данными между локальной хост-системой (компьютером или процессорным узлом, имеющим локальную память данных) и удаленной хост-системой через аналогичное удаленное устройство коммуникационного интерфейса. Локальное устройство и его локальная хост-система в дальнейшем именуются как «Сторона А», удаленные устройство коммуникационного интерфейса и его хост-система - «Сторона Б». Для выполнения указанной задачи данное устройство осуществляет организацию соединения в коммуникационном канале, связывающем стороны А и Б, и обеспечивает управление потоком данных. Коммуникационный канал образован (см. фиг.1) входными симплексными линиями данных (вход 14 данных канального интерфейса устройства) и стробирования (вход 15 стробирования канального интерфейса устройства) и выходными симплексными линиями данных (выход 16 данных коммуникационного интерфейса устройства) и стробирования (выход 17 стробирования коммуникационного интерфейса устройства).

Устройство изменяет свои режимы работы в соответствии с диаграммой состояния, реализуемой блоком 4 управления (см. фиг.13). В диаграмме состояний используется следующий стиль. Состояния представлены в виде эллипсов, имена состояний указываются внутри. Действия, происходящие в данном состоянии, указываются в скобках в том же эллипсе. Переходы из состояния в состояние обозначаются стрелками. Событие, вызвавшее переход из состояния в состояние, обозначается рядом со стрелкой перехода. Начальное условие показывается переходом из пустого места в первое состояние. Если переход может быть выполнен только при выполнении некоторого условия, то условие обозначается рядом с переходом в квадратных скобках.