Изобретение относится к вычислительной технике и предназначено для обмена данными по каналу связи.

Известны устройства [1] , предназначенные для обмена данными по каналу связи, содержащие регистры управления и регистры состояний для хранения управляющей информации, регистры данных, шифратор управления.

Недостатком известных устройств яляются большие аппаратурные затраты, необходимые на реализацию регистров управления, регистров состояний, шифратора управления в случаях, когда требуется значительное количество регистров управления и регистров состояний для обеспечения функций известных устройств.

Наиболее близким к предлагаемому является контроллер [2] , содержащий контроллер шины, интерфейс, селектор адреса, счетчик адреса, регистр адреса, схему сравнения, приемник, передатчик, шифратор управления, причем входы-выходы контроллера шины подключены к системной шине управления контроллера, первая группа входов-выходов интерфейса подключена к шине данных контроллера, вторая группа его входов-выходов подключена к шине адреса контроллера, его входы данных подключены к внутренней шине контроллера, его выходы адреса - к адресным входам селектора адреса, разрядные выходы счетчика адреса подключены к входам адреса интерфейса и к первой группе входов схемы сравнения, к второй группе входов которой подсоединены выходы регистра адреса, входы данных счетчика адреса и информационные входы регистра адреса подсоединены к внутренней шине контроллера, вход записи счетчика адреса, вход записи регистра адреса, вторая группа входов управления интерфейса, третья группа входов управления контроллера шины, вторая группа входов управления передатчика, вторая группа входов управления приемника, первая группа выходов шифратора управления подключены к шине управления контроллера, выход контроллера шины подключен к счетному входу счетчика адреса, выход "Равно" схеме сравнения соединен с первым входом шифратора управления, вход данных приемника подключен к входу данных контроллера, выход передатчика подключен к выходу контроллера.

Недостатком известного контроллера являются большие аппаратурные затраты, необходимые на реализацию регистров управления, регистров состояний и шифратора управления в случаях, когда для функционирования контроллера требуется значительное количество регистров управления и регистров состояний для хранения слов состояний и управления. Поскольку через регистры управления и регистры состояний между ЭВМ и известным контроллером осуществляется обмен управляющей информацией, содержащейся в словах управления и словах состояний, то для обработки управляющей информации и выработки сигналов управления по результатам обработки слов состояний и слов управления требуются аппаратурные затраты на реализацию шифратора управления, выполненного на элементах жесткой логики, тем больше, чем большее число регистров управления и регистров состояний используется, поскольку каждый разряд регистров управления и регистров состояний соединен с соответствующим входом шифратора управления. Применение элементов гибкой логики, например микропроцессоров, для реализации шифратора управления ограничивается временными характеристиками известных контроллеров, для которых обмен данными должен осуществляться в режимах реального времени.

Недостатком известного контроллера является ограничение области применения в случаях, когда использование большого количества регистров управления и состояний невозможно по причине ограниченности адресного пространства шины адреса ЭВМ, отведенного под адресацию внешних регистров. Так, при использовании ЭВМ микропроцессора серии 580 под адресацию внешних регистров отведено адресное пространство в 256 адресов, что ограничивает возможности использования контроллера, если для его реализации требуется большее, чем 256 число регистров управления и регистров состояний.

Цель изобретения - расширение области применения контроллера при сокращении аппаратурных затрат на его реализацию.

Цель достигается тем, что в контроллер, содержащий контроллер шины, интерфейс, селектор адреса, счетчик адреса, регистр адреса, схему сравнения, приемник, передатчик, шифратор управления, причем входы-выходы контроллера шины подключеы к системной шине управления контроллера, первая группа входов-выходов интерфейса подключена к шине данных контроллера, вторая группа его входов-выходов подключена к шине адреса контроллера, его входы данных подключены к внутренней шине контроллера, его выходы адреса - к адресным входам селектора адреса, разрядные выходы счетчика адреса подключены к входам адреса интерфейса и к первой группе входов схемы сравнения, к второй группе входов которой подсоединены выходы регистра адреса, входы данных счетчика адреса и информационные входы регистра адреса подсоединены к внутренней шине контроллера, вход записи счетчика адреса, вход записи регистра адреса, вторая группа входов управления интерфейса, третья группа входов управления контроллера шины, вторая группа входов управления передатчика, вторая группа входов управления приемника, первая группа выходов шифратора управления подключены к шине управления контроллера, выход контроллера шины подключен к счетному входу счетчика адреса, выход "Равно" схемы сравнения соедиен с первым входом шифратора управления, вход данных приемника подключен к входу данных контроллера, выход передатчика подключен к выходу контроллера, введены оперативная память, запоминающее устройство, регистровое устройство, контроллер прерываний, мультиплексор, при этом выходы управления контроллера шины подключены к входам управления селектора адреса, к первой группе входов управления интерфейса, к первой группе входов управления приемника и к первой группе входов управления передатчика, первая группа входов управления контроллера шины подключена к выходам управления передатчика, вторая группа входов управления контроллера шины подключена к выходам управления приемника, входы-выходы приемника, входы-выходы передатчика, входы-выходы оперативной памяти, входы-выходы регистрового устройства, первая группа адресных входов запоминающего устройства подключены к выходам мультиплексора и к внутренней шине контроллера, выходы приемника подключены к входам интерфейса, входы передатчика соединены с выходами интерфейса, входы адреса оперативной памяти соединены с первой группой выходов регистрового устройства, выходы запоминающего устройства соединены с третьей группой входов регистрового устройства, выходы состояний запоминающего устройства соединены с первой группой входов шифратора управления, вторая группа адресных входов запоминающего устройства соединена с второй группой выходов регистрового устройства, первая группа входов регистрового устройства соединена с второй группой выходов шифратора управления, вторая группа входов регистрового устройства соединена с третьей группой выходов шифратора управления, третья группа выходов регистрового устройства соединена с входам управления запоминающего устройства, управляющий вход шифратора управления соединен с выходом переноса запоминающего устройства, вход переноса которого соедиен с первым выходом шифратора управления, вторая группа входов шифратора управления и первая группа входов запроса контроллера прерываний соединены с выходами состояний приемника, выходы состояний передатчика подключены к третьей группе входов шифратора управления и к второй группе входов запросов контроллера прерываний, к третьей группе входов запросов которого и к четвертой группе входов шифратора управления подключены выходы контроллера шины, выходы селектора адреса соединены с четвертой группой входов запросов контроллера прерываний, второй выход шифратора управления соединен с входом запроса контроллера прерываний, выход управления которого соединен с вторым входом шифратора управления, вход синхронизации контроллера прерываний и вход синхронизации регистрового устройства соединены с третьим выходом шифратора управления, к пятой группе входов которого подключены выходы контроллера прерываний, выходы адреса интерфейса подсоединены к первой группе входов мультиплексора, к второй группе входов которого подключены выходы данных интерфейса, выход "Равно" схемы сравнения соединен с входом управления приемника и с входом передатчика, входы управления приоритета контроллера прерываний, входы управления оперативной памяти, входы управления мультиплексора, входы управления регистрового устройства подключены к шине управления контроллера.

Введение в контроллер оперативной памяти, запоминающего устройства, регистрового устройства, контроллера прерываний и мультиплексора в указанной выше взаимосвязи позволяет расширить область применения контроллера при сокращении аппаратурных затрат на его реализацию.

Расширение области применения контроллера выражается в том, что он может использоваться в системах, ведущих обмен данными в реальном времени и использующих ЭВМ, с ограниченным адресным пространством шины адреса, отведенным под адресацию регистров внешних устройств, что ограничивает число регистров управления и регистров состояний в устройстве, к которым ЭВМ может обратиться в режиме программного обмена. Примером ЭВМ, имеющих ограниченное адресное пространство шины адреса, могут служить ЭВМ, построенные с использованием микропроцессоров серии 580, а также ЭВМ серии "электроника 60". Расширение области применения контроллера объясняется тем, что обмен словами управления и словами состояния между ЭВМ и контроллером производится не только в режиме программного обмена, но и в режиме прямого доступа к оперативной памяти ЭВМ со стороны контроллера, и при этом условия обмена данными в режиме реального времени, а также условия обработки слов состояний и слов управления и формирования по результатам обработки управляющих воздействий в режиме реального времени выполняются. Использование оперативной памяти, запоминающего устройства, регистрового устройства, мультиплексора и контроллера прерываний при работе контроллера в режиме прямого доступа к оперативной памяти ЭВМ позволяет вести обмен словами состояний, словами управления между оперативной памятью ЭВМ и оперативной памятью контроллера, а также позволяет производить ускоренную обработку слов состояний и слов управления и по результатам этой обработки управлять режимами работы контроллера в условиях реального времени обмена данными. Оперативная память служит для хранения слов состояний и слов управления, которыми ЭВМ и контроллер обмениваются в режимах программного обмена и прямого доступа к памяти ЭВМ. Применение оперативной памяти позволяет сократить затраты на регистры, необходимые для хранения слов управления и слов состояний. Однако при этом возникает проблема формирования сигналов управления по результатам обработки слов состояний и слов управления, поскольку эти сигналы управления должны формироваться за интервалы времени не большие, чем необходимо для обеспечения режимов реального времени обмена данными. Использование запоминающего устройства позволяет производить за ограниченные интервалы времени обработку битов слов состояний и слов управления и по результатам обработки вырабатывать управляющие сигналы для перевода контроллера в различные режимы функционирования, во время которых реализуются процессы реального времени обмена словами состояний, словами управления в режиме программного обмена и в режиме прямого доступа к памяти ЭВМ и процессы обмена данными. Применение оперативной памяти, контроллера прерываний, запоминающего устройства, мультиплексора позволяет произвести сокращение аппаратурных затрат на реализацию контроллера, функционирующего в условиях реального времени обмена данными при расширении области его применения, во-первых, за счет сокращения аппаратурных затрат на реализацию регистров состояний и регистров управления, поскольку слова состояний и слова управления хранятся в оперативной памяти, а во-вторых, за счет сокращения аппаратурных затрат на шифратор управления, под управлением которого производится обработка слов состояний и слов управления и под управлением которого контроллер выполняет операции по обработке, формированию и обмену данными между ЭВМ, контроллером, передатчиком и приемником. Применение запоминающего устройства, сохраняя работоспособность контроллера в условиях реального времени обмена данными между ЭВМ, контроллером, приемником и передатчиком, позволяет сократить аппаратурные затраты на шифратор управления, использующий в прототипе элементы жесткой логики, соединенные линиями связи с каждым из разрядов регистров управления и регистров состояний. Вместо элементов жесткой логики используется запоминающее устройство для обработки и преобразования слов состояний и слов управления, что достигается за счет хранения в ячейках памяти запоминающего устройства результатов арифметических и логических операций над давлением, которые подаются на первую и вторую группы адресных входов запоминающего устройства. Набор нестандартных и стандартнх арифметических и логических операций, результаты которых хранятся в запоминающем устройстве, позволяет сократить время обработки данных и за требуемые промежутки времени вырабатывать на выходах состояний запоминающего устройства управляющие сигналы, подающиеся на шифратор управления. Набор операций, выполняемых запоминающим устройством, выбирается индивидуально для каждого из вариантов котроллера. Использование контоллера прерываний дает возможность в условиях реального времени работы контроллера обеспечить обмен данными между ЭВМ, оперативным запоминающим устройством, приемником и передатчиком и поизводить арбитраж процессов реального времени. Использование контроллера прерываний совместно с запоминающим устройством, регистровым устройством и мультиплексором позволяет выполнять в реальном времени обмен данными между ЭВМ, приемником, передатчиком и контроллером. Использование мультиплексора позволяет выполнять переключение на первую группу адресных входов запоминающего устройства сигналов адреса с шины адреса контроллера или сигналов данных с шины данных контроллера, что необходимо для обработки слов управления и слов состояний запоминающим устройством. Применение регистрового устройства позволяет обеспечить временное хранение данных при обмене данными между оперативной памятью, запоминающим устройством, ЭВМ, приемником и передатчиком.

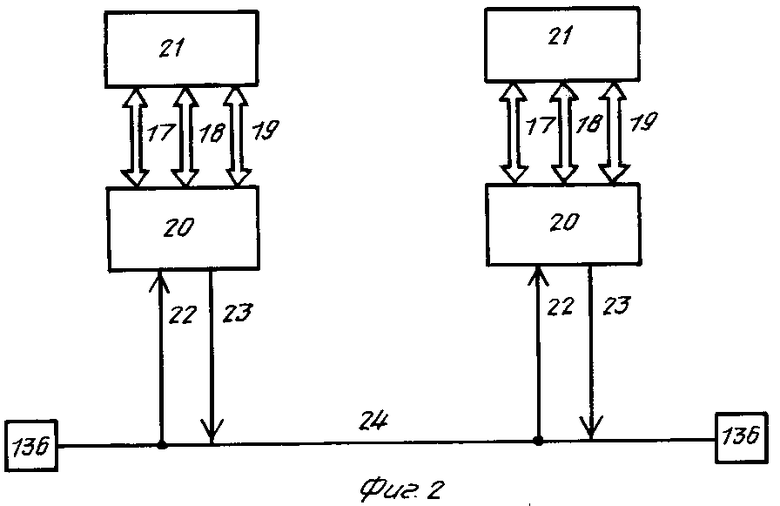

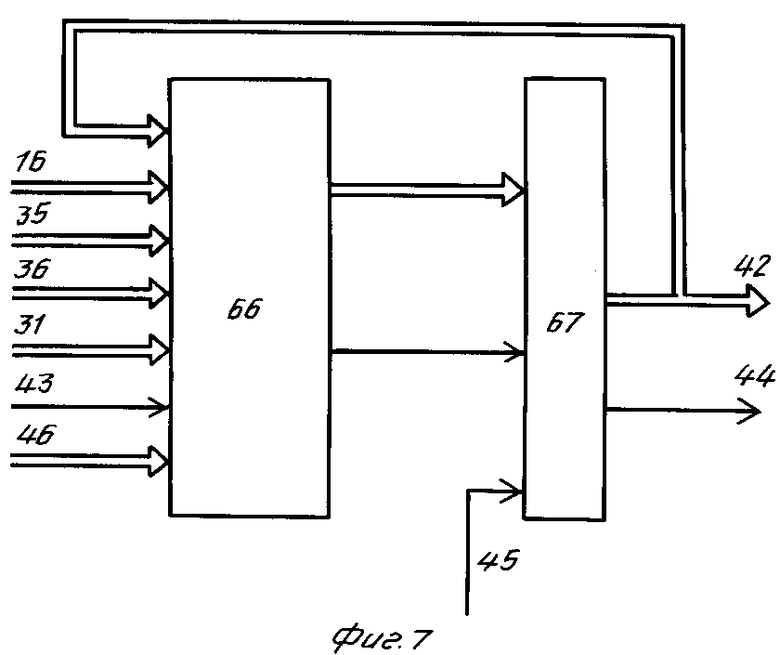

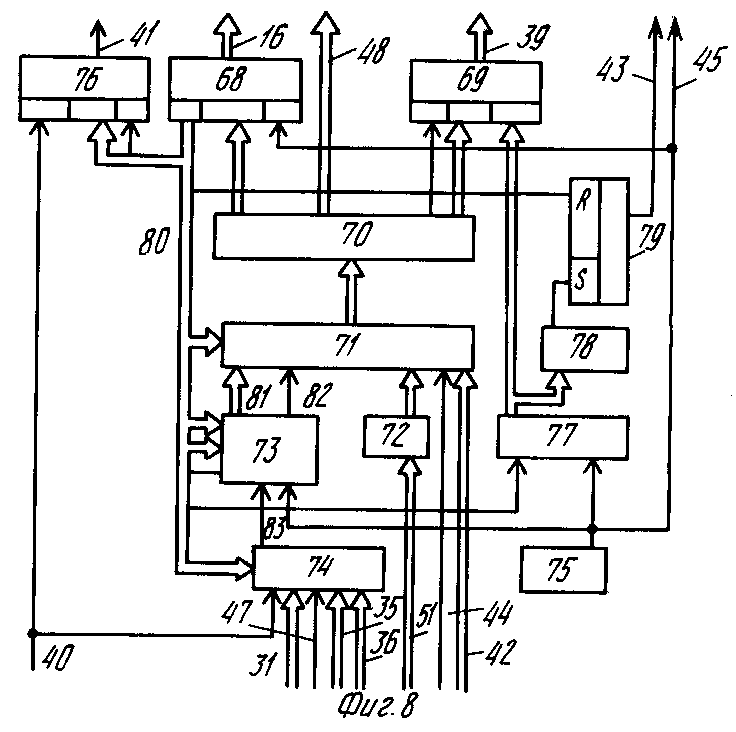

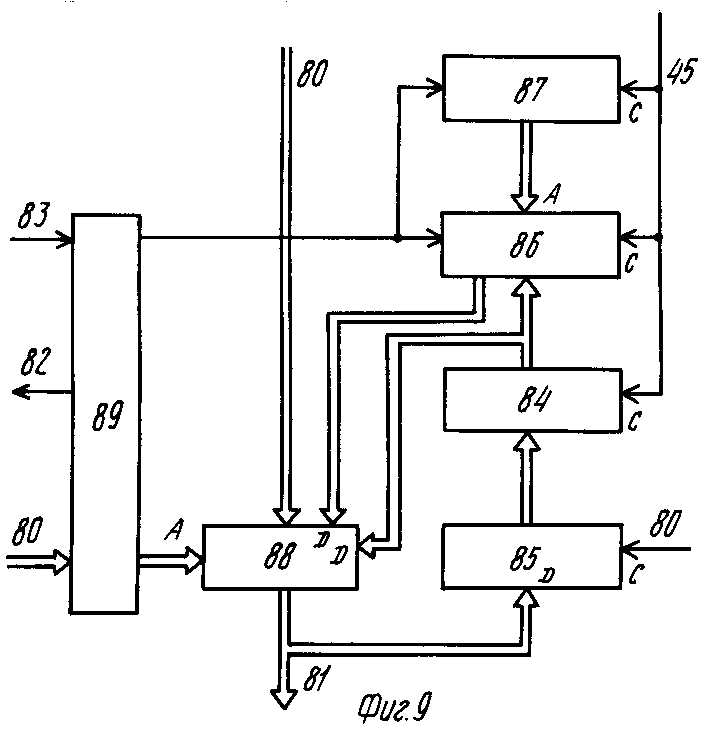

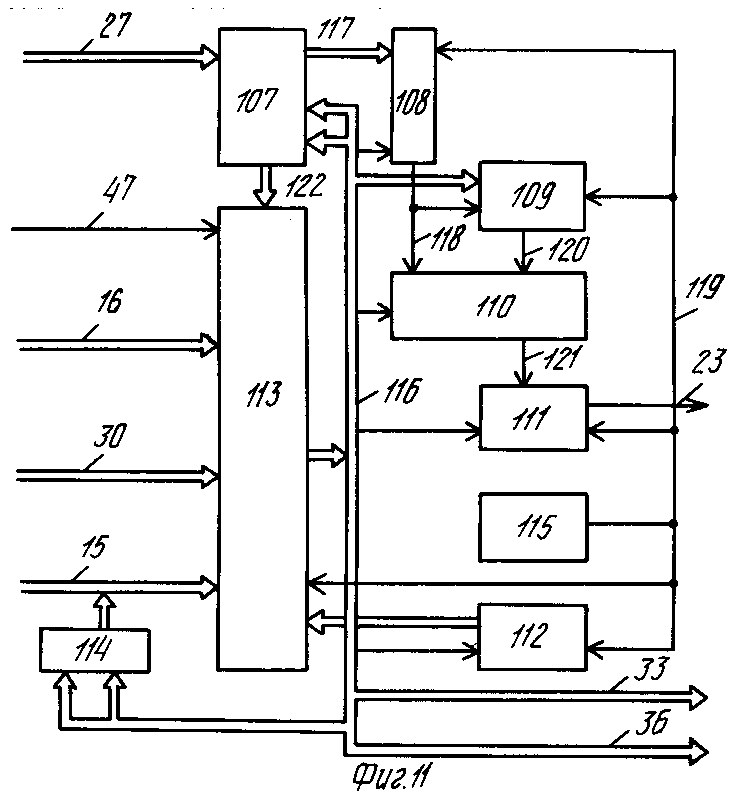

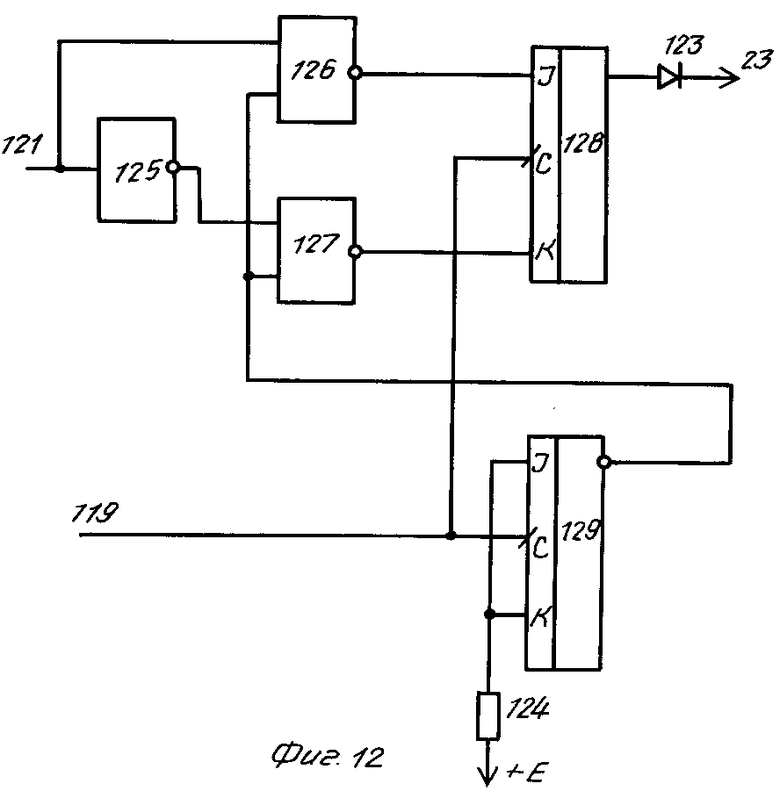

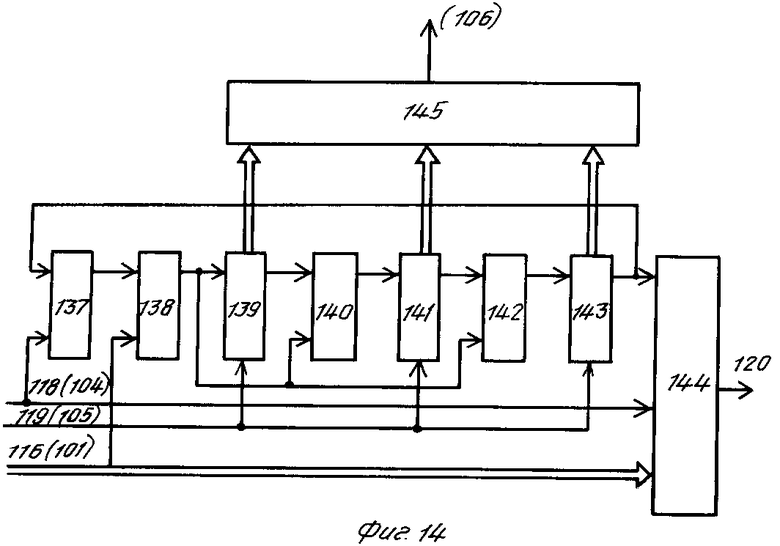

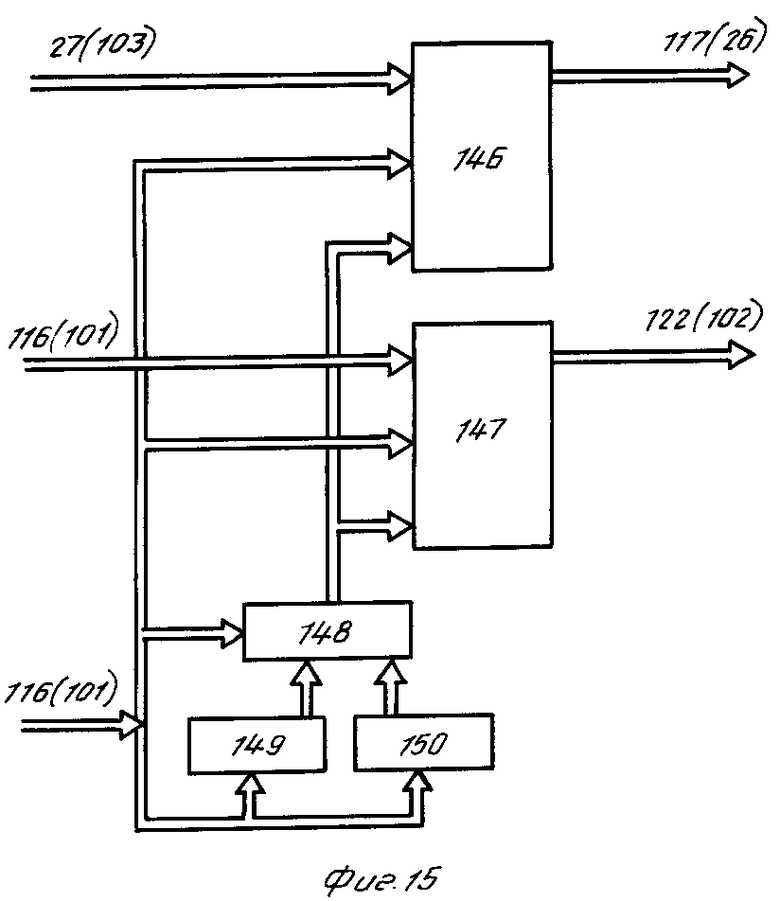

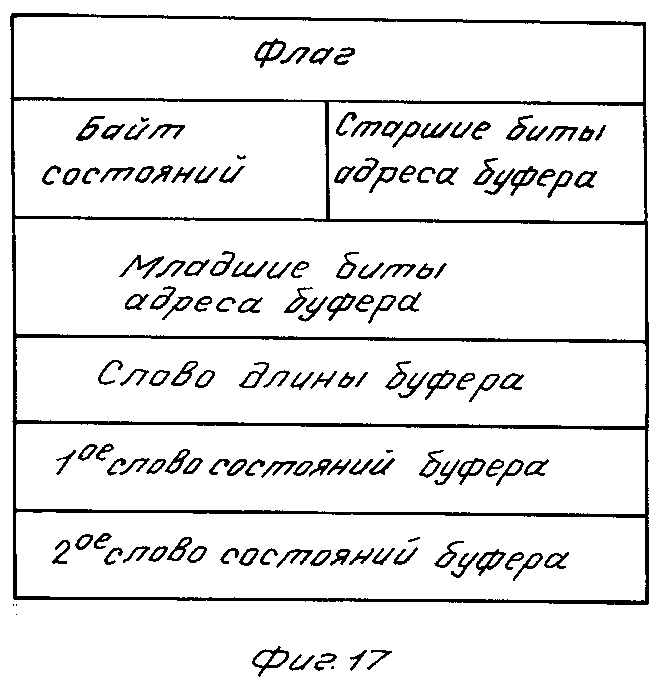

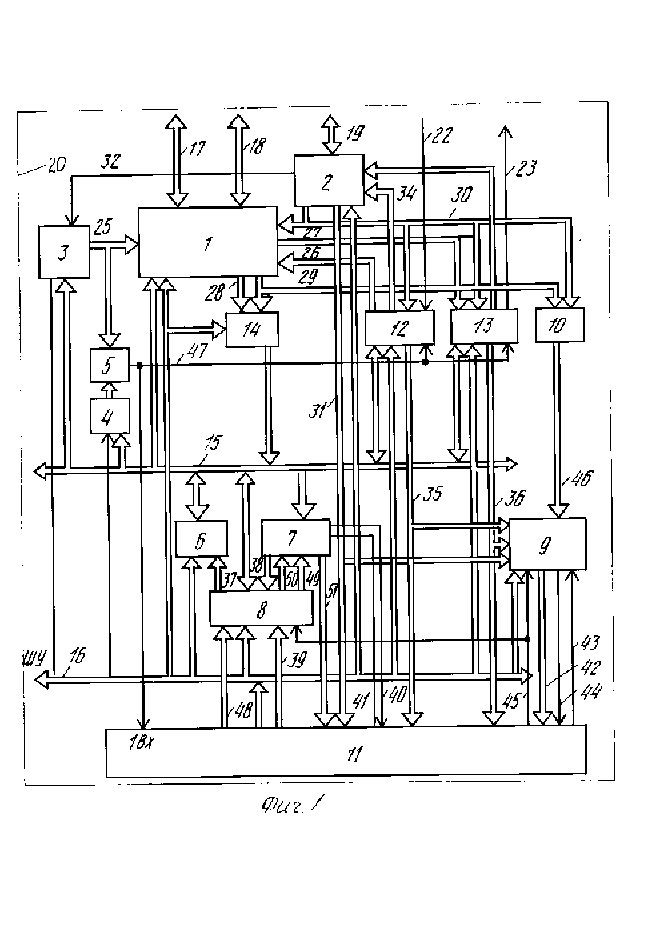

На фиг. 1 представлена структурная схема контроллера; на фиг. 2 - структурная схема подключения ЭВМ через контроллер к каналу связи; на фиг. 3 - структурная схема запоминающего устройства; на фиг. 4 - структурная схема интерфейса; на фиг. 5 - структурная схема контроллера шины; на фиг. 6 - структурная схема регистрового устройства; на фиг. 7 - структурная схема контроллера прерываний; на фиг. 8 - структурная схема шифратора управления; на фиг. 9 - структурная схема формирователя адреса микрокоманды; на фиг. 10 - структурная схема приемника; на фиг. 11 - структурная схема передатчика; на фиг. 12 представлен пример реализации схемы кодера; на фиг. 13 - пример реализации схемы декодера; на фиг. 14 представлена структурная схема логики циклического контроля; на фиг. 15 - структурная схема памяти обратного магазинного типа (схема фифо); на фиг. 16 представлен формат пакетов данных, передаваемых в канал связи; на фиг. 17 - формат дескрипторов буферов передачи и буферов приема. Дескрипторы описывают зоны памяти ЭВМ (буферы приема и буферы передачи), отведенные под хранение принимаемых и передаваемых данных, а также под слова состояний, описывающие процесс обмена данными.

Контроллер содержит (фиг. 1) интерфейс 1, контроллер 2 шины, счетчик 3 адреса, регистр 4 адреса, схему 5 сравнения, оперативную память 6, запоминающее устройство 7, регистровое устройство 8, контроллер 9 прерываний, селектор 10 адреса, шифратор 11 управления, приемник 12, передатчик 13, мультиплексор 14.

Через внутреннюю шину 15, шину 16 управления, через шину 17 данных, шину 18 адреса, системную шину 19 управления контроллер 20 (фиг. 2) имеет связь с ЭВМ 21. Первая группа входов-выходов интерфейса 1 связана с шиной 17 данных контроллера, вторая группа входов-выходов интерфейса 1 связана с шиной 18 адреса контроллера. Шина 17 данных подключается к шине данных ЭВМ, шина 18 адреса - к шине адреса ЭВМ, системная шина 19 управления контроллера подключается к системной шине управления ЭВМ. Входы-выходы контроллера 2 шины соединены с системной шиной 19 управления. По линии 22 через вход данных контроллера и по линии 23 через его выход контроллер подключен к каналу 24 связи. Вход управления приемника 12 подключен к входу данных контроллера, а выход передатчика 13 - к выходу контроллера. Через шину 25 разрядные выходы счетчика 3 адреса подключены к первой группе входов схемы 5 сравнения и к входам адреса интерфейса 1. Выходы регистра 4 адреса соединены с второй группой входов схемы 5 сравнения. Входы интерфейса 1 через шину 26 подключены к выходам приемника 12, а его выходы через шину 27 подключены к входам передатчика 13. По шине 28 выходы данных интерфейса 1 соединены второй группой входов мультиплексора 14, первая группа входов которого и адресные входы селектора 10 адреса связаны по шине 29 с выходами адреса интерфейса 1. По шине 30 первая группа входов управления интерфейса 1, первая группа входов управления приемника 12, первая группа входов управления передатчика 13, входы управления селектора 10 адреса связаны с выходами управления контроллера 2 шины. По шине 31 четвертая группа входов шифратора 11 управления и третья группа входов запросов контроллера 9 прерываний связаны с выходами контроллера 2 шины, выход которого по линии 32 связан со счетным входом счетчика 3 адреса. Первая группа входов управления контроллера 2 шины по шине 33 связана с выходами управления передатчика 13, а вторая группа входов управления по шине 34 связана с выходами управления приемника 12. Выходы состояний приемника 12 связаны по шине 35 с второй группой входов шифратора 11 управления и с первой группой входов запросов контроллера 9 прерываний. Выходы состояний передатчика 13 связаны по шине 36 с третьей группой входов шифратора 11 управления и с второй группой входов запросов контроллера 9 прерываний. Входы адреса оперативной памяти 6 соединены по шине 37 с первой группой выходов регистрового устройства 8. Выходы запоминающего устройства 7 подключены по шине 38 к третьей группе входов регистрового устройства 8. Вторая группа выходов шифратора 11 управления подключена по шине 39 к первой группе входов регистрового устройства 8. Линия 40 соединяет управляющий вход шифратора 11 управления с выходом переноса запоминающего устройства 7, к входу переноса которого по линии 41 подключен первый выход шифратора 11 управления. Пятая группа входов шифратора 11 управления соединена по шине 42 с выходами контроллера 9 прерываний, вход запроса которого соединен по линии 43 с вторым выходом шифратора 11 управления, выход управления соединен по линии 44 с вторым входом шифратора 11 управления, а вход синхронизации и вход синхронизации регистрового устройства 8 соединены по линии 45 с третьим выходом шифратора 11 управления. Выходы селектора 10 адреса подключены по шине 46 к четвертой группе входов запросов контроллера 9 прерываний. Выход "Равно" схемы 5 сравнения соединен по линии 47 с входом управления приемника 12, с входом управления передатчика 13, с первым входом шифратора 11 управления. Третья группа выходов шифратора 11 управления соединена с второй группой входов регистрового устройства 8 по шине 48. Третья группа выходов регистрового устройства 8 по шине 49 соединена с входами управления запоминающего устройства 7, вторая группа выходов регистрового устройства 8 соединена по шине 50 с второй группой адресных входов запоминающего устройства 7. Выходы состояний запоминающего устройства 7 по шине 51 соединены с первой группой входов шифратора 11 управления. К внутренней шине 15 контроллера подключены входы данных счетчика 3 адреса, информационные входы регистра 4 адреса, выходы мультиплексора 14, входы данных интерфейса 1, входы-выходы передатчика 13, входы-выходы приемника 12, входы-выходы оперативной памяти 6, входы-выходы регистрового устройства 8, первая группа адресных входов запоминающего устройства 7. К шине 16 управления контроллера подключены первая группа выходов шифратора 11 управления, вход записи счетчика 3 адреса, вход записи регистра 4 адреса, вторая группа входов управления интерфейса 1, входы управления мультиплексора 14, входы управления оперативной памяти 6, входы управления регистрового устройства 8, третья группа входов управления контроллера 2 шины, вторая группа входов управления приемника 12, вторая группа входов управления передатчика 13, входы управления приоритетами контроллера 9 прерываний.

Запоминающее устройство 7 содержит (фиг. 3) секции 52 и запоминающее устройство 53 ускоренных переносов. Первая и вторая группы адресных входов запоминающего устройства 7, а также его выходы содержат группы линий. Число групп линий в первой группе адресных входов равно числу групп линий во второй группе адресных входов, равно числу групп линий выходов запоминающего устройства 7. Например, при числе секций, равном четырем, в первой, второй группах адресных входов и в выходах запоминающего устройства 7 содержатся по четыре группы линий, причем каждая из групп линий первой группы адресных входов запоминающего устройства 7 соединена с первой группой входов одной из секций 52 запоминающего устройства, а каждая из групп линий второй группы адресных входов запоминающего устройства 7 соединена с второй группой входов одной из секций 52 запоминающего устройства, третьи группы входов секций 52 запоминающего устройства соединены с входами упавления запоминающего устройства 7. Входы переноса каждой из секций 52 запоминающего устройства соединены с одной из гупп выходов переноса запоминающего устройства 53 ускоренных переносов, каждая из групп входов переноса которого соединена с выходами переноса одной из секций 52 запоминающего устройства. Вход переноса запоминающего устройства 7 соединен с входом переноса первой секции 52 запоминающего устройства и с входом переноса запоминающего устройства 53 ускоренных переносов, выход переноса запоминающего устройства 7 соединен с выходом переноса запоминающего устройства 53 ускоренных переносов. Каждая из групп линий выходов запоминающего устройства 7 подключена к выходам одной из секций 52 запоминающего устройства и к выходам состояний запоминающего устройства 7. Входы управления запоминающего устройства 53 ускоренных переносов соединены с входами управления запоминающего устройства 7.

Для реализации секции 52 запоминающего устройства используется постоянное программируемое запоминающее устройство, вход адреса которого соединен с входом переноса секции запоминающего устройства. Первая гуппа входов адреса последнего соединена с первой группой входов секции 52 запоминающего устройства, вторая группа входов адреса соединена с второй группой входов секции запоминающего устройства, третья группа входов адреса соединена с третьей группой входов секции запоминающего устройства, четвертая группа входов адреса соединена с входами переноса секции запоминающего устройства, а первая группа выходов соединена с выходами переноса секции запоминающего устройства, вторая группа выходов - с выходами секции запоминающего устройства.

Запоминающее устройство 53 ускоренных переносов реализуется на постоянном программируемом запоминающем устройстве, причем с каждой из групп входов переноса запоминающего устройства 53 ускоренных переносов соединена одна из групп входов адреса постоянного программируемого запоминающего устройства, вход адреса которого соединен с входом переноса запоминающего устройства 53 ускоренных переносов, а каждая из групп выходов соединена с одной из групп выходов переноса запоминающего устройства 53 ускоренных переносов, выход которого соединен с выходом переноса запоминающего устройства 53 ускоренных переносов, а отдельная группа входов адреса соединена с входами управления запоминающего устройства 53 ускоренных переносов.

Интерфейс 1 содержит (фиг. 4) усилители 54 шины адреса и усилители 55 шины данных, регистр 56, коммутатор 57. Входы-выходы усилители 54 шины адреса соединены с второй группой входов-выходов интерфейса 1, первая группа входов-выходов которого соединена с входами-выходами усилителей 55 шины данных. Входы усилителей 54 шины адреса подключены к входам адреса интерфейса 1, к выходам адреса которого подключены выходы усилителей 54 шины адреса. Выходы усилителей 55 шины данных соединены с выходами данных и с выходами интерфейса 1. Первая группа входов коммутатора 57 соединена с входами данных интерфейса 1, вторая группа входов коммутатора 57 соединена с входами интерфейса 1. Выходы коммутатора 57 соединены с входами регистра 56, выходы которого соединены с входами усилителей 55 шины данных. Первая группа входов управления усилителей 54 шины адреса, первая группа входов управления усилителей 55 шины данных, первый вход управления записью регистра 56, первый вход управления коммутатором 57 соединены с первой группой входов управления интерфейса 1, вторая группа входов управления которого соединена с второй группой входов управления усилителей 54 шины адреса, с второй группой входов управления усилителей 55 шины данных, с вторым входом управления записью регистра 56, с вторым входом управления коммутатора 57.

Контроллер 2 шины содержит (фиг. 5) усилители 58, дешифратор 59, таймерное устройство 60. Входы-выходы усилителей 58 соединены с входами-выходами контроллера 2 шины, выходы которого соединены с первой группой выходов дешифратора 59. Входы усилителей 58 соединены с второй группой выходов дешифратора 59, первая группа входов которого соединена с выходами усилителей 58. Третья группа выходов дешифратора 59 соединена с выходами управления контроллера 2 шины, вторая группа входов дешифратора 59 соединена с третьей группой входов управления контроллера 2 шины. Четвертая группа выходов дешифратора 59 соединена с входами таймерного устройства 60, выходы которого соединены с третьей группой входов дешифратора 59. Четвертая группа входов дешифратора 59 соединена с первой группой входов управления контроллера 2 шины, вторая группа входов управления которого соединена с пятой группой входов дешифратора 59. Выход дешифратора 59 соединен с выходом контроллера 2 шины, выход управления дешифратора 59 соединен с входом управления усилителей 58.

Регистровое устройство 8 содержит (фиг. 6) мультиплексор 61, мультиплексор 62, регистры 63, усилители 64, реверсивный счетчик 65. Входы управления усилителей 64, входы управления мультиплексора 61, входы управления мультиплексора 62, входы управления регистров 63, входы управления реверсивного счетчика 65 соединены с входами управления регистрового устройства 8, первая группа входов которого соединена с первой группой входов мультиплексора 62. Вторая группа входов мультиплексора 62 соединена с второй группой входов регистрового устройства 8. Третья группа входов мультиплексора 62 соединена с выходами усилителей 64. Третья группа входов регистрового устройства 8 соединена с четвертой группой входов мультиплексора 62. Входы-выходы регистрового устройства 8 соединены с входами-выходами усилителей 64, к входам которых подключена первая группа выходов мультиплексора 61. Первая группа выходов регистрового устройства 8 соединена с второй группой выходов мультиплексора 61, его вторая группа выходов соединена с третьей группой выходов мультиплексора 61, а его третья группа выходов соединена с четвертой группой выходов мультиплексора 61. Входы синхронизации регистров 63 и вход синхронизации реверсивного счетчика 65 соединены с входом синхронизации регистрового устройства 8. Мультиплексор 62 имеет несколько групп выходов, причем входы каждого из регистров 63 соединены с одной из групп выходов мультиплексора 62. Мультиплексор 61 содержит несколько групп входов, причем выходы каждого из регистров 63 соединены с одной из групп входов мультиплексора 61. Выходы реверсивного счетчика 65 соединены с входами адреса регистров 63.

Контроллер 9 прерываний содержит (фиг. 7) логическую матрицу 66, в качестве которой может использоваться, например, программируемая логическая матрица, регистр 67. Выходы регистра 67 соединены с выходами контроллера 9 прерываний и с первой группой входов логической матрицы 66, к второй группе входов которой подключены входы управления приоритетами контроллера 9 прерываний, к третьей группе входов подключена первая группа входов запросов контроллера 9 прерываний, к четвертой группе входов подключена вторая группа входов запросов контроллера 9 прерываний, к пятой группе входов подключена третья группа входов запросов контроллера 9 прерываний, к шестой группе входов подключена четвертая группа входов запросов контроллера 9 прерываний, к входу подключен вход запроса контроллера 9 прерываний, а выходы соединены с входами регистра 67, выход соединен с входом управления записью регистра 67. Выход управления контроллера 9 прерываний соединен с выходом регистра 67, вход синхронизации которого соединен с входом синхронизации контроллера 2 шины.

Шифратор 11 управления содержит (фиг. 8) регистр 68 микрокоманд, мультиплексор 69, память 70 микрокоманд, в качестве которой используется, например, постоянное программируемое запоминающее устройство, мультиплексор 71, дешифратор 72 - преобразователь начального адреса, формирователь 73 адреса микрокоманды, мультиплексор 74 условий, генератор 75, мультиплексор 76, счетчик 77 - таймер, дешифратор 78, RS-триггер 79, шину 80 управления.

Выходы формирователя 73 адреса микрокоманды соединены с шиной 81. Его выход соединен с линией 82, его входы адреса, входы инструкций, вход инкремента соединены с шиной 80 управления. Его вход условий соединен с линией 83, вход синхронизации - с линией 45. Вторая группа выходов шифратора 11 управления соединена с выходами мультиплексора 69, первая группа входов которого соединена с выходами счетчика-таймера 77 и с входами дешифратора 78. Первая группа выходов шифратора 11 управления соединена с первой группой выходов регистра 68 микрокоманд, входы которого соединены с первой группой выходов памяти 70 микрокоманд. Входы управления и первый вход мультиплексора 76, входы управления мультиплексора 71, входы адреса, входы инструкций, вход инкремента формирователя 73 адреса микрокоманды, вход сброса счетчика-таймера 77, R-вход RS-триггера 79, входы управления мультиплексора 74 условий, вторая группа выходов регистра 68 соединены с шиной 80. Вход управления мультиплексора 69 соединен с выходом памяти 70 микрокоманд. Вторая группа выходов памяти 70 микрокоманд соединена с второй группой входов мультиплексора 69. Выход генератора 75 соединен со счетным входом счетчика-таймера 77, с входом записи регистра 68 микрокоманд, с входом синхронизации формирователя 73 адреса микрокоманды, с третьим выходом шифратора 11 управления. Входы адреса памяти 70 микрокоманд соединены с выходами мультиплексора 71, первая группа входов которого соединена с выходами формирователя 73 адреса микрокоманды, вторая группа входов соединена с выходами дешифратора-преобразователя 72 начального адреса, третья группа входов соединена с пятой группой входов шифратора 11 управления, а первый вход управления соединен с вторым входом шифратора управления. Входы дешифратора-преобразователя 72 начального адреса соединены с первой группой входов шифратора 11 управления. Выход формирователя 73 адреса микрокоманды соединен с вторым входом управления мультиплексора 71. Вход условий формирователя 73 адреса микрокоманды соединен с выходом мультиплексора 74 условий, первая группа входов которого соединена с третьей группой входов шифратора 11 управления, его вторая группа входов соединена с четвертой группой входов шифратора управления, третья группа входов соединена с второй группой входов шифратора управления, а его первый вход и второй вход мультиплексора 76 подключены к управляющему входу шифратора управления. Второй вход мультиплексора 74 условий соединен с первым входом шифратора 11 управления. Выход дешифратора 78 соединен с S-входом RS-триггера 79, выход которого подключен к второму выходу шифратора 11 управления. Выход мультиплексора 76 соединен с вторым выходом шифратора управления. Третья группа выходов памяти 70 микрокоманд соединена с третьей группой выходов шифратора 11 управления.

Формирователь 73 адреса микрокоманды (фиг. 9) содержит регистр 84, сумматор 85, стек 86, реверсивный счетчик 87 - указатель стека, мультиплексор 88, дешифратор 89 инструкций. Выходы мультиплексора 88 соединены с выходами формирователя 73 адреса микрокоманды и с входами сумматора 85, вход инкремента которого соединен с входом инкремента формирователя 73 адреса микрокоманды, а выходы подключены к входам регистра 84. Входы адреса формирователя 73 адреса микрокоманды соединены с первой группой входов мультиплексора 88, с второй группой входов которого соединены выходы стека 86, а с третьей группой входов и с входами стека 86 соединены выходы регистра 84. Входы инструкций формирователя 73 адреса микрокоманды соединены с входами дешифратора 89 инструкций, вход условий которого соединен с входом условий формирователя 73 адреса микрокоманды, выходы управления соединены с входами управления мультиплексора 88, а выход соединен с входом управления реверсного счетчика-указателя 87 стека и с входом управления стека 86. Выход дешифратора 89 инструкций соединен с выходом формирователя 73 адреса микрокоманды. Вход синхронизации формирователя 73 адреса микрокоманд соединен со счетным входом реверсивного счетчика-указателя 87 стека, с входом синхронизации стека, с входом синхронизации регистра 84. Выходы реверсивного счетчика-указателя 87 стека соединены с входами адреса стека 86.

Пример реализации приемника 12 показан на фиг. 10. Приемник содержит фифо 90 приема, мультиплексор 91, сдвиговый регистр 92, детектор 93 флага, RS-триггер 94, логику 95 циклического контроля, декодер 96, детектор 97 входного сигнала, счетчик 98 битов, счетчик 99 байтов, управляющую логику 100, шину 101. Выходы фифо 90 приема по шине 26 соединены с выходами приемника 12 и с первой группой входов мультиплексора 91. Выходы меток фифо 90 приема по шине 102 соединены с первой группой входов управляющей логики 100. Выходы сдвигового регистра 92 соединены по шине 103 с входами фифо 90 приема и с входами детектора 93 флага, выход которого соединен с S-входом RS-триггера 94. Выход декодера 96 соединен по линии 104 с входом сдвигового регистра 92 и с входом логики 95 циклического контроля. Выход синхронизации декодера 96 соединен по линии 105 с входом синхронизации сдвигового регистра 92, с входом синхронизации логики 95 циклического контроля и со счетным входом счетчика 98 битов. Вход декодера 96 и вход детектора 97 входного сигнала соединены с входом данных приемника 12. Выход контроля логики 95 циклического контроля по линии 106 соединен с первым входом мультиплексора 91. Выход RS-триггера 94 соединен с входом сброса счетчика 98 битов, выходы которого соединены с второй группой входов управляющей логики 100 и с второй группой входов мультиплексора 91. Выходы мультиплексора 91 соединены с входами-выходами приемника 12. Выход детектора 97 входного сигнала соединен с вторым входом мультиплексора 91 и с вторым входом управляющей логики 100. Выходы счетчика 99 байтов соединены с третьей группой входов мультиплексора 91 и с третьей группой входов управляющей логики 100, с четвертой группой входов которой соединена вторая группа входов управления приемника. Выходы состояний и выходы управления приемника 12, входы управления и входы меток фифо 90 приема, входы управления мультиплексора 91, входы управления логики 95 циклического контроля, счетный вход и вход сброса счетчика 99 байтов, R- вход RS-триггера 94, выходы управляющей логики 100 соединены с шиной 101. Пятая группа входов управляющей логики 100 соединена с первой группой входов управления приемника 12, к входам-выходам которого подключена шестая группа входов управляющей логики 100. Вход управления приемника 12 соединен с входом управляющей логики 100.

Пример выполнения передатчика 13 приведен на фиг. 11. Передатчик содержит фифо 107 передачи, сдвиговый регистр 108, логику 109 циклического контроля, коммутатор 110, кодер 111, счетчик 112 битов, управляющую логику 113, усилители 114, генератор 115, шину 116. Выходы фифо 107 передачи соединены по шине 117 с входами регистра 108 сдвига, выход которого по линии 118 подключен к первому входу коммутатора 110 и к входу логики 109 циклического контроля. Выход генератора 115 по линии 119 подключен к входу синхронизации кодера 111, к входу синхронизации управляющей логики 113, к входу синхронизации сдвигового регистра 108, к входу синхронизации логики 109 циклического контроля, к счетному входу счетчика 112 битов. Выход данных логики 109 циклического контроля соединен по линии 120 с вторым входом коммутатора 110, выход которого соединен по линии 121 с входом кодера 111. Выход кодера соединен с выходом передатчика 13. Входы-выходы передатчика соединены с пятой группой входов управляющей логики 113 и с выходами усилителей 114. Входы и входы управления усилителей 114, выходы состояний и выходы управления передатчика 13, входы меток и входы управления фифо 107 передачи, вход записи сдвигового регистра 108, входы управления логики 109 циклического контроля, вход управления коммутатора 110, вход сброса счетчика 112 битов, вход управления кодера 111, выходы управляющей логики 113 соединены с шиной 116. Выходы меток фифо 107 передачи соединены по шине 122 с первой группой входов управляющей логики 113, с второй группой входов которой соединены выходы счетчика 112 битов, с третьей группой входов соединена вторая группа входов управления передатчика 13, а с четвертой группой входов соединена первая группа входов управления передатчика. Входы передатчика 13 подключены по шине 27 к входам фифо 107 передачи. Вход передатчика 13 соединен с входом управляющей логики 113.

Пример выполнения кодера 111 показан на фиг. 12. Кодер содержит диод 123, резистор 124, инвертор 125, схемы 126, 127 совпадений, JK-триггеры 128, 129. Вход инвертора 125 и первый вход схемы 126 совпадений соединены с входом кодера 111. Выход инвертора 125 соединен с первым входом схемы 127 совпадений. Второй вход схемы 126 совпадений и второй вход схемы 127 совпадений соединены с инверсным выходом JK-триггера 129, J- и К-входы которого через резистор 124 подключены к шине питания для установки уровня "1". Выход схемы 126 совпадений соединен с J-входом JK-триггера 128, к К-входу которого подключен выход схемы 127 совпадений. Вход синхронизации JK-триггера 128 и вход синхронизации JK-триггера 129 подключены к входу синхронизации кодера 111. Выход JK-триггера 128 через диод 123 подключен к выходу кодера 111.

Пример выполнения декодера 96 показан на фиг. 13. Декодер содержит линию 130 задержки, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 131, 132, инвертор 133, D-триггеры 134, 135. Вход линии 130 задержки, первый вход схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 131, D-вход D-триггера 135 соединены с входом декодера 96. Второй вход схема ИСКЛЮЧАЮЩЕЕ ИЛИ 131 соединен с первым выходом линии 130 задержки, второй выход которой соединен с первым входом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 132, а третий выход - с вторым входом схема ИСКЛЮЧАЮЩЕЕ ИЛИ 132. Выход схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 131 соединен с входом инвертора 133, выход которого подключен к D-входу D-триггера 134. Выход схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 132 соединен с входом синхронизации D-триггера 134, выход которого подключен к выходу синхронизации декодера 96 и к входу синхронизации D-триггера 135. Инверсный выход D-триггера 135 подключен к выходу декодера 96.

Подключение контроллеров 20 к каналу 24 связи производится через некоторые расстояния. Такие подключения могут производиться, например, путем прокола коаксиального кабеля, применяемого для реализации канала 24 связи. По концам коаксиального кабеля в этом случае устанавливаются согласующие нагрузки 136 (фиг. 2).

Логика 109 циклического контроля передатчика 13 и логика 95 циклического контроля приемника 12 реализуют проверку данных с помощью полинома х15+х12+х5+1 и построены по одинаковой схеме (фиг. 14), в состав которой входят схема ИСКЛЮЧАЮЩЕЕ ИЛИ 137, схема 138 совпадений, пятиразрядный сдвиговый регистр 139, схема ИСКЛЮЧАЮЩЕЕ ИЛИ 140, семиразрядный сдвиговый регистр 141, схема ИСКЛЮЧАЮЩЕЕ ИЛИ 142, пятиразрядный сдвиговый регистр 143, мультиплексор 144, дешифратор 145. Вход логики циклического контроля соединен с первым входом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 137 и с первым входом мультиплексора 144. Вход синхронизации логики циклического контроля соединен по линии 119 для передатчика 13 и по линии 105 для приемника 12 с входами синхронизации регистров 139, 141, 143. Входы управления логики циклического контроля соединены с первым входом схемы 138 совпадений и входами управления мультиплексора 144. Выход данных логики циклического контроля соединен с выходом мультиплексора 144, к второму входу которого и второму входу схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 137 подключен выход сдвигового регистра 143. Выход схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 137 соединен с вторым входом схемы 138 совпадений, выход которой соединен с входом сдвигового регистра 139, с первыми входами схем ИСКЛЮЧАЮЩЕЕ ИЛИ 140, 142. Выход регистра 139 соединен с вторым входом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 140, выход которой соединен с входом сдвигового регистра 141. Выход сдвигового регистра 141 соединен с вторым входом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 142, выход которой соединен с входом сдвигового регистра 143. Выходы сдвигового регистра 139 соединены с первой группой входов дешифратора 145. Выходы сдвигового регистра 141 соединены с второй группой входов дешифратора 145. Выходы сдвигового регистра 143 соединены с третьей группой входов дешифратора 145, выход которого соединен с выходом контроля логики циклического контроля.

Фифо 90 приема и фифо 107 передачи являются памятью обратного магазинного типа, в которую входят (фиг. 15) оперативная память 146, оперативная память 147, мультиплексор 148, счетчики 149, 150. Входы фифо соединены с входами оперативной памяти 146, к выходам которой подключены выходы фифо. Входы фифо соединены с входами оперативной памяти 147, к выходам которой подключены выходы меток фифо. Входы управления фифо соединены с входами управления оперативной памяти 146, оперативной памяти 147, мультиплексора 148, счетчиков 149, 150. Выходы счетчика 149 соединены с первой группой входов мультиплексора 148, к второй группе входов которого подключены выходы счетчика 150. Выходы мультиплексора 148 соединены с входами адреса оперативной памяти 146 и оперативной памяти 147.

Запоминающее устройство 7 предназначено для хранения результатов арифметических и логических операций над данными. Операнды поступают на первую и вторую группы адресных входов запоминающего устройства 7, если операции производятся над двумя операндами, или поступают только на первую группу адресных входов запоминающего устройства 7, если операции производятся над одним операндом, при этом вторая группа входов используется для расширения разрядности сигналов управления запоминающим устройством 7. В последнем случае на вторую группу адресных входов и на входы управления запоминающего устройства 7 подают код выполняемой операции.

Запоминающее устройство 7 может быть реализовано, например, на основе постоянных программируемых запоминающих устройств или программируемых логических матриц. Программирование постоянных программируемых запоминающих устройств или программируемых логических матриц производится предварительно перед сборкой контроллера.

Запоминающее устройство 7 выполняет функции арифметико-логического устройства с нестандартным набором арифметических и логических команд, который выбирается индивидуально для каждого конкретного исполнения контроллера. Набор арифметических и логических команд реализуется путем программирования постоянных программируемых запоминающих устройств или программируемых логических матриц, входящих в состав запоминающего устройства 7. Нестандартный набор арифметических и логических команд при программировании запоминающего устройства 7 выбирается таким, чтобы повысить быстродействие контроллера и, в частности, за счет этого добиться сокращения аппаратурных затрат и расширения его функций.

При использовании постоянных программируемых запоминающих устройств для построения запоминающего устройства 7 в их ячейках памяти должны быть записаны результаты логических и арифметических операций над операндами, которые подаются на их адресные входы.

Примером программируемой в запоминающем устройстве 7 нестандартной арифметической операции может служить операция вычитания, выполняемая на запоминающем устройстве. Время выполнения такой операции меньше, чем время выполнения аналогичной операции на стандартных арифметико-логических устройствах, поскольку для выполнения этой операции не требуется перевода одного из операндов в дополнительный код. Программирование должно выполняться таким образом, чтобы результат операции читался на выходы запоминающего устройства 7 при подаче операндов на первую и вторую группы его входов, при подаче кода операции на входы управления и при подаче сигнала входного переноса на вход переноса запоминающего устройства 7.

Другим примером операции может служить операция умножения на константу. При этом запоминающее устройство 7 должно программироваться таким образом, чтобы при подаче множимого на первую группу адресных входов и при подаче на входы управления кода операции на выходах ячеек памяти запоминающего устройства 7 считывался результат операции, а выход переноса запоминающего устройства 7 мог указывать на то, что результат операции не вмещается в одно слово. В этом случае запоминающее устройство 7 программируется таким образом, чтобы при подаче кода операции извлечения из запоминающего устройства 7 следующего слова результата операции умножения на выходах запоминающего устройства 7 читалось следующее слово результата операции.

Если запоминающее устройство 7 выполнено односекционным на основе программируемого постоянного запоминающего устройства, то первая группа адресных входом запоминающего устройства 7 соединена с первой группой входов адреса программируемого постоянного запоминающего устройства, вторая группа входов адреса которого соединена с второй группой адресных входов запоминающего устройства 7, третья группа входов адреса соединена с входами управления запоминающего устройства 7, выходы соединены с выходами запоминающего устройства 7, вход адреса соединен с входом переноса запоминающего устройства 7, а выход - с выходом переноса запоминащего устройства 7.

Для выполнения операции вычитания предварительно перед сборкой контроллера программируемые постоянные запоминающие устройства программируются таким образом, что при подаче на входы управления запоминающего устройства 7 кода операции вычитания, на первую группу его адресных входов кода уменьшаемого, на вторую группу его адресных входов кода вычитаемого на выходы программируемого постоянного запоминающего устройства, являющиеся выходами запоминающего устройства 7, из его ячеек памяти считываются коды чисел, являющиеся разностью уменьшаемого и вычитаемого. Если уменьшаемое меньше вычитаемого, то на выходе переноса запоминающего устройства 7, являющемся выходом программируемого постоянного запоминающего устройства, из ячейки памяти, адрес которой определяется кодами уменьшаемого, вычитаемого и кодом операции, считывается сигнал выходного переноса. Сигнал входного переноса, подключаемый к одному из входов адреса программируемого постоянного запоминающего устройства, также влияет на результат операции, поскольку выбирается соответствующая ячейка памяти.

Если входов адреса программируемого постоянного запоминающего устройства недостаточно для выполнения операций над многоразрядными числами, то запоминающее устройство 7 выполняется секционированным. Каждая из секции 52 запоминающего устройства может выполняться на основе программируемого постоянного запоминающего устройства. При этом первая группа входов секции 52 запоминающего устройства предназначена для подачи нескольких разрядов уменьшаемого, вторая группа входов - нескольких разрядов вычитаемого, третья группа входов - кода операции, входы переноса секции 52 запоминающего устройства - выходных сигналов с выходов переноса запоминающего устройства 53 ускоренных переносов, входы переноса которого предназначены для подачи сигналов распространения и генерации переноса с выходов переноса секции 52 запоминающего устройства. Вход переноса запоминающего устройства 53 ускоренных переносов и вход переноса секции 52 запоминающего устройства предназначены для подачи на них сигнала входного переноса. Входы управления запоминающего устройства 53 служит для подачи на них сигналов кодов операции.

Запоминающее устройство 53 ускоренных переносов может быть выполнено, например, на основе программируемой логической матрицы или программируемого постоянного запоминающего устройства, которые программируются заранее перед сборкой контроллера таким образом, что при подаче на входы переносов сигналов распространения переноса и генерации переноса с выходов переноса секции 52 запоминающего устройства на выходах переносов запоминающего устройства 53 ускоренных переносов генерируются сигналы входных переносов для каждой из секций 52 запоминающего устройства, с учетом этих сигналов на выходах которых формируется результат операции.

Аналогично путем программирования в ячейках памяти запоминающего устройства 7 результатов операций реализуются операции сложения, сдвига, логического сложения и умножения. Кроме того, реализуются логические операции преобразования кодов, например преобразования кодов адреса с шины 18 адреса контроллера в коды адреса ячеек оперативной памяти 6. Реализуются логические операции преобразования слов состояний и управления в коды управления, которые подаются с выходов состояний запоминающего устройства 7 на первую группу входов шифратора 11 управления. По этим кодам управления контроллер переходит на тот или иной режим функционирования.

Каждая из операций, выполняемая на запоминающем устройстве 7, программируется таким образом, чтобы максимально уменьшить время реакции контроллера по отработке внешних воздействий и добиться выполнения процессов реального времени, например обеспечить обмен данными (словами управления и состояний) между шиной 17 данных контроллера и оперативной памятью 6 в режиме программного обмена со стороны ЭВМ 21 за время, отведенное для режимов чтения и записи на шине 17 данных. Операции, выполняемые на запоминающем устройстве 7, позволяют, например, обеспечить фильтрацию принимаемых из канала 24 связи пакетов по адресам назначения этих пакетов за промежутки времени, не превышающие время приема пакета минимальной длины.

Для расширения возможности запоминающего устройства 7 по хранению в его ячейках памяти результатов арифметических и логических операций над операндами, подаваемыми на его входы при выполнении однооперандных команд, вторая группа адресных входов запоминающего устройства 7 используется как группа управляющих входов, сигналы управления при этом подаются с второй и третьей групп выходов памяти 70 микрокоманд через регистровое устройство 8.

Контроллер 9 прерываний обеспечивает арбитраж запросов внутренних прерываний и формирует на своих выходах вектор внутренних прерываний для перевода контроллера в новый режим работы.

В качестве логической матрицы 66 может использоваться программируемая логическая матрица, программируемая перед установкой в контроллер. Программирование выполняется таким образом, что программируемая логическая матрица на своих выходах формирует сигналы вектора, значение которого определяется состоянием входов управления приоритетами, состоянием входов текущего приоритета и входов запросов. Программирование выполняется таким образом, что если состояние входов управления приоритетами определяет приоритет более высокий, чем запрашиваемый приоритет на входах запроса логической матрицы 66, то на ее выходе управления не формируется сигнал запроса. Если на входах запроса запрашиваемый приоритет равен или выше приоритета на входах управления приоритета и на первой группе входов логической матрицы 66 (выше текущего приоритета), то на выходах логической матрицы 66 должны формироваться сигналы вектора внутренних прерываний, соответствующие наивысшему из запрашиваемых приоритетов на входах запроса, а на выходе управления логической матрицы 66 должен формироваться сигнал запроса.

Регистр 67 служит для хранения сигнала запроса, который вместе с сигналами вектора внутренних прерываний по тактовому импульсу на входе синхронизации регистра 67 вектора прерываний переписывается на его выходы и на выход управления.

Приоритеты могут распределяться следующим образом. Наивысшим приоритетом обладают режим инициализации контроллера, затем его режимы чтения и записи при работе в программном обмене с ЭВМ 21, затем режимы перехода на прямой доступ к памяти ЭВМ 21 - переход на эти режимы производится после выполнения внутренних прерываний по сигналам запросов с выходов контроллера 2 шины. Следующий по значению приоритет у программы фильтрации принимаемых пакетов по адресам назначения. Запросы на прерывания для этого режима поступают с второй группы выходов состояний приемника 12. Следующий по приоритету запрос с выходов состояний передатчика 13 на прерывание по концу передачи пакета. Наиболее низкий приоритет поступает на вход запроса контроллера 9 прерываний при переходе на подпрограмму таймера-задатчика.

Шифратор 11 управления предназначен для формирования управляющих сигналов на узлы контроллера. Управляющие сигналы, в частности, могут формироваться в виде последовательности микрокоманд. Ргеистр 68 микрокоманд предназначен для временного хранения микрокоманд и для выдачи микрокоманд с первой группы выходов регистра 68 микрокоманд на шину 16 управления контроллера и с второй его группы выходов на шину 80 управления. Память 70 микрокоманд предназначена для хранения микрокоманд и констант. В качестве памяти 70 микрокоманд может быть использовано программируемое постоянное запоминающее устройство. Константы считываются с второй группы выходов памяти 70 микрокоманд. Последовательность выборки микрокоманд из памяти 70 микрокоманд обеспечивается подачей на ее входы адреса сигналов адреса, формируемых формирователем 73 адреса микрокоманды, дешифратором-преобразователем 72 начального адреса, контроллером 9 прерываний. Мультиплексор 71 предназначен для коммутации сигналов адреса с выходов формирователя 73 адреса микрокоманды, дешифратора-преобразователя 72 начального адреса, контроллера 9 прерываний на входы адреса памяти 70 микрокоманд. Дешифратор-преобразователь 72 начального адреса преобразует сигналы управления с выходов запоминающего устройства 7 в адреса памяти 70 микрокоманд. Генератор 75 синхронизирует работу шифратора 11 управления. По его импульсам осуществляются смена микрокоманд в регистре 68 микрокоманд, синхронизация формирователя 73 адреса микрокоманды, счетчика-таймера 77, контроллера 9 прерываний и регистрового устройства 8. Мультиплексор 69 позволяет выполнить переключение сигналов констант с второй группы выходов памяти 70 микрокоманд и сигналов интервалов времени с выходов счетчика-таймера 77 на первую группу входов регистрового устройства 8. Мультиплексор 76 обеспечивает по сигналам на своих входах управления переключение сигнала входного переноса или с выхода переноса запоминающего устройства 7, или с шины 80 управления на вход переноса запоминающего устройства 7. Мультиплексор 74 условий переключает со своих входов на вход условий формирователя 73 адреса микрокоманды сигналы условий. Счетчик-таймер 77 предназначен для синхронизации работы программных таймеров контроллера по сигналам с его выходов. Дешифратор 78 по достижении на выходах счетчика-таймера 77 определенного значения сигналов на своем выходе формирует сигнал, опрокидывающий RS-триггер 79. RS-триггер 79 формирует сигнал запроса прерываний контроллера 9 прерываний при переходе на подпрограмму таймера-задатчика.

Формирователь 73 адреса микрокоманды формирует адреса микрокоманд, которые поступают на его выходы или с выходов регистра 84, или с выходов стека 86, или с шины 80 управления через его входы адреса. Сумматор 85 при наличии на входе инкремента сигнала единицы наращивает адрес микрокоманды на единицу, что дает возможность формировать последовательность адресов. Стек 86 при переходе на подпрограмму обеспечивает загрузку адреса микрокоманды из регистра 84 в стек 86 с последующей его выгрузкой на выходы стека 86 при выходе из подпрограммы. Дешифратор 89 предназначен для установки режимов работы формирователя 73 адреса микрокоманды по сигналам на входах инструкций дешифратора 89. В соответствии с сигналом на входе условий на его выходах формируются сигналы управления узлами формирователя 73 адреса микрокоманды. Синхронизация узлов формирователя 73 адреса микрокоманды производится по импульсам, поступающим через его вход синхронизации с генератора 75. По этим импульсам производятся наращивание или вычитание содержимого реверсивного счетчика-указателя 87 стека, запись в стек 86, запись в регистр 84. Регистр 84 служит для временного хранения адресов микрокоманд, которые записываются в регистр 84 с выходов сумматора 85 по тактовым импульсам, поступающим на вход синхронизации регистра 84. Реверсивный счетчик-указатель 87 стека формирует сигналы адреса на входах адреса стека 86, необходимые для выбора ячеек памяти в стеке 86. Мультиплексор 88 служит для коммутации сигналов с выходов стека 86, с выходов регистра 84, с входов адреса формирователя 73 адреса микрокоманды на выходы формирователя адреса микрокоманды.

Контроллер 2 шины обеспечивает управление процессом обмена данными между ЭВМ 21 и контроллером. В режимах программного обмена, прямого доступа к памяти и в режиме прерывания сигналы на входах управления контроллера 2 шины задают режимы его работы. Контроллер 2 шины обеспечивает управление интерфейсом 1, приемником 12, передатчиком 13, селектором 10 адреса сигналами, подаваемыми с выходов управления контроллера 2 шины. Контроллер 2 шины при обмене данными с ЭВМ 21 выполняет обмен сигналами управления с ЭВМ 21 по системной шине 19 управления.

Дешифратор 59 предназначен для формирования сигналов, обеспечивающих управление процессом обмена данными между ЭВМ 21 и контроллером. Таймерное устройство 60 формирует сигналы, которые позволяют дешифратору 59 при формировании сигналов, управляющих процессом обмена данными, выдерживать требуемые на системной шине ЭВМ 21 временные соотношения. Усилители 58 предназначены для согласования цепей шины 19 управления контроллера с цепями контроллера 2 шины.

Интерфейс 1 предназначен для сопряжения шины 17 данных и шины 18 адреса контроллера с его внутренними цепями. Интерфейс 1 под управлением сигналов с выходов управления контроллера 2 шины выполняет обмен данными между шиной 17 данных и узлами контроллера. Интерфейс 1 пересылает сигналы адреса в режиме программного обмена с шины 18 адреса на адресные входы селектора 10 адреса и на первую группу входов мультиплексора 14 или пересылает в режиме прямого доступа к памяти сигналы адреса с разрядных выходов счетчика 3 адреса на шину 18 адреса контроллера.

Усилители 54 и 55 являются двунаправленными и предназначены для согласования внутренних цепей контроллера с его шиной 17 данных и шиной 18 адреса. Усилители 54 коммутируют сигналы адреса с разрядных выходов счетчика 3 адреса на шину 18 адреса или шины 18 адреса на первую группу входов мультиплексора 14. Усилители 55 коммутируют сигналы данных между шиной 17 данных контроллера и выходами регистра 56, а также второй группой входов мультиплексора 14 и входами передатчика 13. Регистр 56 предназначен для временного хранения данных, пересылаемых из контроллера на шину 17 данных. Коммутатор 57 предназначен для коммутации данных на входы регистра 56 с внутренней шины 15 контроллера или с выходов приемника 12.

Регистровое устройство 8 предназначено для хранения данных, загружаемых в его регистры 63 с выходов запоминающего устройства 7 с внутренней шины 15, а также для хранения констант, загружаемых с второй группы памяти 70 микрокоманд через мультиплексор 69, и хранения сигналов управления, загружаемых с третьей группы выходов памяти микрокоманд. Регистровое устройство 8 выдает сигналы из регистров 63 на входы адреса оперативной памяти 6, на внутреннюю шину 15 контроллера, на вторую группу адресных входов и на вход управления запоминающего устройства 7. Регистры 63 являются памятью со стековой организацией и служат для хранения данных, записываемых в регистры 63 под управлением сигналов с входов управления регистрового устройства 8 по синхроимпульсам с входа синхронизации регистрового устройства 8. Стековая организация памяти позволяет уменьшить время перехода на подпрограммы. Реверсивный счетчик 65 служит указателем стека, и его выходные сигналы, подаваемые на входы адреса регистров 63, позволяют производить выбор ячеек памяти регистров 63. Реверсивный счетчик 65 под управлением сигналов с входов управления регистрового устройства 8 позволяет наращивать или уменьшать адреса ячеек памяти регистров 63 при подаче на вход синхронизации реверсивного счетчика 65 синхроимпульсов с выхода генератора 75. Мультиплексор 62 предназначен для переключения входных, а мультиплексор 61 - для переключения выходных сигналов регистров 63 по сигналам с входов управления регистрового устройства 8. Двунаправленные усилители 64 служат для коммутации сигналов между входами-выходами регистрового устройства 8, выходами регистров 63, коммутируемыми через мультиплексор 61, или входами регистров 63, коммутируемыми через мультиплексор 62.

Оперативная память 6 служит для хранения в ее ячейках слов состояний и управления, которыми ЭВМ 21 и контроллер обмениваются в режиме программного обмена и режиме прямого доступа к памяти. Там же хранится вектор прерывания. Кроме того, оперативная память служит для хранения данных, необходимых для функционирования контроллера.

Мультиплексор 14 служит для коммутации данных на внутреннюю шину 15 контроллера, поступающих с шины 17 данных через интерфейс 1 на вторую группу входов мультиплексора 14, или коммутации сигналов адреса, поступающих с шины 18 адреса через интерфейс 1 на первую группу входов мультиплексора 14.

Счетчик 3 адреса предназначен для формирования сигналов адреса, которые в режиме прямого доступа поступают через интерфейс 1 на шину 18 адреса для адресации к памяти ЭВМ 21. Счетчик 3 адреса обеспечивает параллельную загрузку начального адреса с внутренней шины 15 контроллера и дальнейший отсчет адресов импульсов с выходов контроллера 2 шины.

Регистр 4 адреса служит для хранения конечного адреса зоны памяти ЭВМ 21, загружаемого в него с внутренней шины 15.

Схема 5 сравнения предназначена для формирования на ее выходе сигнала сравнения при равенстве содержимого счетчика 3 адреса и регистра 4 адреса, что позволяет определить момент, когда при чтении или записи в режиме прямого доступа к памяти обращение выполнено ко всем ячейкам памяти ЭВМ 21, начиная от начального адреса, загруженного по входам данных в счетчик 3 адреса, и заканчивая конечным адресом, загруженным в регистр 4 адреса.

Селектор 10 адреса предназначен для селекции адресов шины 18 адреса контроллера, с которым ЭВМ 21 обращается к контроллеру в режиме программного обмена. При этом с выходов управления контроллера 2 шины в режиме программного обмена при наличии сигналов адресов на шине 18 адреса на входы управления селектора 10 адреса поступают сигналы разрешения селекции. При распознании адреса селектора 10 адреса на своих выходах формирует сигналы запросов внутренних прерываний, поступающих на четвертую группу входов запросов контроллера 9 прерываний. Селектор 10 адреса предназначен для формирования сигналов запросов прерываний по чтению или по записи данных в режиме программного обмена в зависимости от того, производит ЭВМ 21 запись в котроллер или чтение данных.

Приемник 12 предназначен для приема с входа контроллера последовательного потока данных, представленных кодом Манчестер-11, декодирования принимаемых данных в код без возвращения к нулю, преобразования принимаемых данных в параллельный шестнадцатиразрядный код слов данных. Приемник 12 буферизирует принимаемые данные в фифо 90 приема и через свои выходы в режиме прямого доступа передает слова данных через интерфейс 1 на шину 17 данных контроллера. Он поддерживает режим прямого доступа к памяти, формируя на своих выходах управления сигналы управления контроллером 2 шины в режиме прямого доступа, и контролирует ошибки контроля в принимаемом сигнале и наличие передач в кабеле связи (контроль несущей). Приемник 21 различает в принимаемом коде ограничитель преамбулы, после которого следуют данные пакета, и формирует по числу принятых данных на своих выходах состояний сигнал требования внутренних прерываний на фильтрацию адресов назначений принимаемых пакетов, а также формирует биты состояний, определяющие качество принятого пакета, правильную его длину в битах и словах.

Декодер 96 предназначен для преобразования кода Манчестер-11 в код данных без возвращения к нулю на выходе декодера 96, сопровождаемый тактовыми синхроимпульсами на его выходе синхронизации. Сдвиговый регистр 92 служит для преобразования последовательного кода данных без возвращения к нулю в параллельный код шестнадцатиразрядных слов данных. Фифо 90 приема предназначено для временной буферизации принимаемых данных, что позволяет выполнить согласование скоростей обмена данными по каналу 24 связи и по шине 17 данных контроллера. Оно предназначено для хранения меток конца кадра, которыми метится последнее слово принятого пакета. Детектор 93 флага определяет момент приема ограничителя преамбулы в принимаемом пакете и вырабатывает при этом сигнал, который по S-входу опрокидывает RS-триггер 94, и с этого момента начинается прием данных из канала 24 связи. RS-триггер 94 формирует на своем выходе сигнал сброса счетчика 98 битов. Детектор 97 входного сигнала предназначен для формирования на его выходе сигнала несущей при наличии передач в канале 24 связи. Логика 95 циклического контроля предназначена для выявления ошибок в принимаемых пакетах. Контроль ошибок выполняется на основе полинома степени 16. При наличии ошибок в пакет на выходе контроля логики циклического контроля формируется сигнал ошибки. Счетчик 98 битов позволяет производить подсчет принимаемых битов данных по синхроимпульсам на его счетом входе и, таким образом, определять кратность принимаемых данных числу восемь для выявления байтовых границ принимаемых пакетов. Некратность числу восемь определяет ошибку приема. По счетчику 98 битов управляющая логика 100 формирует синхроимпульсы для подачи их на счетный вход счетчика 99 для подсчета числа принятых байтов в пакете. Счетчик 99 байтов предназначен для подсчета числа принимаемых байтов в пакете. Управляющая логика 100 предназначена для управления работой узлов приемника 12 и формирует на своих выходах сигналы запросов внутренних прерываний на фильтрацию пакетов по адресам назначения, которые выдаются на выходы состояний приемника. Управляющая логика 100 формирует на выходах приемника 12 сигналы состояний приема, которые подаются на третью группу входов мультиплексора 74 условий, и формирует на своих выходах, подключенных к выходам управления приемника 12, сигналы, управляющие работой контроллера 2 шины в режиме прямого доступа к памяти. Мультиплексор 91 предназначен для коммутации на внутреннюю шину 15 контроллера данных с выходов фифо 90 приема или битов состояний с шины 106, с выходов счетчика 98 битов, с выхода детектора 97 входного сигнала и с выхода логики 95 циклического контроля.

Передатчик 13 предназначен для обмена передаваемыми данными с ЭВМ 21 и внутренней шины 15 контроллера, а также для предварительной буферизации передаваемых данных в фифо 107 передачи и для последующего преобразования данных в код Манчестер-11 и передачи его в канал 24 связи. Передатчик 13 перед передачей пакета данных передает в канал 24 связи преамбулу, завершая ее ограничителем преамбулы, а завершает передачу пакета контрольной суммой, сгенерированной логикой 109 циклического контроля. Фифо 107 передачи предназначен для временного хранения передаваемых пакетов данных. Сдвиговый регистр 108 предназначен для преобразования передаваемых данных в последовательный код без возвращения к нулю. Логика 109 логического контроля предназначена для генерации контрольной суммы при делении передаваемых данных на полином степени 16. Логика циклического контроля аналогична имеющейся в прототипе. Коммутатор 110 предназначен для коммутации на вход кодера 111 данных с выхода сдвигового регистра 108 или контрольной суммы с выхода логики 109 циклического контроля, передаваемой после передачи последнего бита данных. Усилители 114 предназначены для согласования шины 116 и внутренней шины 15 контроллера при передаче на внутреннюю шину 15 битов состояний с выходов управляющей логики 113. Управляющая логика 113 предназначена для управления работой узлов передатчика 13. Она формирует и подает на вход меток фифо 107 передачи сигналы меток, которыми метится последнее слово передаваемого пакета при записи его в фифо 107 передачи. Управляющая логика 113 вырабатывает сигналы управления на входах управления фифо 107 передачи, по которым выполняется запись слов данных с входов передатчика 13 в фифо 107 передачи или чтение передаваемых слов данных на выходы фифо 107 передачи.

Управляющая логика 113 формирует при передаче пакета сигнал записи слов на входе записи сдвигового регистра 108 по состоянию выходов счетчика 112 битов, когда все биты предыдущего слова сдвинуты регистром 108, и формирует на входах управления логики 109 циклического контроля сигналы управления, по которым логика циклического контроля генерирует контрольную сумму для передаваемого пакета или выдает контрольную сумму на свой выход побитно, синхронизируя наличие каждого из битов контрольной суммы на выходе синхроимпульсами с выходам генератора 115. Управляющая логика 113 формирует сигналы управления на входе управления коммутатора 110, по которым производится коммутация сигналов или с выхода сдвигового регистра 108, или с выхода логики 109 циклического контроля на вход кодера 111. Она формирует сигнал сброса счетчика 112 битов, что позволяет последнему в отсутствие сигнала сброса производить счет синхроимпульсов с выхода генератора 115. Это необходимо для формирования управляющей логикой 113 по сигналам с выходов счетчика 112 битов сигналов управления для последовательного считывания слов из фифо 107 передачи и перезаписи их в сдвиговый регистр 108. Управляющая логика 113 формирует на выходах состояний вектор внутренних прерываний по концу передачи пакета для запроса внутренних прерываний по второй группе входов запросов внутренних прерываний контроллера 9 прерываний. Она формирует на входах управления усилителей 114 сигнал управления, по которому слова состояний передачи пересылаются через усилители 114 с выходов состояний передачи на внутреннюю шину 15 контроллера. Сигнал управления на входах управления усилитей 114 формируется при запросе слова состояния передатчика 13 по его второй группе входов управления со стороны шифратора 11 управления. Управляющая логика 113 формирует на входах управления фифо 107 передачи сигнала управления записью слов данных при наличии на выходах управления контроллера 2 шины сигналов управления записью, поступающих на первую группу входов управления передатчика 13. При этом слова данных с входов передатчика 13 записываются в фифо 107 передачи. Логика 113 управления в синхронном режиме по сигналам управления с выходов управления контроллера 2 шины, формируемых в режиме записи прямого доступа к памяти ЭВМ 21, формирует на выходах управления передатчика 13 сигналы синхронизации, поддерживающие обмен между ЭВМ 21 и передатчиком 13. Логика 113 управления прекращает обмен данными с ЭВМ 21, снимая сигнал занятости с выходов управления передатчика 13 при наличии на входе передатчика сигнала сравнения с выхода "Равно" схемы 5 сравнения. Она имеет связь с внутренней шиной 15 контроллера через пятую группу своих входов. Это позволяет уменьшить число входов управления на второй группе входов управления передатчика 13 за счет того, что сигналы управления передатчиком подаются одновременно по внутренней шине 15 контроллера и по второй группе входов управления передатчика 13. Счетчик 112 битов служит для счета числа битов принятых данных. Кодер 111 предназначен для преобразования последовательного кода данных и кода контрольной суммы в код Манчестер-11.

Схема 126 совпадений формирует на своем выходе инверсный код с возвращением к нулю передаваемых данных. Инвертор 125 и схема 127 совпадений формируют на своем выходе инверсный код с возвращением к нулю инвертированных передаваемых данных. JK-триггер 128 формирует на своем выходе код Манчестер-11. JK-триггер 129 является делителем частоты и формирует на своем выходе импульсы, подаваемые на вторые входы 126 и 127 совпадений.

Линия 130 задержки декодера 96 служит для фазовой задержки принимаемого кода Манчестер-11. Схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 131, 132, инвертор 133 и D-триггер 134 служат для выделения синхронизирующей тактовой частоты из принимаемого кода Манчестер-11. D-триггер 135 служит для формирования из принимаемого сигнала кода данных без возвращения к нулю. Схема ИСКЛЮЧАЮЩЕЕ ИЛИ 137, схема 138 совпадений, сдвиговый регистр 139, схема ИСКЛЮЧАЮЩЕЕ ИЛИ 140, сдвиговый регистр 141, схема ИСКЛЮЧАЮЩЕЕ ИЛИ 142, сдвиговый регистр 143 служат для вычисления контрольной суммы при делении входного кода данных на образующий полином х15+х12+х5+1.

Мультиплексор 144 служит для коммутации на выход данных входных данных, подаваемых на его первый вход, или кода контрольной суммы, подаваемого на его второй вход. Это позволяет выполнять передачу кода контрольной суммы после передачи пакета данных. Дешифратор 145 по сигналам на его входах формирует на своем выходе контроля сигнал ошибки контрольной суммы при наличии ошибки в принимаемых на вход логики циклического контроля данных.

Оперативная память 146 служит для временного хранения принимаемых или передаваемых данных, что позволяет согласовывать скорости обмена в канале 24 связи и на шине 17 данных контроллера. Оперативная память 147 служит для хранения сигналов меток, которыми размечаются слова принимаемых или передаваемых данных. Мультиплексор 148 переключает сигналы адресов с выходов счетчиков 149 и 150 на входы адреса оперативной памяти 146 и оперативной памяти 147. Счетчик 149 служит для формирования адреса при записи слов данных в оперативную память 146. Счетчик 150 служит для формирования адреса при считывании слов данных из оперативной памяти 147.

Работает контроллер следующим образом.

Перед началом работы ЭВМ 21 инициализирует контроллер. Его инициализация осуществляется или при подаче сигнала инициализации по системной шине 19 управления со стороны ЭВМ 21, или программной инициализацией. В режиме инициализации контроллер записывает в оперативную память 6 слова начальных состояний слов состояний и управления. Переход на подпрограмму инициализации осуществляется при запросе прерывания на третьей группе входов запросов прерываний контроллера 9 прерываний. Эти запросы поступают с выходов контроллера 2 шины при наличии на его входах-выходах сигнала инициализации со стороны ЭВМ 21.

Переход на подпрограмму инициализации может быть произведен при записи первого слова состояний из ЭВМ 21 в контроллер в режиме программного обмена. В процессе работы контроллер обменивается данными с ЭВМ 21 в режиме программного обмена и в режиме прямого доступа к памяти ЭВМ 21. В режиме программного обмена контроллер и ЭВМ 21 обмениваются словами состояний и словами управления. В режиме прямого доступа к памяти ЭВМ 21 контроллер обменивается с ЭВМ 21 принимаемыми из канала 24 связи или передаваемыеми в канал 24 связи пакетами, а также данными управления. Слова состояний и управления хранятся в оперативном запоминающем устройстве 7. Обмен данными в режиме прямого доступа к памяти ЭВМ 21 может производиться группами слов без возврата системной шины в пользование ЭВМ 21.

Обмен данными в режимах программного обмена и прямого доступа к памяти осуществляется при управлении узлами контроллера микрокомандами, которые выбираются из памяти 70 микрокоманд во время выполнения соответствующих подпрограмм, описанных далее. Переход на какую-либо управляющую подпрограмму возможен при формировании вектора внутренних прерываний на выходах контроллера 9 прерываний, а также при формировании кода начального адреса управляющей подпрограммы на выходах запоминающего устройства 7, а также по адресам ветвлений, подаваемых с второй группы выходов регистра 68 микрокоманд на входы адреса формирователя 73 адреса микрокоманды. По векторам внутренних прерываний выполняются переходы на управляющие подпрограммы обслуживания внутренних прерываний, в число которых входят подпрограммы, перечисляемые далее в порядке убывания их приоритетности: подпрограмма инициализация контроллера, подпрограммы чтения и записи при программном обмене данными между ЭВМ 21 и контроллер, подпрограмма прямого доступа к памяти, подпрограмма фильтрации принимаемых пакетов по адресам назначения, подпрограмма таймера-задатчика.

Код начального адреса управляющих подпрограмм формируется на выходах запоминающего устройства 7 в результате выполнения нестандартных логических операций над словами управления и состояний. Код начального адреса управляющих подпрограмм преобразуется на выходах дешифратора-преобразователя 72 начального адреса в адрес памяти 70 микрокоманд.

Обмен данными, представляющими собой пакеты информации, слова управления и слова состояний, выполняется между контроллером, ЭВМ 21, приемником 12 и передатчиком 13. Приемник 12 принимает из канала 24 связи пакеты данных. Передатчик 13 передает в канал 24 связи пакеты данных. В режиме программного обмена ЭВМ 21 обращается к контроллеру по нескольким адресам шины 18 адреса для выполнения циклов чтения или записи.

Передача пакетов (фиг. 16) начинается с передачи преамбулы - чередующейся последовательности единиц и нулей, заканчивающейся двумя единицами - ограничителем преамбулы. Преамбула необходима для синхронизации приемников 12 всех устройств, подключенных к каналу 24 связи. Ограничитель преамбулы отделяют преамбулу от поля номера устройства, ведущего передачу (поле НУП), в котором передается уникальный номер устройства в локальной вычислительной сети. Этим номером определяется порядок передач пакетов устройствами. В поле управления указывается тип передаваемого пакета. Установленный бит 15 или бит 14 указывает на то, что передается пакет устройства-монитора. Установленный бит 13 указывает, что передается пакет маркера.

Устройство-монитор предоставляет право на передачу пакетов в канал 24 связи устройствам. Пакет монитора может содержать произвольные данные. Пакет верхних уровней локальной вычислительной сети имеет в поле управления нулевые биты 15, 14 и 13, установленные в ноль.

В поле адреса назначения указывается 48-битный адрес назначения пакета. Адрес назначения может быть индивидуальный (первый бит адреса установлен в ноль), групповым (первый бит адреса установлен в единицу) или широковещательным (все биты адреса установлены в единицу). В поле адреса источника указывается адрес устройства - отправителя пакета. В поле данных содержатся данные пакета. В поле контроля суммы передается контрольная сумма для данных, содержащихся в полях, передаваемых после ограничителя преамбулы.

Установленный бит 15 в поле управления означает, что передаваемый пакет является пакетом маркера. Установленный бит 14 в поле управления означает, что станция, передающая пакет, готовится стать станцией-монитором. Установленный бит 13 в поле управления означает, что передается пакет станции-монитора.