Настоящее изобретение относится к области передачи цифровых данных в высокоскоростных последовательных коммуникационных интерфейсах, используемых в каналах типа «точка-точка». Данное устройство может найти применение при построении распределенных вычислительных систем, используемых, в том числе, в бортовых вычислительных комплексах.

В качестве аналога из уровня техники известно устройство кодирования 8b/10b, применяемое при последовательной передаче данных по каналу, представляющему собой одну волоконно-оптическую линию связи [Patent US №6295010 B1. 8b/10b Encoded system and method. Data of patent: Sep.25, 2001. Appl. No.: 09/345,913. Filed: Jul. 1, 1999]. Устройство реализует известный способ кодирования 8b/10b ["Fibre Channel - Physical and Signaling Interface (FC-PH) - Rev 4.3", Proposed Working Draft, American National Standard for Information Systems, pp.1-387 (Jun. 1, 1994)]. Для представления восьми битов данных применяется избыточное кодирование в виде 10-битового символа, что позволяет обнаруживать некоторые ошибки при передаче данных в канале вследствие наличия запрещенных избыточных комбинаций. Для обеспечения поэлементной (побитовой) синхронизации при данном кодировании, относящегося к самосинхронизирующимся кодам, необходимо периодически передавать специальный символ (К-символ), который используется приемником для подстройки фазы своего задающего генератора под фазу задающего генератора передатчика. Такая схема фазовой подстройки является сложной и требует специальной проработки на аналоговом уровне. Так как оба генератора должны работать на одинаковой фиксированной частоте, то уход частоты хотя бы одного генератора означает рассинхронизацию процесса передачи и отказ канала. Таким образом, недостатком этого устройства и известного способа кодирования 8b/10b является ограничение более чем на 20% пропускной способности канала и низкая надежность, что имеет существенное значение для бортовых и встраиваемых применений.

Ближайшим аналогом к заявляемому устройству является устройство формирования DS-кода, используемое в коммуникационном интерфейсе [PATENT GB №91304711.4. Communication interface for serial transmission of variable length data tokens / Priority 25.05.90, №9011700. Data of filing 24.05.91. Data of publication 27.11.91. Bulletin 91/48 of European Patent Office. Publication number 0458648A2] для соединения как минимум двух хост-систем (компьютеров или процессорных модулей), причем устройство формирования DS-кода содержит первый блок DS-кодирования битов, блок формирования D-сигналов и блок формирования S-сигналов, выход стробирования которого является выходом стробирования коммуникационного интерфейса устройства, выход данных блока формирования D-сигналов является выходом данных коммуникационного интерфейса устройства, вход полного кода символа устройства соединен с входом битов символа первого блока DS-кодирования битов, вход числа битов которого соединен с входом длины символа устройства, вход записи которого является входом записи первого блока DS-кодирования битов, вход сброса которого является входом сброса устройства и соединен с входами сброса блоков формирования D- и S-сигналов, первые информационные входы которых соединены соответственно с выходом битов данных и выходом стробов первого блока DS-кодирования битов, который содержит первый сдвигающий регистр, первый счетчик, первый формирователь стробов, первый триггер бита и первый триггер строба, выход которого соединен с первым входом первого формирователя строба и является выходом стробов первого блока DS-кодирования битов, вход битов символа которого является информационным входом первого сдвигающего регистра, информационный выход которого соединен со вторым входом первого формирователя строба и информационным входом первого триггера бита, выход которого соединен с третьим входом первого формирователя строба и является выходом битов данных первого блока DS-кодирования битов, вход сброса которого соединен с входами сброса первого сдвигающего регистра, первого триггера бита, первого триггера строба и первого счетчика, информационный вход которого является входом числа битов первого блока DS-кодирования битов, вход записи которого является входом загрузки первого счетчика, выход которого соединен с входом разрешения первого сдвигающего регистра и является выходом готовности первого блока DS-кодирования битов, вход синхронизации которого соединен с входами синхронизации первого сдвигающего регистра, первого счетчика, первого триггера бита, первого триггера строба и первого формирователя строба, выход которого соединен с информационным входом первого триггера строба, причем блок формирования D-(S-) сигналов содержит первый триггер D-(S-)сигнала, вход синхронизации которого является первым входом синхронизации блока формирования D-(S-)сигналов, вход сброса которого является входом сброса первого триггера D-(S-)сигнала, информационный вход которого является первым информационным входом блока формирования D-(S-) сигналов.

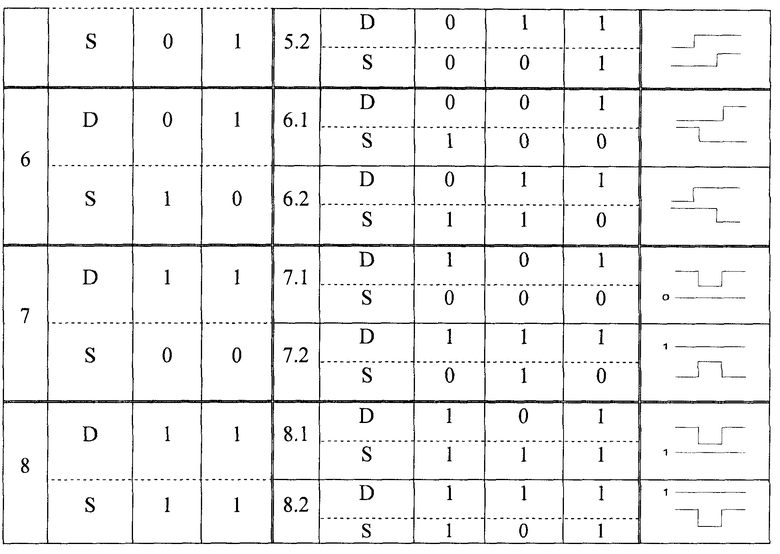

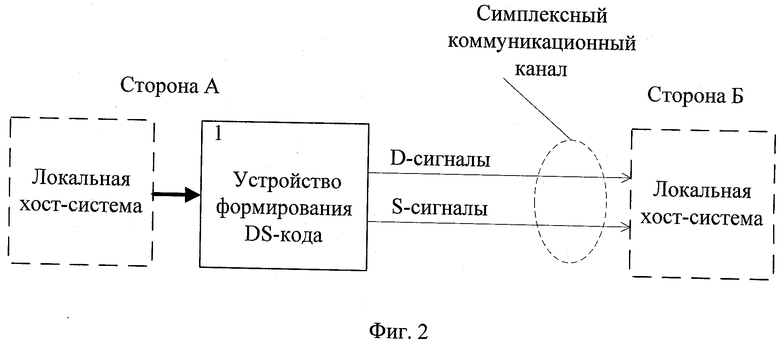

Данное устройство реализует способ формирования из последовательности битов символа данных DS-кода, состоящего из последовательности сигналов данных D, принимающих значения соответствующих битов данных и передаваемых по отдельной линии данных коммуникационного интерфейса, и последовательности сигналов стробов S, передаваемых по отдельной линии стробирования коммуникационного интерфейса, причем состояние сигнала строба S изменятся на противоположное на границе двух смежных битовых интервалов всякий раз, когда сигналы данных в этих смежных битовых интервалах не меняют свое состояние (см. фиг.1). Данное кодирование обеспечивает более надежную синхронизацию при приеме данных по сравнению с кодированием 8b/10b, так как на приемной стороне коммуникационного интерфейса путем объединения D-сигнала и S-сигнала по функции ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR) формируется синхросигнал, изменяющий свое состояние в каждом битовом интервале, что позволяет его использование для приема сигналов данных D и дальнейшего формирования битов символов данных. Так как отпадает необходимость передачи специальных символов для обеспечения синхронизации, то соответственно повышается пропускная способность коммуникационного канала. По сравнению с традиционной параллельной синхронизацией использование DS-кодирования для передачи данных в коммуникационном интерфейсе позволяет снизить энергопотребление без снижения скоростных характеристик за счет того, что в один момент времени может происходить изменение только одного сигнала, либо сигнала стробирования S, либо сигнала данных D.

Недостатком этого устройства, осуществляющего DS-кодирование символов данных, является повышенное энергопотребление из-за того, что все элементы известного устройства работают на той же частоте, на которой осуществляется подготовка битов символов данных к выдаче и их последующая передача через коммуникационный интерфейс. Такой подход ограничивает возможность повышения быстродействие устройства, поскольку приводит к излишнему росту энергопотребления, что сужает область применения устройства и, в частности, использование в бортовых системах и для встраиваемых применений.

Техническим результатом предлагаемого изобретения являются способ формирования DS-кода и устройство, его реализующее, которые обеспечивают расширение области применения за счет снижения роста энергопотребления при повышении быстродействия путем уменьшения в два раза частоты, на которой работают все элементы устройства формирования DS-кода, по сравнению с частотой передачи сигналов данных и стробирования через коммуникационный интерфейс.

Настоящее изобретение предназначено для энергосберегающего кодирования сигналов при организации высокоскоростного обмена информацией между процессорными узлами или компьютерами по последовательному интерфейсу при использовании DS-кодирования и может быть использовано при создании высокопроизводительных многопроцессорных вычислительных систем и распределенных вычислительных комплексов для применения в широких областях, требующих пониженного энергопотребления и повышения быстродействия. В предлагаемом техническом решении это достигается путем независимого DS-кодирования разделенного на два потока битов символов данных - нечетных и четных битов. Таким образом, данное устройство может быть эффективно использовано при создании высокоскоростных распределенных бортовых вычислительных комплексов, а также в различных встраиваемых применениях.

Технический результат достигается тем, что в устройстве формирования DS-кода, содержащем первый блок DS-кодирования битов, блок формирования D-сигналов и блок формирования S-сигналов, выход стробирования которого является выходом стробирования коммуникационного интерфейса устройства, выход данных блока формирования D-сигналов является выходом данных коммуникационного интерфейса устройства, вход полного кода символа устройства соединен с входом битов символа первого блока DS-кодирования битов, вход числа битов которого соединен с входом длины символа устройства, вход записи которого является входом записи первого блока DS-кодирования битов, вход сброса которого является входом сброса устройства и соединен с входами сброса блоков формирования D- и S-сигналов, первые информационные входы которых соединены соответственно с выходом битов данных и выходом стробов первого блока DS-кодирования битов, который содержит первый сдвигающий регистр, первый счетчик, первый формирователь стробов, первый триггер бита и первый триггер строба, выход которого соединен с первым входом первого формирователя строба и является выходом стробов первого блока DS-кодирования битов, вход битов символа которого является информационным входом первого сдвигающего регистра, информационный выход которого соединен со вторым входом первого формирователя строба и информационным входом первого триггера бита, выход которого соединен с третьим входом первого формирователя строба и является выходом битов данных первого блока DS-кодирования битов, вход сброса которого соединен с входами сброса первого сдвигающего регистра, первого триггера бита, первого триггера строба и первого счетчика, информационный вход которого является входом числа битов первого блока DS-кодирования битов, вход записи которого является входом загрузки первого счетчика, выход которого соединен с входом разрешения первого сдвигающего регистра и является выходом готовности первого блока DS-кодирования битов, вход синхронизации которого соединен с входами синхронизации первого сдвигающего регистра, первого счетчика, первого триггера бита, первого триггера строба и первого формирователя строба, выход которого соединен с информационным входом первого триггера строба, причем блок формирования D-(S-)сигналов содержит первый триггер D-(S-)сигнала, вход синхронизации которого является первым входом синхронизации блока формирования D-(S-)сигналов, вход сброса которого является входом сброса первого триггера D-(S-)сигнала, информационный вход которого является первым информационным входом блока формирования D-(S-)сигналов, введены второй блок DS-кодирования битов, элемент НЕ, повторитель синхросигнала, элемент ИЛИ, причем выход элемента ИЛИ является выходом готовности устройства, вход полного кода символа которого соединен с входом битов символа второго блока DS-кодирования битов, вход числа битов которого соединен с входом длины символа устройства, вход записи которого является входом записи второго блока DS-кодирования битов, вход сброса которого соединен с входом сброса устройства, вход синхронизации которого соединен с входами повторителя синхросигнала и элемента НЕ, выход которого соединен с первыми входами синхронизации блоков формирования D- и S-сигналов и входом синхронизации первого блока DS-кодирования битов, выход готовности которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом готовности второго блока DS-кодирования битов, вход синхронизации которого соединен с выходом повторителя сигналов и со вторыми входами синхронизации блоков формирования D- и S-сигналов, второй информационный вход блока формирования S-сигналов соединен с выходом стробов второго блока DS-кодирования битов, выход битов данных которого соединен со вторым информационным входом блока формирования D-сигналов, причем второй блок DS-кодирования битов содержит второй сдвигающий регистр, второй счетчик, второй триггер бита, второй триггер строба и второй формирователь строба, выход которого соединен с первым входом второго формирователя строба и является выходом стробов второго блока DS-кодирования битов, вход битов символа которого является информационным входом второго сдвигающего регистра, информационный выход которого соединен со вторым входом второго формирователя стробов и с информационным входом второго триггера бита, выход которого соединен с третьим входом второго формирователя стробов и является выходом битов данных второго блока DS-кодирования битов, вход сброса которого соединен с входами сброса второго сдвигающего регистра, второго триггера бита, второго триггера строба и второго счетчика, информационный вход которого является входом числа битов второго блока DS-кодирования битов, вход записи которого является входом загрузки второго счетчика, выход которого соединен с входом разрешения второго сдвигающего регистра и является выходом готовности второго блока DS-кодирования битов, вход синхронизации которого соединен с входами синхронизации второго сдвигающего регистра, второго счетчика, второго триггера бита, второго триггера строба и второго формирователя строба, выход которого соединен с информационным входом второго триггера строба; блок формирования D-(S-)сигналов содержит второй триггер D-(S-)сигнала и мультиплексор сигналов, выход которого является выходом данных (стробирования) блока формирования D-(S-)сигналов, первый вход синхронизации которого соединен с управляющим входом мультиплексора сигналов, первый и второй входы которого соединены с выходами соответственно первого и второго триггеров D-(S-)сигнала, вход сброса второго триггера D-(S-)сигнала соединен с входом сброса блока формирования D-(S-)сигналов, второй вход синхронизации которого является входом синхронизации второго триггера D-(S-)сигнала, информационный вход которого является вторым информационным входом блока формирования D-(S-)сигналов.

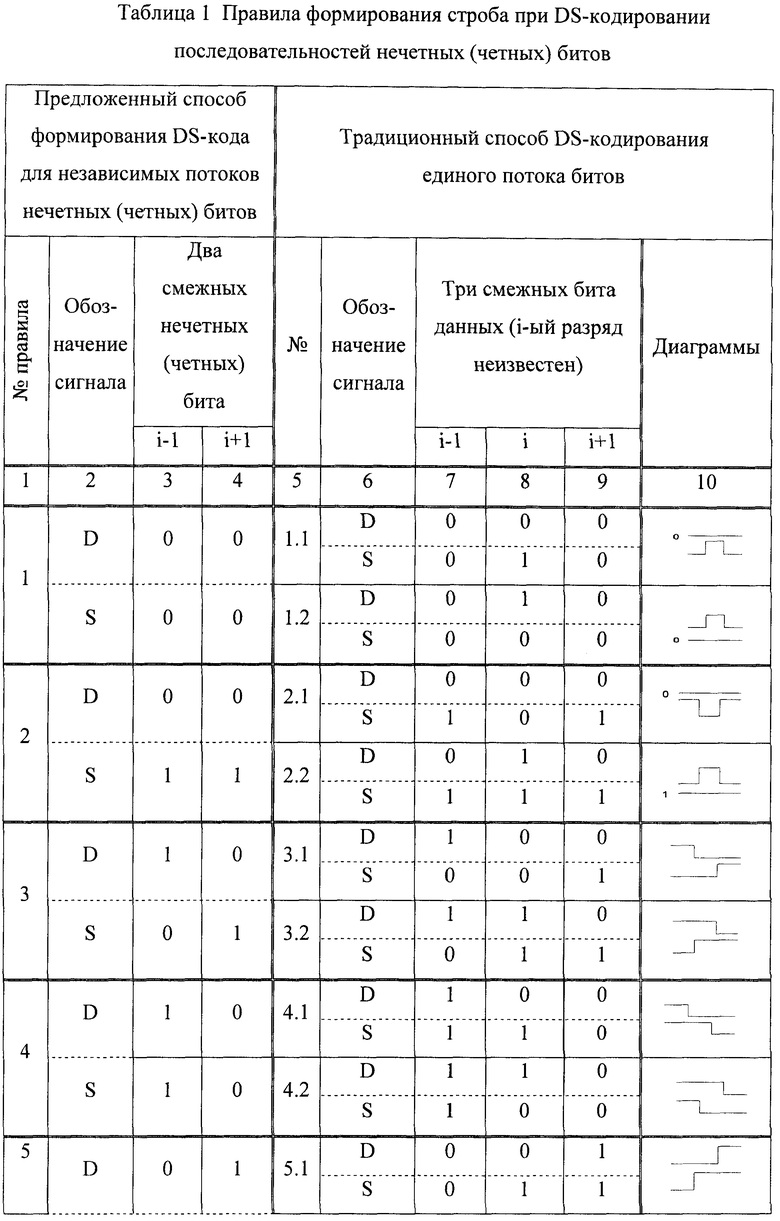

В предлагаемом техническом решении реализуется способ формирования DS-кода, включающий независимое формирование стробов для нечетной и четной последовательностей из общего потока битов данных, при котором сигнал стробирования для каждого нечетного (четного) бита данных формируется таким образом, чтобы общее число сигналов единичного значения в предыдущей и текущей парах битов данных и сигналов стробирования для последовательности нечетных (четных) битов было четным, причем последовательности нечетных и четных битов данных посредством мультиплексирования объединяются в единый поток сигналов данных (D-сигналов) и соответственно полученные последовательности нечетных и четных сигналов стробирования посредством мультиплексирования объединяются в единый поток сигналов стробирования (S-сигналов). При этом первый (второй) блок DS-кодирования битов символа реализует независимое DS-кодирование последовательности нечетных (четных) битов путем генерации сигнала стробирования согласно предложенному способу формирования DS-кода.

Благодаря этому в предлагаемом техническом решении обеспечивается возможность для повышения скорости передачи данных в коммуникационном интерфейсе при одновременном ограничении роста энергопотребления за счет разделения всех элементов устройства на два временных домена. Первый временной домен, включающий элементы устройства, непосредственно осуществляющие выдачу данных, работает на частоте передачи данных. Второй временной домен, в который включены все остальные элементы устройства, осуществляющие DS-кодирование выдаваемых данных, работает на частоте, меньшей в два раза по сравнению с частотой передачи данных. Поскольку в данном техническом решении имеется возможность минимизировать число триггеров, работающих на максимальной частоте передачи данных, то это способствует снижению потребляемой мощности по сравнению с прототипом при одинаковых значениях скорости передачи данных. Кроме того, реализация в устройстве при выдаче данных независимого и одновременного DS-кодирования символов данных, разделенных на два потока нечетных и четных битов, позволяет уменьшить временные задержки при формировании D- и S-сигналов и повысить скорость их передачи в коммуникационном интерфейсе. Отдельные элементы устройства могут быть реализованы стандартными средствами из данной области техники, при этом только системное решение, предложенное в рамках настоящего изобретения, позволяет достигнуть соответствующего технического результата.

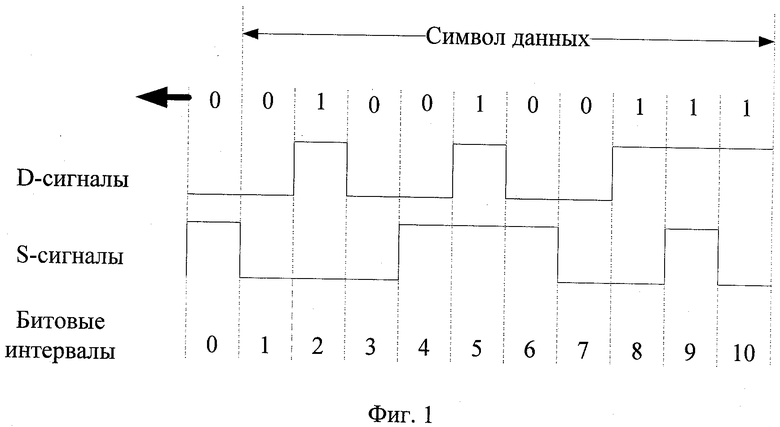

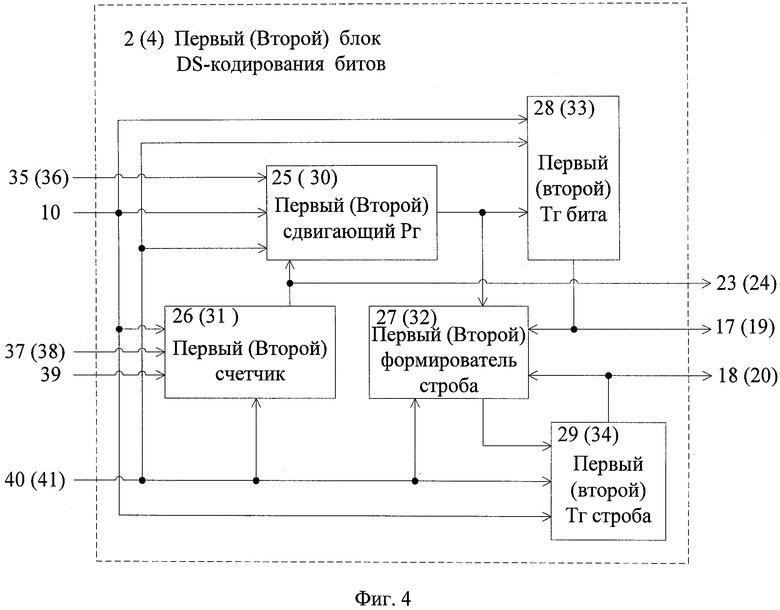

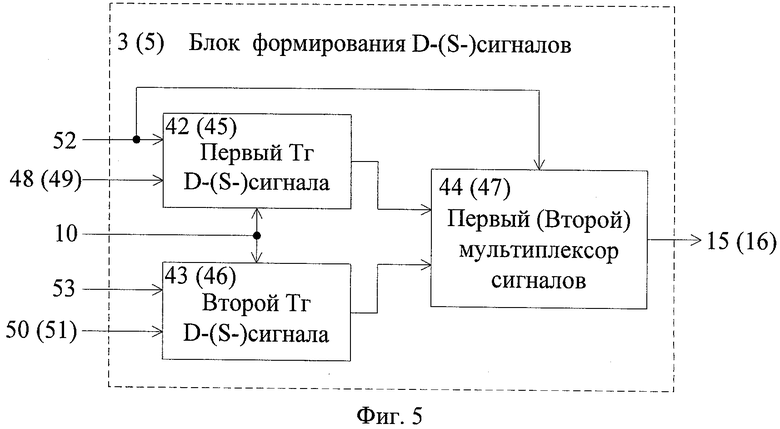

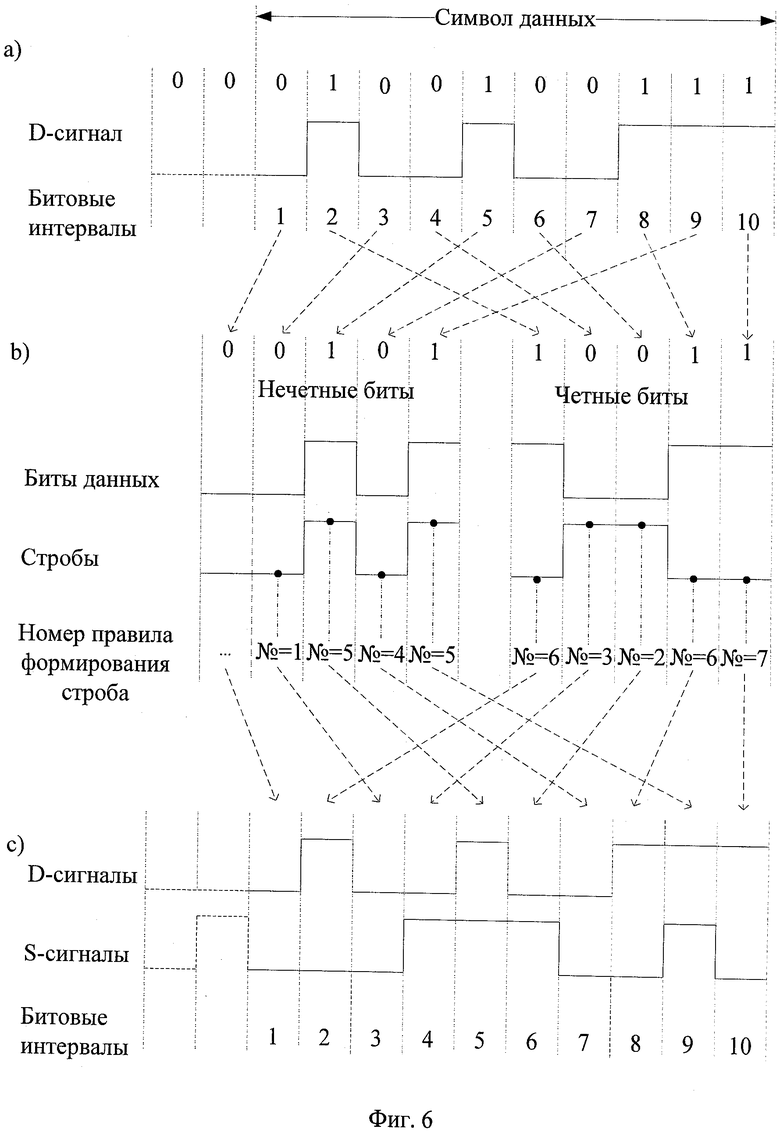

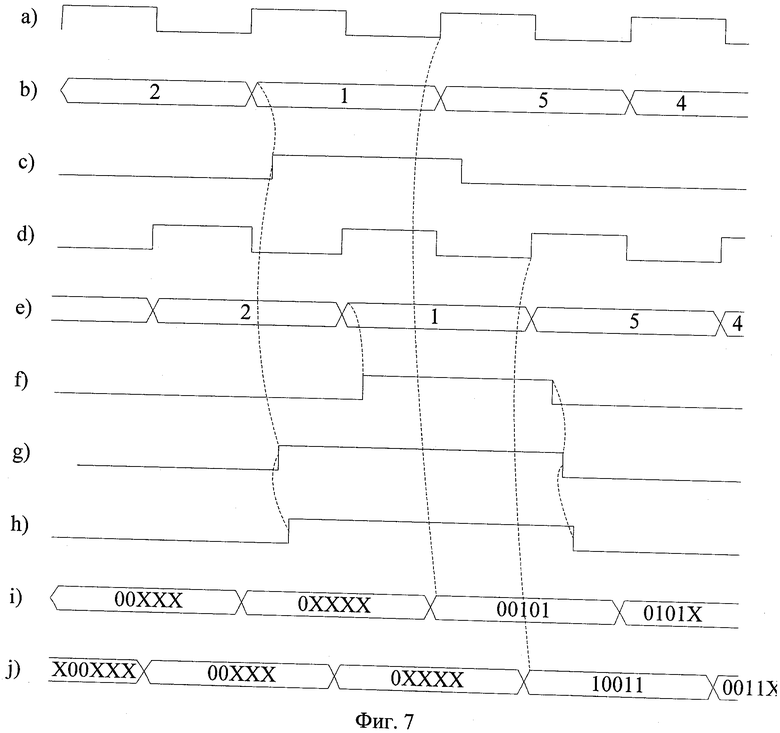

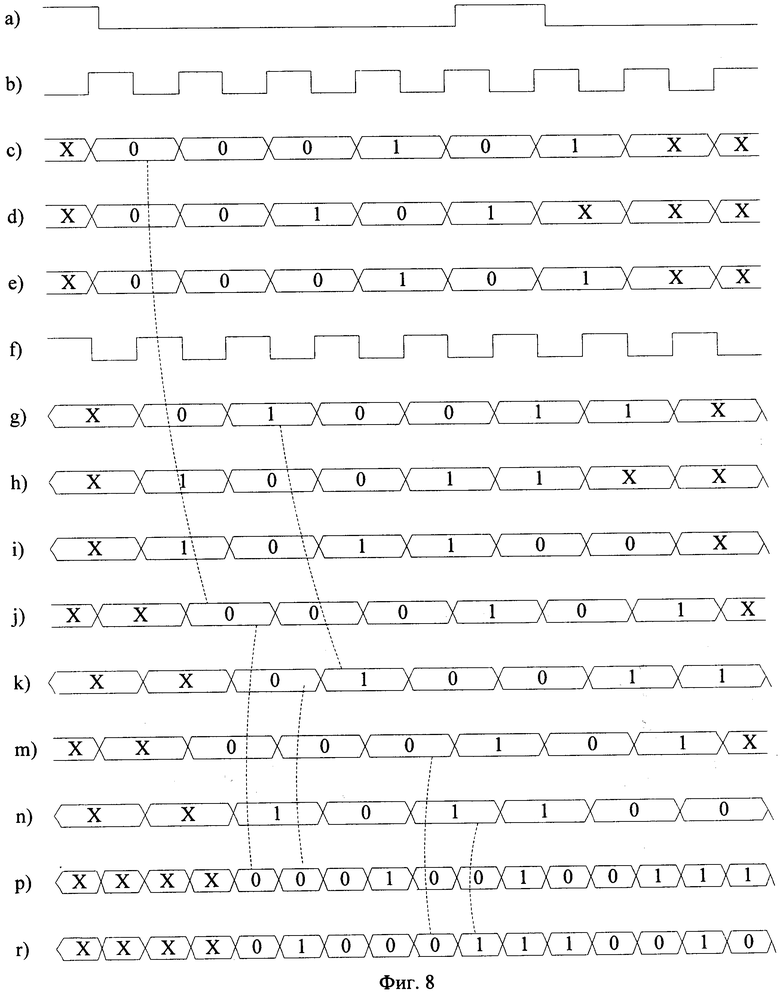

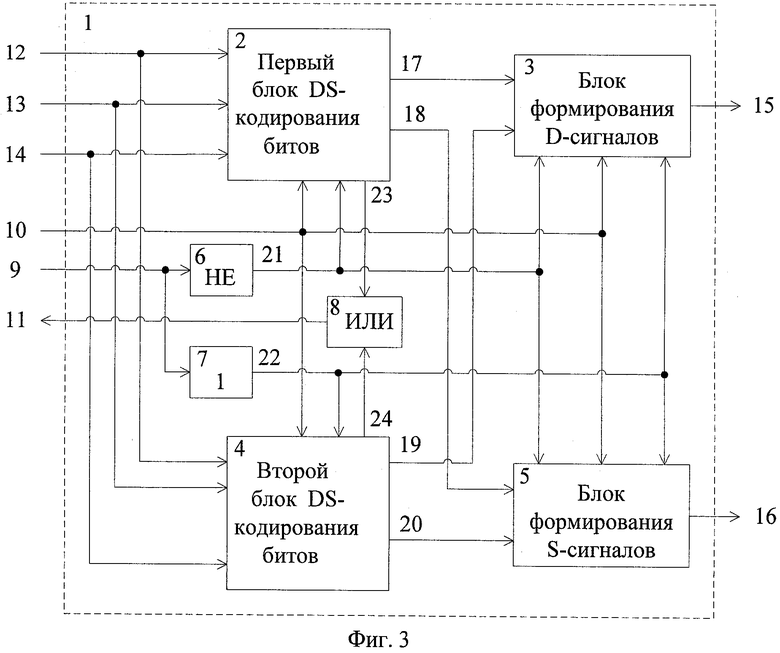

Детально сущность данного технического решения поясняется описанием со ссылками на фигуры чертежей, где на фиг.1 показаны временные диаграммы, поясняющие на примере DS-кодирование 10-битового символа данных и формирование D- и S-сигналов для его передачи в коммуникационном интерфейсе устройства. На фиг.2 показан известный вариант применения устройства 1 формирования DS-кода. На фиг.3 - представлена структурная схема устройства, на фиг.4 - структурная схема первого (второго) блока DS-кодирования битов, на фиг.5 - функциональная схема блока формирования D-(S-)сигналов. На фиг.6 представлены временные диаграммы, иллюстрирующие на конкретном примере применение правил формирования стробов в первом и втором блоках DS-кодирования битов для предложенного способа формирования DS-кода для разделенного на два потока - нечетных и четных битов - 10-битового символа данных. На фиг.7 показаны временные диаграммы при загрузке битов символа данных в устройство. На фиг.8 показаны временные диаграммы, поясняющие работу элементов устройства при формировании D-(S-)сигналов для 10-битового символа данных.

Устройство 1 формирования DS-кода содержит (см. фиг.3) первый блок 2 DS-кодирования битов, блок 3 формирования D-сигналов, второй блок 4 DS-кодирования битов, блок 5 формирования S-сигналов, элемент 6 НЕ, повторитель 7 синхросигнала, элемент 8 ИЛИ, вход 9 синхронизации устройства, вход 10 сброса устройства, выход 11 готовности устройства, вход 12 полного кода символа устройства, вход 13 длины символа устройства, вход 14 записи устройства, выход 15 данных коммуникационного интерфейса устройства, выход 16 стробирования коммуникационного интерфейса устройства, выход 17 битов данных первого блока 2 DS-кодирования битов, выход 18 стробов первого блока 2 DS-кодирования битов, выход 19 битов данных второго блока 4 DS-кодирования битов, выход 20 стробов второго блока 4 DS-кодирования битов, выход 21 элемента 6 НЕ, выход 22 повторителя 7 синхросигнала, выход 23 готовности первого блока 2 DS-кодирования битов, выход 24 готовности второго блока 2 DS-кодирования битов.

Первый (второй) блок 2 (4) DS-кодирования битов содержит (см. фиг.4) первый (второй) сдвигающий регистр 25 (30), первый (второй) счетчик 26 (31), первый (второй) формирователь 27 (32) строба, первый (второй) триггер 28 (33) бита, первый (второй) триггер 29 (34) строба, вход битов символа 35 (36), вход 37 (38) числа битов, вход 39 записи, вход 40 (41) синхронизации блока 2 (4), вход 10 сброса, выход 17 (19) битов данных блока 2 (4), выход 18 (20) стробов блока 2 (4), выход 23 (24) готовности.

Блок 3 (5) формирования D-(S-)сигналов содержит (см. фиг.5) первый триггер 42 (45) D-(S-)сигнала, второй триггер 43 (46) D-(S-)сигнала, первый (второй) мультиплексор 43 (47) сигналов, вход 10 сброса, первый информационный вход 48 (49) блока 3 (5), второй информационный вход 50 (51) блока 3 (5), первый вход 52 синхронизации, второй вход 53 синхронизации, выход 15 (16) данных (стробирования) блока 3 (5).

На временных диаграммах, иллюстрирующих предложенный способ формирования DS-кода (см. фиг.6), показано: а - разделение 10 битов символа данных на последовательности нечетных битов и четных битов и запись этих последовательностей соответственно в первый блок 2 и во второй блок 4 DS кодирования битов, b - формирование стробов для нечетной и четной последовательностей битов данных на выходах соответственно первого блока 2 и второго блока 4, с - формирование D- и S-сигналов на выходах 15 и 16 устройства 1 DS-кодирования символов данных.

На временных диаграммах, иллюстрирующих загрузку битов символа данных в устройство (см. фиг.7), показано: а - синхросигналы на входе 40 синхронизации первого блока 2 DS кодирования битов, b - изменение состояния первого счетчика 26, с - изменение сигнала готовности на выходе первого счетчика 26, d - синхросигналы на входе 41 синхронизации второго блока 4 DS кодирования битов, е - изменение состояния второго счетчика 31, f - изменение сигнала готовности на выходе второго счетчика 31, g - изменение сигнала готовности на выходе 11 готовности устройства, h - изменение сигнала на входе 14 записи устройства, i - изменение состояния первого сдвигающего регистра 25, j - изменение состояния второго сдвигающего регистра 30.

На временных диаграммах, поясняющих работу элементов устройства 1 при DS-кодировании 10-битового символа данных (см. фиг.8), показано: а - изменение сигнала на выходе счетчика 26 (31), b - изменение сигнала на входе 40 синхронизации первого блока 2 DS кодирования битов, с - изменение состояния выхода первого триггера 28 бита, d - изменение состояния выхода первого сдвигающего регистра 25, е - изменение состояния выхода первого триггера 29 строба, f - изменение сигнала на входе 41 синхронизации второго блока 4 DS кодирования битов, g - изменение состояния выхода второго триггера 33 бита, h - изменение состояния выхода второго сдвигающего регистра 30, i - изменение состояния выхода второго триггера 34 строба, j - состояния выхода первого триггера 42 D-сигнала, k - изменение состояния выхода второго триггера 43 D-сигнала, m - изменение состояния выхода первого триггера 45 S-сигнала, n - изменение состояния выхода второго триггера 46 S-сигнала, p - изменение состояния выхода 15 данных устройства, r - изменение состояния выхода 16 стробирования устройства.

Устройство 1 формирования DS-кода обеспечивает для последовательности символов данных, поочередно загружаемых из хост-системы (компьютера) или его контроллера выдачи информации, выработку DS-кода, представляющего собой последовательность сигналов данных (D-сигналов), совпадающих по уровню с соответствующими битами данных и выдаваемых через выход 15 данных коммуникационного интерфейса, и сопровождающих их сигналов стробирования (S-сигналов), изменяющих свое состояние всякий раз, когда очередной D-сигнал не изменяет свое состояние по сравнению с предыдущим, и выдаваемых через выход 16 стробирования коммуникационного интерфейса (см. фиг.3). Входящие в состав устройства 1 первый и второй блоки 2 и 4 DS-кодирования битов предназначены для раздельного и совмещенного во времени DS-кодирования соответственно последовательностей нечетных и четных битов одного и того же символа. Блок 3 формирования D-сигналов предназначен для формирования последовательности сигналов данных полного символа и обеспечивает удвоение скорости их выдачи с выхода, являющегося выходом 15 данных устройства 1. Блок 5 формирования S-сигналов предназначен для формирования последовательности сигналов стробирования битов данных полного символа и обеспечивает удвоение скорости их выдачи с выхода, являющегося выходом 16 стробирования устройства 1. Элемент 6 НЕ и повторитель 7 синхросигнала обеспечивают формирование двух синхросигналов для тактирования соответственно первого блока 2 DS-кодирования битов по падающему фронту входного синхросигнала, а второго блока 4 DS-кодирования битов - по возрастающему фронту входного синхросигнала. Элемент 8 ИЛИ, выход которого является выходом 11 готовности устройства 1, предназначен для выработки общего сигнала готовности устройства к получению от хост-системы следующего символа для его кодирования и выдачи в коммуникационный интерфейс. Вход 9 синхронизации устройства 1 соединен с входами элемента 6 НЕ и повторителя 7 синхросигнала. Выход элемента 6 НЕ соединен с входом синхронизации первого блока 2 DS-кодирования битов и со вторыми входами синхронизации блоков формирования 3 D- и 5 S-сигналов. Выход повторителя 7 синхросигнала соединен с входом синхронизации второго блока 4 DS-кодирования битов и с первыми входами синхронизации блоков формирования 3 D-сигналов и 5 S-сигналов. Вход 10 сброса предназначен для начальной установки блоков устройства и соединен с входами сброса первого блока 2 и второго блока 4 DS-кодирования битов и с входами сброса блоков формирования 3 D-сигналов и 5 S-сигналов. Вход 12 полного кода символа устройства 1 соединен как с входом 35 битов символа первого блока 2 DS-кодирования битов, на который обеспечивается поступление только нечетных битов полного кода символа, так и с входом 36 битов символа второго блока 4 DS-кодирования битов, на который обеспечивается поступление только четных битов полного кода символа. Вход 13 длины символа устройства 1 соединен с входами 37 и 38 числа битов первого блока 2 и второго блока 4 DS-кодирования битов, при этом обеспечивается поступление двоичного кода количества нечетных битов символа на вход 37 числа битов первого блока 2 DS-кодирования битов, а двоичного кода количества четных битов символа - на вход 38 числа битов второго блока 4 DS-кодирования битов. Вход 14 записи устройства 1 соединен с входами 39 записи первого блока 2 и второго блока 4 DS-кодирования битов и предназначен для фиксации числа нечетных битов и числа четных битов символа соответственно в первом блоке 2 и втором блоке 4 DS-кодирования битов. Выход готовности 23 первого блока 2 DS-кодирования битов соединен с первым входом элемента 8 ИЛИ, второй вход которого соединен с выходом готовности 24 второго блока 4 DS-кодирования битов. Выход 17 битов данных первого блока 4 DS-кодирования битов, который обеспечивает выдачу нечетных битов символа данных в последовательном виде, начиная с младших битов символа данных соединен с первым информационным входом блока 3 формирования D-сигналов. Выход 19 битов данных второго блока 4 DS-кодирования битов, обеспечивающий выдачу четных битов символа данных в последовательном виде, начиная с младших битов соединен со вторым информационным входом блока 3 формирования D-сигналов. Выход 18 стробов первого блока 2 DS-кодирования битов предназначен для выдачи стробов, сопровождающих в последовательном виде нечетные биты символа данных, и соединен с первым информационным входом блока 5 формирования S-сигналов. Выход 20 стробов второго блока 4 DS-кодирования битов предназначен для выдачи стробов, сопровождающих в последовательном виде четные биты символа данных, и соединен со вторым информационным входом блока 5 формирования S-сигналов.

В первом (втором) блоке 2 (4) DS-кодирования битов (см. фиг.4) первый (второй) сдвигающий регистр 25 (30) предназначен для преобразования параллельного кода в последовательный, который формируется на его информационном выходе, соединенном с информационным входом первого (второго) триггера 28 (33) бита и со вторым входом первого (второго) формирователя 27 (32) строба. Информационный вход первого сдвигающего регистра 25 (второго сдвигающего регистра 30) является входом 35 битов символа первого блока 2 (второго блока 4) DS-кодирования битов и предназначен для загрузки нечетных (четных) битов символа. Первый (второй) триггер 28 (33) бита предназначен для хранения очередного бита данных, выдвигаемого из первого (второго) сдвигающего регистра 25 (30). Выход первого (второго) триггера 28 (33) бита, являющийся выходом 17 (19) битов данных первого блока 2 (второго блока 4) DS-кодирования битов, соединен с третьим входом первого (второго) формирователя 27 (32) стробов. Первый (второй) счетчик 26 (31) предназначен для отслеживания длины последовательности нечетных (четных) битов одного символа, загруженной в первый (второй) сдвигающий регистр 25 (30) и выдаваемой из него в последовательном виде. Информационный вход первого (второго) счетчика 26 (31) соединен с входом 37 (38) числа битов первого (второго) блока 2 (4) DS-кодирования битов, с которого поступает двоичный код числа нечетных (четных) битов символа данных. Вход записи 39 первого (второго) блока 2 (4) DS-кодирования битов является входом загрузки первого (второго) счетчика 26 (31) и предназначен для записи него двоичного кода длины последовательности нечетных (четных) битов нового символа данных. Выход первого (второго) счетчика 26 (31) предназначен для формирования признака готовности, при наличии которого разрешается загрузка новой последовательности нечетных (четных) битов следующего символа в первый (второй) сдвигающий регистр 25 (30), а при отсутствии которого разрешается последовательный сдвиг загруженных битов данных. Выход первого (второго) счетчика 26 (31) соединен с входом разрешения первого (второго) сдвигающего регистра 25 (30) и является выходом 23 (24) готовности первого (второго) блока 2 (4) DS-кодирования битов. Первый (второй) формирователь 27 (32) строба предназначен для выработки последовательности сигналов стробирования, которые в соответствии с правилами формирования строба в предлагаемом способе DS-кодирования последовательностей нечетных (четных) битов сопровождают выдачу битов данных символа в коммуникационный интерфейс. Правила предложенного способа формирования DS-кода представлены в табл.1.

Выход первого (второго) формирователя 27 (32) строба соединен с информационным входом первого (второго) триггера 29 (34) строба. Первый (второй) триггер 29 (34) строба предназначен для запоминания в течение такта значения сформированного (i-1) строба в целях использования его для формирования значения следующего (i+1) строба (см. табл.1). Выход первого (второго) триггера 29 (34) строба соединен с первым входом первого (второго) формирователя 27 (32) строба и является выходом 18 (20) стробов первого (второго) блока 2 (4) DS-кодирования битов. Вход 40 (41) синхронизации первого (второго) блока 2 (4) DS-кодирования битов символа обеспечивает тактирование всех элементов блока 2 (4) и соединен с входами синхронизации первого (второго) сдвигающего регистра 25 (30), первого (второго) счетчика 26 (31), первого (второго) формирователя 27 (32) строба, первого (второго) триггера 28 (33) бита и первого (второго) триггера 29 (34) строба. Вход 10 сброса первого (второго) блока 2 (4) DS-кодирования битов символа обеспечивает установку начального состояния всех элементов памяти блока 2 (4) и соединен с входами сброса первого (второго) сдвигающего регистра 25 (30), первого (второго) счетчика 26 (31), первого (второго) триггера 28 (33) бита и первого (второго) триггера 29 (34) строба.

В блоке 3 (5) формирования D-(S-)сигналов (см. фиг.4) первый триггер 42 (45) D-(S-)сигнала предназначен для фиксации каждого нечетного D-(S-)сигнала на один такт синхронизации. Второй триггер 43 (46) D-(S-)сигнала предназначен для фиксации каждого четного D-(S-)сигнала на один такт синхронизации. Информационный вход первого триггера 42 (43) D-(S-)сигнала является первым информационным входом 46 (49) блока 3 (5) формирования D-(S-)сигналов, который предназначен для подачи нечетных D-(S-)сигналов. Информационный вход второго триггера 43 (46) D-(S-)сигнала является вторым информационным входом 50 (51) блока 3 (5) формирования D-(S-)сигналов, который предназначен для подачи четных D-(S-)сигналов. Вход синхронизации 52 блока 3 (5) формирования D-(S-)сигналов соединен с первым входом синхронизации первого триггера 42 (45) D-(S-)сигнала, обеспечивая запись значения очередного нечетного D-(S-)сигнала по возрастающему фронту в первый триггер 42 (45), и с управляющим входом первого (второго) мультиплексора 44 (46) сигналов. Вход синхронизации второго триггера 43 (46) D-(S-)сигнала является вторым входом синхронизации 53 блока 3 (5) формирования D-(S-)сигналов, который обеспечивает запись значения очередного четного D-(S-)сигнала по возрастающему фронту во второй триггер 43 (46). Вход 10 сброса блока 3 (5) формирования D-(S-)сигналов соединен с входами сброса первого триггера 42 (45) и второго триггера 43 (46) D-(S-)сигнала и обеспечивает их сброс в исходное нулевое состояние. Первый (второй) мультиплексор 44 (47) сигналов предназначен для поочередной передачи нечетных и четных D-(S-)сигналов на свой выход, который является выходом 15 (16) данных (стробирования) блока 3 (5) формирования D-(S-)сигналов. Первый и второй информационные входы первого (второго) мультиплексора 44 (47) сигналов соединены соответственно с выходами первого триггера 42 (45) D-(S-)сигнала и второго триггера 43 (46) D-(S-)сигнала. Наличие высокого уровня синхросигнала на управляющем входе первого (второго) мультиплексора 44 (47) сигналов обеспечивает подключение к его выходу первого информационного входа, при низком уровне синхросигнала - второго информационного входа мультиплексора.

Устройство 1 формирования DS-кода для символов данных работает следующим образом. В соответствии с известным вариантом применения основной задачей устройства 1 является обеспечение DS-кодирования битов символов данных при их передаче из локальной хост-системы (компьютера, процессорного узла или его контроллера ввода-вывода) в удаленную хост-систему через коммуникационный интерфейс. Локальное устройство 1 и его локальная хост-система в дальнейшем именуются как «Сторона А», удаленная хост-система - как «Сторона Б». Для обеспечения дуплексного режима взаимодействия Сторона Б также может содержать устройство 1 для DS-кодирования битов данных, передаваемых на сторону А через свой коммуникационный интерфейс. Поэтому для реализации дуплексного режима в коммуникационном канале, связывающем Стороны А и Б, должны иметься два симплексных коммуникационных канала: первый - для передачи из Стороны А в Сторону Б и второй - в обратном направлении. В каждом симплексном канале данных присутствуют две симплексные линии - для передачи D-сигналов и S-сигналов. На фиг.2 показан только один симплексный коммуникационный канал из А в Б, что достаточно для понимания сути изобретения. Линия данных (выход 15 данных коммуникационного интерфейса устройства 1) используется для передачи D-сигналов, значение которых тождественно битам передаваемого символа данных. Линия стробирования (выход 16 стробирования коммуникационного интерфейса устройства 1) используется для передачи S-сигналов, которые вырабатываются устройством 1 формирования DS-кода для сопровождения передаваемых битов символа данных.

После окончания выдачи последовательности битов очередного символа данных устройство 1 формирует сигнал готовности на своем выходе 11 (см. фиг.3), при получении которого хост-система должна обеспечить загрузку битов нового символа данных. Хост-система выставляет полный код нового символа данных в параллельном виде на входе 12 устройства, а на входе 13 - двоичный код длины символа. Нечетные биты символа данных, поступающие на вход 35 битов символа первого блока 2 DS-кодирования битов, должны быть загружены в первый сдвигающий регистр 25 (см. фиг 4). Четные биты символа данных, поступающие на вход 36 битов символа второго блока 4 DS-кодирования битов, должны быть загружены во второй сдвигающий регистр 30. Синхронная работа всех блоков устройства обеспечивается подачей синхроимпульсов на вход 9 синхронизации устройства. При этом первый блок 2 DS-кодирования битов синхронизируется с помощью синхропоследовательности, сформированной на выходе 21 элемента 6 НЕ в инверсном виде по отношению к исходной последовательности синхроимпульсов, в то время как второй блок 4 - с помощью синхропоследовательности, сформированной на выходе повторителя 7 и совпадающей с исходной последовательностью синхроимпульсов. Разнесение на половину такта синхронизации двух блоков 2 и 4 обеспечивает снижение динамического электропотребления в блоках устройства. Загрузка нечетных битов в первый сдвигающий регистр 25 осуществляется по возрастающему фронту синхросигнала на входе 40 и при наличии единичного состояния сигнала готовности на выходе первого счетчика 26 (см. фиг.7, диаграммы а, с, i). Загрузка четных битов во второй сдвигающий регистр 30 осуществляется по возрастающему фронту синхросигнала на входе 41 и при наличии единичного уровня сигнала готовности на выходе второго счетчика 26 (см. фиг.7, диаграммы d, f, j). Сигнал записи, поступающий на вход 14 устройства, разрешает запись как числа нечетных битов символа с входа 37 в первый счетчик 26, которая осуществляется по возрастающему фронту синхросигнала на входе 40 (см. фиг.7, диаграммы a, b, h), так и числа четных битов символа с входа 38 во второй счетчик 31 - по возрастающему фронту синхросигнала на входе 41 (см. фиг.7, диаграммы d, е, h). После записи нового содержимого в счетчики 26 и 31 сигналы готовности на их выходах переходят в нулевое состояние (см. фиг.7, диаграммы с, f), запрещая загрузку новых последовательностей битов в сдвиговые регистры 25 и 30 и разрешая последовательный сдвиг загруженных битов.

Как показано на диаграмме (см. фиг.6,а), биты данных подготовленного хост-системой к передаче, например, 10-битового символа в устройстве 1 DS-кодирования символов данных разделяются на две последовательности, состоящие в данном примере из пяти нечетных и пяти четных битов. Для каждой из этих последовательностей битов данных в первом блоке 2 и втором блоке 4 DS-кодирования битов одновременно и независимо формируются соответствующие последовательности из пяти стробов. Каждый из двух блоков 2 и 4 осуществляет DS-кодирование своей последовательности битов (см. фиг.6,b) в соответствии с правилами формирования строба для предложенного способа, изложенными в табл.1. Две последовательности обработанных в блоках 2 и 4 нечетных и четных битов символа данных в блоке 3 формирования D-сигналов объединяются в единую 10-битовую последовательность D-сигналов, которая поступает на выходы 16 данных коммуникационного интерфейса устройства. Сформированные в блоках 2 и 4 последовательности из пяти стробов, сопровождающие нечетные и четные биты символа данных, объединяются в единую 10-битовую последовательность S-сигналов, которая поступает (см. фиг.6,с) на выходы 17 стробирования коммуникационного интерфейса устройства.

Работа элементов блоков 2 и 4 DS-кодирования битов и блоков 3 5 формирования D-(S-)сигналов описана на примере обработки 10-битового символа данных, формат которого показан на фиг.1. Как следует из диаграмм на фиг.1 и 6, предполагается, что два последние бита предыдущего символа данных имеют нулевое значение. Запись нечетных и четных битов символа в сдвигающие регистры 25 и 30 осуществляется при единичном значении сигналов загрузки на выходах счетчиков 26 и 31 (см. диаграмму на фиг.8,а). При загрузке нечетных битов нового символа данных в первый сдвигающий регистр 25 в первом триггере 28 бита еще сохраняется нулевое значение последнего нечетного бита предыдущего символа (см. фиг.8,с), а в первом триггере 29 строба - нулевое значение сформированного строба, сопровождающего последний нечетный бит предыдущего символа (см. фиг.8,е). При нулевом значении сигнала на выходе первого счетчика 26 разрешается сдвиг данных в первом сдвигающем регистре 25 и на его выходе (см. фиг.8,d) появляется нулевое значение первого нечетного бита. Первый формирователь 27 строба в соответствии с правилом №1 (см. табл.1, столбцы 3, 4) формирует на своем выходе нулевое значение строба, который должен сопровождать первый нечетный бит нового символа. В следующем битовом интервале эти значения бита и строба записываются соответственно в триггеры 28 и 29 и появляются на их выходах (см. фиг.8,с,е). Аналогичным образом в блоке 4 DS-кодирования битов второй формирователь 32 строба в соответствии с правилом №6 при наличии на своих входах нулевого значения последнего четного бита с выхода второго триггера 33 бита (см. фиг.8,g), единичного значения сопровождающего его строба из второго триггера 34 строба (см. фиг.8,i) и единичного значения первого четного бита нового символа с выхода второго сдвигающего регистра 30 (см. фиг.8,h) вырабатывает на своем выходе нулевое значение следующего строба, который записывается во второй триггер 34 строба (см. фиг.8,i).

Таким образом, четные биты и сформированные для них стробы последовательно появляются соответственно на выходах 19 и 20 блока 4 (см. фиг.8,g, i) со сдвигом на полпериода входного синхросигнала (см. фиг.8,b или 8,f) по отношению к нечетным битам данных и стробам, появляющимся на выходах 17 и 18 блока 2 (см. фиг.8,с, е) соответственно. Нечетные биты данных поступают в блок 3 формирования D-сигналов на первый информационный вход 48 (см. фиг.4) и поочередно перезаписываются в первый триггер 42 D-сигнала (см. фиг.8,j) по возрастающему фронту синхросигнала на первом входе 52 синхронизации блока 3 (см. фиг.8,b). Четные биты данных поступают в блок 3 формирования D-сигналов на второй информационный вход 50 и поочередно перезаписываются во второй триггер 43 D-сигнала (см. фиг.8,k) по возрастающему фронту синхросигнала на втором входе 53 синхронизации блока 3 (см. фиг.8,f). Нечетные стробы поступают в блок 5 формирования S-сигналов на первый информационный вход 49 и поочередно перезаписываются в первый триггер 45 S-сигнала (см. фиг.8,m) по возрастающему фронту синхросигнала на первом входе 52 синхронизации блока 5 (см. фиг.8,b). Четные стробы поступают в блок 5 формирования S-сигналов на второй информационный вход 51 и поочередно перезаписываются во второй триггер 46 S-сигнала (см. фиг.8,n) по возрастающему фронту синхросигнала на втором входе 53 синхронизации блока 5 (см. фиг.8,f). Первый мультиплексор 44 сигналов во время действия нулевого полупериода синхросигнала на своем управляющем входе (см. фиг.8,b) передает на выход 15 блока 3 состояние нечетного D-сигнала с выхода первого триггера 42 D-сигнала. В течение единичного полупериода синхросигнала на выход первого мультиплексора 44 сигналов передается состояние четного D-сигнала с выхода второго триггера 43 D-сигнала. Объединенная последовательность нечетных и четных D-сигналов, соответствующая битам полного символа, с выхода 15 данных поступает в коммуникационный интерфейс с частотой, в два раза превышающей частоту, на которой работают первый блок 2 и второй блок 4 DS-кодирования (см. фиг.8,p). Аналогичным образом второй мультиплексор 47 сигналов формирует из нечетных и четных S-сигналов объединенную последовательность S-сигналов, сопровождающих D-сигналы обработанного символа. Единая последовательность S-сигналов с выхода 16 стробирования поступает в коммуникационный интерфейс с частотой, также в два раза превышающей частоту, на которой работают первый блок 2 и второй блок 4 DS-кодирования (см. фиг.8,r).

Таким образом, выдача битов данных из устройства 1 формирования DS-кода в коммуникационный интерфейс осуществляется со скоростью, в два раза превышающей частоту синхросигнала, поступающего из локальной хост-системы и определяющего скорость формирования D- и S-сигналов при DS-кодировании. В рассматриваемом варианте реализации устройства 1 выдача D- и S-сигналов осуществляется на частоте 400 МГц, при этом частота синхронизации устройства, определяемая локальной хост-системой, равна 200 МГц. На частоте локальной синхронизации работает абсолютное большинство элементов устройства, и только функционирование выходных элементов - первого и второго мультиплексоров 44 и 47 сигналов соответственно в блоках 3 и 5 формирования D- и S-сигналов осуществляется на удвоенной частоте. Поскольку частота локальной синхронизации в два раза меньше скорости передачи выходных сигналов, полученных при DS-кодировании, то предлагаемое техническое решение способствует значительному снижению энергопотребления на одинаковых скоростях передачи по сравнению с прототипом, реализующим известный способ формирования DS-кода, что является важным фактором при использовании данного устройства в бортовых и встраиваемых применениях. Поэтому предложенное устройство имеет значительные функциональные преимущества перед известными аналогами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА | 2010 |

|

RU2460124C2 |

| КОММУНИКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ГАЛЬВАНИЧЕСКОЙ РАЗВЯЗКИ DS-ЛИНКА | 2012 |

|

RU2485580C1 |

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА ДЛЯ СЕТИ SpaceWire | 2012 |

|

RU2483351C1 |

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА GIGASPACEWIRE | 2018 |

|

RU2700560C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к области передачи данных в высокоскоростных последовательных коммуникационных интерфейсах и может найти применение при построении распределенных вычислительных систем, используемых, в том числе, в бортовых вычислительных комплексах. Техническим результатом является снижение энергопотребления и повышение быстродействия. Формирование стробов осуществляется одновременно и независимо для нечетной и четной последовательностей передаваемых битов данных в двух блоках DS-кодирования битов, работающих параллельно. 2 н.п. ф-лы, 8 ил., 1 табл.

1. Способ формирования DS-кода, включающий этапы независимого формирования стробов для нечетной и четной последовательностей из общего потока битов данных, при котором сигнал стробирования для каждого нечетного бита данных формируется таким образом, чтобы общее число сигналов единичного значения в предыдущей и текущей парах битов данных и сигналов стробирования для последовательности нечетных битов данных было четным, и сигнал стробирования для каждого четного бита данных формируется так, чтобы общее число сигналов единичного значения в предыдущей и текущей парах битов данных и сигналов стробирования для последовательности четных битов было четным; мультиплексирования битов данных нечетной и четной последовательностей в единый поток сигналов данных и соответственно мультиплексирования сигналов стробирования нечетной и четной последовательностей в единый поток сигналов стробирования.

2. Устройство формирования DS-кода символов данных, содержащее первый блок DS-кодирования битов, блок формирования D-сигналов и блок формирования S-сигналов, выход стробирования которого является выходом стробирования коммуникационного интерфейса устройства, выход данных блока формирования D-сигналов является выходом данных коммуникационного интерфейса устройства, вход полного кода символа устройства соединен с входом битов символа первого блока DS-кодирования битов, вход числа битов которого соединен с входом длины символа устройства, вход записи которого является входом записи первого блока DS-кодирования битов, вход сброса которого является входом сброса устройства и соединен с входами сброса блоков формирования D- и S-сигналов, первые информационные входы которых соединены соответственно с выходом битов данных и выходом стробов первого блока DS-кодирования битов, который содержит первый сдвигающий регистр, первый счетчик, первый формирователь стробов, первый триггер бита и первый триггер строба, выход которого соединен с первым входом первого формирователя строба и является выходом стробов первого блока DS-кодирования битов, вход битов символа которого является информационным входом первого сдвигающего регистра, информационный выход которого соединен со вторым входом первого формирователя строба и информационным входом первого триггера бита, выход которого соединен с третьим входом первого формирователя строба и является выходом битов данных первого блока DS-кодирования битов, вход сброса которого соединен с входами сброса первого сдвигающего регистра, первого триггера бита, первого триггера строба и первого счетчика, информационный вход которого является входом числа битов первого блока DS-кодирования битов, вход записи которого является входом загрузки первого счетчика, выход которого соединен с входом разрешения первого сдвигающего регистра и является выходом готовности первого блока DS-кодирования битов, вход синхронизации которого соединен с входами синхронизации первого сдвигающего регистра, первого счетчика, первого триггера бита, первого триггера строба и первого формирователя строба, выход которого соединен с информационным входом первого триггера строба, причем блок формирования D-(S-)сигналов содержит первый триггер D-(S-)сигнала, вход синхронизации которого является первым входом синхронизации блока формирования D-(S-)сигналов, вход сброса которого является входом сброса первого триггера D-(S-)сигнала, информационный вход которого является первым информационным входом блока формирования D-(S-)сигналов, отличающееся тем, что в него введены второй блок DS-кодирования битов, элемент НЕ, повторитель синхросигнала, элемент ИЛИ, причем выход элемента ИЛИ является выходом готовности устройства, вход полного кода символа которого соединен с входом битов символа второго блока DS-кодирования битов, вход числа битов которого соединен с входом длины символа устройства, вход записи которого является входом записи второго блока DS-кодирования битов, вход сброса которого соединен с входом сброса устройства, вход синхронизации которого соединен с входами повторителя синхросигнала и элемента НЕ, выход которого соединен с первыми входами синхронизации блоков формирования D- и S-сигналов и входом синхронизации первого блока DS-кодирования битов, выход готовности которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом готовности второго блока DS-кодирования битов, вход синхронизации которого соединен с выходом повторителя сигналов и со вторыми входами синхронизации блоков формирования D- и S-сигналов, второй информационный вход блока формирования S-сигналов соединен с выходом стробов второго блока DS-кодирования битов, выход битов данных которого соединен со вторым информационным входом блока формирования D-сигналов, причем второй блок DS-кодирования битов содержит второй сдвигающий регистр, второй счетчик, второй триггер бита, второй триггер строба и второй формирователь строба, выход которого соединен с первым входом второго формирователя строба и является выходом стробов второго блока DS-кодирования битов, вход битов символа которого является информационным входом второго сдвигающего регистра, информационный выход которого соединен со вторым входом второго формирователя стробов и с информационным входом второго триггера бита, выход которого соединен с третьим входом второго формирователя стробов и является выходом битов данных второго блока DS-кодирования битов, вход сброса которого соединен с входами сброса второго сдвигающего регистра, второго триггера бита, второго триггера строба и второго счетчика, информационный вход которого является входом числа битов второго блока DS-кодирования битов, вход записи которого является входом загрузки второго счетчика, выход которого соединен с входом разрешения второго сдвигающего регистра и является выходом готовности второго блока DS-кодирования битов, вход синхронизации которого соединен с входами синхронизации второго сдвигающего регистра, второго счетчика, второго триггера бита, второго триггера строба и второго формирователя строба, выход которого соединен с информационным входом второго триггера строба; блок формирования D-(S-)сигналов содержит второй триггер D-(S-)сигнала и мультиплексор сигналов, выход которого является выходом данных (стробирования) блока формирования D-(S-)сигналов, первый вход синхронизации которого соединен с управляющим входом мультиплексора сигналов, первый и второй входы которого соединены с выходами соответственно первого и второго триггеров D-(S-)сигнала, вход сброса второго триггера D-(S-)сигнала соединен с входом сброса блока формирования D-(S-)сигналов, второй вход синхронизации которого является входом синхронизации второго триггера D-(S-)сигнала, информационный вход которого является вторым информационным входом блока формирования D-(S-)сигналов.

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ С ИСПОЛЬЗОВАНИЕМ СИГНАЛОВ С ПРЯМЫМ РАСШИРЕНИЕМ И АВТОКОРРЕЛЯЦИОННЫМ СЖАТИЕМ СПЕКТРА | 2008 |

|

RU2358401C1 |

| ПРОЦЕССОР ПОИСКА ДЛЯ МНОГОСТАНЦИОННОЙ СИСТЕМЫ СВЯЗИ С РАСШИРЕННЫМ СПЕКТРОМ | 1995 |

|

RU2149509C1 |

| US 6295010 B1, 25.09.2001 | |||

| СВЕТОЧУВСТВИТЕЛЬНЫЕ СОЕДИНЕНИЯ В ВАКУУМНЫХ ФОТОЛИТОГРАФИЧЕСКИХ ПРОЦЕССАХ | 1985 |

|

SU1351426A1 |

Авторы

Даты

2013-06-20—Публикация

2011-04-15—Подача