Изобретение представляет собой устройство (систему) коммуникационного интерфейса и относится к цифровой вычислительной технике, а именно к высокоскоростным коммуникационным системам для высокопроизводительных многопроцессорных вычислительных систем с распределенной обработкой информации, и локальным вычислительным сетям, создаваемых на базе технологии SpaceWire [ECSS Standard ECSS-E-50-12A, "SpaceWire, Links, Nodes, Routers and Networks", Issue 1, European Cooperation for Space Data Standardization, February 2003]. Данное устройство предназначено, в частности, для использования при построении многопроцессорных вычислительных систем с распределенной архитектурой, используемых во встраиваемых применения, в том числе в бортовых вычислительных комплексах, а также бортовых локальных сетей.

В качестве аналога из уровня техники известен коммуникационный интерфейс, описанный в стандарте FibreChannel [Fibre Channel - Physical Interfaces - 2 (FC-PI-2), ISO 1.25.13], в котором при передаче данных по последовательному коммуникационному каналу используется преобразование 8b/10b для представления восьмибитовых символов в виде 10-битовых кодов. В устройствах, взаимодействующих через данный коммуникационный интерфейс, каждые восемь битов исходной последовательности заменяются 10 битами в соответствии с определенными правилами. В результате для 256 возможных комбинаций из восьми входных битов получается 1024 возможные комбинации для 10 выходных битов. Но разрешенными из этих 1024 комбинаций являются только 256, а остальные - запрещенными. Как правило, такая избыточность используется для того, чтобы повысить помехоустойчивость кодирования (если при приеме обнаруживается запрещенная последовательность, то распознается ошибка передачи). Кроме того, такая избыточность улучшает самосинхронизирующие свойства кода, поскольку исключает возможность появления в цепочке передаваемых битов длинных последовательностей нулей и единиц, что способствует, в конечном счете, повышению надежности работы устройства. При приеме данных осуществляется декодирование 8b/10b, то есть каждой группе из 10 битов сопоставляется восемь битов.

Недостаток этого подхода состоит в отсутствии возможности передачи специальных управляющих кодов наряду с символами данных. Специальные управляющие коды необходимы для поддержки системных функций и управления в реальном масштабе времени, что существенно ограничивает область применения.

Известно устройство преобразования 8b/10b [US Patent 06977599B2. 8B/10B encoding and decoding for high speed applications, Apr 30, 2002], используемое в стандарте FibreChannel. Устройство содержит блок кодирования 8b/10b, выходной 10-разрядный сдвиговый регистр, обеспечивающий преобразование параллельных 10-битовых кодов в последовательный поток битов, выдаваемых в коммуникационный интерфейс, входной 10-разрядный сдвиговый регистр, обеспечивающий обратное преобразование последовательного потока битов в параллельные 10-битовые коды, и блок декодирования 8b/10b. Устройство работает на локальной частоте в 10 раз меньшей частоты передачи битов в коммуникационном интерфейсе. Применение кода 8b/10b позволяет использовать в коммуникационном канале одну передающую линию данных, так как при кодировании 8b/10b имеется возможность передачи наряду с символами данных специального встроенного символа тактирования, предназначенного для синхронизации взаимодействующих устройств.

В качестве недостатка необходимо отметить, что устройство не обеспечивает передачу в реальном масштабе времени различных специальных управляющих кодов (системных прерываний, маркеров системного времени и других управляющих сигналов, необходимых для управления на системном уровне), поскольку отсутствует возможность вставить управляющий код внутрь последовательности передаваемых восьмибитовых символов данных одного кадра. Необходимость ожидания окончания передачи очередного кадра данных проводит к существенным временным задержкам при выполнении системных функций. Кроме того, невозможность реализации системных механизмов в реальном масштабе времени значительно сужает область применения.

Известен последовательный коммуникационный интерфейс, реализующий способ DS-кодирования (Data-Strobe coding) в соответствии со стандартом SpaceWire [ECSS Standard ECSS-E-50-12A, "SpaceWire, Links, Nodes, Routers and Networks", Issue 1, European Cooperation for Space Data Standardization, February 2003] и широко применяемый для передачи потоков битов между обрабатывающими узлами в бортовых распределенных вычислительных комплексах. Использование в коммуникационном интерфейсе линий данных и строба (D- и S-сигналов) в каждом направлении позволяет обеспечить высокоскоростную передачу битов данных в широком диапазоне скоростей от 2 Мбит/с до 400 Мбит/с. Простая реализация процедуры формирования пакетов данных, основанная на применении служебных (управляющих) символов конца пакета ЕОР (End Of Packet), позволяет передавать информационные символы в виде пакетов произвольной длины. Такая возможность упрощает структуру коммутационных узлов (коммутаторов и концентраторов), применяемых для передачи и коммутации битовых потоков от бортовых датчиков к обрабатывающим узлам в распределенных вычислительных комплексах.

Недостатком интерфейса SpaceWire является наличие джиттера (вариации времени задержки) между параллельно передаваемыми D- и S-сигналами в физическом канале. DS-кодирование из-за необходимости использования двух линий для передачи битов данных и сигналов стробирования предъявляет достаточно жесткие требования к скосу (фазовому сдвигу) и джиттеру D- и S-сигналов, что затрудняет его использование на расстояниях более 10 метров. Так же наличие двух линий для каждого направления передачи затрудняет использование гальванической развязки из-за возникающих разных задержек на самой развязке, что существенно ограничивает область применения устройств SpaceWire в бортовых распределенных вычислительных комплексах.

Известно устройство коммуникационного интерфейса [Patent GB №91304711.4. Communication interface for serial transmission of variable length data tokens / Priority 25.05.90, №9011700. Data of filing 24.05.91. Data of publication 27.11.91. Bulletin 91/48 of European Patent Office. Publication number 0458648A2] для использования в коммуникационной системе, соединяющей как минимум два компьютера, причем устройство коммуникационного интерфейса, содержащее блок управления, блок управления потоком данных, блок выдачи данных и блок приема данных, входы данных и стробирования которого являются соответственно входами данных и стробирования интерфейса устройства с каналом приема информации, выходы данных и стробирования интерфейса устройства с каналом выдачи информации являются соответственно выходами данных и стробирования блока выдачи данных. Блок управления потоком устройства с помощью специальных управляющих символов управления потоком FCT (Flow Control Token) реализует механизм кредитования, позволяющий использовать буферы ограниченного размера для приема и передачи пакетов неограниченной длины.

Недостатком данного устройства коммуникационного интерфейса является ограничение расстояния между взаимодействующими сторонами и отсутствие гальванической развязки, что может вызывать отказы и неисправности из-за коротких замыканий.

Ближайшим аналогом к заявляемому является устройство коммуникационного интерфейса [Решение о выдаче Патента РФ на изобретение от 30.03.2012 по заявке №2010121016/08(029872). Устройство коммуникационного интерфейса. Заявл. 26.05.2010, H04L 1/00 (2006.01)], обеспечивающее передачу данных из хост-системы в последовательный канал в соответствии со стандартом SpaceWire и содержащее блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными выходами блока приема данных и одноименными входами блока управления, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства, вход сброса системного интерфейса устройства является входом сброса блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, выход «получен NULL» которого соединен с одноименным входом блока управления, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком блока выдачи данных являются соответственно одноименными выходами блока арбитража выдачи символов, вход запроса на выдачу символа управления потоком которого является одноименным входом блока выдачи данных, вход сброса которого является входом сброса блока арбитража выдачи символов и соединен с входом сброса буфера выдачи данных, выход готовности данных которого соединен с одноименным входом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом синхронизации блока выдачи данных, входы разрешения выдачи и разрешения передачи символа управления потоком которого является одноименными входами блока арбитража выдачи символов, выход чтения данных которого соединен с одноименным входом буфера выдачи данных, выход признака конца пакета которого соединен с одноименным входом блока арбитража выдачи символов; блок приема данных содержит буфер приема данных и дешифратор преобразованного кода, выход подтверждения приема символа управления потоком и выход «получен NULL» которого являются одноименными выходами блока приема данных, выход принятых данных которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности принятых данных которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, вход разрешения записи, буфера приема данных соединен с выходом подтверждения приема информационного символа дешифратора преобразованного кода и является одноименным выходом блока приема данных, вход сброса которого является входом сброса буфера приема данных.

Данное устройство поддерживает работу на частотах до 400 МГц с локальной частотой в 2 раза меньше, чем частота передачи и приема битов. То есть оно позволяет передавать поток битов данных и стробов в коммуникационном интерфейсе на частоте в два раза большей локальной частоты, на которой работают все остальные блоки устройства. Однако различное некратное кодирование символов SpaceWire, имеющих различную длину, не позволяет эффективно увеличить скорость передачи битов относительно частоты локальной синхронизации.

Недостатком данного технического решения является ограниченные функциональные возможности. С одной стороны, такое ограничение связано с отсутствием возможности передачи управляющих сигналов в реальном масштабе времени поверх потока передаваемых пакетных данных. С другой стороны, имеется ограничение скорости передачи битов и расстояния между взаимодействующими устройствами коммуникационного интерфейса, а также уменьшение надежности из-за отсутствия возможности применения гальванической изоляции устройств друг от друга, что не позволяет предотвращать отказы и неисправности из-за коротких замыканий.

В основу настоящего изобретения поставлена задача разработки устройства коммуникационного интерфейса, обеспечивающего расширение функциональных возможностей за счет реализации возможности передачи в реальном масштабе времени системных управляющих сигналов наряду с передачей битов пакетных данных; повышение скорости передачи и приема битов данных; преодоление ограничений взаимодействия устройств на больших расстояниях и возможность применения гальванической изоляции взаимодействующих устройств.

Техническим результатом предлагаемого изобретения является расширение области применения устройства коммуникационного интерфейса за счет обеспечения передачи управляющих сигналов системного уровня и использования схемы кодирования, обеспечивающей выравнивание длины передаваемых символов и позволяющей передавать биты данных по кабелю, содержащему только одну линию передачи данных в каждую сторону, а также увеличивать длину кабеля коммуникационного интерфейса при достижении более высоких показателей быстродействия и надежности по сравнению с известными аналогами.

Технический результат достигается тем, что в предложенном устройстве коммуникационного интерфейса для сети SpaceWire, содержащем блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными выходами блока приема данных и одноименными входами блока управления, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства, вход сброса системного интерфейса устройства является входом сброса блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, выход «получен NULL» которого соединен с одноименным входом блока управления, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком блока выдачи данных являются соответственно одноименными выходами блока арбитража выдачи символов, вход запроса на выдачу символа управления потоком которого является одноименным входом блока выдачи данных, вход сброса которого является входом сброса блока арбитража выдачи символов и соединен с входом сброса буфера выдачи данных, выход готовности данных которого соединен с одноименным входом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом синхронизации блока выдачи данных, входы разрешения выдачи и разрешения передачи символа управления потоком которого является одноименными входами блока арбитража выдачи символов, выход чтения данных которого соединен с одноименным входом буфера выдачи данных, выход признака конца пакета которого соединен с одноименным входом блока арбитража выдачи символов; блок приема данных содержит буфер приема данных и дешифратор преобразованного кода, выход подтверждения приема символа управления потоком и выход «получен NULL» которого являются одноименными входами блока управления, выход принятых данных которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности принятых данных которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, вход разрешения записи буфера приема данных соединен с выходом подтверждения приема информационного символа дешифратора преобразованного кода и является одноименным выходом блока приема данных, вход сброса которого является входом сброса буфера приема данных, дополнительно введены преобразователь передаваемых символов, блок кодирования 8b/10b, блок передачи битов, блок приема битов, блок декодирования 8b/10b, буфер символов 8b, преобразователь принимаемых символов, блок проверки соединения, выход ошибки рассоединения которого соединен с одноименным входом блока управления, первый выход сброса соединен с одноименными входами преобразователя передаваемых символов и блока кодирования 8b/10b, информационный вход которого соединен с выходом данных символа 8b преобразователя передаваемых символов, выход готовности выдачи символа которого соединен с вход готовности блока выдачи данных, информационный выход и выход типа символа которого соединены соответственно с входами данных и типа символа преобразователя передаваемых символов, выход признака спецсимвола которого соединен с входом признака типа символа блока кодирования 8b/10b, выход кодированных данных которого соединен с одноименным входом блока передачи битов, выход битовых сигналов которого является одноименным выходом коммуникационного интерфейса устройства, выход локальной синхронизации блока передачи битов соединен с одноименными входами блока кодирования 8b/10b, преобразователя передаваемых символов, буфера символов 8b, преобразователя принимаемых символов, блока управления, блока приема данных и блока выдачи данных, вход записи управляющего кода которого является одноименным входом системного интерфейса устройства, выход готовности выдачи управляющего кода которого является одноименным выходом блока выдачи данных, вход управляющего кода для выдачи которого является одноименным входом системного интерфейса устройства, выход принятого управляющего кода которого является одноименным выходом блока приема данных, выход готовности принятого управляющего кода которого является одноименным выходом системного интерфейса устройства, вход чтения управляющего кода которого является одноименным входом блока приема данных, информационный вход и вход типа символа которого соединены соответственно с одноименными входами преобразователя принимаемых символов, информационный вход и вход признака спецсимвола которого соединены соответственно с одноименными выходами буфера символов 8b, вход разрешения записи соединен с одноименным выходом блока декодирования 8b/10b, выход символа 8b которого соединен с информационными входами буфера символов 8b и блока проверки соединения, вход признака спецсимвола которого соединен с одноименным входом буфера символов 8b и с одноименным выходом блока декодирования 8b/10b, выход ошибки кодирования которого соединен с одноименным входом блока управления, вход установления соединения которого соединен с одноименным выходом блока проверки соединения, вход признака соединения которого соединен с одноименным входом преобразователя принимаемых символов и с одноименным выходом блока приема битов, выход синхронизации приема данных которого соединен с входом синхронизации приема буфера символов 8b, с входом синхронизации блока проверки соединения и с входом синхронизации блока декодирования 8b/10b, информационный вход которого соединен с выходом принятых кодированных данных блока приема битов, вход битовых сигналов которого является одноименным входом коммуникационного интерфейса устройства, причем в блок выдачи данных введен регистр выдачи управляющего кода, выход готовности выдачи управляющего кода которого является одноименным выходом блока выдачи данных, вход записи которого является входом записи регистра выдачи управляющего кода, вход управляющего кода для выдачи которого является одноименным входом блока выдачи данных, входы сброса и синхронизации которого соединены соответственно с входами сброса и синхронизации регистра выдачи управляющего кода, выход готовности управляющего кода которого соединен с одноименным входом блока арбитража выдачи символов, выход чтения управляющего кода которого соединен с одноименным входом регистра выдачи управляющих кодов, выход управляющего кода которого соединен со вторым информационным входом мультиплексора данных; в блок приема данных введен регистр приема управляющего кода, информационный вход которого является одноименным входом блока приема данных, входы сброса и локальной синхронизации которого соединены соответственно с входами сброса и локальной синхронизации регистра приема управляющего кода, выходы готовности принятого управляющего кода и принятого управляющего кода которого являются соответственно одноименными выходами блока приема данных, вход чтения управляющего кода которого является одноименным входом регистра приема управляющего кода, входы разрешения записи и синхронизации которого соединены соответственно с входом синхронизации блока приема данных и с выходом селекции управляющего кода дешифратора преобразованного кода.

Предпочтительно, преобразователь передаваемых символов содержит регистр выходных данных, первый регистр типа символа, селектор управляющего кода, триггер управляющего кода, первое ПЗУ констант, выходной мультиплексор, первый счетчик, первый элемент И, второй элемент И, третий элемент И, выход готовности выдачи символа которого является одноименным выходом преобразователя передаваемых символов, вход данных которого является входом данных регистра выходных данных, выход которого соединен с первым информационным входом выходного мультиплексора, выход данных символа 8b которого является одноименным выходом преобразователя передаваемых символов, вход локальной синхронизации которого соединен с входами синхронизации первого регистра типа символа, первого триггера управляющего кода, со счетным входом первого счетчика и с входом синхронизации регистра входных данных, вход сброса преобразователя соединен с входами сброса регистра выходных данных, первого регистра типа символа, первого триггера управляющего кода и первого счетчика, выход переноса которого соединен со вторым входом первого ПЗУ констант, со вторым инверсным входом второго элемента И, с вторым входом первого элемента И, выходе запрета которого соединен с инверсным входом сброса первого счетчика, вход типа символа преобразователя передаваемых символов является входом данных первого регистра типа символа, выход первого регистра типа символа соединен с первым входом первого ПЗУ констант и с входом селектора управляющего кода, выход селекции управляющего кода которого соединен с первым входом третьего элемента И, выход установки флага которого соединен с входом данных триггера управляющего кода, прямой выход которого соединен с первым входом первого элемента И, с первым инверсным входом второго элемента И, с третьим входом первого ПЗУ констант, выход кода спецсимвола которого соединен с вторым информационным входом выходного мультиплексора. Выход признака спецсимвола первого ПЗУ констант является одноименным выходом преобразователя передаваемых символов и соединен с управляющим входом выходного мультиплексора, инверсный выход триггера соединен со вторым входом третьего элемента И.

Предпочтительно, преобразователь принимаемых символов содержит второе ПЗУ констант, второй регистр типа символа, второй триггер управляющего кода, входной мультиплексор, регистр типа входного символа, регистр входных данных, выход типа принятого символа которого является одноименным выходом преобразователя принимаемых символов, информационный вход которого соединен с входом данных регистра входных данных и с первым входом второго ПЗУ констант, второй вход второго ПЗУ констант является входом признака спецсимвола преобразователя принимаемых символов, разрешающий вход ПЗУ является входом признака соединения преобразователя принимаемых символов, выход типа символа второго ПЗУ констант соединен с входом данных второго регистра типа символа и с первым информационным входом входного мультиплексора, выход селекции управляющего кода второго ПЗУ констант соединен с входом данных второго триггера управляющего кода и с входом сброса регистра типа входного символа, вход данных которого соединен с выходом входного мультиплексора, второй информационный вход которого соединен с выходом задержанного типа символа второго регистра типа символа, вход синхронизации которого является входом локальной синхронизации преобразователя принимаемых символов и соединен с входами синхронизации второго триггера управляющего кода, регистра типа входного символа и регистра входных данных, выход которого является информационным выходом преобразователя принимаемых символов.

В данном устройстве коммуникационного интерфейса технический результат обеспечивается за счет применения дополнительного преобразования символов технологии SpaceWire в символы формата 8b с последующим кодированием 8b/10b перед их передачей в виде последовательности битовых сигналов в удаленное устройство по выделенному коммуникационному каналу, имеющему одну линию передачи в каждом направлении. Кроме символов пакетных данных сети SpaceWire данное устройство дополнительно обеспечивает передачу управляющих сигналов реального времени для поддержки системных механизмов (метки системного времени, прерывания и др.). В результате данного технического решения появились условия для передачи данных между устройствами в сети SpaceWire на расстояниях, значительно превышающих значения, определяемые для кабелей в стандарте SpaceWire, при одновременном снятии ограничений на повышение скорости передачи данных в коммуникационном канале. Использование для передачи данных только одной линии существенно уменьшает влияние джиттера сигнала на ограничение скорости передачи, так как джиттер сигнала будет зависеть только от одного передатчика. Использование кодирования 10b/8b позволяет повысить скорость передачи битовых сигналов в коммуникационном канале относительно частоты локальной синхронизации в десять раз и упростить реализацию устройства на частоте локальной синхронизации в силу одинаковой кратности символов 8b/10b в отличие от заложенной в стандарте неодинаковой кодировки символов SpaceWire. Кроме того, обеспечиваемая при этом возможность использования гальванической развязки на входе и выходе коммуникационного интерфейса позволяет повысить надежность работы устройства.

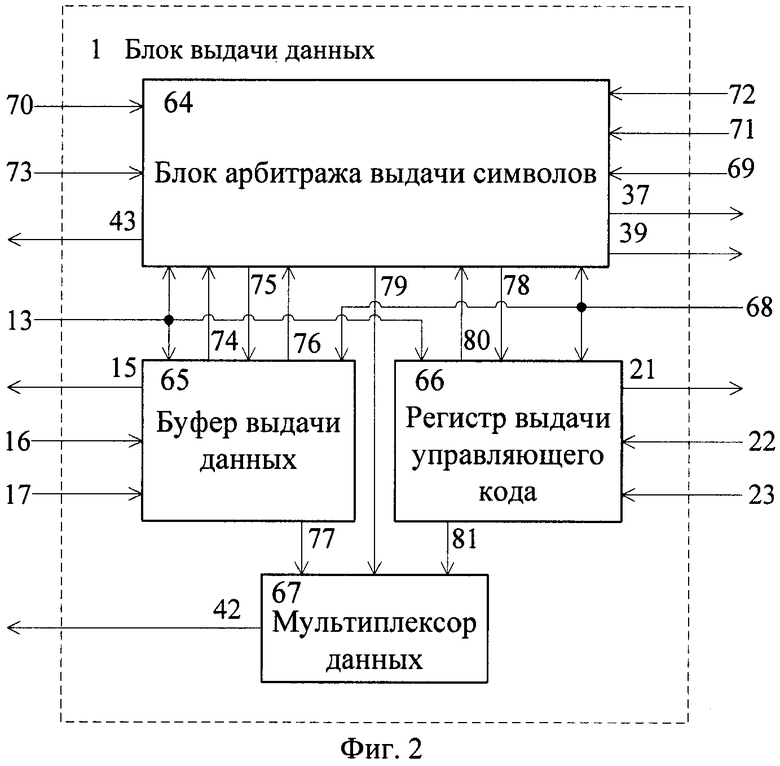

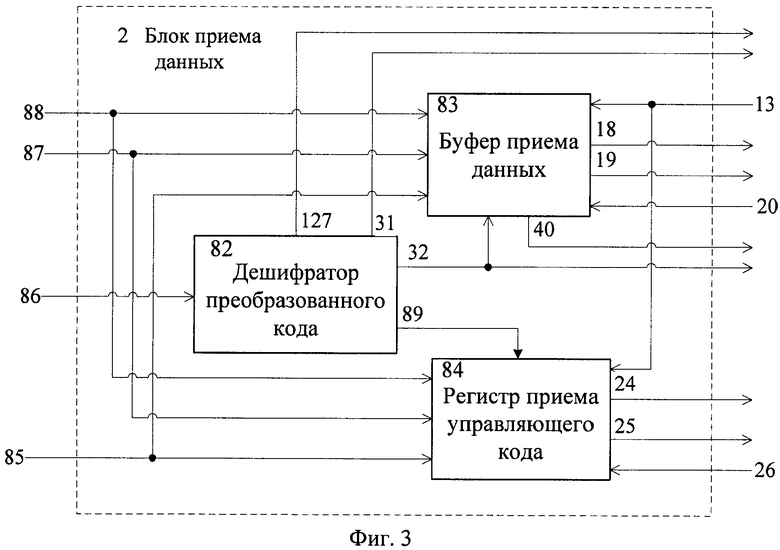

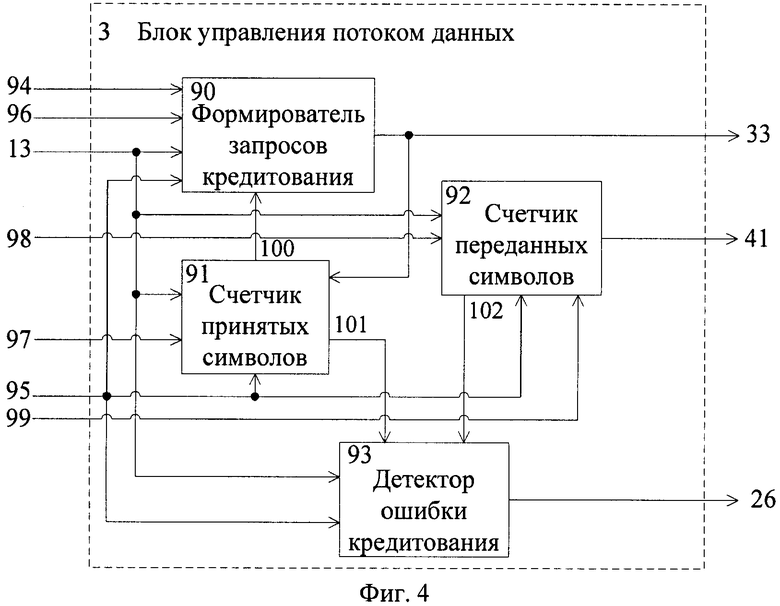

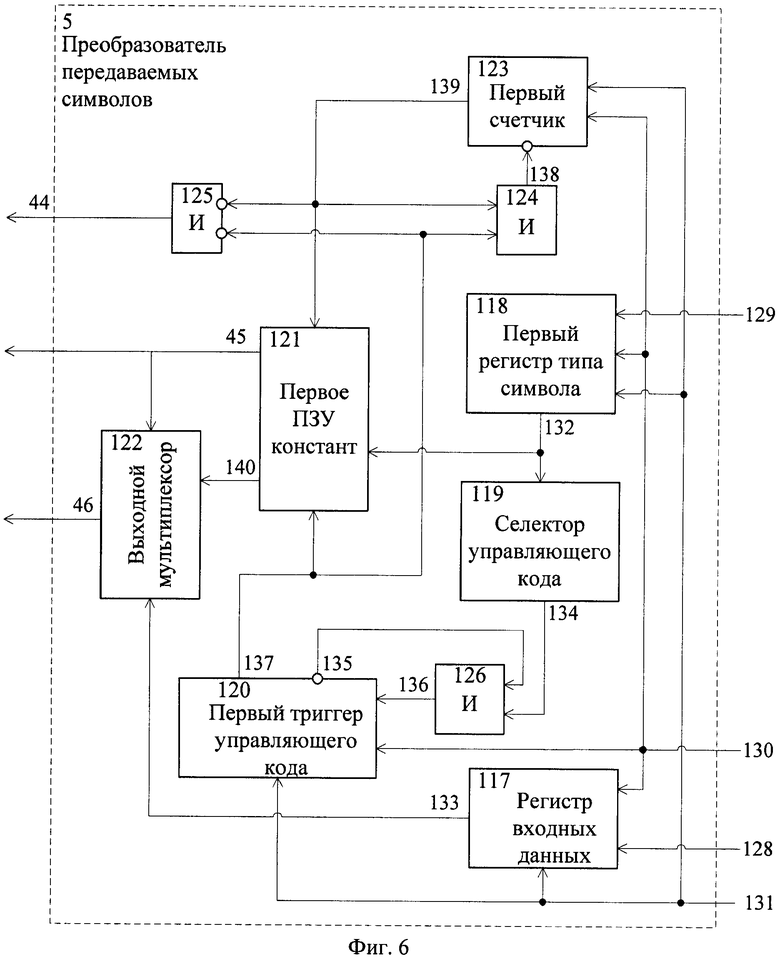

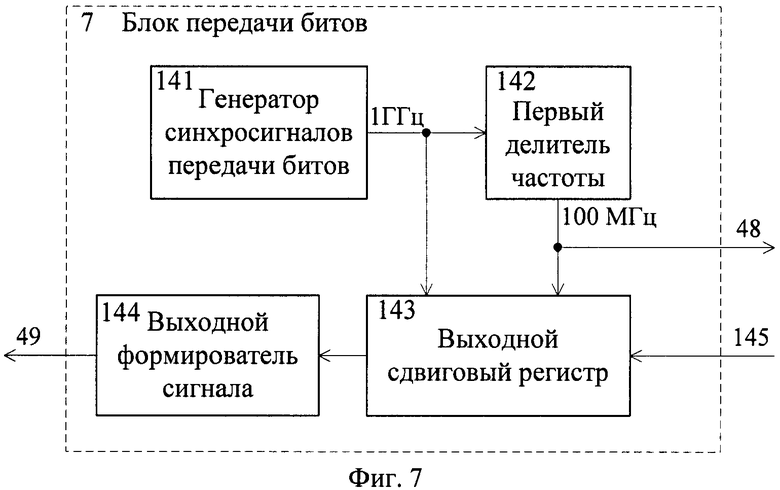

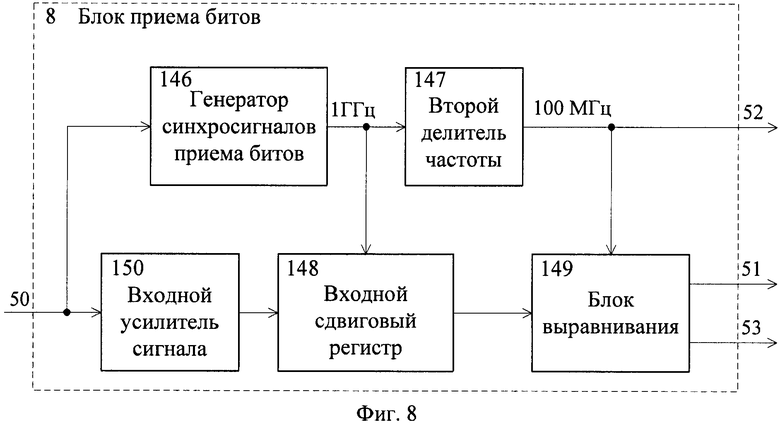

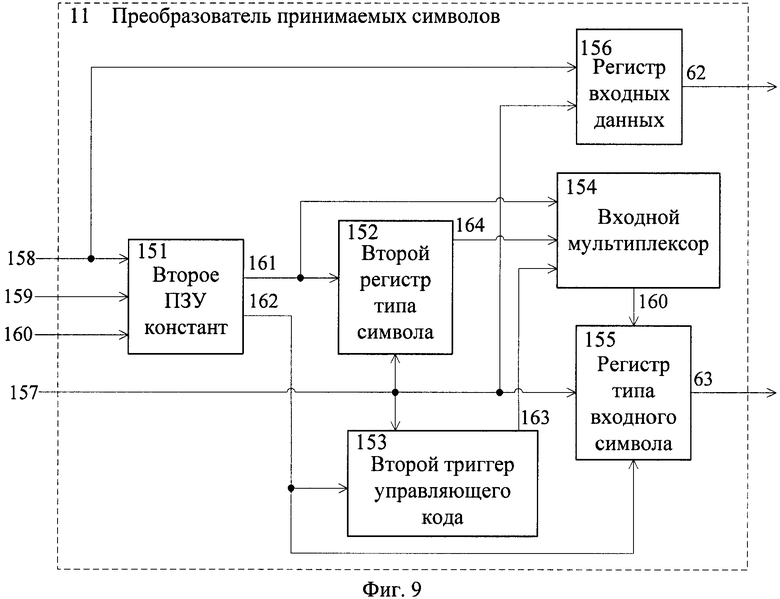

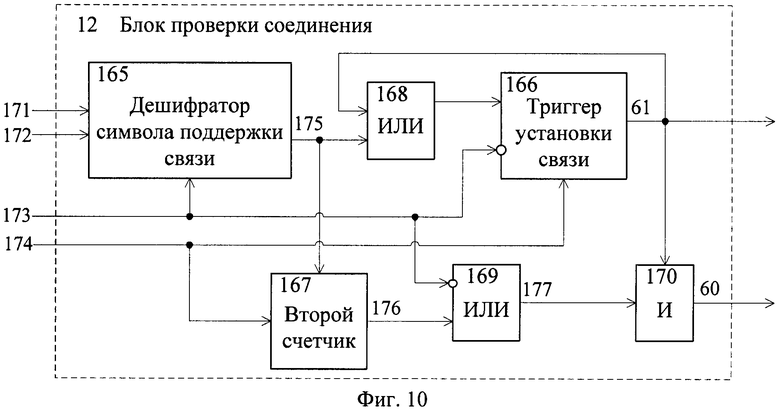

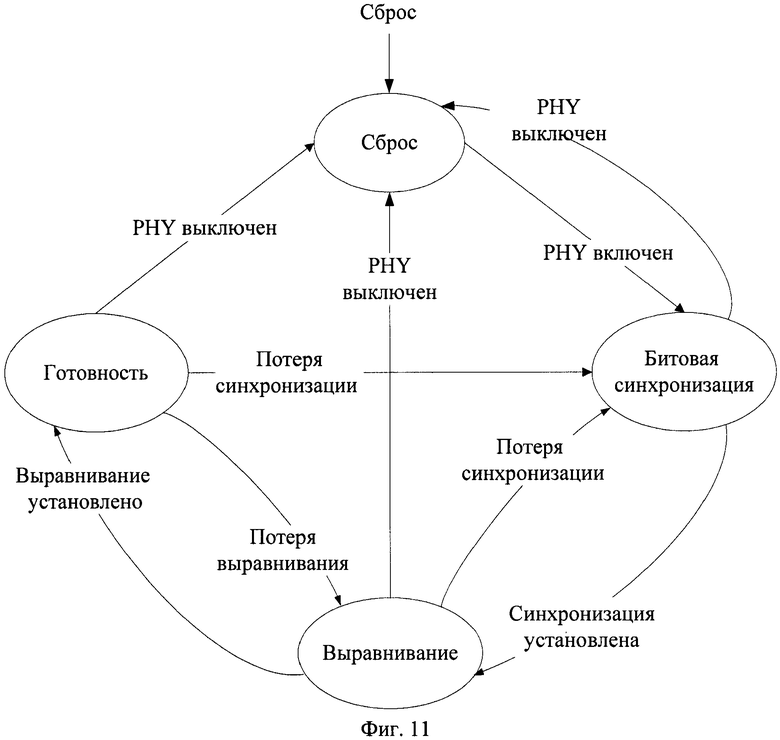

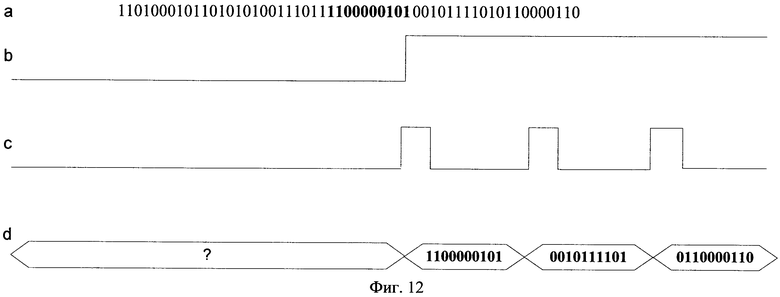

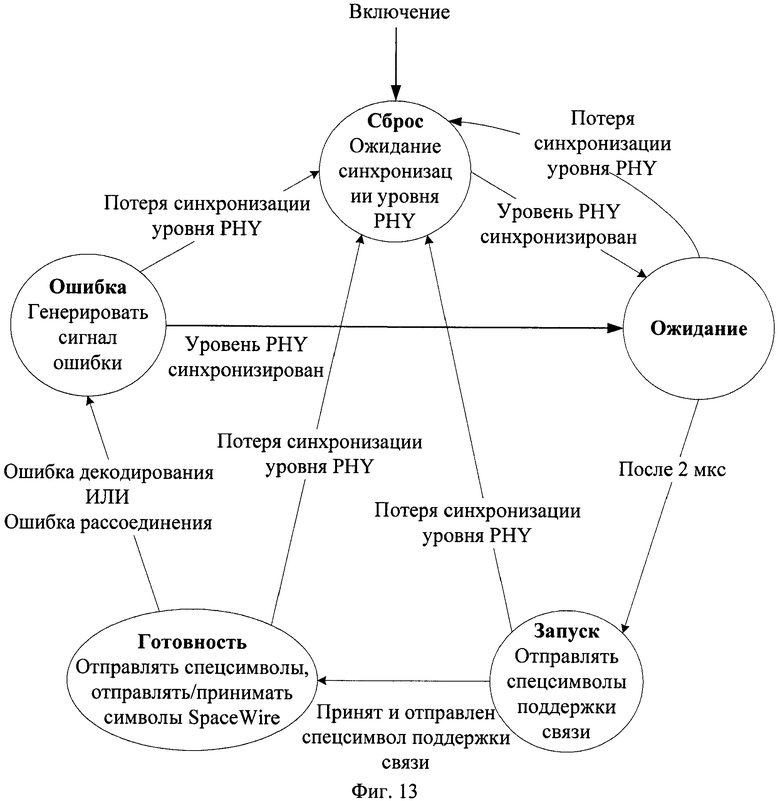

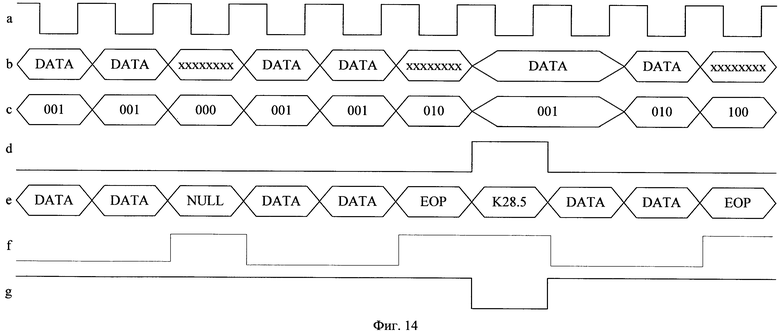

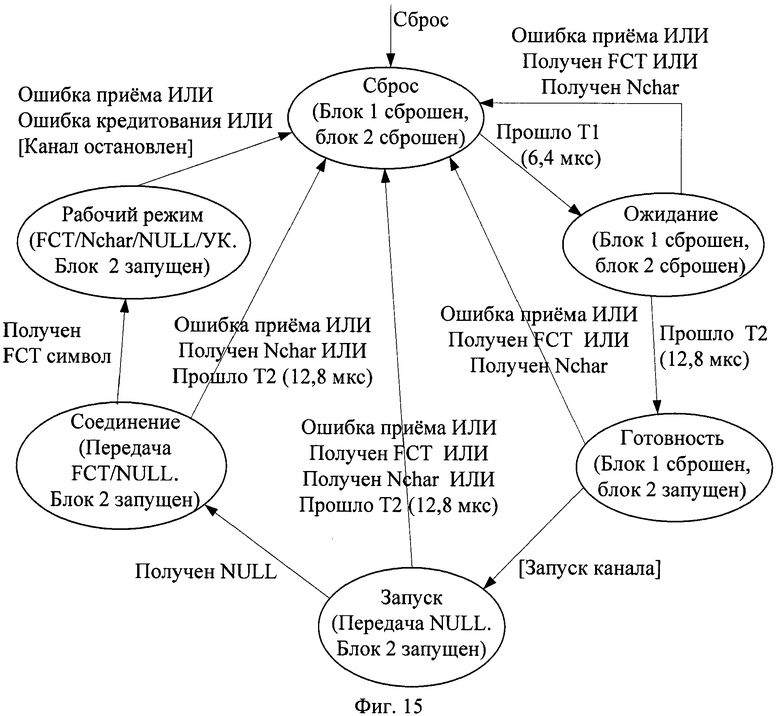

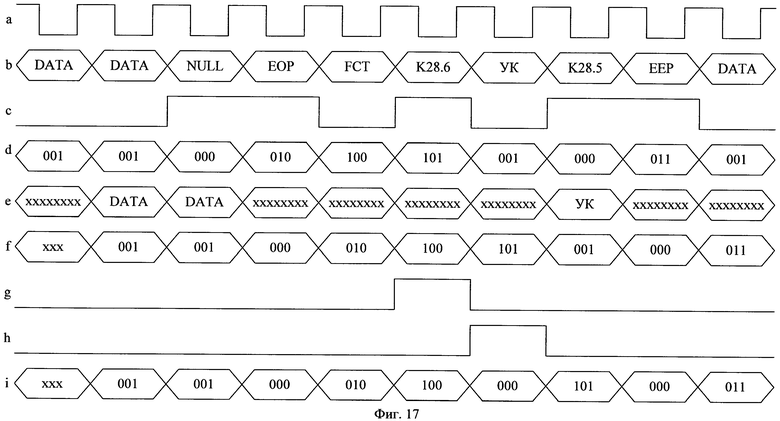

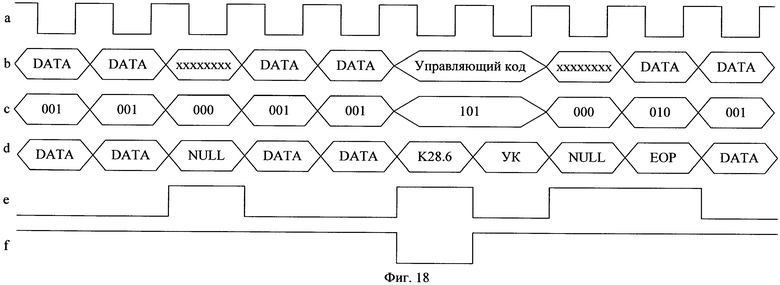

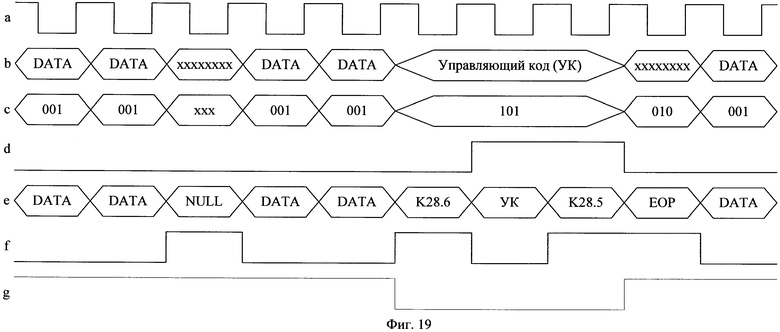

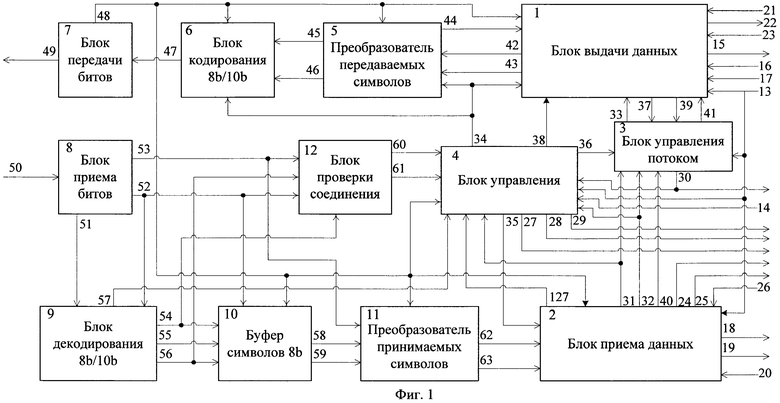

Детально сущность данного технического решения поясняется описанием со ссылками на фигуры чертежей, где на фиг.1 представлена структурная схема устройства, на фиг.2 - функциональная схема блока выдачи данных, на фиг.3 - функциональная схема блока приема данных. На фиг.4 и 5 представлены возможные варианты реализации функциональных схем блока управления потоком данных и блока управления. На фиг.6 приведена функциональная схема преобразователя передаваемых символов. На фиг.7 приведен вариант возможной реализации функциональной схемы блока передачи битов. На фиг.8 приведен вариант возможной реализации функциональной схемы блока приема битов. На фиг.9 приведена функциональная схема преобразователя принимаемых символов. На фиг.10 приведена функциональная схема блока проверки соединения. На фиг.11 показан автомат состояний физического уровня обмена сигналами (PHY). На фиг.12 приведены временные диаграммы, иллюстрирующие процедуру выравнивания символов 10b. На фиг.13 изображен автомат уровня адаптации SpaceWire. На фиг.14 приведены временные диаграммы, иллюстрирующие передачу спецсимвола поддержки связи среди других символов. На фиг.15 представлен граф машины состояния, описывающий режимы функционирования устройства на уровне обмена SpaceWire. На фиг.16 приведены временные диаграммы передачи байтов пакетных данных, на фиг.17 - временные диаграммы приема символов данных, управляющих символов и управляющих кодов, на фиг.18 - временные диаграммы передачи управляющего кода, на фиг.19 - временные диаграммы передачи управляющего кода и спецсимвола поддержки связи.

Как показано на фиг.1, предлагаемое устройство содержит блок 1 выдачи данных, блок 2 приема данных, блок 3 управления потоком данных, блок 4 управления, преобразователь 5 передаваемых символов, блок 6 кодирования 8b/10b, блок 7 передачи битов, блок 8 приема битов, блок 9 декодирования 8b/10b, буфер 10 символов 8b, преобразователь 11 принимаемых символов, блок 12 проверки соединения, вход 13 синхронизации системного интерфейса, вход 14 сброса системного интерфейса, выход 15 готовности выдачи данных системного интерфейса, вход 16 записи данных системного интерфейса, вход 17 данных для выдачи системного интерфейса, выход 18 готовности принятых данных системного интерфейса, выход 19 принятых данных системного интерфейса, вход 20 чтения данных системного интерфейса, выход 21 готовности выдачи управляющего кода системного интерфейса, вход 22 записи управляющего кода системного интерфейса, вход 23 управляющего кода для выдачи системного интерфейса, выход 24 готовности принятого управляющего кода системного интерфейса, выход 25 принятого управляющего кода системного интерфейса, вход 26 чтения управляющего кода системного интерфейса, выход 27 установления соединения системного интерфейса, выход 28 ошибки рассоединения системного интерфейса, выход 29 ошибки кодировки символа системного интерфейса, выход 30 ошибки кредитования системного интерфейса, выход 31 подтверждения приема символа управления потоком, выход 32 подтверждения приема информационного символа, выход 33 запроса на выдачу символа управления потоком, первый выход 34 сброса, второй выход 35 сброса, третий выход 36 сброса, выход 37 готовности выдачи символа управления потоком, выход 38 разрешения передачи символа управления потоком, выход 39 подтверждения выдачи информационного символа, выход 40 разрешения приема данных, выход 41 разрешения выдачи данных, информационный выход 42, выход 43 типа символа, выход 44 готовности выдачи символа, выход 45 признака спецсимвола, выход 46 данных символа 8b, выход 47 кодированных данных, выход 48 локальной синхронизации, выход 49 битовых сигналов коммуникационного интерфейса, вход 50 битовых сигналов коммуникационного интерфейса, выход 51 принятых кодированных данных, выход 52 синхронизации приема данных, выход 53 признака соединения, выход 54 символа 8b, выход 55 признака спецсимвола, выход 56 разрешения записи, выход 57 ошибки кодирования, информационный выход 58, выход 59 признака спецсимвола, выход 60 ошибки рассоединения, выход 61 установления соединения, информационный выход 62, выход 63 типа принятого символа, выход 127 «Получен NULL».

Блок 1 выдачи данных (см. фиг.2) содержит блок 64 арбитража выдачи символов, буфер 65 выдачи данных, регистр 66 выдачи управляющего кода, мультиплексор 67 данных, вход 68 сброса, вход 69 разрешения выдачи, вход 70 синхронизации выдачи, вход 71 запроса на выдачу символа управления потоком, вход 72 разрешения передачи символа управления потоком, вход 73 готовности, выход 74 готовности данных, выход 75 чтения данных, выход 76 признака конца пакета, выход 77 данных, выход 78 чтения управляющего кода, выход 79 селекции информации, выход 80 готовности управляющего кода, выход 81 управляющего кода, вход 13 синхронизации, выход 15 готовности выдачи данных, вход 16 записи, вход 17 данных для выдачи, выход 21 готовности выдачи управляющего кода, вход 22 записи управляющего кода, вход 23 управляющего кода для выдачи, выход 37 готовности выдачи символа управления потоком, выход 39 подтверждения выдачи информационного символа, информационный выход 42, выход 43 типа символа.

Блок 2 приема данных (см. фиг.3) содержит дешифратор 82 преобразованного кода, буфер 83 приема данных, регистр 84 приема управляющего кода, информационный вход 85, вход 86 типа символа, вход 87 сброса, вход 88 локальной синхронизации, выход 89 селекции управляющего кода, выход 127 «Получен NULL», вход 13 синхронизации системного интерфейса, выход 18 готовности принятых данных, выход 19 принятых данных, вход 20 чтения данных системного интерфейса, выход 24 готовности принятого управляющего кода, выход 25 принятого управляющего кода, вход 26 чтения управляющего кода системного интерфейса, выход 31 подтверждения приема символа управления потоком, выход 32 подтверждения приема информационного символа, выход 40 разрешения приема данных.

Блок 3 управления потоком данных содержит (см. фиг.4) формирователь 90 запросов кредитования, счетчик 91 принятых символов, счетчик 92 переданных символов, детектор 93 ошибки кредитования, вход 94 разрешения приема данных, вход 95 сброса, вход 96 готовности выдачи символа управления потоком, вход 97 подтверждения приема информационного символа, вход 98 подтверждения приема символа управления потоком, вход 99 подтверждения выдачи информационного символа, выход 100 состояния счетчика, выход 101 ошибки кредита приема, выход 102 ошибки кредита выдачи, вход 13 синхронизации, выход 26 ошибки кредитования, выход 33 запроса на выдачу символа управления потоком, выход 41 разрешения выдачи данных.

Блок 4 управления содержит (см. фиг.5) регистр 103 состояния, блок 104 формирования нового состояния, формирователь 105 управляющих сигналов, блок 106 задержки, вход 107 установления соединения, вход 108 ошибки кредитования, вход 109 ошибки рассоединения, вход 110 ошибки кодировки символа, вход 111 подтверждения приема символа управления потоком, вход 112 подтверждения приема информационного символа, вход 113 локальной синхронизации, выход 114 состояния, выход 115 управления состоянием, управляющий выход 116, вход 178 «Получен NULL», вход 13 синхронизации системного интерфейса, вход 14 сброса системного интерфейса, выход 27 установления соединения системного интерфейса, выход 28 ошибки рассоединения системного интерфейса, выход 29 ошибки кодировки символа системного интерфейса, первый выход 34 сброса, второй выход 35 сброса, третий выход 36 сброса, выход 38 разрешения передачи символа управления потоком.

Преобразователь 5 передаваемых символов (см. фиг.6) содержит регистр 117 выходных данных, первый регистр 118 типа символа, селектор 119 управляющего кода, триггер 120 управляющего кода, первое ПЗУ 121 констант, выходной мультиплексор 122, первый счетчик 123, первый элемент 124 И, второй элемент 125 И, третий элемент 126 И, вход 128 данных, вход 129 типа символа, вход 130 локальной синхронизации, вход 131 сброса, выход 132 типа символа, выход 133 селекции символа данных, выход 134 селекции управляющего кода, инверсный выход 135 флага управляющего кода, выход 136 установки флага, прямой выход 137 управляющего кода, выход 138 запрета счета, выход 139 переноса, выход 140 кода спецсимвола, выход 44 готовности выдачи символа, выход 45 признака спецсимвола, выход 46 данных символа 8b.

Блок 7 передачи битов (см. фиг.7) содержит генератор 141 синхросигналов передачи битов, первый делитель 142 частоты, выходной сдвиговый регистр 143, выходной формирователь сигнала 144, вход 145 кодированных данных, выход 48 локальной синхронизации, выход 49 битовых сигналов.

Блок 8 приема битов (см. фиг.8) содержит генератор 146 синхросигналов приема битов, второй делитель 147 частоты, входной сдвиговый регистр 148, блок 149 выравнивания, выходной усилитель сигнала 150, вход 50 битовых сигналов, выход 51 принятых кодированных данных, выход 52 синхронизации приема данных, выход 53 признака соединения.

Преобразователь 11 принимаемых символов (см. фиг.9) содержит второе ПЗУ 151 констант, второй регистр 152 типа символа, второй триггер 153 управляющего кода, входной мультиплексор 154, регистр 155 типа входного символа, регистр 156 входных данных, вход 157 локальной синхронизации, информационный вход 158, вход 159 признака спецсимвола, вход 160 признака соединения, выход 161 типа символа, выход 162 селекции управляющего кода, выход 163 флага управляющего кода, выход 164 задержанного типа символа, информационный выход 62, выход 63 типа принятого символа.

Блок 12 проверки соединения (см. фиг.10) содержит дешифратор 165 символа поддержки связи, триггер 166 установки связи, второй счетчик 167, первый элемент 168 ИЛИ, второй элемент 169 ИЛИ, четвертый элемент 170 И, информационный вход 171, вход 172 признака спецсимвола, вход 173 признака соединения, вход 174 синхронизации, выход 175 селекции символа поддержки связи, выход 176 переноса, выход 177 признака рассоединения, выход 60 ошибки рассоединения, выход 61 установления соединения.

На временных диаграммах (см. фиг.12) для процесса выравнивания символов в устройстве показано: а - значения битовых сигналов, b - признак соединения на выходе 53 блока 8 приема битов, с - тактовые сигналы на выходе 52 синхронизации приема данных блока 8 приема битов, d - выровненные символы 10b на выходе 51 блока 8 приема битов.

На временных диаграммах (см. фиг.14) для процесса передачи спецсимвола поддержки связи показано: а - тактовые сигналы, b - данные на выходе 133 регистра 117 выходных данных, с - код типа символа на выходе 132 первого регистра 118 типа символа, d - сигнал переноса на выходе 139 первого счетчика 123, е - данные на выходе 46 выходного мультиплексора 122, f - признак спецсимвола на выходе 45 первого ПЗУ 121 констант, g - сигнал готовности записи в регистры 117 и 118 на выходе 44 преобразователя 5 передаваемых символов.

На временных диаграммах (см. фиг.16) для процесса передачи байтов пакетных данных преобразователя 5 передаваемых символов: а - тактовые сигналы, b - данные на выходе 133 регистра 117 выходных данных, с - код типа символа на выходе 132 первого регистра 118 типа символа, d - данные на выходе 46 выходного мультиплексора 122, е - признак спецсимвола на выходе 45 первого ПЗУ 121 констант, f - сигнал готовности записи в регистры 117и 118 на выходе 44 преобразователя 5 передаваемых символов.

На временных диаграммах (см. фиг.17) для процесса приема символов 8b показано: а - тактовые сигналы, b - данные на информационном входе 158 преобразователя 11 принимаемых символов, c - признак спецсимвола на входе 159 второго ПЗУ 151 констант, d - код типа символа на выходе 161 типа символа второго ПЗУ 151, е - данные на информационном выходе 62 регистра 156 входных данных, f - код типа символа на выходе 164 задержанного типа символа второго регистра 152 типа символа, g - признак управляющего кода на выходе 162 селекции управляющего кода второго ПЗУ 151, h - флаг управляющего кода на выходе 163 второго триггера 153 управляющего кода, i - код типа символа на выходе 63 регистра 155 типа входного символа.

На временных диаграммах (см. фиг.18) для процесса передачи управляющего кода показано: а - тактовые сигналы, b - данные на выходе 133 регистра 117 выходных данных, с - код типа символа на выходе 132 первого регистра 118 типа символа, d - данные на выходе 46 выходного мультиплексора 122, е - признак спецсимвола на выходе 45 первого ПЗУ 121 констант, f - сигнал готовности на выходе 44 преобразователя 5 передаваемых символов.

На временных диаграммах (см. фиг.19) для процесса передачи управляющего кода и спецсимвола поддержки связи показано: а - тактовые сигналы, b - данные на выходе 133 регистра 117 выходных данных, с - код типа символа на выходе 132 первого регистра 118 типа символа, d - сигнал переноса на выходе 139 первого счетчика 123, е - данные на выходе 46 выходного мультиплексора 122, f - признак спецсимвола на выходе 45 первого ПЗУ 121 констант, g - сигнал готовности на выходе 44 преобразователя 5 передаваемых символов.

Блок 1 выдачи данных предназначен для формирования символов данных SpaceWire из пакетных данных, поступающих через вход данных для выдачи, соединенного с одноименным входом 17 системного интерфейса устройства, а также управляющих символов по требованию, поступающему с выхода 33 запроса на выдачу символа управления потоком блока 3 управления потоком данных на одноименный вход блока 1. Вход 16 записи данных системного интерфейса устройства является одноименным входом блока 1 выдачи данных, выход 15 готовности выдачи данных которого является одноименным выходом системного интерфейса-устройства. Выход 15 и вход 16 системного интерфейса предназначены для реализации стандартного механизма буферизации пакетных данных из хост-системы (компьютера, коммутатора или другого узла сети SpaceWire) в блоке 1 выдачи данных. Вход 22 записи управляющего кода системного интерфейса устройства является одноименным входом блока 1 выдачи данных, выход 21 готовности выдачи управляющего кода которого является одноименным выходом системного интерфейса. Вход 23 управляющего кода для выдачи системного интерфейса устройства соединен с одноименным входом блока 1. Запись байтов пакетных данных и управляющих кодов в блок 1 тактируется с его входа синхронизации, соединенного с входом 13 синхронизации системного интерфейса устройства. Выходы 37 готовности выдачи символа управления потоком и 39 подтверждения выдачи информационного символа блока 1 соединены с одноименными входами блока 3 управления потоком данных и предназначены для реализации механизма кредитования, необходимого для организации передачи и приема данных через коммуникационный интерфейс без переполнения буферов приема у взаимодействующих устройств. Информационный выход 42 блока 1 соединен с входом данных преобразователя 5 передаваемых символов и обеспечивают передачу байтов данных пакетов и управляющих кодов. Выход 43 типа символа блока 1 соединен с одноименным входом преобразователя 5 передаваемых символов и предназначен для определения типа передаваемого символа SpaceWire.

Блок 2 приема данных обеспечивает получение символов SpaceWire и управляющих кодов от удаленного устройства, буферизацию байтов данных пакетов и управляющих кодов. Выход 19 принятых данных блока 2 является одноименным выходом системного интерфейса устройства и обеспечивает выдачу байтов буферируемых пакетных данных в хост-систему. Выход 18 готовности принятых данных блока 2 является одноименным выходом системного интерфейса устройства, вход 20 чтения данных которого является одноименным входом блока 2 приема данных. Выход 40 разрешения приема данных блока 2, соединенный с одноименным входом блока 3 управления потоком данных, предназначен для извещения о наличии достаточного свободного пространства в буфере 83 приема данных. Выход 25 принятого управляющего кода блока 2 является одноименным выходом системного интерфейса устройства и обеспечивает выдачу управляющего кода в хост-систему. Выход 24 готовности принятого управляющего кода блока 2 является одноименным выходом системного интерфейса устройства, вход 26 чтения управляющего кода которого является одноименным входом блока 2 приема данных. Блок 2 приема данных обеспечивает извещение блока 3 управления потоком данных и блока 4 управления через выход 31 приема символа управления потоком, соединенный с одноименными входами блоков 3 и 4, о приеме управляющего символа управления потоком и через выход 32 подтверждения приема информационного символа, соединенный с одноименными входами блоков 3 и 4, о получении информационного символа от удаленного устройства. Выход 127 «Получен NULL» блока 2 соединен с одноименным входом блока 4 управления.

Блок 3 управления потоком данных предназначен для реализации механизма кредитования, необходимого при обмене пакетными данными в дуплексном режиме между двумя устройствами через коммуникационный интерфейс с учетом ограниченного объема буферной памяти для приема данных, имеющейся у каждого устройства в блоке 2 приема данных. Выход 33 запроса на выдачу символа управления потоком блока 3, соединенный с одноименным входом блока 1 выдачи данных, предназначен для инициализации выдачи блоком 1 управляющего символа управления потоком, подтверждающего наличие в блоке 2 приема данных свободного буферного пространства, необходимого для приема определенного числа символов данных. В описываемом устройстве величина кредита, предоставляемого при выдаче одного символа управления потоком, в соответствии со стандартом SpaceWire принята равной восьми. Выход 26 ошибки кредитования блока 3 управления потоком данных соединен с одноименным входом блока 4 управления и является одноименным выходом системного интерфейса устройства. Блок 3 управления потоком данных тактируется с входа синхронизации, соединенного с входом 13 синхронизации системного интерфейса устройства.

Блок 4 управления предназначен для отслеживания состояния устройства при поступлении из блока 2 приема данных сигналов о выделении символов SpaceWire из принятого преобразованного кода и выработки управляющих сигналов под воздействием машины состояний и сигнала начальной установки с входа сброса, соединенного с входом 14 сброса системного интерфейса устройства. Выход 38 разрешения передачи символа управления потоком блока 4 управления соединен с одноименным входом блока 1 выдачи данных и предназначен для извещения о том, что машина состояния блока 4 перешла в режим, разрешающий выдачу символов управления потоком. Первый 34 выход сброса блока 4 управления соединен с входами сброса блока 1 выдачи данных, преобразователя 5 передаваемых символов и блока 6 кодирования 8b/10b. Второй 35 и третий 36 выходы сброса блока 4 управления соединены с входами сброса соответственно блока 2 приема данных и блока 3 управления потоком данных и предназначены для установки их в начальное состояние. Выход 27 установления соединения блока 4 является одноименным выходом системного интерфейса устройства и предназначен для информирования хост-системы об этом событии. Выход 28 ошибки рассоединения блока 4 является одноименным выходом системного интерфейса устройства и предназначен для информирования хост-системы об этом событии. Выход 29 ошибки кредитования блока 4 является одноименным выходом системного интерфейса устройства и предназначен для информирования хост-системы об этом событии. Тактирование при формировании сигналов состояния блока 4 управления осуществляется с входа синхронизации, соединенного с входом 13 синхронизации системного интерфейса устройства.

Преобразователь 5 передаваемых символов предназначен для перекодирования символов SpaceWire и управляющих кодов в символы 8b. Выход 46 данных символа 8b преобразователя 5 соединен с информационным входом блока 6 кодирования 8b/10b и предназначен для передачи восьмиразрядного кода символа 8b, который соответствует либо байту данных, либо коду специального символа управления. Выход 45 признака спецсимвола преобразователя 5 соединен с входом признака типа символа блока 6 кодирования 8b/10b и идентифицирует, какой тип символа 8b выдается с выхода 46 преобразователя 5 - в текущем такте (байт данных или специальный символ управления). Выход 44 готовности выдачи символа преобразователя 5 соединен с входом готовности блока 1 выдачи данных и обеспечивает индикацию состояния готовности преобразователя 5 к поступлению очередного символа SpaceWire или управляющего кода из блока 1 выдачи данных. Если сигнал готовности равен «0», то преобразователь 5 в текущем такте не считывает информацию из блока 1, поскольку занят формированием дополнительного символа 8b в соответствии с алгоритмом своего функционирования.

Блок 6 кодирования 8b/10b предназначен для преобразования восьмиразрядных символов в 10-разрядные символы стандарта 8b/10b. Выход 47 кодированных данных блока 6 соединен с одноименным входом блока 7 передачи битов и обеспечивает выдачу 10-разрядного кода в каждом такте локальной синхронизации.

Блок 7 передачи битов предназначен для выдачи в последовательном виде битовых сигналов сформированных 10-разрядных символов 10b и обеспечивает формирование необходимых для этого синхросигналов, определяющих скорость передачи сигналов в коммуникационном канале, а также тактовых сигналов локальной синхронизации. Выход 48 локальной синхронизации блока 7 соединен с одноименными входами блока 1 выдачи данных, блока 2 приема данных, блока 4 управления, преобразователя 5 передаваемых символов, блока 6 кодирования 8b/10b, эластичного буфера 10 и преобразователя 11 принимаемых символов. Выход 49 битовых сигналов блока 7 является одноименным выходом коммуникационного интерфейса устройства.

Блок 8 приема битов предназначен для приема входного потока битовых сигналов с входа 50 битовых сигналов коммуникационного интерфейса и формирования из них параллельного кода символов формата 10b на выходе 51 принятых кодированных данных, соединенным с информационным входом блока 9 декодирования 8b/10b. Выход 52 синхронизации приема данных блока 8 соединен с входом синхронизации блока 9 декодирования 8b/10b, с входом синхронизации приема буфера 10 символов 8b и с входом синхронизации блока 12 проверки соединения. Выход 53 признака соединения блока 8 предназначен для формирования единичного сигнала при выделении в потоке принятых битовых сигналов одного из специальных символов управления - символа проверки связи и соединен с одноименными входами преобразователя 11 принимаемых символов и блока 12 проверки соединения.

Блок 9 декодирования 8b/10b предназначен для преобразования символа 10b в параллельный код символа формата 8b на выходе 54 символа 8b, соединенном с информационными входами буфера 10 символов 8b и блока 12 проверки соединения. Выход 55 признака спецсимвола блока 9 соединен с одноименными входами буфера 10 символов 8b и блока 12 проверки соединения и определяет, какой тип символа 8b (байт данных или специальный символ управления) выдается с выхода 54 в текущем такте. Выход 56 разрешения записи блока 9 соединен с одноименным входом буфера 10 символов 8b и указывает при единичном значении, что блок 9 выставил на своих выходах 54 и 55 действительные данные. Выход 57 ошибки кодирования блока 9 соединен с одноименным входом блока 4 управления и извещает о выявлении ошибки при декодировании символов 10b.

Буфер 10 символов 8b предназначен для буферизации принимаемых символов в формате 8b на частоте приема и осуществления перехода в другой временной домен с локальной синхронизацией. Информационный выход 58 буфера 10 соединен с одноименным входом преобразователя 11 принимаемых символов и обеспечивает выдачу восьмиразрядного кода символа в формате 8b. Выход 59 признака спецсимвола буфера 10 соединен с одноименным входом преобразователя 11 принимаемых символов и определяет, какой символ считывается с выхода 58 буфера 10.

Преобразователь 11 принимаемых символов перекодирует символы формата 8b в символы стандарта SpaceWire. Информационный выход 62 преобразователя 11 соединен с одноименным входом блока 2 приема данных и обеспечивает передачу в него символов SpaceWire и управляющих кодов, полученных от удаленного устройства. Выход 63 типа символа преобразователя 11 соединен с одноименным входом блока 2 приема данных и предназначен для идентификации типа символа SpaceWire либо управляющего кода, выставленного на информационном выходе 62 в текущем такте.

Блок 12 проверки соединения осуществляет контроль за состоянием соединения между удаленными устройствами в процессе их взаимодействия путем отслеживания интервалов между поступлением специального символа управления - символа проверки связи. Выход 60 ошибки рассоединения блока 12 соединен с одноименным входом блока 4 управления и обеспечивает передачу единичного сигнала о нарушении соединения при истечении времени ожидания символа поверки связи. Выход 61 установления соединения блока 12 соединен с одноименным входом блока 4 управления и обеспечивает формирование сигнала готовности приема выровненных символов 10b/8b.

В блоке 1 выдачи данных буфер 65 выдачи данных (см. фиг.2) предназначен для промежуточного хранения пакетных данных, поступающих на вход данных для выдачи буфера 65, соединенный с одноименным входом 17 блока 1 выдачи данных. Выход 15 готовности выдачи данных буфера 65 является одноименным выходом блока 1 выдачи данных и предназначен для уведомления хост-системы через системный интерфейс о возможности буферизации очередного байта данных, которая осуществляется при подаче сигнала записи на вход записи буфера 65, являющийся входом 16 записи блока 1 выдачи данных. Буферизация данных обеспечивается при тактировании с входа синхронизации буфера 65, соединенного с входом 13 синхронизации блока 1 выдачи данных. Вход 68 сброса блока 1 выдачи данных соединен с входом сброса буфера 65 выдачи данных и предназначен для его инициализации. Представление информации в пакете данных, поступающем из системного интерфейса устройства в буфер 65 выдачи данных, показано в табл.1.

Считывание буферированных пакетных данных обеспечивается с выхода 77 данных буфера 65 выдачи данных, соединенного с первым информационным входом мультиплексора 67 данных. Выход 74 готовности данных буфера 65 соединен с одноименным входом блока 64 арбитража выдачи символов и предназначен для уведомления о наличии байта данных, готового к выдаче. Выход 76 признака конца пакета буфера 65 соединен с одноименным входом блока 64 арбитража выдачи символов и предназначен для индикации о том, что предыдущий байт был последним в пакете.

Регистр 66 выдачи управляющего кода предназначен для промежуточного хранения управляющего кода, поступающего на вход управляющего кода для выдачи, соединенный с одноименным входом 23 блока 1 выдачи данных. Выход 21 готовности выдачи управляющего кода регистра 66 является одноименным выходом блока 1 выдачи данных и предназначен для уведомления хост-системы через системный интерфейс о возможности выдачи очередного управляющего кода, которая осуществляется при подаче сигнала записи на вход записи регистра 66, соединенный с входом 16 записи блока 1 выдачи данных. Запоминание управляющего кода обеспечивается при тактировании с входа синхронизации регистра 66, соединенного с входом 13 синхронизации блока 1 выдачи данных. В управляющем коде, поступающем в устройство из хост-системы, содержится два поля: поле типа управляющего кода и поле значения управляющего кода. В поле типа управляющего кода указывается, для передачи какого конкретного системного сигнала управления используется данный управляющий код, например метки системного времени или сигнала системного прерывания. В поле значения управляющего кода приводится конкретный параметр, характеризующий смысл передаваемого системного сигнала управления, например значение текущего системного времени или вектор конкретного прерывания. Вход 68 сброса блока 1 выдачи данных соединен с входом сброса регистра 66 выдачи данных и предназначен для его инициализации. Считывание записанного управляющего кода обеспечивается с выхода 81 управляющего кода регистра 66, соединенного со вторым информационным входом мультиплексора 67 данных. Выход 80 готовности управляющего кода регистра 66 соединен с одноименным входом блока 64 арбитража выдачи символов и предназначен для уведомления о наличии управляющего кода, готового к выдаче.

Блок 64 арбитража выдачи символов предназначен для регулирования формирования и порядка выдачи символов данных и управляющих символов, определяемых стандартом SpaceWire, по требованиям от блока 3 управления потоком данных и управляющих кодов по мере их поступления и в зависимости от заданного приоритета. Символы SpaceWire, передаваемые устройством через коммуникационный интерфейс, подразделяются на канальные и информационные символы. К информационным символам относятся символ данных (Nchar), символ конца пакета (ЕОР) и символ ошибочного конца пакета (ЕЕР). Канальные символы предназначены для управления состоянием коммуникационного канала и в отличие от информационных символов в системный интерфейс не передаются. К канальным символам относятся символ управления потоком (FCT) и нулевой символ (NULL код). Символ FCT используется для реализации механизма кредитования при передаче пакетных данных между взаимодействующими через коммуникационный канал устройствами. NULL код предназначен для сохранения активности коммуникационного канала и должен постоянно передаваться, если канал не занят передачей других символов. С входа 71 запроса на выдачу символа управления потоком блока 1 выдачи данных, соединенного с одноименным входом блока 64, поступает требование выдачи управляющего символа управления потоком. Выход 75 чтения данных блока 64 арбитража выдачи символов, соединенный с одноименным входом буфера 65 выдачи данных, предназначен для управления темпом поступления данных из буфера 65 для формирования внутреннего кода символов данных в блоке 64. Выход 78 чтения управляющего кода блока 64, соединенный с одноименным входом регистра 66 управляющих кодов, предназначен для управления темпом выдачи управляющих кодов с выхода 81 регистра 66. Внутренне кодирование формируемых в блоке 64 символов показано в табл.2.

Вход 72 разрешения передачи символа управления потоком блока 1 выдачи данных, являющийся одноименным входом блока 64 арбитража выдачи символов, предназначен для первоначального разрешения выдачи символов FCT после установления соединения с удаленным устройством. Выход готовности 37 выдачи символа управления потоком блока 64, являющийся одноименным выходом блока 1 выдачи данных, предназначен для извещения блока 3 управления потоком о возможности выдачи очередного символа FCT. Выход 39 подтверждения выдачи информационного символа, являющийся одноименным выходом блока 1 выдачи данных, предназначен для извещения блока 3 управления потоком о выдаче очередного символа Nchar с целью управления кредитным счетчиком 92 переданных символов. Выход 43 типа символа блока 64 арбитража выдачи символов, являющийся одноименным выходом блока 1 выдачи данных, предназначен для идентификации в соответствии с кодировкой, приведенной в табл.2, символа иди управляющего кода, передаваемого через мультиплексор 67 данных. Выход 79 селекции информации блока 64, соединенный с управляющим входом мультиплексора 67 данных, обеспечивают выбор источника информации для передачи через мультиплексор 67. При нулевом значении сигнала селекции на информационный выход 42 мультиплексора 67 с первого информационного входа подается байт данных из буфера 65 выдачи данных; при единичном значении сигнала селекции на информационный выход 42 мультиплексора 67 со второго информационного входа подается управляющий код из буфера 66 выдачи управляющих кодов. Таким образом, как показано в табл.2, тип символа данных или управляющего кода на выходе 43 сопровождается самим байтом данных на выходе 42 блока 1 выдачи символов. Тактирование блока 64 арбитража выдачи символов осуществляется с входа синхронизации, соединенного с входом 13 синхронизации блока 1 выдачи данных, вход 68 сброса которого соединен с входом сброса блока 64 и предназначен для его инициализации. Информационный выход 42 мультиплексора 67 данных является одноименным выходом блока 1 выдачи данных.

В блоке 2 приема данных дешифратор 82 преобразованного кода (см. фиг.3) кода предназначен для распознавания символов и управляющих кодов сети SpaceWire в соответствии с кодированием, показанном в табл.3, и формирования управляющих сигналов, необходимых для буферизации принимаемых пакетных данных и управляющих кодов, а также изменения состояния блоков 3 управления потоком данных и 4 управления. Информационный вход дешифратора 82 является входом 86 типа символа блока 2 приема данных. Выход 32 подтверждения приема информационного символа дешифратора 82, являющийся одноименным выходом блока 2 приема данных и соединенный с входом разрешения записи буфера 83 приема данных, предназначен для формирования единичного сигнала в одном из двух следующих вариантов: либо при приеме символа данных Nchar, либо при приеме символа конца пакета (ЕОР). Выход 89 селекции управляющего кода дешифратора 82, соединенный с входом разрешения записи буфера 84 приема управляющих кодов, формирует единичный сигнал, подтверждающий прием управляющего кода. Выход 31 подтверждения приема символа управления потоком, являющийся одноименным выходом блока 2 приема данных, предназначен для выдачи признака подтверждения приема символа FCT, необходимого для работы механизма кредитования при управлении потоком данных из данного устройства в удаленное. Выход 127 «Получен NULL» дешифратора 82, являющийся одноименным выходом блока 2 приема данных, формирует единичный сигнал, подтверждающий прием NULL кода.

Буфер 83 приема данных предназначен для промежуточного запоминания принятых пакетов данных, поступающих на его информационный вход с одноименного входа 85 блока 2 приема данных, при наличии единичного сигнала на входе разрешения записи. На выходе 19 принятых данных буфера 83, являющемся одноименным выходом блока 2 приема данных, обеспечивается побайтная выдача пакетов данных, разделенных признаками конца пакета. Выдача данных из буфера 83 приема данных обеспечивается по принципу «первым принят, первым считан» (FIFO) в сопровождении сигнала готовности данных на выходе 18 готовности принятых данных, являющемся одноименным выходом блока 2 приема данных, и при наличии единичного сигнала на входе чтения данных буфера 83, являющегося входом 20 чтения данных блока 2 приема данных. Выход 40 разрешения приема данных буфера 83, являющийся одноименным выходом блока 2 приема данных, свидетельствует о наличии определенного числа свободных ячеек в нем (в описываемом варианте - не менее восьми) и предназначен для управления механизмом кредитования. При записи данных в буфер 83 приема данных тактируется по восходящему фронту синхросигнала с первого входа синхронизации, соединенного с входом 88 локальной синхронизации блока 2 приема данных. При считывании данных буфер 83 тактируется со второго входа синхронизации, соединенного с входом 13 синхронизации блока 2 приема данных, и переводится в начальное состояние по сигналу с входа сброса, соединенного с входом 87 сброса блока 2 приема данных.

Регистр 84 приема управляющего кода предназначен для промежуточного запоминания принятого управляющего кода, поступающего на его информационный вход с информационного входа 85 блока 2 приема данных, при наличии соответствующего единичного сигнала на входе разрешения записи. На выходе 25 принятого управляющего кода регистра 84, являющемся одноименным выходом блока 2 приема данных, обеспечивается выдача управляющего кода. Считывание управляющего кода из регистра 84 обеспечивается в сопровождении единичного сигнала готовности на выходе 24 готовности принятого управляющего кода, являющимся одноименным выходом блока 2 приема данных, и при наличии единичного сигнала на входе чтения управляющего кода регистра 84, являющемся одноименным входом 26 блока 2 приема данных. При записи управляющего кода регистр 84 приема управляющего кода тактируется по восходящему фронту синхросигнала с первого входа синхронизации регистра 84, соединенного с входом 88 локальной синхронизации блока 2 приема данных. При считывании управляющего кода регистр 84 тактируется со второго входа синхронизации, соединенного с входом 13 синхронизации блока 2 приема данных и переводится в начальное состояние по сигналу с входа сброса, соединенного с входом 87 сброса блока 2 приема данных.

В блоке 3 управления потоком данных (см. фиг.4) формирователь 90 запросов кредитования предназначен для выработки сигнала запроса выдачи символа FCT на выходе 33 запроса на выдачу символа управления потоком блока 3 при наличии разрешающих сигналов на входах 96 готовности выдачи символа управления потоком и 94 разрешения приема данных блока 3 и в зависимости от состояния счетчика 91 принятых символов. Вход 94 разрешения приема данных блока 3 является первым входом формирователя 90. Вход 96 готовности выдачи символа управления потоком блока 3 является вторым входом формирователя 90. Выход 100 состояния счетчика 91 принятых символов соединен с третьим входом формирователя 90. Вход 13 синхронизации блока 3, соединенный с входами синхронизации формирователя 90 запросов кредитования, счетчика 91 принятых символов, счетчика 92 переданных символов и детектора 93 ошибки кредитования, обеспечивает синхронизацию их работы на частоте системного интерфейса. Вход 95 сброса блока 3 предназначен для установки начального состояния и соединен с входами сброса формирователя 90 запросов кредитования, счетчика 91 принятых символов, счетчика 92 переданных символов и детектора 93 ошибки кредитования. Счетчик 91 принятых символов обеспечивает формирование двоичного кода, определяющего число информационных символов, которые разрешается принять в данном устройстве. Первый управляющий вход счетчика 91, соединенный с выходом формирователя 90 запросов кредитования, предназначен для увеличения состояния счетчика 91 на восемь при выдаче сигнала запроса на выдачу символа управления потоком. Второй управляющий вход счетчика 91, являющийся входом 97 подтверждения приема информационного символа блока 3, предназначен для уменьшения на единицу содержимого счетчика 91 при принятии каждого информационного символа. Изменение состояния счетчика 91 принятых символов под воздействием управляющих сигналов осуществляется по фронту синхросигналов, поступающих с входа 13 синхронизации блока 3 на вход синхронизации счетчика 91. Выход ошибки кредита приема счетчика 91 соединен с первым информационным входом детектора 93 ошибки кредитования и предназначен для формирования сигнала ошибки при попытке уменьшения состояния счетчика ниже предельно допустимого значения. Счетчик 92 переданных символов обеспечивает формирование двоичного кода, определяющего число информационных символов, которые разрешается передать из данного устройства. Первый управляющий вход счетчика 92, являющийся входом 98 подтверждения приема символа управления потоком блока 3, предназначен для увеличения состояния счетчика 92 на восемь при приеме каждого символа FCT. Второй управляющий вход счетчика 92, являющийся входом 99 подтверждения выдачи информационного символа блока 3, предназначен для уменьшения на единицу содержимого счетчика 92 переданных символов. Изменение состояния счетчика 92 переданных символов при подаче управляющих сигналов осуществляется по фронту синхросигналов, поступающих с входа 13 синхронизации блока 3 на вход синхронизации счетчика 92. Выход ошибки кредита выдачи счетчика 92 соединен со вторым информационным входом детектора 93 ошибки кредитования и предназначен для формирования сигнала ошибки при попытке увеличения состояния счетчика 92 выше предельно допустимого значения. Детектор 93 ошибки кредитования обеспечивает формирование объединенного тактируемого сигнала ошибки кредитования на своем выходе, являющемся выходом 26 ошибки кредитования блока. Вход синхронизации детектора 93 соединен с входом 13 синхронизации блока 3 управления потоком данных.

В блоке 4 управления (см. фиг.5), реализующем машину состояний, регистр 103 состояния предназначен для оперативного запоминания и контроля состояния фаз работы устройства. Фактически регистр 103 состояния является памятью машины состояний, которая реализуется блоком 4 управления. Регистр 103 может быть доступен как на чтение, так и на запись для хост-системы (на фиг.5 не показано). Заполнение регистра выполняется побитно по сигналам от блока 2 приема данных или процессора хост-системы. Выход 114 состояния регистра 103 соединен с первым управляющим входом блока 104 формирования нового состояния и с управляющим входом формирователя 105 управляющих сигналов. Выход 27 установления соединения регистра 103 состояния является одноименным выходом блока 4 управления. Единичное значение сигнала на этом выходе свидетельствует о наличии соединения на уровне обмена стандарта SpaceWire. Выход 28 ошибки рассоединения регистра 103 состояния является одноименным выходом блока 4 управления. Единичное значение сигнала на этом выходе свидетельствует о наличии ошибки соединения при обмене данными между удаленными устройствами. Выход 28 ошибки кредитования регистра 103 состояния является одноименным выходом блока 4 управления. Единичное значение сигнала на этом выходе свидетельствует о наличии ошибки кредита при обмене данными между удаленными устройствами. Вход 14 сброса блока 4 управления предназначен для установки начального состояния и соединен с входами сброса регистра 103 состояния, формирователя 105 управляющих сигналов и блока 106 задержки. Запись битов состояния в регистр 103 обеспечивается по восходящему фронту тактового сигнала на его входе синхронизации, являющемся входом 13 синхронизации блока 4 управления.

Блок 104 формирования нового состояния предназначен для реализации логики машины состояний, выполняющей функцию автомата, переходящего под воздействием входных сигналов в различные состояния. Формирователь 105 управляющих сигналов обеспечивает выработку управляющих сигналов, с помощью которых машина состояний переводит блок 1 выдачи данных, блок 2 приема данных, и блок 3 управления потоком данных в исходные состояния, позволяя таким образом обеспечить корректную работу устройства в целом. Блок 106 задержки предназначен для формирования тайм-аутов, необходимых для правильного функционирования машины состояний при установлении и поддержании соединения с удаленной стороной через коммуникационный интерфейс. Из показанной на фиг.16 примерной реализации графа машины состояний видна необходимость в реализации двух тайм-аутов Т1 и Т2. В реализованном макете устройства величины тайм-аутов выбраны в соответствии с требованиями стандарта SpaceWire: T1=6,4 мкс, Т2=12,8 мкс. Вход 113 локальной синхронизации блока 4 управления соединен с входами синхронизации формирователя 105 управляющих сигналов и блока 106 задержки. Вход 107 установления соединения блока 4 управления является первым входом блока 104 формирования нового состояния. Вход 108 ошибки кредитования блока 4 является вторым входом блока 104. Вход 109 ошибки рассоединения блока 4 является третьим входом блока 104. Вход 110 ошибки кодировки символа блока 4 является четвертым входом блока 104. Вход 111 подтверждения приема символа управления потоком блока 4 является пятым входом блока 104. Вход 112 подтверждения приема информационного символа блока 4 является шестым входом блока 104. Вход 178 «Получен NULL» является седьмым входом блока 104 формирования нового состояния, выход 115 которого соединен с входом записи битов состояния регистра 103 состояния. Управляющий выход 116 формирователя 105 управляющих сигналов соединен с входом управления блока 106 задержки, выход которого соединен с вторым управляющим входом блока 104 формирования нового состояния. Выход 38 разрешения передачи символа управления потоком формирователя 105 управляющих сигналов является одноименным выходом блока 4 управления. Первый выход 34 сброса формирователя 105 является одноименным выходом блока 4 управления. Второй выход 35 сброса формирователя 82 является одноименным выходом блока 4 управления. Третий выход 36 сброса формирователя 82 является одноименным выходом блока 4 управления.

В преобразователе 5 передаваемых символов (см. фиг.6) регистр 117 выходных данных предназначен для фиксации байта пакетных данных или управляющего кода в течение такта для его преобразования в код символа формата 8b. Вход данных регистра 117 является входом 128 данных преобразователя 5 передаваемых символов. Запись данных в регистр 117 осуществляется по возрастающему фронту тактового сигнала на его входе синхронизации, который соединен с входами синхронизации первого регистра 118 типа символа, первого триггера 120 управляющего кода, со счетным входом первого счетчика 123 и является входом 130 локальной синхронизации преобразователя 5 передаваемых символов. Вход 131 сброса преобразователя 5 соединен с входами сброса регистра 117 выходных данных, первого регистра 118 типа символа, первого триггера 120 управляющего кода и первого счетчика 123 и обеспечивает подачу единичного сигнала для перевода их в нулевое состояние. Выход 133 регистра 117 соединен с первым информационным входом выходного мультиплексора 122. Первый регистр 118 типа символа предназначен для фиксации в текущем такте кода типа символа SpaceWire. Вход данных первого регистра 118 типа символа является входом 129 типа символа преобразователя 5 передаваемых символов. Выход 132 первого регистра 118 типа символа соединен с входом селектора 119 управляющего кода и с первым входом первого ПЗУ 121 констант.

Селектор 119 управляющего кода обеспечивает селекцию управляющего кода из поступающего на его вход типа символа SpaceWire, формируя единичный сигнал на выходе 134. Выход 134 селекции управляющего кода селектора 119 соединен с первым входом третьего элемента 126 И, выход 136 установки флага которого соединен с входом данных триггера 120 управляющего кода и обеспечивает перевод триггера 120 из нулевого состояния в единичное по восходящему фронту тактового сигнала локальной синхронизации.

Триггер 120 управляющего кода предназначен для формирования бита флага управляющего кода (УК) путем фиксации на один такт признака управляющего кода. Это необходимо потому, что преобразование управляющего кода в символы формата 8b занимает два такта. Прямой выход 137 триггера 120 управляющего кода соединен с третьим входом первого ПЗУ 121 констант, с первым входом первого элемента 124 И, а также с первым инверсным входом второго элемента 125 И. Инверсный выход 135 триггера 120 соединен со вторым входом третьего элемента 126 И. Нулевое значение на инверсном выходе триггера 120 и соответственно на выходе 136 третьего элемента 127 И обеспечивает возврат триггера 120 в исходное нулевое состояние по восходящему фронту следующего тактового сигнала.

Первое ПЗУ 121 констант обеспечивает хранение кодов специальных символов управления, определяемых кодированием символов 8b. Выход 140 кода спецсимвола ПЗУ 121 соединен со вторым информационным входом выходного мультиплексора 122 и обеспечивает передачу восьмиразрядных констант, определяющих при кодировании символов 8b специальные символы управления, которые используются в данном техническом решении для кодирования управляющих символов SpaceWire и управляющих кодов различных типов. К таким управляющим символам будем относить символы ЕОР, ЕЕР, FCT и NULL, используемые для управления потоком данных и их форматирования. При генерации спецсимвола в преобразователе 5 байт данных через регистр 117 не передается. Выход 45 признака спецсимвола первого ПЗУ 121 констант соединен с управляющим входом выходного мультиплексора 122 и является одноименным выходом преобразователя 5 передаваемых символов. Единичное значение на выходе 45 первого ПЗУ 121 констант указывает на то, что считываемый при этом с выхода 140 ПЗУ 121 один из специальных символов управления (спецсимволов) должен выдаваться с выхода 46 мультиплексора 122. Правила формирования кодов спецсимволов на выходах первого ПЗУ 121 констант показаны в табл.3.

Выходной мультиплексор 122 предназначен для выбора типа символа 8b, передаваемого на его выход, являющийся выходом 46 данных символа 8b преобразователя 5 передаваемых символов, в зависимости от значения признака спецсимвола на управляющем входе. При нулевом значении признака спецсимвола на выход 46 мультиплексора 122 выдается байт данных с первого информационного входа мультиплексора 122 из регистра 117 выходных данных. При единичном значении признака спецсимвола на выход 46 мультиплексора 122 выдается со второго информационного входа код спецсимвола 8b из первого ПЗУ 121 констант.

Первый счетчик 123 предназначен для определения временного интервала ТЗ, через который преобразователем 5 передаваемых символов для поддержания состояния соединения между устройствами должен генерироваться специальный символ управления - символ поддержки связи (согласно табл.4 для его реализации из 12 предусмотренных кодированием спецсимволов 8b используются К28.5). Разрядность первого счетчика 123 выбрана равной пяти, поэтому интервал ТЗ равен 32 тактам локальной синхронизации. Выход 139 переноса первого счетчика 123 соединен со вторым входом первого ПЗУ 121 констант, с вторым инверсным входом второго элемента 125 И, со вторым входом первого элемента 124 И и обеспечивает формирование единичного сигнала через каждые 32 периода синхросигнала при нулевом состоянии его разрядов. Первый элемент 124 И обеспечивает формирование единичного сигнала на своем выходе 138 запрета счета в случае совпадения сигнала переноса и флага управляющего кода в одном такте. Выход 138 запрета счета первого элемента 124 И соединен с инверсным входом сброса первого счетчика 123. При единичном значении сигнала запрета счета счетчик 123 сбрасывается в нуль на второй дополнительный такт. Второй элемент 125 И обеспечивает формирование единичного значения сигнала готовности выдачи символа только в случае отсутствия сигнала переноса и флага управляющего кода. Выход 44 готовности выдачи символа второго элемента 125 И является одноименным выходом преобразователя 5 передаваемых символов.

В блоке 7 передачи битов (см. фиг.7) генератор 141 синхросигналов передачи битов обеспечивает формирование базовой синхропоследовательности с частотой, выбранной равной 1 ГГц. Выход генератора 141 соединен с входом первого делителя 142 частоты и с входом синхронизации выходного сдвигового регистра 143. Первый делитель 142 частоты предназначен для формирования тактовых сигналов локальной синхронизации и соединен с входом записи выходного сдвигового регистра 143 и является выходом 48 локальной синхронизации блока 7 передачи битов. Частота тактовых сигналов локальной синхронизации выбрана равной 100 МГц. Выходной сдвиговый регистр 143 предназначен для преобразования параллельного кода десятиразрядного символа в последовательный. Последовательный выход выходного сдвигового регистра 143 соединен с выходным формирователем 144 битового сигнала, обеспечивающего выработку битового сигнал в требуемом виде для передачи в коммуникационный канал.