Изобретение относится к области вычислительной техники и может использоваться в высокопроизводительных системах обработки больших массивов данных, передаваемых по высокоскоростным каналам передачи (приема), в том числе и в режиме реального времени.

Известна параллельная вычислительная система с программируемой архитектурой, включающая параллельный процессор, который содержит матрицу процессорных элементов, и ОЗУ, дополнительно снабженная первой коммуникационной средой и N параллельными процессорами, причем каждый параллельный процессор дополнительно содержит управляющий процессор, системную шину, служебное ОЗУ, буферное ОЗУ и узел загрузки, первая группа входов-выходов которого соединена с первой коммуникационной средой, при этом вторая группа входов-выходов узла загрузки соединена с группой информационных входов-выходов буферного ОЗУ, группа управляющих входов которого соединена с первой группой управляющих выходов узла загрузки, третья группа входов-выходов которого соединена с группой информационных входов-выходов служебного ОЗУ, группа управляющих входов которого соединена со второй группой управляющих выходов узла загрузки, четвертая группа входов-выходов которого соединена с группой информационных входов-выходов ОЗУ, группа управляющих входов которого соединена с третьей группой управляющих выходов узла загрузки, первая группа выходов которого связана с группой информационных входов матрицы процессорных элементов, группа информационных выходов которой связана с группой входов блока загрузки, группа управляющих выходов которого связана с группой управляющих входов матрицы процессорных элементов, группа управляющих выходов которой связана с группой управляющих входов блока загрузки, пятая группа входов-выходов которого соединена с системной шиной, которая также соединяется с группой входов-выходов управляющего процессора. [1]

Существенным недостатком такой системы является жесткая взаимосвязь между собой отдельных параллельных процессоров, что при решении многих задач обусловливает низкую производительность системы в целом, особенно в случае отказов в работе некоторых процессоров, а также затрудняет наращивание производительности системы путем подключения дополнительных блоков. Кроме того, большое число параллельных процессоров, работающих с одним блоком управления, снижает эффективность их использования. Стоит отметить также, что параллельные процессоры неэффективны для задач, при решении которых требуется жестко последовательное выполнение, друг за другом, отдельных модулей и команд программы, реализующих отдельные части задачи.

Увеличение же числа параллельных процессоров наряду с введением в состав каждого параллельного процессора управляющего процессора, введение в состав системы вычислительных узлов, состоящих из процессоров другого типа (последовательных), объединенных одной или несколькими коммуникационными средами, позволяет наиболее быстро и эффективно выполнять сложные программы.

Наиболее близкой к описываемому изобретению (прототип) является система Т2-РМС с качественной мультиобработкой, масштабируемостью и скоростной пропускной способностью ввода-вывода [2], содержащая четыре процессора Analog Devices ADSP-TS20/S Tiger SHARC DSPs, ОЗУ, ПЗУ, контроллер ввода-вывода, который обеспечивает прием и передачу данных с внешними устройствами через LINK0 и LINK1 порты и обработку прерываний, контроллер шины PCI, отладчик Jtag, группа входов-выходов которого соединена с группами входов-выходов контроллера ввода-вывода, первого, второго, третьего и четвертого процессоров, связанных между собой контроллер шины PCI, отладчик Jtag, группа входов-выходов которого соединена с группами входов-выходов контроллера ввода-вывода, первого, второго, третьего и четвертого процессоров, связанных между собой двунаправленной 64 разрядной cluster шиной, которая соединена с ОЗУ и контроллером PCI, 8-разрядная периферийная шина которого соединена с ПЗУ и контроллером ввода-вывода, четыре двунаправленных LINK0 порта соединены с двунаправленными LINK0 портами четырех процессоров, двунаправленные LINK1 порты которых соединены с четырьмя двунаправленными LINK1 портами контроллера ввода-вывода, группа входов-выходов прерываний и флагов которого соединена с первой группой входов-выходов четырех процессоров, вторая группа входов-выходов прерываний и флагов которых соединена с контроллером PCI, 64-разрядная шина PCI которого является 64-разрядной шиной PCI системы Т2-РМС, шина расширения РМС которой соединена с шиной РМС контроллера ввода-вывода, причем двунаправленный LINK2 порт первого процессора соединен с двунаправленным LINK3 портом четвертого процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом третьего процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом второго процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом первого процессора.

Недостатком такой системы является низкое быстродействие за счет обращения четырех процессоров к одной памяти ОЗУ, жесткая взаимосвязь между собой отдельных параллельных процессоров, обусловливает низкую производительность системы в целом, особенно в случае отказов некоторых процессоров. Связь между процессорами полудуплексная с необходимостью согласования направления передачи данных.

Задачей изобретения является повышение быстродействия за счет введения ОЗУ каждому процессору, прием и передача данных (дуплексный режим) по высокоскоростным каналам приема и передачи, организация высоких скоростей передачи данных между процессорами, высококачественная обработка принятых данных, устойчивая к отказам и сбоям в системе передачи данных в реальном времени.

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1-55, где:

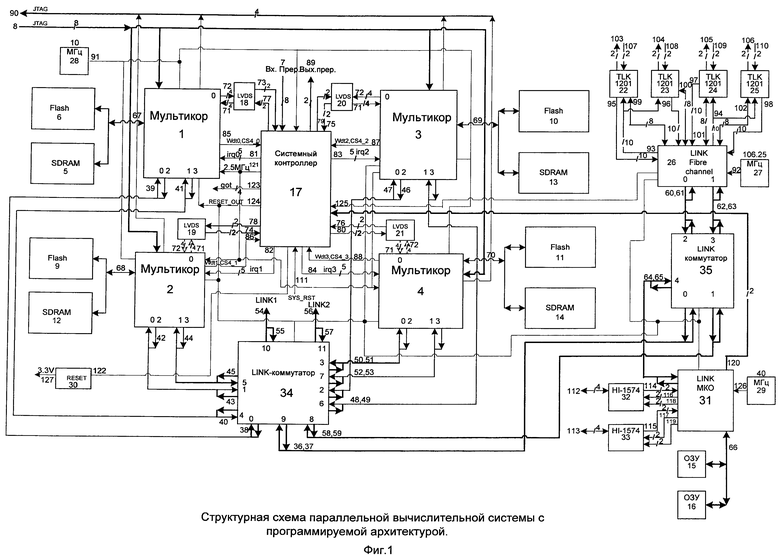

- на фиг.1 представлена структурная схема параллельной вычислительной системы с программируемой архитектурой (далее по тексту ПВС);

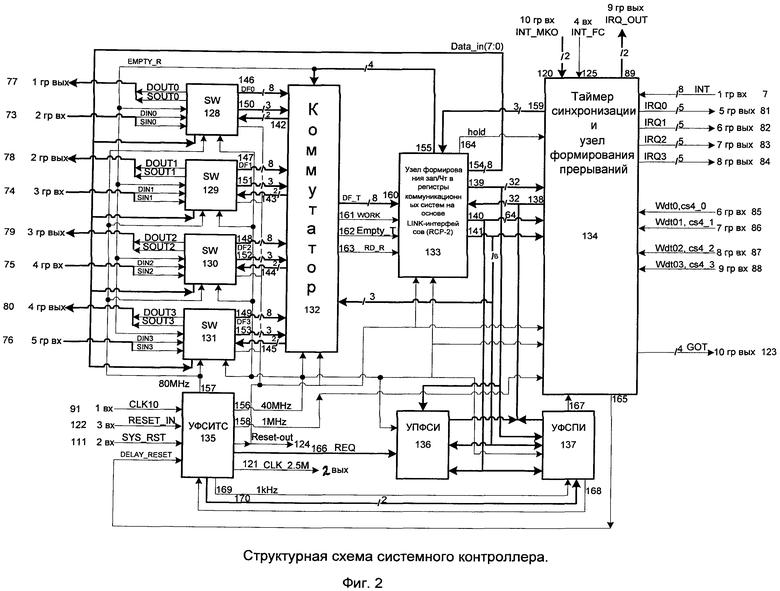

- на фиг.2 представлена структурная схема системного контроллера;

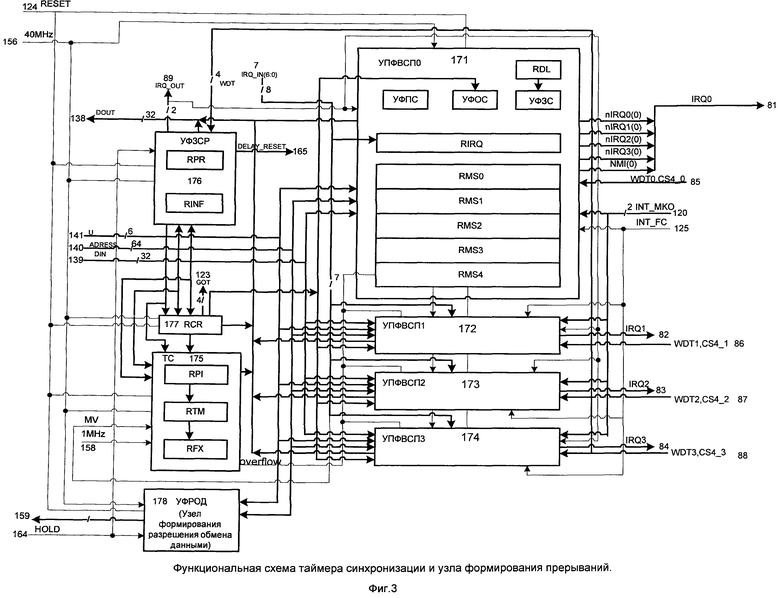

- на фиг.3 представлена функциональная схема таймера синхронизации и узла формирования прерываний;

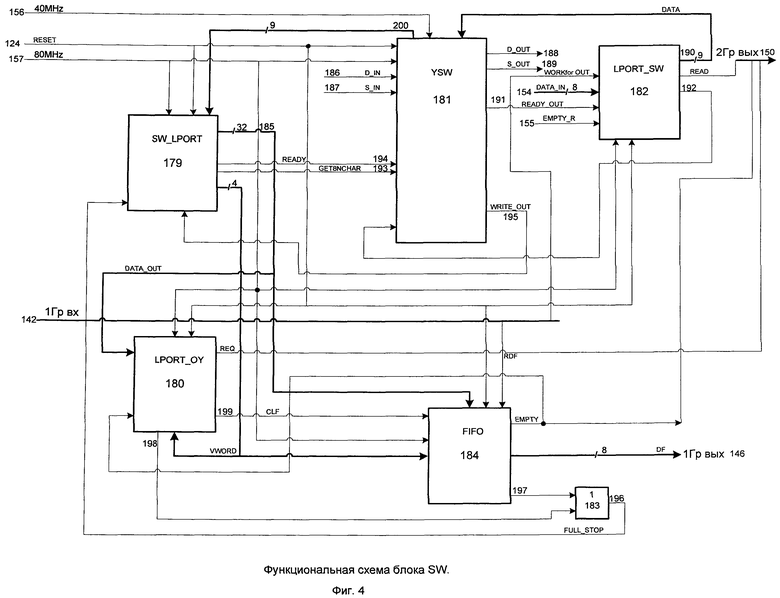

- на фиг.4 представлена функциональная схема блока SW;

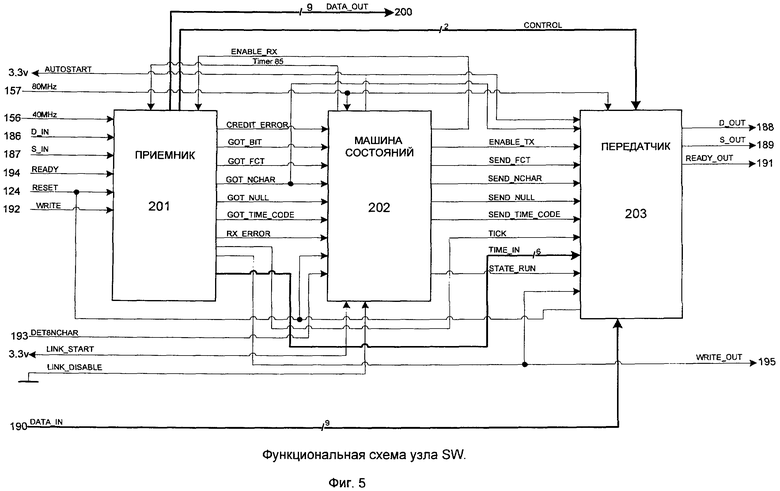

- на фиг.5 представлена функциональная схема узла SW;

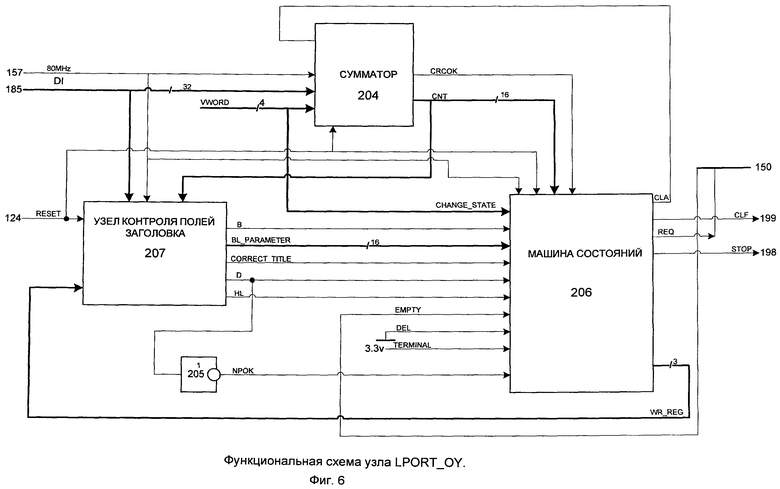

- на фиг.6 представлена функциональная схема LPORT_OY;

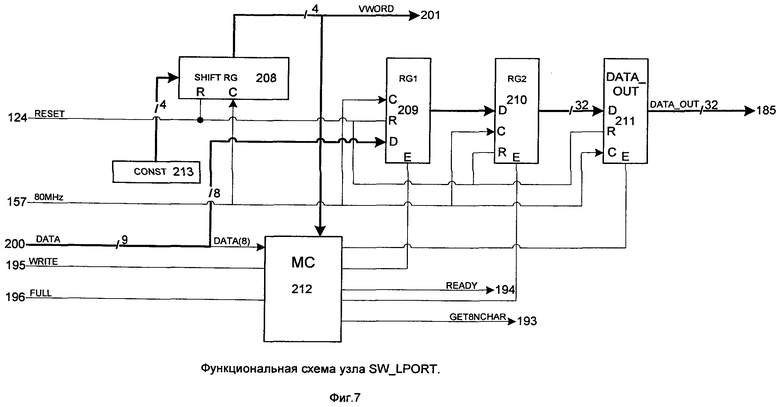

- на фиг.7 представлена функциональная схема узла SW_LPORT;

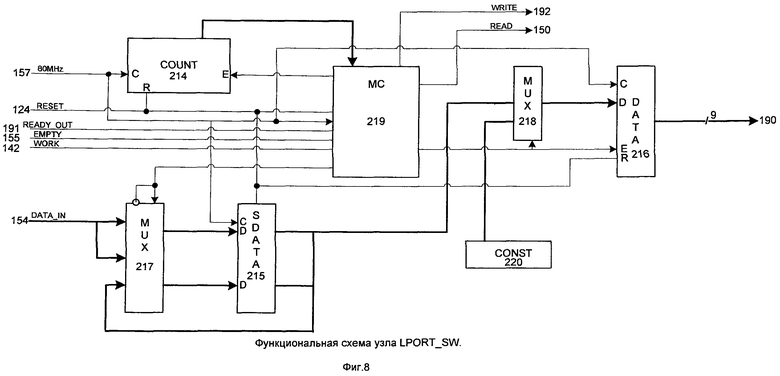

- на фиг.8 представлена функциональная схема узла LPORT_SW;

- на фиг.9 представлена функциональная схема узла формирования сигнала программной инициализации;

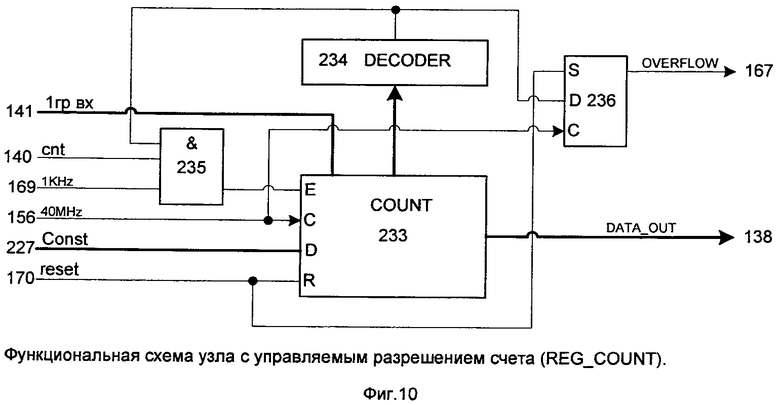

- на фиг.10 представлена функциональная схема узла с управляемым разрешением счета (REG_COUNT);

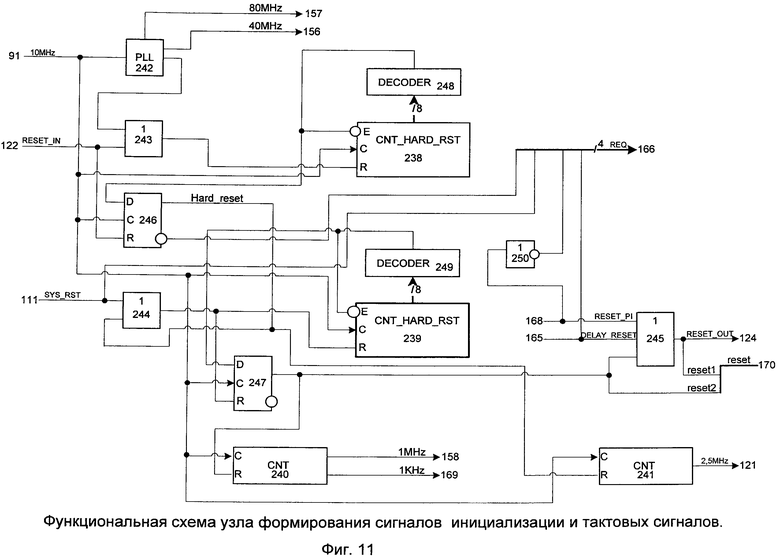

- на фиг.11 представлена функциональная схема узла формирования сигналов инициализации и тактовых сигналов;

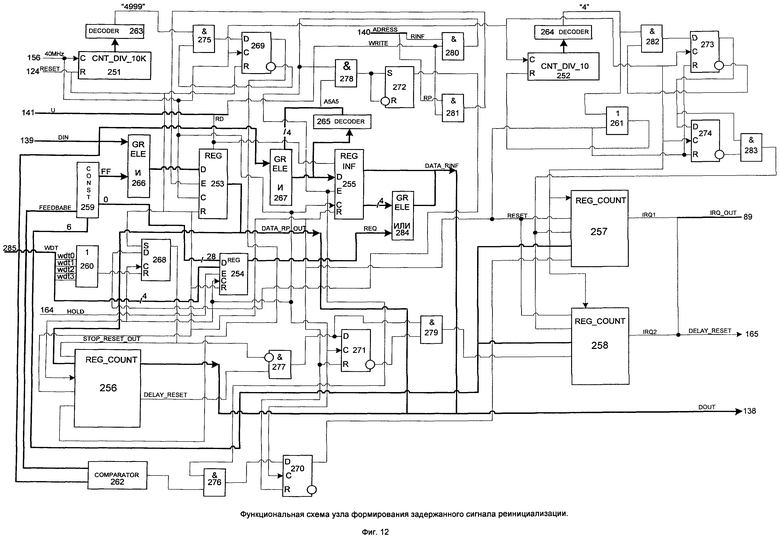

- на фиг.12 представлена функциональная схема узла формирования задержанного сигнала реинициализации;

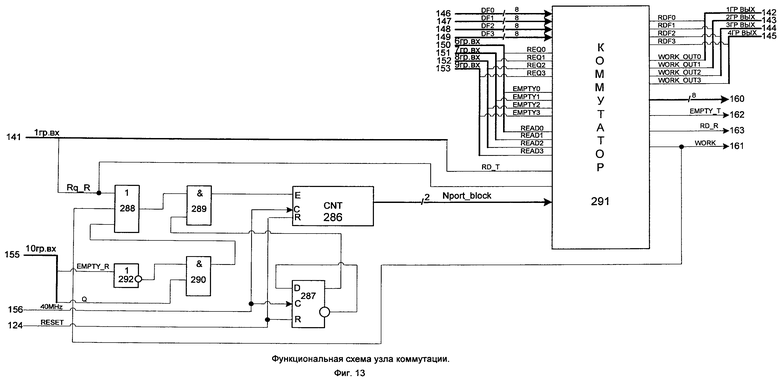

- на фиг.13 представлена функциональная схема узла коммутации;

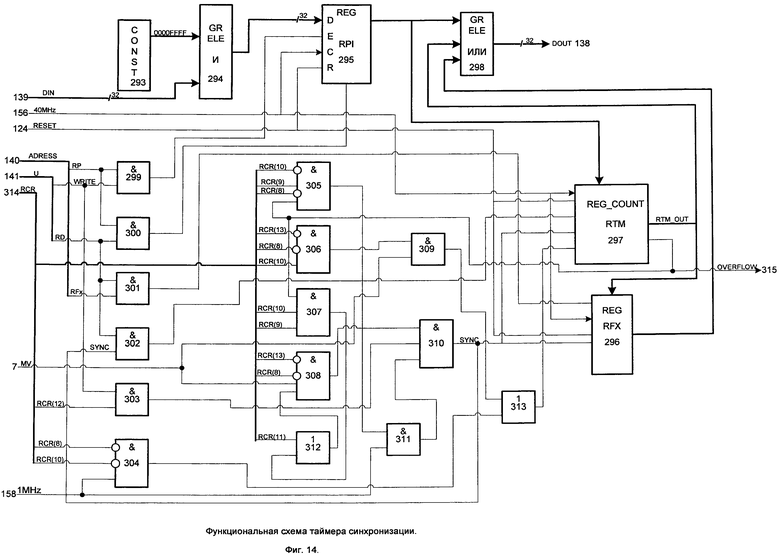

- на фиг.14 представлена функциональная схема таймера синхронизации;

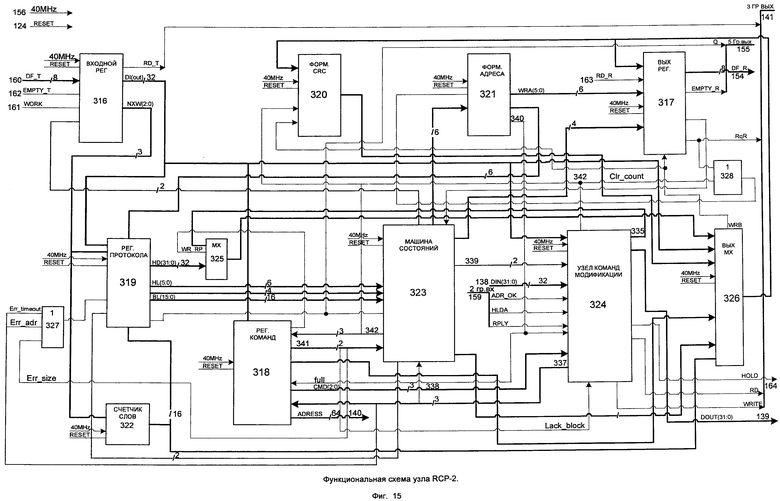

- на фиг.15 представлена функциональная схема узла RCP-2;

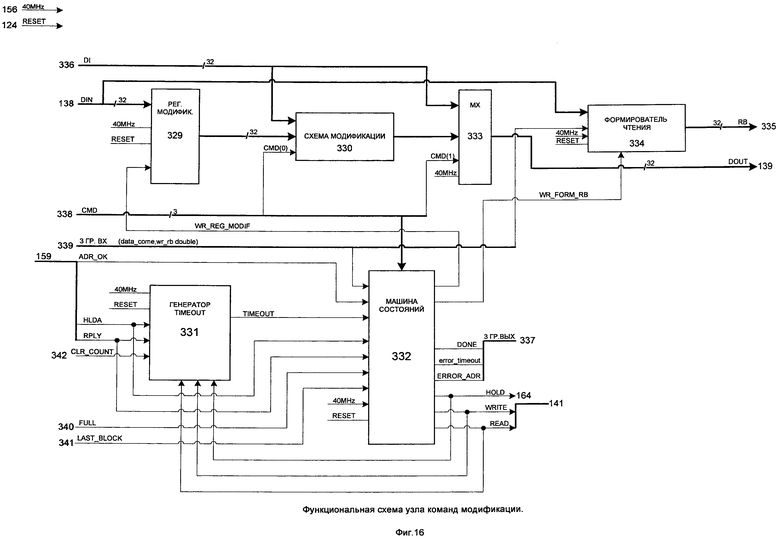

- на фиг.16 представлена функциональная схема узла команд модификации.;

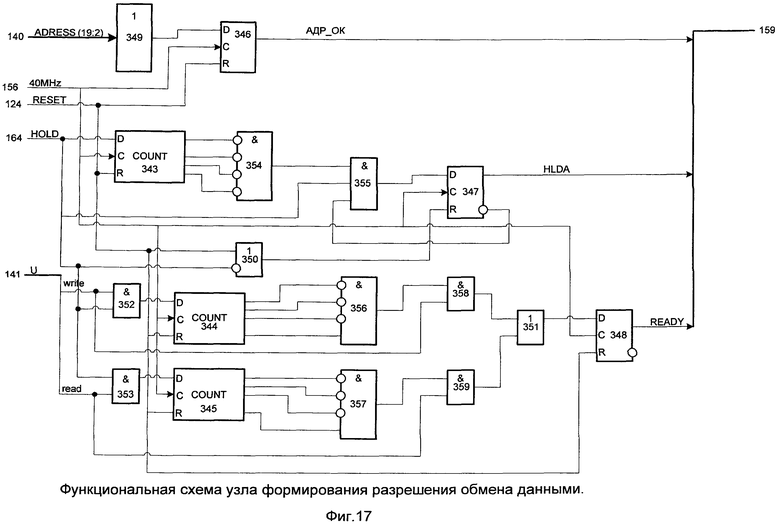

- на фиг.17 представлена функциональная схема узла формирования разрешения обмена данными;

- на фиг.18 представлен алгоритм работы машины состояний узла SW;

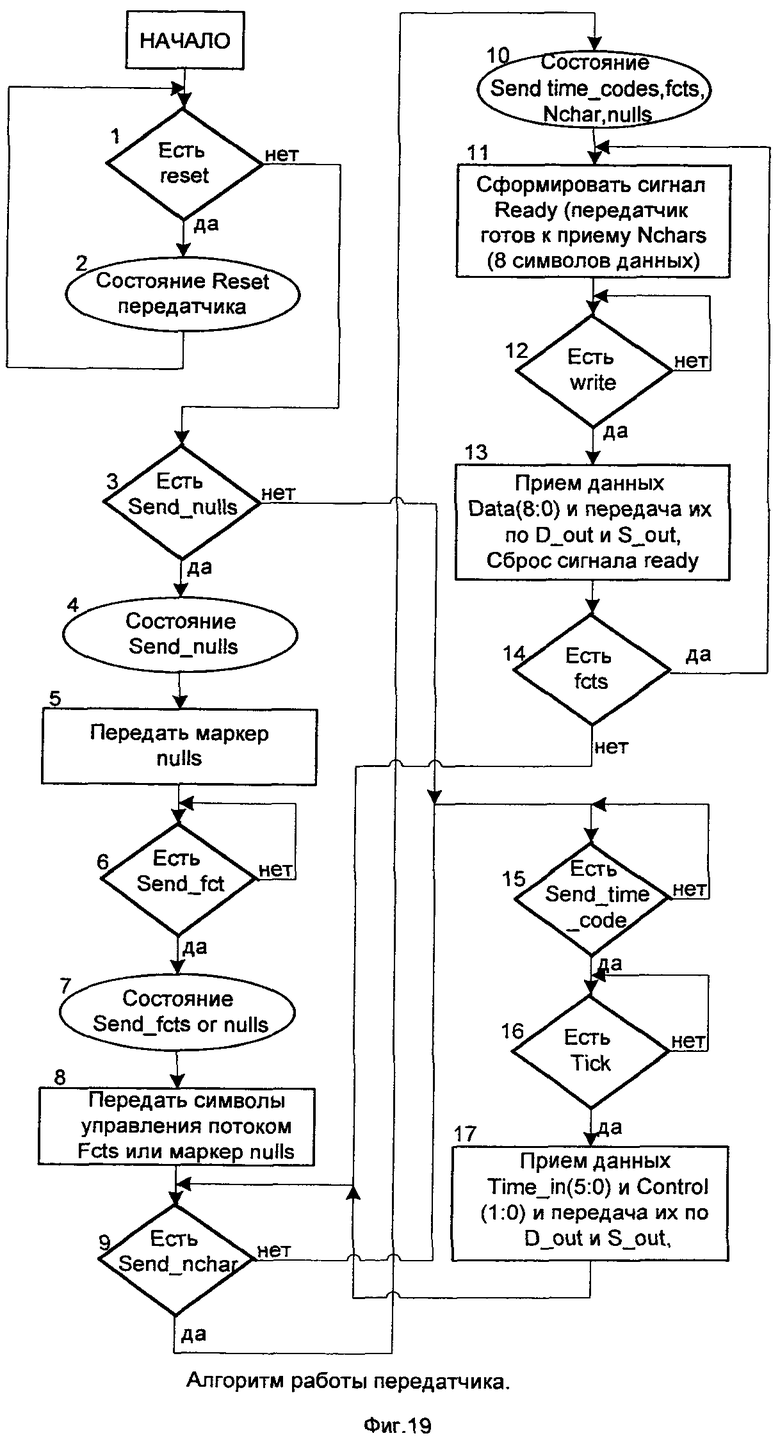

- на фиг.19 представлен алгоритм работы передатчика;

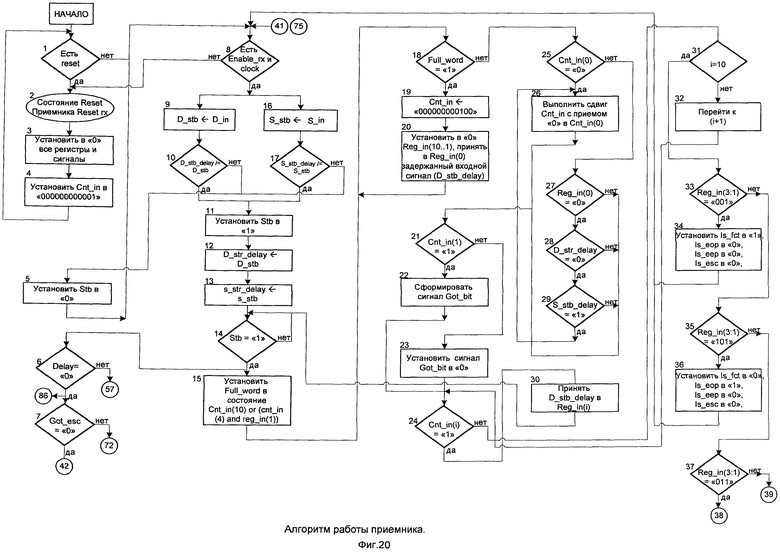

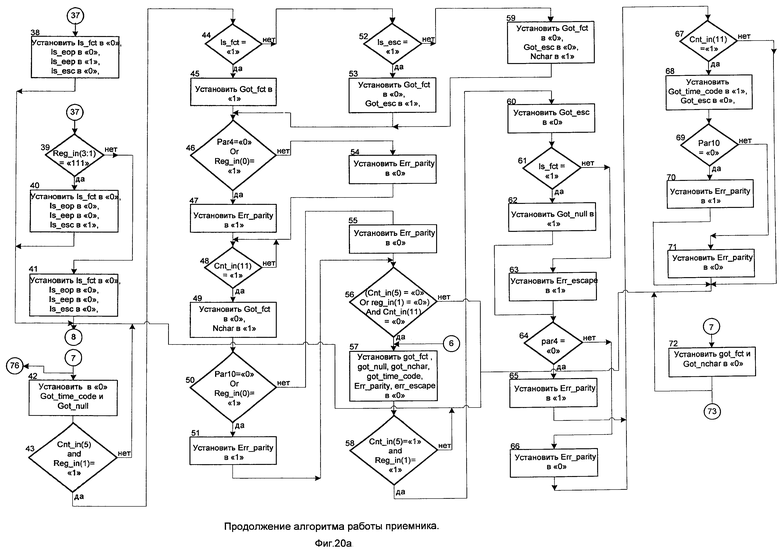

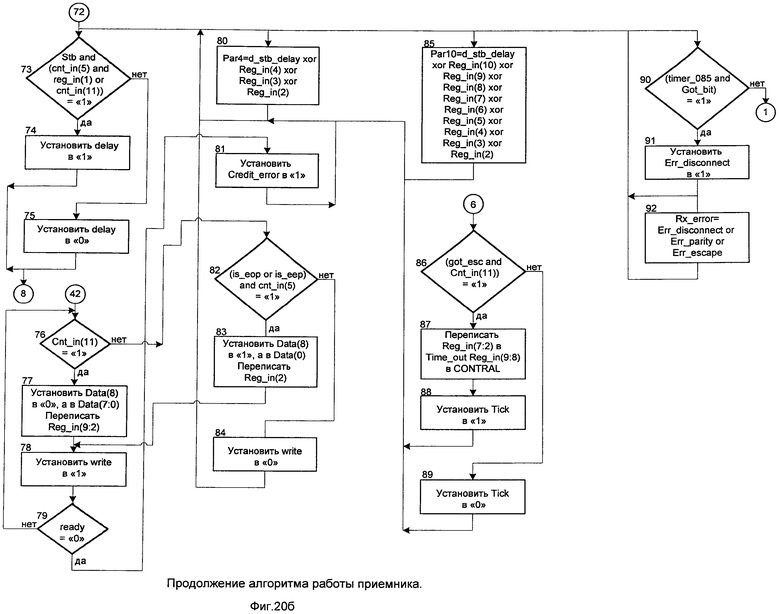

- на фиг.20, 20а, 20б представлен алгоритм работы приемника;

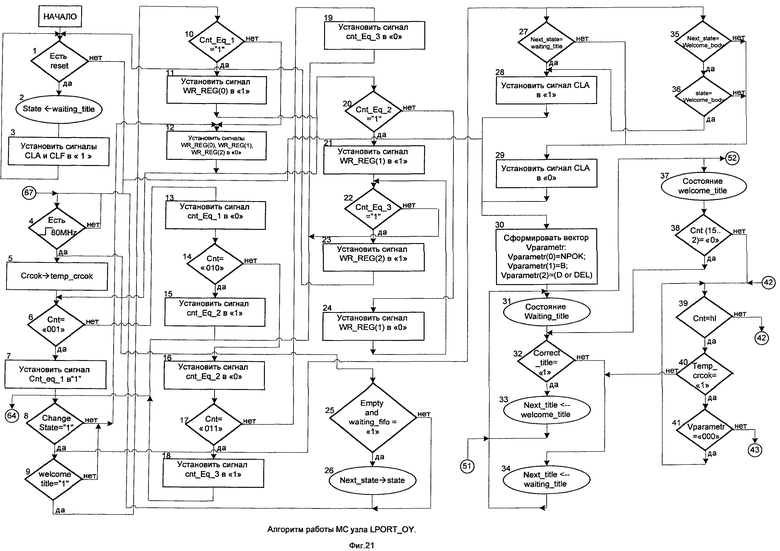

- на фиг.21, 21а представлен алгоритм работы МС узла LPORT_OY;

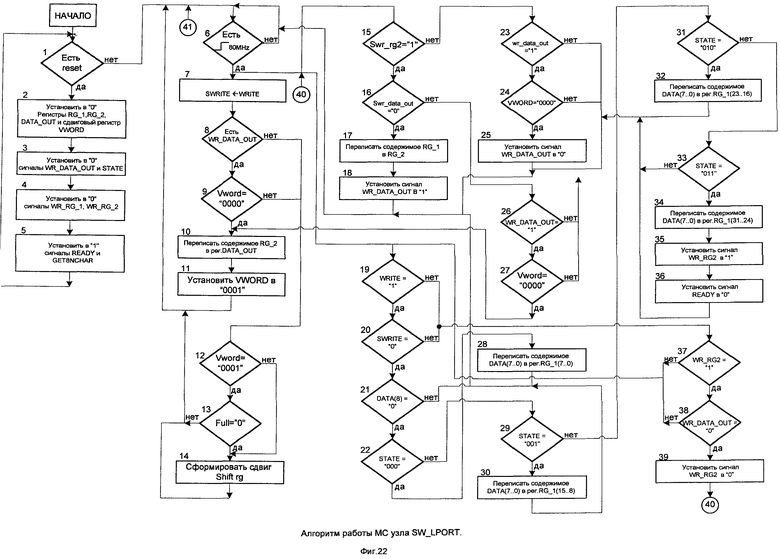

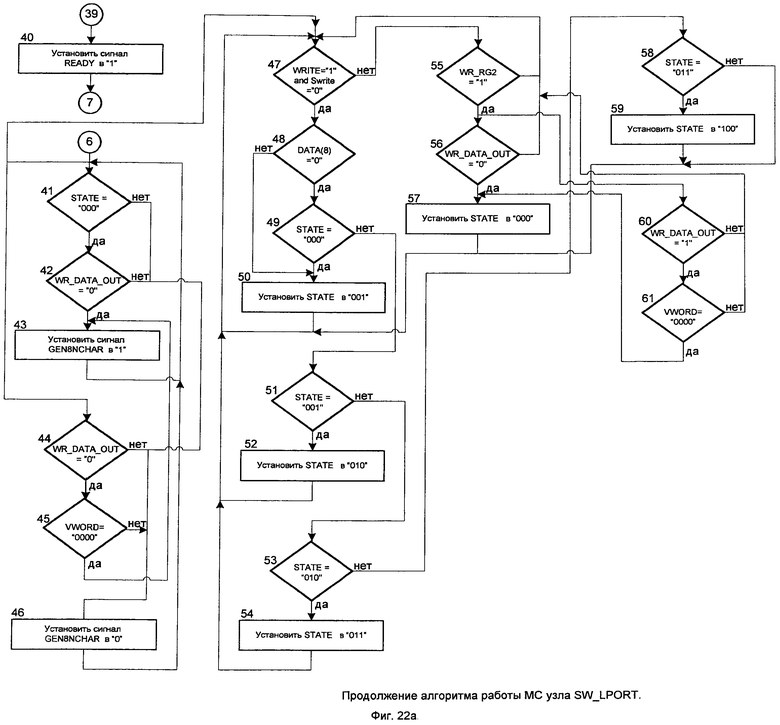

- на фиг.22,22а представлен алгоритм работы МС узла SWJ-PORT;

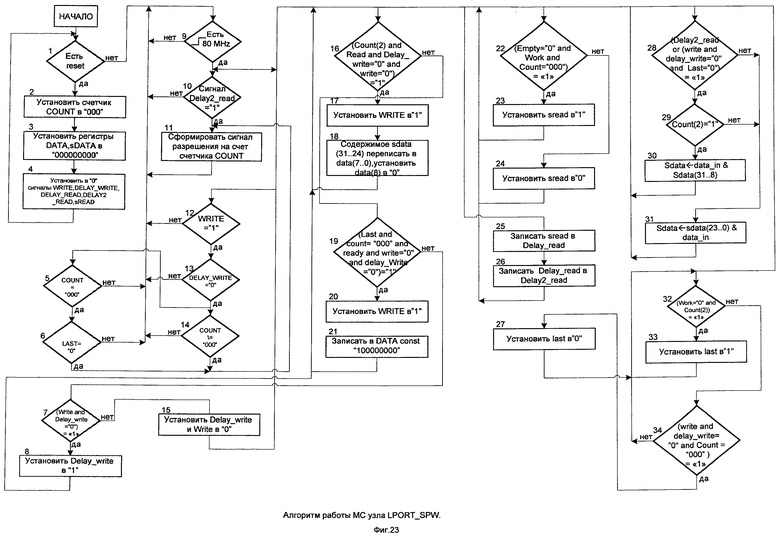

- на фиг.23 представлен алгоритм работы МС узла LPORT_SPW;

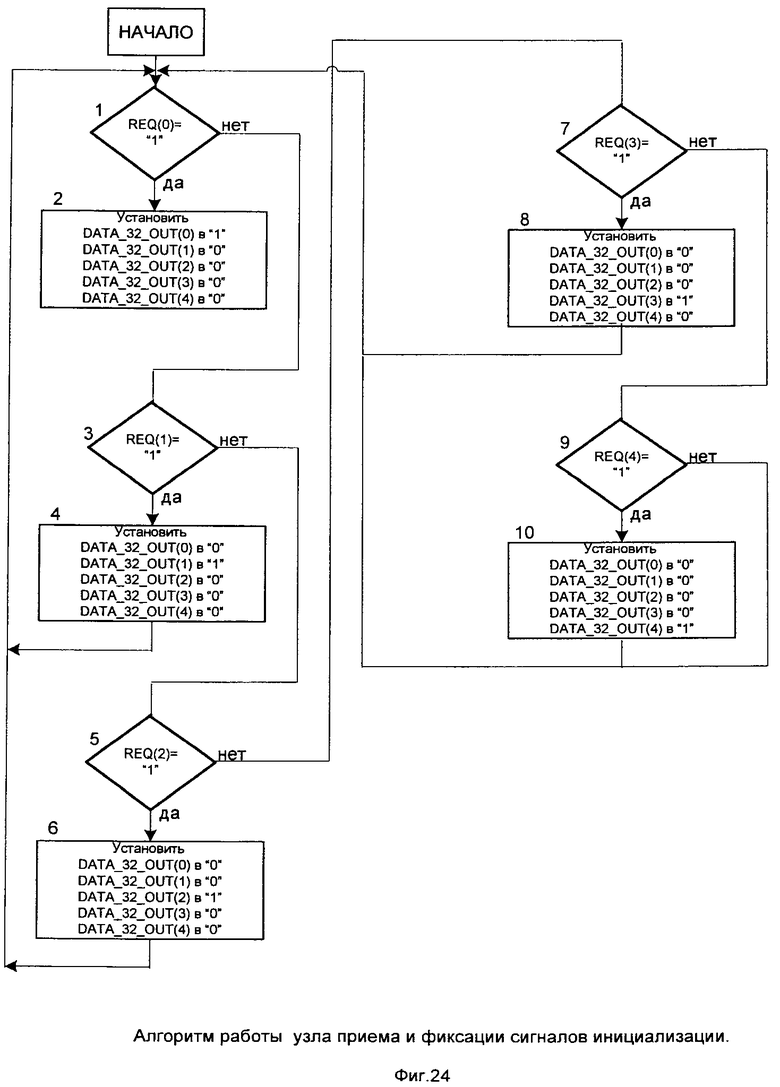

- на фиг.24 представлен алгоритм работы узла приема и фиксации сигналов инициализации;

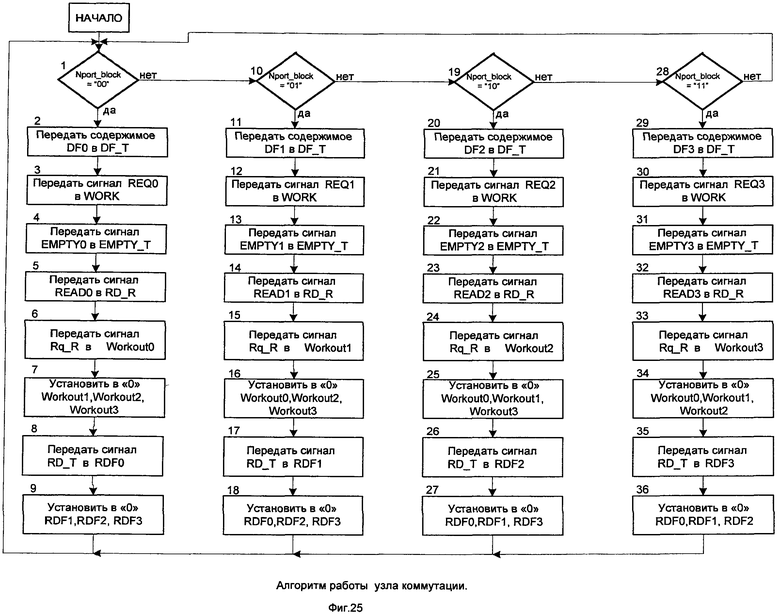

- на фиг.25 представлен алгоритм работы узла коммутации;

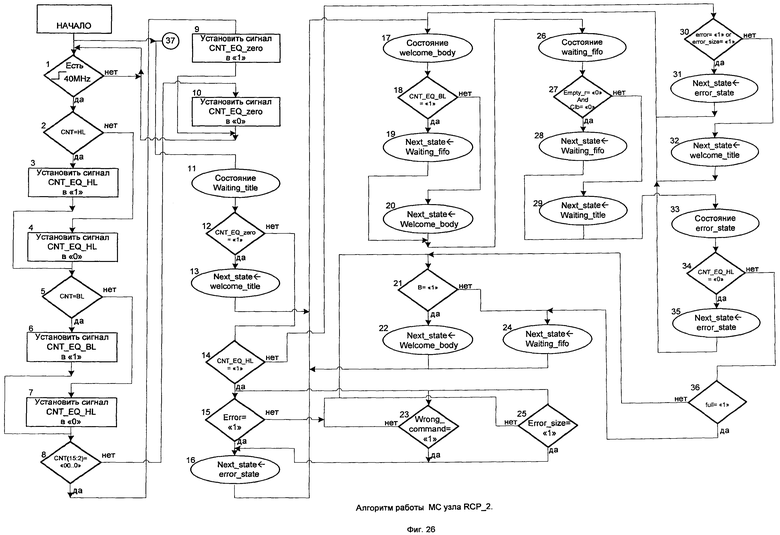

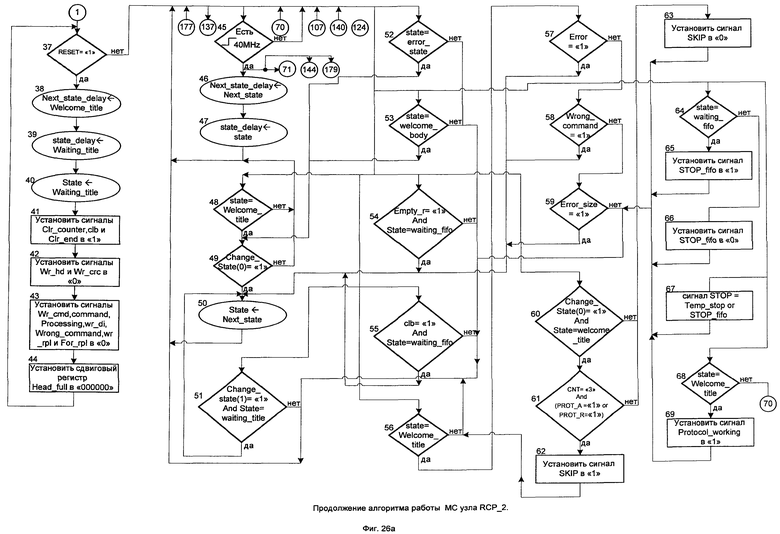

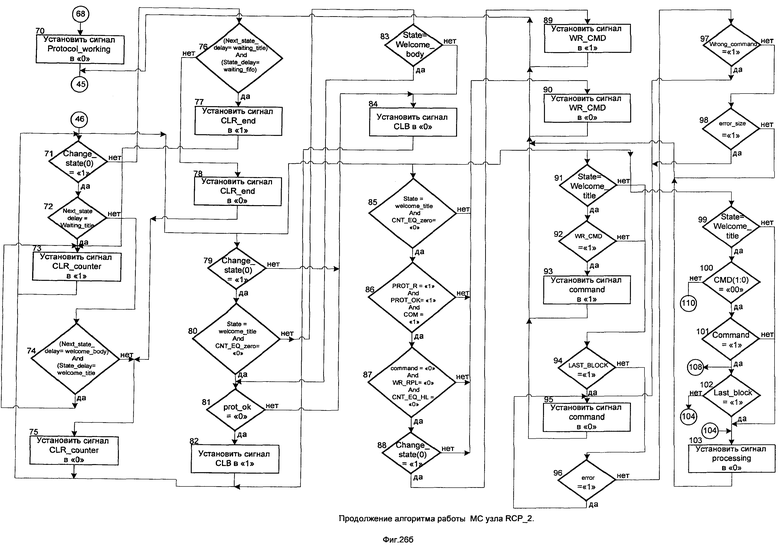

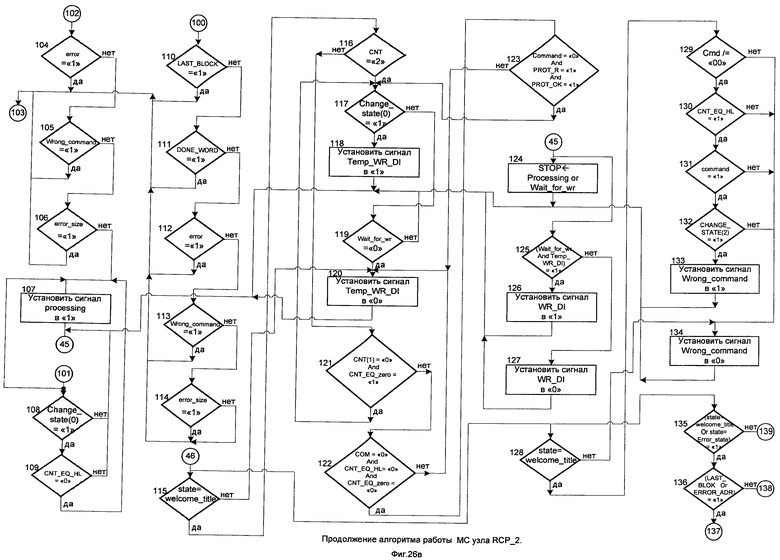

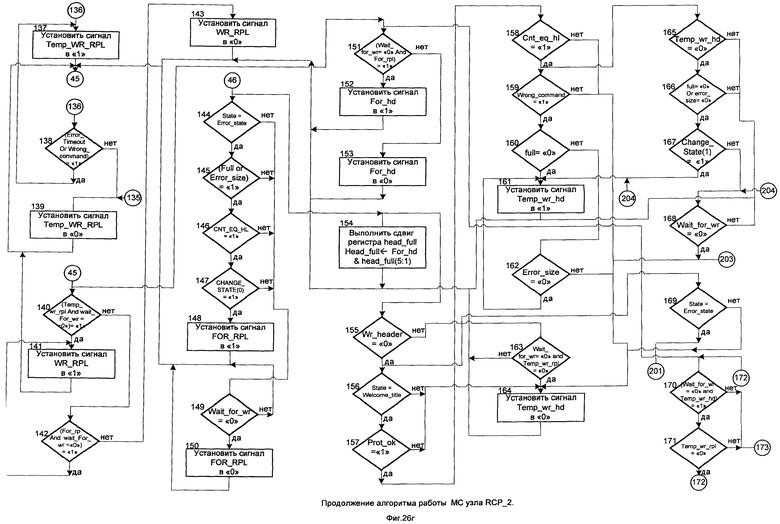

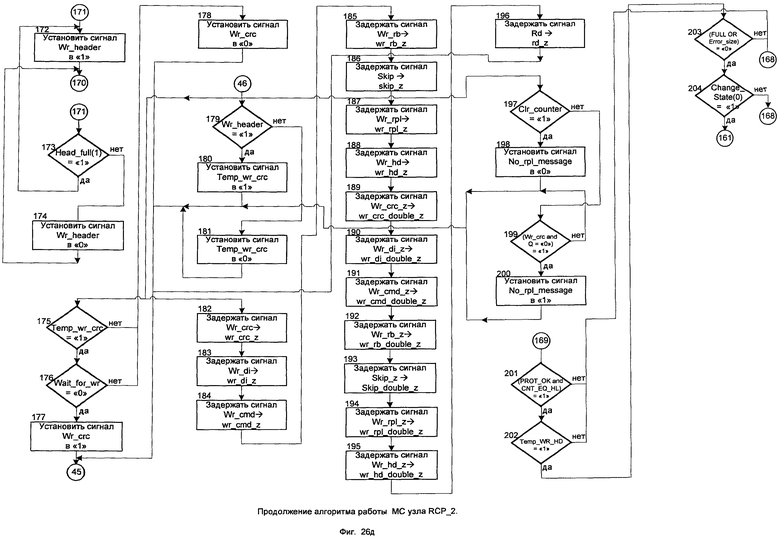

- на фиг.26, 26а, 26б, 26в, 26г, 26д представлен алгоритм работы МС узла RCP_2;

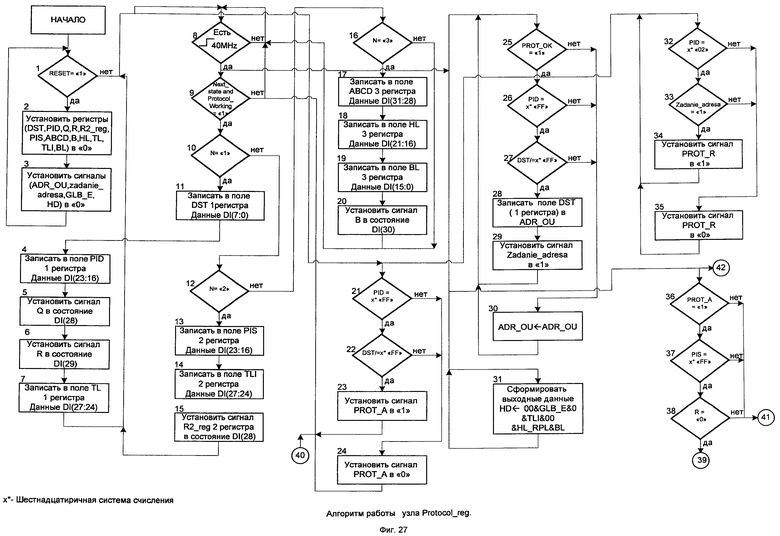

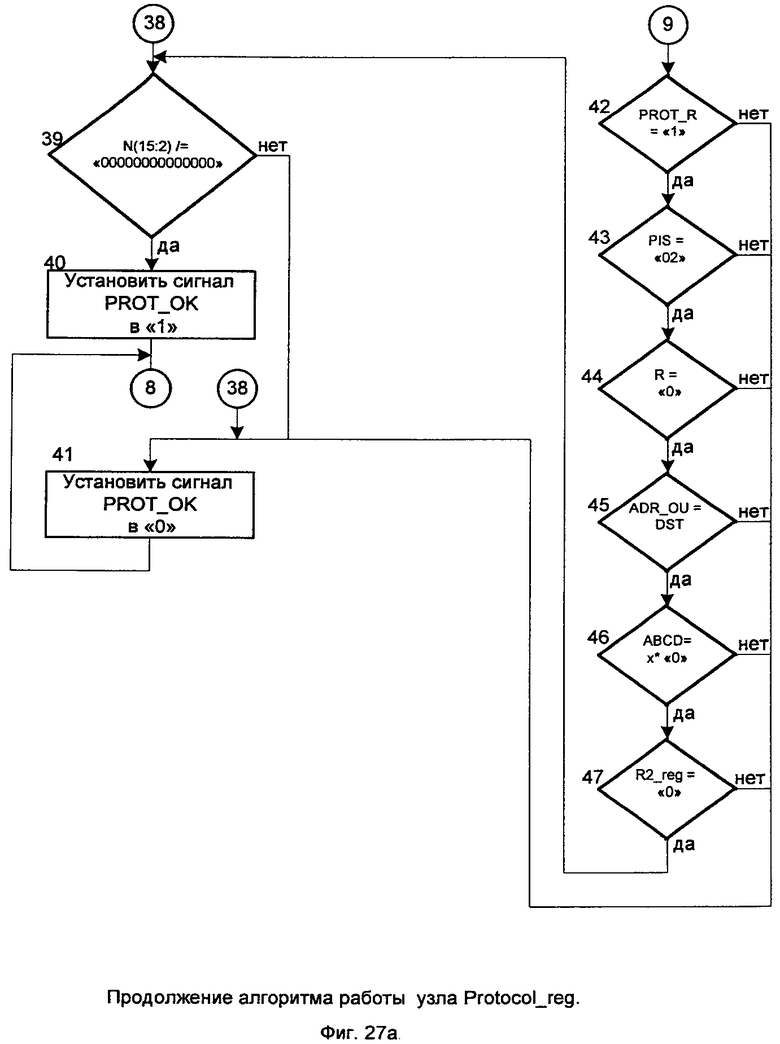

- на фиг.27, 27а представлен алгоритм работы узла Protocol-reg;

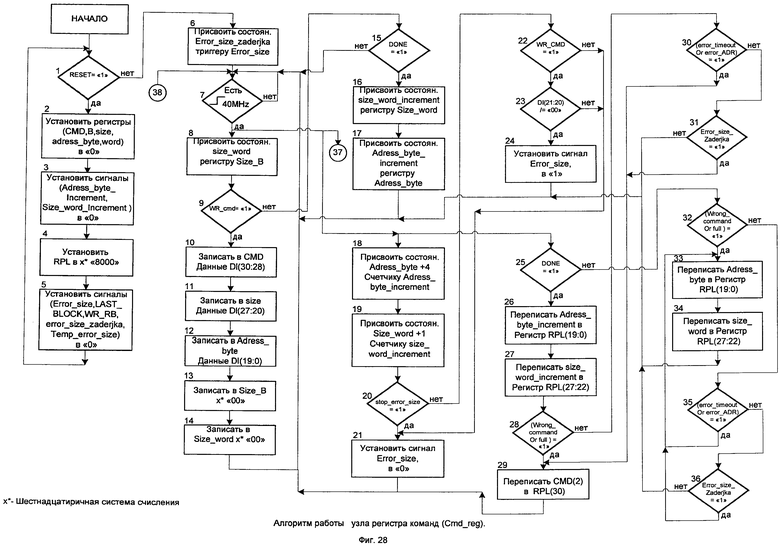

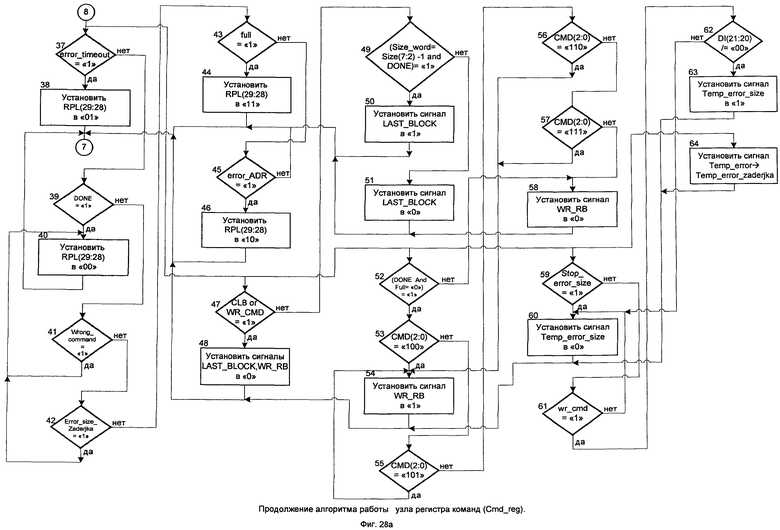

- на фиг.28, 28а представлен алгоритм работы узла регистра команд (Cmd_reg);

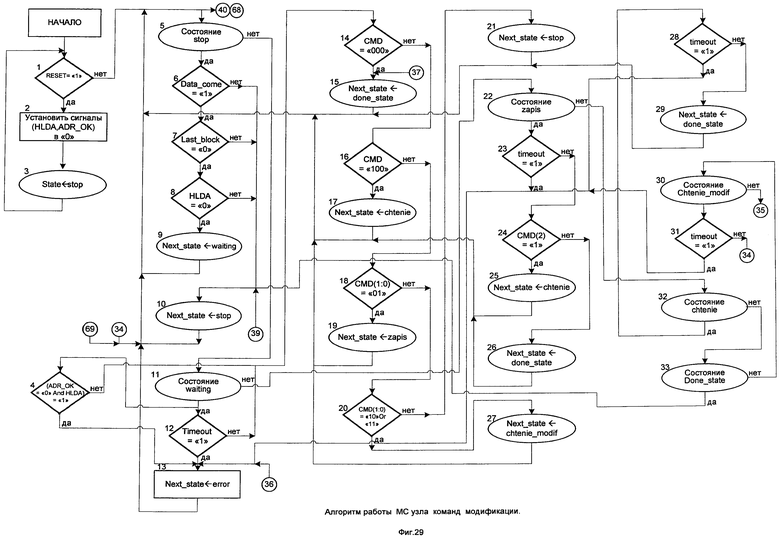

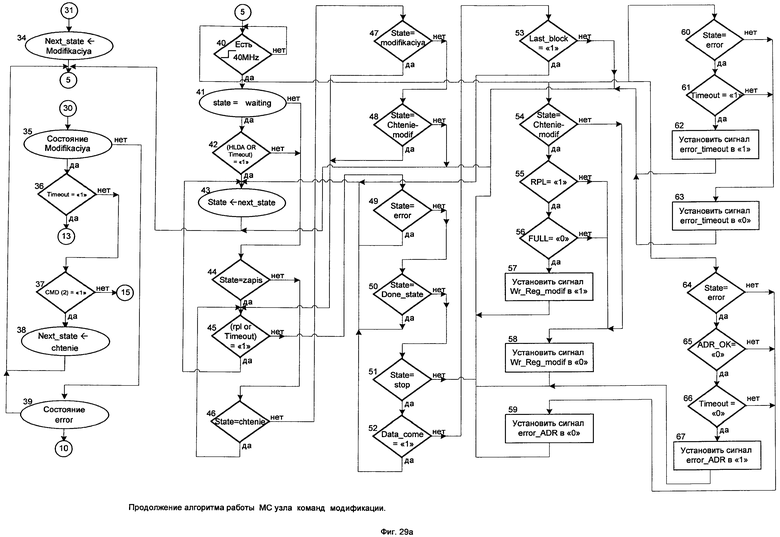

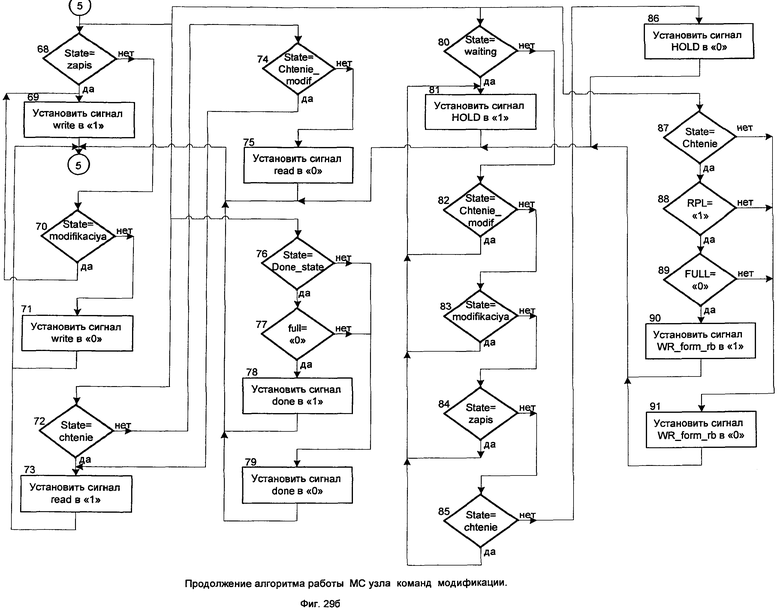

- на фиг.29, 29а, 29б представлен алгоритм работы МС узла команд модификации;

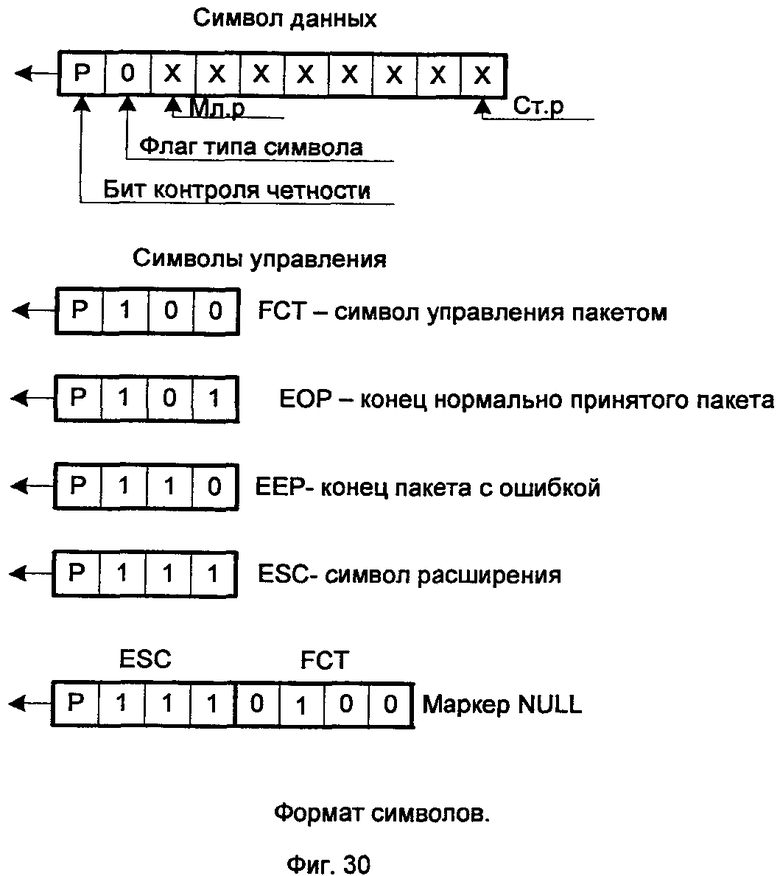

- на фиг.30 представлен формат символов;

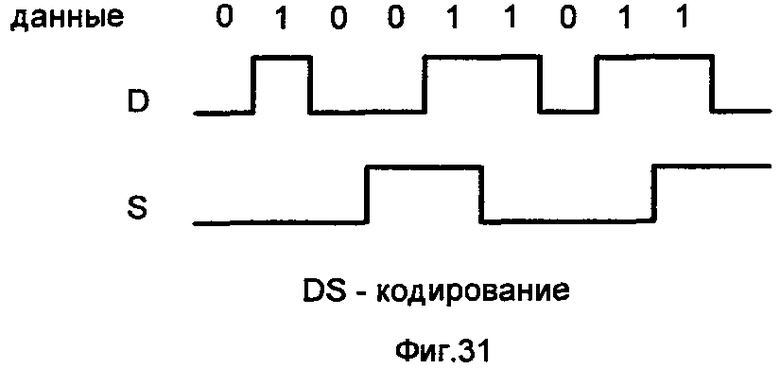

- на фиг.31 представлено DS-кодирование;

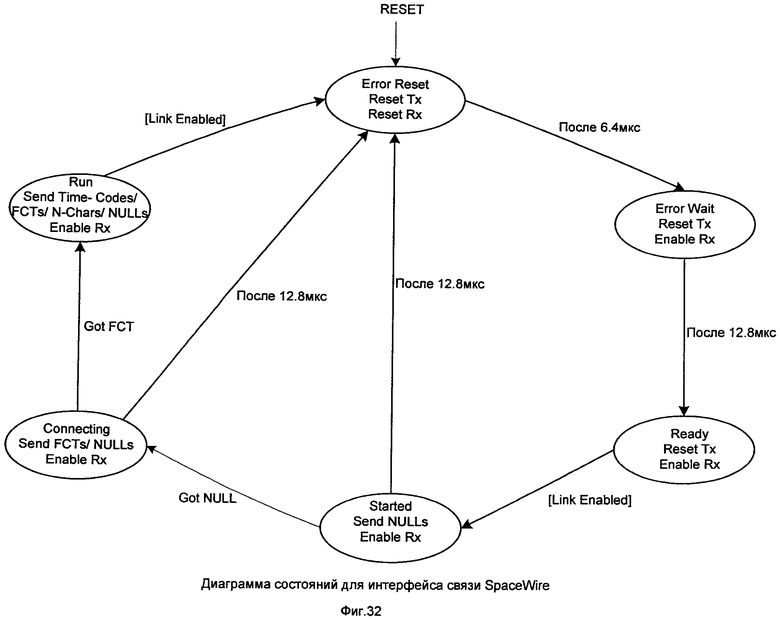

- на фиг.32 представлена диаграмма состояний интерфейса связи SpaceWire;

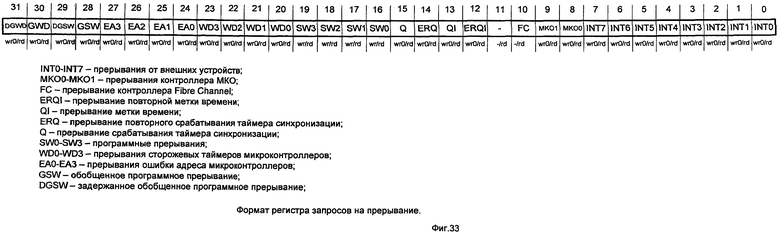

- на фиг.33 представлен формат регистра запросов на прерывание;

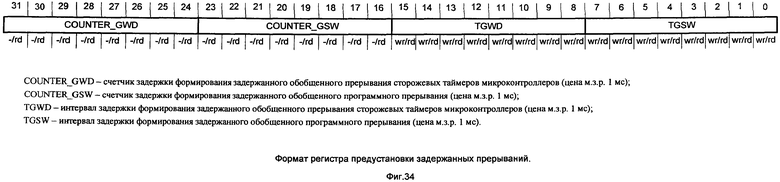

- на фиг.34 представлен формат регистра предустановки задержанных прерываний;

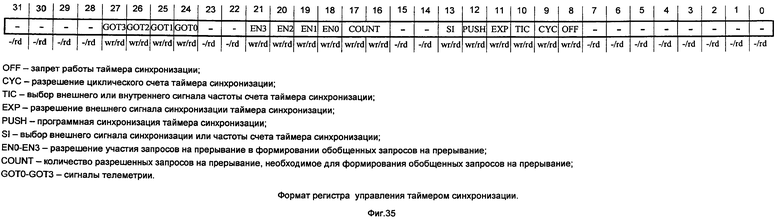

- на фиг.35 представлен формат регистра управления таймером синхронизации;

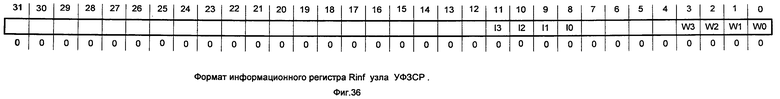

- на фиг.36 представлен формат информационного регистра Rinf узла УФЗСР;

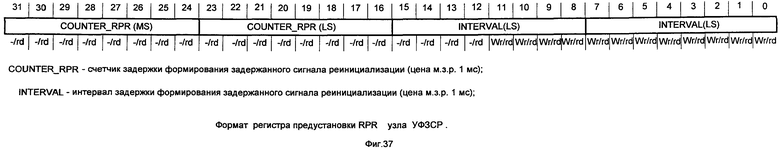

- на фиг.37 представлен формат регистра предустановки RPR узла УФЗСР;

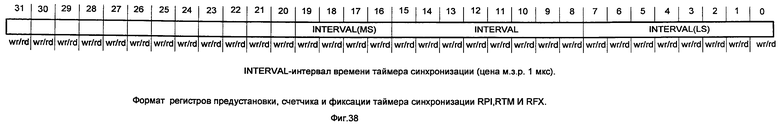

- на фиг.38 представлен формат регистров предустановки, счетчика и фиксации таймера синхронизации RPI, RTM И RFX;

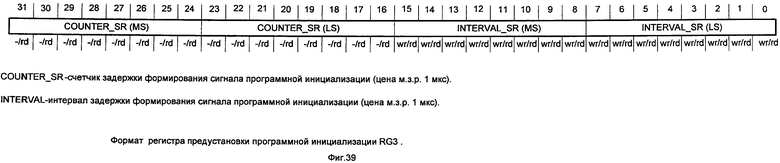

- на фиг.39 представлен формат регистра предустановки программной инициализации RG3;

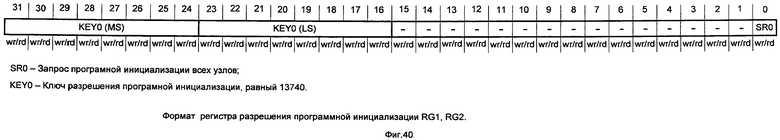

- на фиг.40 представлен формат регистра разрешения программной инициализации RG1, RG2;

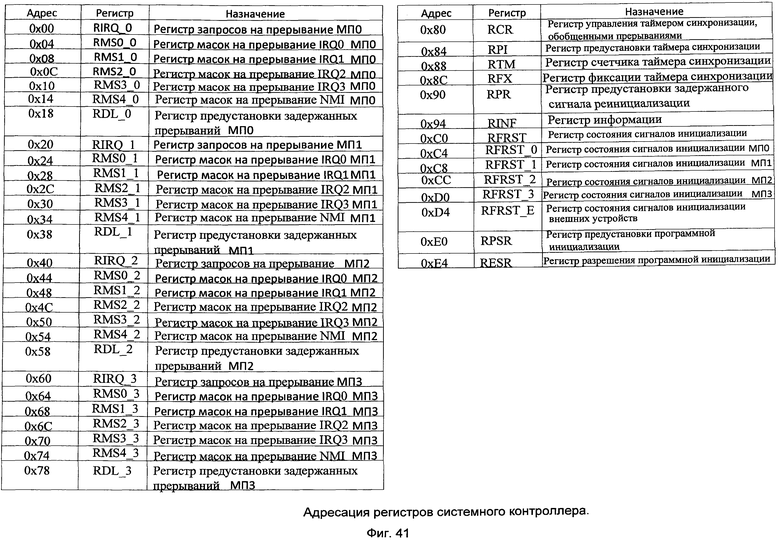

- на фиг.41 представлена адресация регистров системного контроллера;

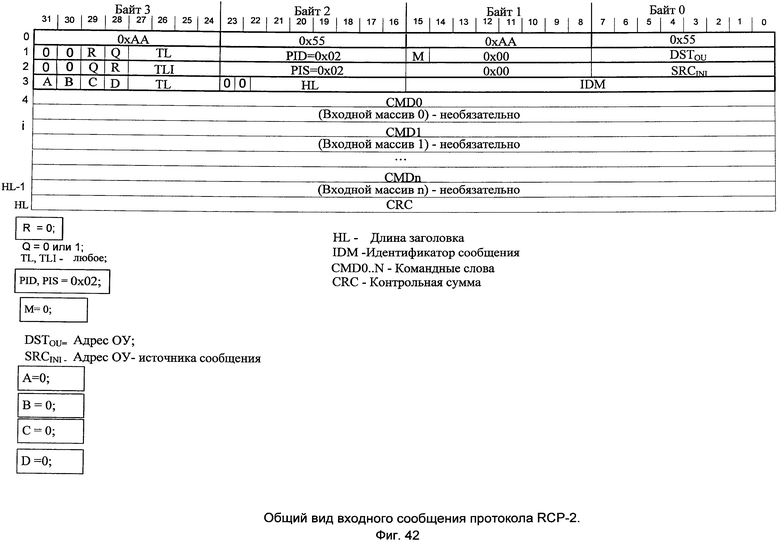

- на фиг.42 представлен общий вид входного сообщения протокола RCP-2;

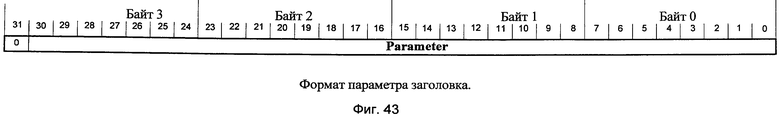

- на фиг.43 представлен формат параметра заголовка;

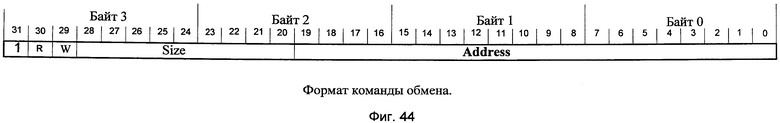

- на фиг.44 представлен формат команды обмена;

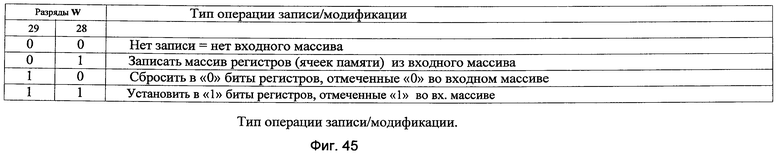

- на фиг.45 представлен тип операции записи/модификации;

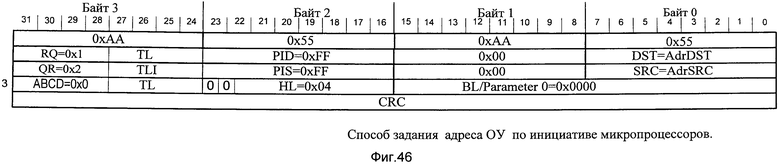

- на фиг.46 представлен способ задания адреса ОУ по инициативе микропроцессоров;

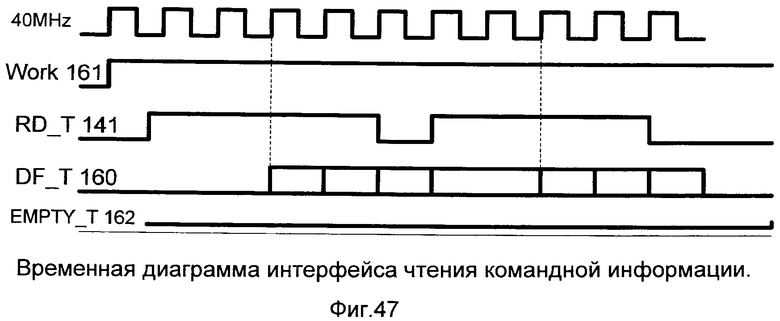

- на фиг.47 представлена временная диаграмма интерфейса чтения командной информации;

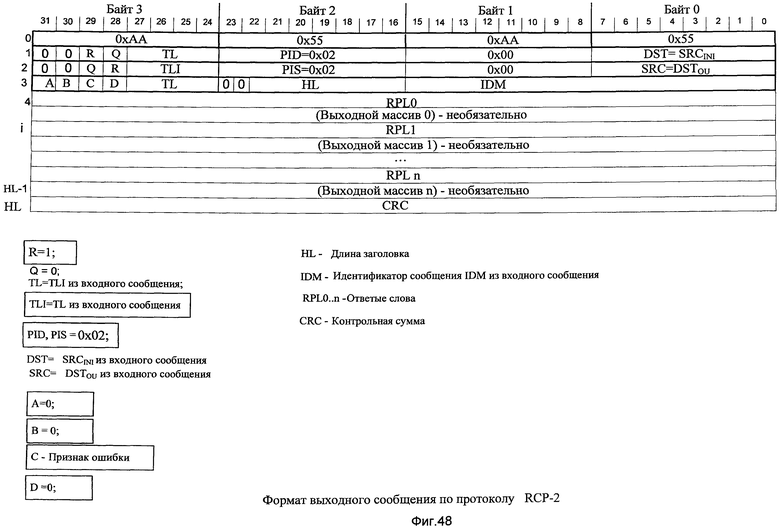

- на фиг.48 представлен формат выходного сообщения по протоколу RCP-2;

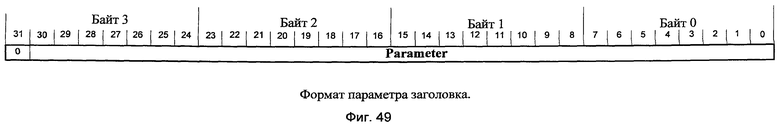

- на фиг.49 представлен формат параметра заголовка;

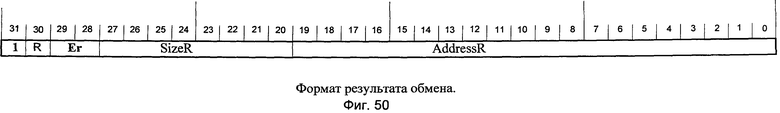

- на фиг.50 представлен формат результата обмена;

- на фиг.51 представлено поле кода ошибки;

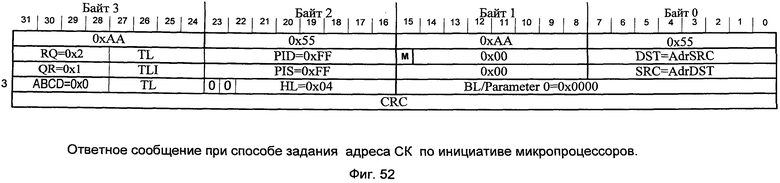

- на фиг.52 представлено ответное сообщение при способе задания адреса СК по инициативе микропроцессоров;

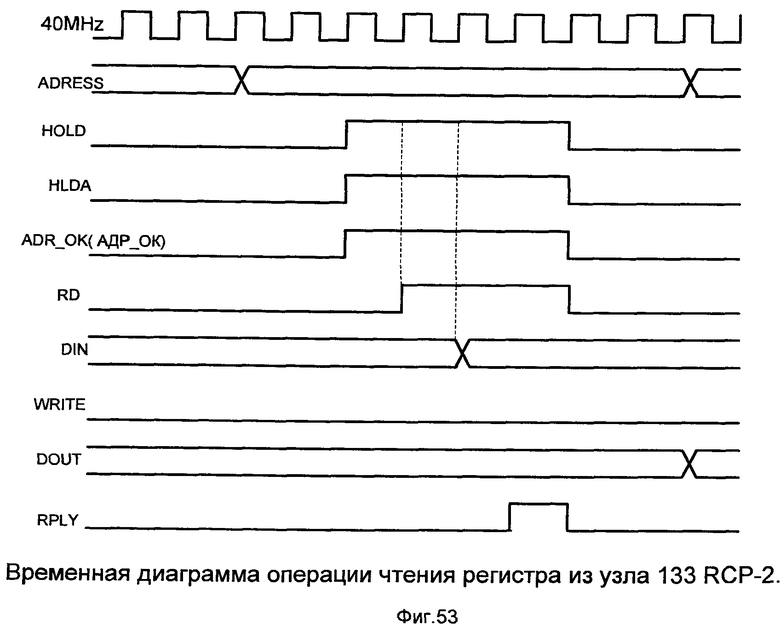

- на фиг.53 представлена временная диаграмма операции чтения регистра из узла 133 RCP-2;

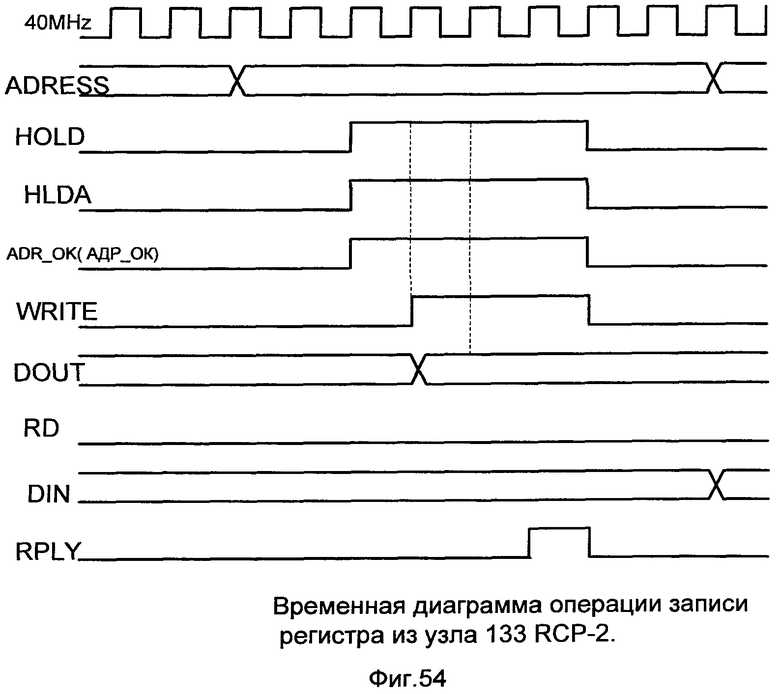

- на фиг.54 представлена временная диаграмма операции записи регистра из узла 133 RCP-2;

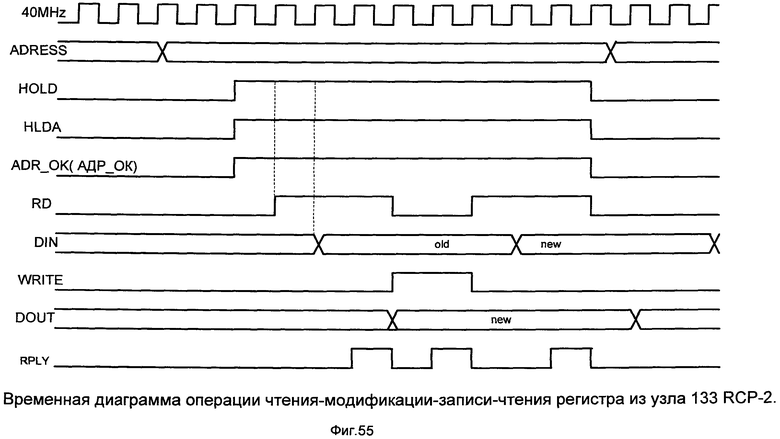

- на фиг.55 представлена временная диаграмма операции чтения-модификации-записи-чтения регистра из узла 133 RCP-2;

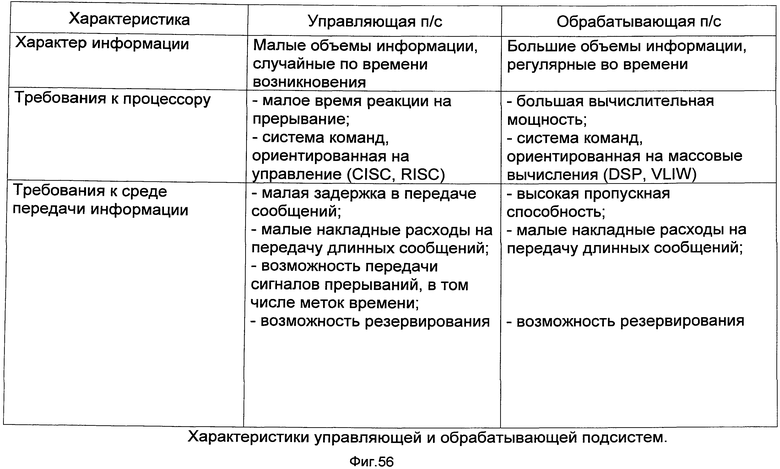

- на фиг.56 представлены характеристики управляющей и обрабатывающей подсистем;

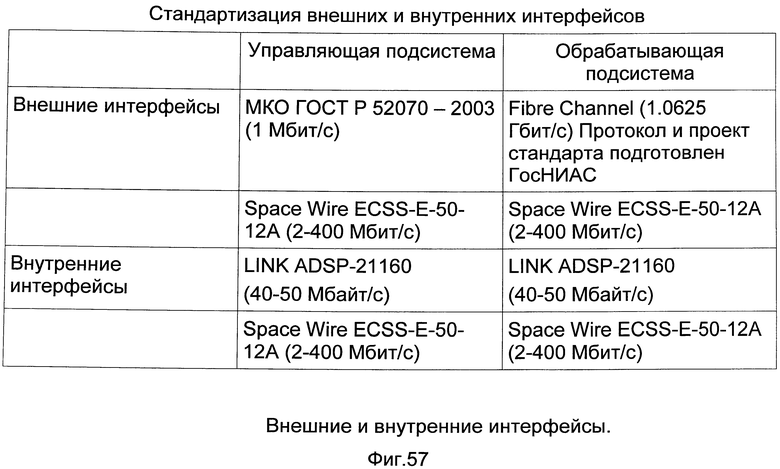

- на фиг.57 представлены внешние и внутренние интерфейсы.

Указанные преимущества заявляемой ПВС перед прототипом достигаются за счет того, что в ПВС, содержащую первый 1, второй 2, третий 3 и четвертый 4 микропроцессоры, ОЗУ 5, ПЗУ 6, первая 7 и вторая 8 группы входов ПВС соединены с первой группой входов системного контроллера 17 и первыми группами входов первого 1, второго, 2, третьего 3 и четвертого 4 процессоров, дополнительно введены второе 9, третье 10 и четвертое 11 ПЗУ, второе 12, третье 13 и четвертое 14, пятое 15 и шестое 16 ОЗУ, системный контроллер 17, первый 18, второй 19, третий 20 и четвертый 21 приемопередатчики LVDS, первый 22, второй 23, третий 24 и четвертый 25 приемопередатчики Fibre channal TLK 1201, контроллер 26 LINK Fibre channal, генератор 27 на 106,25 МГц, генератор 28 на 10 МГц, генератор 29 на 40 МГц, узел сброса по питанию 30, контроллер 31 LINK МКО, первый 32 и второй 33 приемо-передатчики МКО HI-1574, первый 34 LINK коммутатор, второй 35 LINK коммутатор, первые группы входов 36 и выходов 37 которого соединены с первыми группами входов и выходов первого 34 LINK коммутатора, вторые группы входов 38 и выходов 39 которого соединены со второй группой входов и первой группой выходов первого 1 микропроцессора, третья группа входов и вторая группа выходов которого соединены с третьими группами входов 40 и выходов 41 первого 34 LINK коммутатора, четвертые группы входов 42 и выходов 43 которого соединены со второй группой входов и первой группой выходов второго 2 микропроцессора, третья группа входов и вторая группа выходов которого соединены с пятыми группами входов 44 и выходов 45 первого 34 LINK коммутатора, шестые группы входов 46 и выходов 47 которого соединены со второй группой входов и первой группой выходов третьего 3 микропроцессора, третья группа входов и вторая группа выходов которого соединены с седьмыми группами входов 48 и выходов 49 первого 34 LINK коммутатора, восьмые группы входов 50 и выходов 51 которого соединены со второй группой входов и первой группой выходов четвертого 4 микропроцессора, третья группа входов и вторая группа выходов которого соединены с девятыми группами входов 52 и выходов 53 первого 34 LINK коммутатора, десятые группы входов 55 и выходов 54 которого являются третьей группой входов и первой группой выходов ПВС, четвертая группа входов и вторая группа выходов которой соединены с одиннадцатыми группами входов 57 и выходов 56 первого 34 LINK коммутатора, двенадцатые группы входов 58 и выходов 59 которого соединены со вторыми группами входов и выходов второго 35 LINK коммутатора, третьи группы входов и выходов которого соединены с первыми 60 группами входов и выходов 61 контроллера LINK Fibre channal, вторые группы входов и выходов которого соединены с четвертыми группами входов 62 и выходов 63 второго 35 LINK коммутатора, пятые группы входов 64 и выходов 65 которого соединены с первыми группами входов и выходов контроллера LINK МКО 31, первая 66 группа входов-выходов которого соединена с группами входов-выходов пятого 15 и шестого 16 ОЗУ, причем группы входов-выходов 67, 68, 69, 70 первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров соединены с группами входов-выходов первых 5, 6, вторых 12, 9, третьих 13, 10 и четвертых 14, 11 ОЗУ и ПЗУ соответсвенно, причем четвертые группы входов 71 и третьи группы выходов 72 первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров соединены с первыми группами входов и выходов первого 18, второго 19, третьего 20 и четвертого 21 приемопередатчиков LVDS, вторые группы входов и выходов которых соединены со вторыми 73, третьими 74, четвертыми 75 и пятыми 76 группами входов и с первыми 77, вторыми 78, третьими 79 и четвертыми 80 группами выходов системного контроллера 17, пятая 81, шестая 82, седьмая 83 и восьмая 84 группы выходов которого соединены с пятыми группами входов первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, четвертые группы выходов которых соединены с шестой 85, седьмой 86, восьмой 87 и девятой 88 группами входов системного контроллера 17, девятая 89 группа выходов которого является первой группой выходов ПВС, вторая 90 группа выходов которой соединена с первыми выходами первого 1, второго, 2 третьего 3 и четвертого 4 микропроцессоров, первые входы которых соединены с первым входом системного контроллера 17 и с выходом 91 генератора 28 на 10 МГц, причем генератор 27 на 106.25 МГц соединен с первым 92 входом контроллера LINK Fibre channal 26, третья 93 группа выходов которого соединена с первыми группами входов первого 22 и второго 23 приемопередатчиков Fibre channal TLK 1201, a четвертая 94 группа выходов соединена с первыми группами входов третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, первые группы выходов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201 соединены с первой 95, второй 96, третьей 97 и четвертой 98 группами входов контроллера LINK Fibre channal 26, пятые 99, шестые 100, седьмые 101 и восьмые 102 управляющие группы входов и выходов которого соединены со вторыми группами входов и выходов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, вторые группы выходов которых являются третьей 103, четвертой 104, пятой 105 и шестой 106 группами выходов ЛВС, третья 107, четвертая 108, пятая 109 и шестая 110 группы входов которой соединены с третьими группами входов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, причем первый 111 вход ПВС соединен со вторым входом системного контроллера 17, первая 112 и вторая 113 группы входов-выходов ПВС соединены с группами входов-выходов первого 32 и второго 33 приемопередатчиков МКО HI-1574, группы выходов которых соединены со второй 114 и третьей 115 группами входов контроллера LINK МКО 31, вторая 116 и третья 117 группы выходов которого соединены с первыми группами входов первого 32 и второго 33 приемопередатчиков МКО HI-1574, вторые группы входов которых соединены с четвертой 118 и пятой 119 группами выходов контроллера LINK МКО 31, шестая 120 группа выходов которого соединена с десятой группой входов системного контроллера 17, первый 121 выход которого соединен со вторыми входами первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, причем выход 122 узла сброса по питанию 30 соединен с третьим входом системного контроллера 17, десятая группа выходов которого является третьей 123 группой выходов ПВС, причем второй 124 выход системного контроллера 17 соединен с третьими входами первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, с первыми входами первого 34 и второго 35 LINK коммутаторами и контроллером LINK МКО 31, вторым входом контроллера LINK Fibre channal 26, первый 125 выход которого соединен с четвертым входом системного контроллера 17, причем выход 126 генератора 29 на 40 МГц соединен со вторым входом контроллера LINK МКО 31, а вход 127 узла сброса по питанию 30 соединен с питанием 3.3V.

Системный контроллер 17 содержит первый 128, второй 129, третий 130, четвертый 131 блоки Space Wire, коммутатор 132, узел формирования зап/чт в регистры коммуникационных систем на основе LINK-интерфейсов (далее по тексту узел RCP_2) 133, таймер синхронизации и узел формирования прерываний (ТСУФП) 134, узел формирования сигналов инициализации и тактовых сигналов (УФСИТС) 135, узел приема и фиксации сигналов инициализации (УПФСИ) 136, узел формирования сигнала программной инициализации (УФСПИ) 137, первая 138 группа выходов которого соединена с первыми группами выходов УПФСИ 136 и ТСУФП 134 и первой группой входов узла 133 RCP_2, первая 139 группа выходов которого соединена с первыми группами входов УПФСИ 136, УФСПИ 137 и ТСУФП 134, вторая группа входов которого соединена со вторыми группами входов УПФСИ 136 и УФСПИ 137 и второй 140 группой выходов узла 133 RCP_2, третья 141 группа выходов которого соединена с третьими группами входов УПФСИ 136, УФСПИ 137, ТСУФП 134 и первой группой входов коммутатора 132, первая 142, вторая 143, третья 144 и четвертая 145 группы выходов которого соединены с первыми группами входов первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, первые группы выходов которых соединены со второй 146, третьей 147, четвертой 148 и пятой 149 группами входов коммутатора 132, шестая 150, седьмая 151, восьмая 152 и девятая 153 группы входов которого соединены со вторыми группами выходов первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, первый и второй выходы которых являются первой 77, второй 78, третьей 79 и четвертой 80 группами выходов системного контроллера 17 соответственно, вторая 73, третья 74, четвертая 75 и пятая 76 группы входов которого являются первым и вторым входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, вторые группы входов которых соединены с четвертой 154 группой выходов узла 133 RCP_2, пятая 155 группа выходов которого соединена с десятой группой входов коммутатора 132 и с третьими входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, четвертые входы которых соединены между собой, с первыми входами коммутатора 132, УПФСИ 136, УФСПИ 137, ТСУФП 134, узла 133 RCP_2 и первым 156 выходом УФСИТС 135, второй 157 выход которого соединен с пятыми входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, шестые входы которых соединены между собой и со вторыми входами ТСУФП 134 и узла 133 RCP_2, с третьим 124 выходом УФСИТС 135 и является первым выходом системного контроллера 17, второй 121 выход которого соединен с четвертым выходом УФСИТС 135, пятый 158 выход которого соединен с третьим входом ТСУФП 134, вторая 159 группа выходов которого соединена со второй группой входов узла 135 RCP_2, третья группа входов которого соединена с пятой 160 группой выходов коммутатора 132, первый 161, второй 162 и третий 163 выходы которого соединены с третьим, четвертым и пятым входами узла 133 RCP_2, первый 164 выход которого соединен с четвертым входом ТСУФП 134, первый 165 выход которого соединен с первым входом УФСИТС 135, первая 166 группа выходов которого соединена с четвертой группой входов УПФСИ 136, причем шестой вход ТСУФП 134 соединен с первым 167 выходом УФСПИ 137, второй 168 выход которого соединен со вторым входом УФСИТС 135, шестой 169 выход которого соединен со вторым входом УФСПИ 137, причем третий, четвертый и пятый входы УФСИТС 135 являются первым 91, третьим 122 и вторым 111 входами системного контроллера 17, пятая 81, шестая 82, седьмая 83, восьмая 84 группы выходов которого соединены с третьей, четвертой, пятой и шестой группами выходов ТСУФП 134, седьмая и восьмая группы выходов которого соединены с девятой 89 и десятой 123 группами выходов системного контроллера 17, четвертая, пятая, шестая, седьмая и восьмая группы входов которого соединены с первой 7, шестой 85, седьмой 86, восьмой 87 и девятой 88 группами входов системного контроллера 17 соответственно, десятая 120 группа входов которого соединена с девятой группой входов ТСУФП 134, пятый вход которого является и четвертым 125 входом системного контроллера 17, причем вторая 170 группа выходов УФСИТС 135 соединена с четвертой группой входов УФСПИ 137.

Таймер синхронизации и узел формирования прерываний (ТСУФП) 134 содержат первый 171, второй 172, третий 173 и четвертый 174 узлы приема, фиксации и выдачи сигналов прерываний (УПФВСП), таймер синхронизации (ТС) 175, узел формирования задержанного сигнала реинициализации (УФЗСР) 176, регистр управления таймером синхронизации (RCR) 177, узел формирования разрешения обмена данными (УФРОД) 178, группа выходов которого является второй 159 группой выходов ТСУФП 134, первая 138 группа выходов которого соединена с первыми группами выходов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, УФЗСР 176, RCR 177 и ТС 175, первая 314 группа входов которого соединена со второй группой выходов RCR 177, третья группа выходов которого соединена с первыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, вторые группы входов которых соединены между собой, с первыми группами входов УФЗСР 176, RCR 177 и второй группой входов ТС 175 и являются первой 139 группой входов ТСУФП 134, вторая 140 группа входов которого соединена с первой группой входов УФРОД, со вторыми группами входов УФЗСР 176, RCR 177, третьей группой входов ТС 175 и с третьими группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, четвертые группы входов которых соединены между собой, со второй группой входов УФРОД, с третьими группами входов УФЗСР 176, RCR 177, с четвертой группой входов ТС 175 и являются третьей 141 группой входов ТСУФП 134, третья 81, четвертая 82, пятая 83 и шестая 84 группы выходов которого соединены со вторыми группами выходов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, первые входы которых соединены между собой и с первыми входами УФЗСР 176, RCR 177, УФРОД 178, ТС 175 и являются первым 156 входом ТСУФП 134, второй 124 вход которого соединен со вторыми входами УФЗСР 176, RCR 177, УФРОД 178, ТС 175 и первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, пятые группы входов которых являются пятой 85, шестой 86, седьмой 87 и восьмой 88 группами входов ТСУФП 134, девятая 120 группа входов которого соединена с шестыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, третьи входы которых соединены с пятым 125 входом ТСУФП 134, третий 158 вход которого соединен с третьим входом ТС 175, причем четвертый 164 вход ТСУФП 134 соединен с третьими входами УФРОД 178 и УФЗСР 176, первый выход которого является первым 165 выходом ТСУФП 134, седьмая 89 и восьмая 123 группы выходов которого соединены со второй группой выходов УФЗСР 176 и с четвертой группой выходов RCR 177, причем четвертая 7 группа входов ТСУФП 134 соединена с седьмыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП и с четвертым входом ТС 175, четвертая группа входов УФЗСР 176 соединена с первыми сигналами пятой 85, шестой 86, седьмой 87 и восьмой 88 группами входов ТСУФП 134, причем первый выход ТС соединен с четвертыми входами первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП.

Блок SW (128, 129, 130, 131) содержит узел SW_LPORT 179, узел LPORT_OY 180, узел SW (YSW) 181, узел LPORT_SW 182, элемент ИЛИ 183, FIFO 184, первая группа выходов которого является первой 146 группой выходов блока SW 128, вторая 150 группа выходов которого соединена с первыми выходами узла LPORT_SW 182, узла LPORT_OY 180 и FIFO 184, первый выход которой соединен с первым входом узла LPORT_OY 180, первая группа входов которого соединена с первой группой входов FIFO 184 и с первой 185 группой выходов узла SW_LPORT 179, первый вход которого соединен с первыми входами YSW 181, узла LPORT_ SW 182, FIFO 184, со вторым входом узла LPORT_OY 180 и является пятым 157 входом блока SW 128, первый 186 и второй 187 входы которого соединены со вторым и третьим входами YSW 181, первый и второй выходы которого являются первым 188 и вторым 189 выходами блока SW 128, первая 142 группа входов которого соединена со вторыми входами FIFO 184 и узла LPORT_SW 182, группа выходов 190 которого соединена с первой группой входов YSW 181, третий 191 выход которого соединен с третьим входом узла LPORT_ SW 182, второй 192 выход которого соединен с четвертым входом YSW 181, пятый 193 и шестой 194 входы которого соединены с первым и вторым выходами узла SW_LPORT 179, второй вход которого соединен с третьими входами узла LPORT_OY 180 и FIFO 184, с четвертым и седьмым входами узла LPORT_SW 182 и YSW 181 и является шестым 124 входом блока SW 128, четвертый 156 вход которого соединен с восьмым входом YSW 181, четвертый 195 выход которого соединен с третьим входом узла SW_LPORT 179, четвертый вход которого соединен с выходом 196 элемента ИЛИ 183, первый и второй входы которого соединены со вторыми 197,198 выходами FIFO 184 и узла LPORT_OY 180, третий 199 выход которого соединен с четвертым входом FIFO 184, причем третий 155 вход блока SW 128 соединен с пятым входом узла LPORT_SW 182, группа выходов 200 YSW 181 соединена с группой входов узла SW_LPORT 179, вторая VWORD группа выходов которого соединена со вторыми группами входов LPORT_OY 180 и FIFO 184, вторая 154 группа входов блока SW 128 соединена с группой входов LPORT_SW 182.

Узел SW 181 содержит приемник 201, машину состояний (МС) 202, передатчик 203, первый, второй и третий выходы которого являются первым 188, вторым 189 и третьим 191 выходами узла SW 181, четвертый 195 выход которого соединен с первым входом передатчика 203 и первым выходом приемника 201, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы которого соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым входами МС 202, первый выход которой соединен с первым входом приемника 201, первая и вторая группы выходов которого соединены с первой и второй группами входов передатчика 203, второй вход которого соединен с восьмым входом МС 202 и с первым 157 входом узла SW 181, второй 186 и третий 187 входы которого соединены со вторым и третьим входами приемника 201, четвертый, пятый и шестой входы которого соединены с восьмым 156, шестым 194, четвертым 192 входами узла SW 181 соответственно, пятый 193 вход которого соединен с девятым входом МС 202, десятый вход которого соединен с третьим входом передатчика 203, седьмым входом приемника 201 и является седьмым 124 входом узла SW 181, причем четвертый вход передатчика 203 соединен с одиннадцатым входом МС 202, с питанием 3.3v и с двенадцатым входом МС 202, второй, третий, четвертый, пятый, шестой и седьмой выходы которой соединены с пятым, шестым, седьмым, восьмым, девятым и десятым входами передатчика 203, одиннадцатый вход которого соединен с пятым выходом приемника 201, девятый выход которого соединен с двенадцатым входом передатчика 203, причем тринадцатый вход МС 202 соединен с корпусом, а восьмой выход МС 202 с восьмым входом приемника 201, причем первая 200 группа выходов и первая 190 группа входов узла SW 181 соединены с третьей группой выходов приемника 201 и с третьей группой входов передатчика 203.

Узел LPORT_OY 180 содержит сумматор 204, инвертор 205, МС 206 и узел контроля полей заголовка 207, группа выходов которого соединена с первой группой входов МС 206, группа выходов которой соединена с первой группой входов узла контроля полей заголовка 207, первый, второй и третий выходы которого соединены с первым, вторым и третьим входами МС 206, первый, второй и третий выходы которой являются третьим сигналом второй группы выходов 150, первым 198 и вторым 199 выходами узла LPORT_OY 180 соответственно, первая 185 группа входов которого соединена с первой группой входов сумматора 204 и второй группой входов узла контроля полей заголовка 207, четвертый выход которого соединен с четвертым входом МС 206 и входом инвертора 205, выход которого соединен с пятым входом МС 206, четвертый выход которой соединен с первым входом сумматора 204, группа выходов которого соединена со второй группой входов МС 206 и третьей группой входов узла контроля полей заголовка 207, первый вход которого соединен со вторым входом сумматора 204, шестым входом МС 206 и является вторым 157 входом узла LPORT_OY 180, вторая VWORD группа входов которого соединена со второй группой входов сумматора 204 и третьей группой входов МС 206, седьмой вход которой является вторым сигналом второй группы выходов 150 узла LPORT_OY 180, третий 124 вход которого соединен со вторым входом узла контроля полей заголовка 207, с третьим входом сумматора 204 и с восьмым входом МС 206, девятый вход которой соединен с выходом сумматора 204, причем десятый вход МС 206 соединен с питанием +3.3v, а одиннадцатый вход соединен с «корпусом».

Узел SW_LPORT 179 содержит сдвиговый регистр 208, первый 209, второй 210 и третий 211 регистры, МС 212 и константу 213, группа выходов которой соединена с группой входов сдвигового регистра 208, группа выходов которого соединена с группой входов МС 212 и является второй 201 группой выходов узла SW_LPORT 179, первая 185 группа выходов которого соединена с группой выходов третьего 211 регистра, группа входов которого соединена с группой выходов второго 210 регистра, группа входов которого соединена с группой выходов первого 209 регистра, группа входов которого является группой входов 200 узла SW_LPORT 179, а восьмой разряд соединен с первым входом МС 212, первый и второй выходы которой являются первым 193 и вторым 194 выходами узла SW_LPORT 179, первый 157 вход которого соединен с тактовыми входами сдвигового регистр 208, первого 209, второго 210 и третьего 211 регистров, сбросовые входы которых соединены между собой и являются вторым 124 входом узла SW_LPORT 179, третий 195 и четвертый 196 входы которого соединены со вторым и третьим входами МС 212, третий, четвертый и пятый выходы которой соединены с разрешающими входами третьего 211 регистра, первого 209 регистра и второго 210 регистра соответственно.

Узел LPORT_SW 182 содержит счетчик 214, первый 215 и второй 216 регистры, первый 217 и второй 218 мультиплексоры, МС 219 и константу 220, группа выходов которой соединена с первой группой входов второго 218 мультиплексора, группа выходов которого соединена с информационной группой входов второго 216 регистра, группа выходов которого является группой выходов 190 узла LPORT_SW 182, первый сигнал второй группы выходов 150 и второй 192 выход которого соединены с первым и вторым выходами МС 219, третий выход которой соединен со входом второго 218 мультиплексора и с разрешающим входом второго 216 регистра, тактовый вход которого соединен с тактовыми входами счетчика 214 и первого 215 регистра, с первым входом МС 219 и является первым 157 входом узла LPORT_SW 182, второй сигнал первой группы входов 142, третий 19d и пятый 155 (первый сигнал) входы которого соединены со вторым, третьим и четвертым входами МС 219, четвертый выход которой соединен с прямым и инверсным входами первого 217 мультиплексора, первая и вторая группы выходов которого соединены с информационными входами первого 215 регистра, сбросовый вход которого соединен со сбросовыми входами счетчика 214 и второго 216 регистра, с пятым входом МС 219 и является четвертым 124 входом узла LPORT_SW 182, группа входов 154 которого соединена с первой и второй группами входов первого 217 мультиплексора, третья группа входов которого соединена с первой и второй группами выходов первого 215 регистра и второй группой входов второго 218 мультиплексора, причем группа выходов счетчика 214 соединена с группой входов МС 219, пятый выход которой соединен с разрешающим входом счетчика 214.

Узел формирования сигнала программной инициализации (УФСПИ) 137 содержит первый 221, второй 222 и третий 223 регистры, первый 224 и второй 225 узлы REG_COUNT, элемент ИЛИ 226, блок констант 227, схему сравнения 228, первый 229, второй 230 и третий 231 элемент И, триггер 232, выход которого соединен с первым входом третьего 231 элемента И, выход которого соединен с первым входом первого 224 узла REG_COUNT, выход которого соединен с инверсным входом первого 229 элемента И и является первым 167 выходом УФСПИ 137, второй 168 выход которого соединен с выходом первого 229 элемента И, прямой вход которого соединен с выходом элемента ИЛИ 226, группа входов которого соединена с первой группой выходов второго 222 регистра, вторая группа выходов которого соединена с первой и второй группами выходов первого 221 регистра, с первой группой входов схемы сравнения 228, с группами выходов третьего 223 регистра, первого 224 и второго 225 узла REG_COUNT и является первой 138 группой выходов УФСПИ 137, первая 139 группа входов которого соединена с информационными группами входов первого 221, второго 222 и третьего 223 регистров, первые группы входов которых соединены с первыми группами входов первого 224 и второго 225 узлов REG_COUNT и являются третьей 141 группой входов УФСПИ 137, вторая 140 группа входов которого соединена с разрешающими входами первого 221, второго 222 и третьего 223 регистров и со вторым входом первого 224 узла REG_COUNT и первым входом второго 225 узла REG_COUNT, второй вход которого соединен с третим входом первого 224 узла REG_COUNT и с тактовыми входами первого 221, второго 222, третьего 223 регистров и триггера 232 и является первым 156 входом УФСПИ 137, первый сигнал четвертой 170 группы входов соединен со сбросовыми входами первого 221, третьего 223 регистров и триггера 232, с четвертым входом первого 224 узла REG_COUNT и третьим входом второго 225 узла REG_COUNT, второй сигнал четвертой 170 группы входов соединен со сбросовым входом второго 222 регистра, причем выход второго 225 узла REG_COUNT соединен с прямым входом второго 230 элемента И, инверсный вход которого соединен с четвертым входом второго 225 узла REG_COUNT и инверсным выходом схемы сравнения 228, вторая группа входов которой соединена с первой группой выходов блока констант 227, вторая группа выходов которого соединена со вторыми группами входов первого 224 и второго 225 узлов REG_COUNT, пятые входы которых соединены со вторым 169 входом УФСПИ 137, причем выход второго 230 элемента И соединен с информационным входом триггера 232 и вторым входом третьего 231 элемента И.

Узел с управляемым разрешением счета (REG_COUNT)(224, 225) содержит счетчик 233, дешифратор 234, элемент И 235 и триггер 236, выход которого является выходом 167 узла REG_COUNT 224, группа выходов 138 которого соединена с первой группой выходов счетчика 233, вторая группа выходов которого соединена с группой входов дешифратора 234, выход которого соединен с первым входом элемента И 235 и информационным входом триггера 236, тактовый вход которого соединен с тактовым входом счетчика 233 и является первым 156 входом узла REG_COUNT 224, пятый 169 вход которого соединен со вторым входом элемента И 235, выход которого соединен с разрешающим входом счетчика 233, информационная группа входов которого является второй 227 группой входов узла REG_COUNT 224, первая 141 группа входов которого соединена с группой входов счетчика 233, сбросовый вход которого соединен с установочным входом триггера 236 и является первым сигналом четвертой 170 группы входов узла REG_COUNT 224, второй 140 вход которого соединен с третьим входом элемента И 235.

Узел формирования сигналов инициализации и тактовых сигналов (УФСИТС) 135 содержит первый 238 счетчик, второй 239 счетчик, третий 240 счетчик, четвертый 241 счетчик, PLL 242, первый 243 элемент ИЛИ, второй 244 элемент ИЛИ, третий 245 элемент ИЛИ, первый 246 триггер, второй 247 триггер, первый 248 дешифратор, второй 249 дешифратор, инвертор 250, выход которого является первым сигналом первой 166 группы выходов УФСИТС 135, второй сигнал которой соединен с инверсным выходом первого 246 триггера, прямой выход которого соединен с первым входом второго 244 элемента ИЛИ и сбросовым входом четвертого 241 счетчика, выход которого является четвертым 121 выходом УФСИТС 135, третий сигнал первой 166 группы выходов которого соединен со вторым входом второго 244 элемента ИЛИ и является пятым 111 входом УФСИТС 135, четвертый сигнал первой 166 группы выходов которого соединен с первым входом третьего 245 элемента ИЛИ и является вторым 165 входом УФСИТС 135, первый сигнал второй 170 группы выходов которого соединен с выходом третьего 245 элемента ИЛИ и является третьим 124 выходом УФСИТС 135, второй сигнал второй 170 группы выходов которого соединен с выходом второго 247 триггера, со вторым входом третьего 245 элемента ИЛИ, сбросовым входом третьего 240 счетчика, первый и второй выходы которого являются пятым 158 и шестым 169 выходами УФСИТС 135 соответственно, первый 156 и второй 157 выходы которого соединены с первым и вторым выходами PLL 242, третий выход которой соединен с первым входом первого 243 элемента ИЛИ, выход которого соединен со сбросовым входом первого 238 счетчика, инверсный разрешающий вход которого соединен с информационным входом первого 246 триггера и выходом первого 248 дешифратора, группа входов которого соединена с группой выходов первого 238 счетчика, тактовый вход которого соединен с тактовыми входами второго 239, третьего 240 и четвертого 241 счетчиков и первого 246 и второго 247 триггеров, входом PLL 242 и является третьим 91 входом УФСИТС 135, первый 168 вход которого соединен со входом инвертора 250 и третьим входом третьего 245 элемента ИЛИ, причем четвертый 122 вход УФСИТС 135 соединен со вторым входом первого 243 элемента ИЛИ и сбросовым входом первого 246 триггера, выход второго 249 дешифратора соединен с инверсным разрешающим входом второго 239 счетчика и информационным входом второго 247 триггера, сбросовый вход которого соединен со сбросовым входом второго 239 счетчика и выходом второго 244 элемента ИЛИ, причем группа выходов второго 239 счетчика соединена с группой входов второго 249 дешифратора.

Узел формирования задержанного сигнала реинициализации (УФЗСР) 176 содержит первый 251 счетчик, второй 252 счетчик, первый 253 регистр, второй 254 регистр, третий 255 регистр, первый 256 узел REG_COUNT, второй 257 узел REG_COUNT, третий 258 узел REG_COUNT, блок констант 259, первый 260 элемент ИЛИ, второй 261 элемент ИЛИ, схему сравнения 262, первый 263 дешифратор, второй 264 дешифратор, третий 265 дешифратор, первую 266 группу элементов И, вторую 267 группу элементов И, первый 268 триггер, второй 269 триггер, третий 270 триггер, четвертый 271 триггер, пятый 272 триггер, шестой 273 триггер, седьмой 274 триггер, первый 275 элемент И, второй 276 элемент И, третий 277 элемент И, четвертый 278 элемент И, пятый 279 элемент И, шестой 280 элемент И, седьмой 281 элемент И, восьмой 282 элемент И, девятый 283 элемент И, группу элементов ИЛИ 284, выходы которой соединены с первой группой выходов третьего 255 регистра, с группами выходов первого 253 регистра и первого 256 узла REG_COUNT, с группой входов первого 256 узла REG_COUNT и являются первой 138 группой выходов УФЗСР 176, вторая 89 группа выходов которого соединена с первыми выходами второго 257 и третьего 258 узлов REG_COUNT, группы входов которых соединены с первой группой выходов блока констант 259, вторая группа выходов которого соединена с первой группой входов первой 266 группы элементов И, группа выходов которой соединена с группой входов первого 253 регистра, разрешающий вход которого соединен с выходом седьмого 281 элемента И, первый вход которого является первым сигналом второй 140 группы входов, а второй сигнал соединен с первым входом шестого 280 элемента И, выход которого соединен с первыми входами второго 276 и четвертого 278 элементов И и разрешающим входом третьего 255 регистра, вторая группа выходов которого соединена с первой группой входов группы элементов ИЛИ 284, вторая группа входов которой соединена с группой выходов второго 254 регистра, первая группа входов которого соединена с третьей группой выходов блока констант 259, четвертая группа выходов которого соединена с первой группой входов схемы сравнения 262, выход которой соединен со вторым входом второго 276 элемента И, выход которого соединен с информационным входом третьего 270 триггера, выход которого соединен с первым входом второго 257 узла REG_COUNT, второй вход которого соединен с первыми входами первого 256 и третьего 258 узлов REG_COUNT, с тактовыми входами первого 251 и второго 252 счетчиков, первого 268, второго 269, третьего 270, четвертого 271, шестого 273 и седьмого 274 триггеров, первого 253, второго 254 и третьего 255 регистров и является первым 156 входом УФЗСР 176, первый 165 выход которого соединен с первым выходом третьего 258 узла REG_COUNT, второй вход которого соединен с первым входом второго 261 элемента ИЛИ, со вторым и третьим входами первого 256 и второго 257 узлов REG_COUNT, со сбросовыми входами первого 251 счетчика, первого 253, второго 254 и третьего 255 регистров, второго 269, третьего 270, четвертого 271, шестого 273 и седьмого 274 триггеров, с установочным входом первого 268 триггера и является вторым 124 входом УФЗСР 176, первая 139 группа входов которого соединена со вторыми группами входов схемы сравнения 262 и первой группой элементов И 266 и с первой группой входов второй 267 группы элементов И, группа выходов которой соединена с информационной группой входов третьего 255 регистра и группой входов третьего 265 дешифратора, первая группа выходов и выход которого соединены со второй группой входов второй 267 группы элементов И и вторым входом четвертого 278 элемента И, выход которого соединен с установочным и инверсным сбросовым входами пятого 272 триггера, выход которого соединен с информационным входом первого 268 триггера, выход которого соединен с третьим входом первого 256 узла REG_COUNT и с инверсным входом третьего 277 элемента И, выход которого соединен с информационным входом четвертого 271 триггера и с первым входом пятого 279 элемента И, выход которого соединен с третьим входом третьего 258 узла REG_COUNT, причем первый сигнал третьей 141 группы входов УФЗСР 176 соединен со входами первого 253 и третьего регистров, а второй сигнал соединен со вторыми входами шестого 280 и седьмого 281 элементов И, четвертая 285 группа входов УФЗСР 176 соединена со второй информационной группой входов второго 254 регистра и четырьмя входами первого 260 элемента ИЛИ, выход которого соединен со сбросовым входом первого 268 триггера, третий 164 вход УФЗСР 176 соединен с разрешающим входом второго 254 регистра, причем группа выходов первого 251 счетчика соединена с группой входов первого 263 дешифратора, выход которого соединен с первым входом первого 275 элемента И, выход которого соединен с информационным входом второго 269 триггера, инверсный и прямой выходы которого соединены со вторым входом первого 275 элемента И и четвертым входом первого 256 узла REG_COUNT соответственно, выход которого соединен со входом третьего 277 элемента И, причем инверсный выход четвертого 271 триггера соединен со вторым входом пятого 279 элемента И, группа выходов второго 252 счетчика соединена с группой входов второго 264 дешифратора, выход которого соединен со вторым входом второго 261 элемента ИЛИ и первым входом восьмого 282 элемента И, выход которого соединен с информационным входом шестого 273 триггера, инверсный и прямой выходы которого соединены со вторым входом восьмого 282 элемента И и с информационным входом седьмого 274 триггера и первым входом девятого 283 элемента И, выход которого соединен с четвертыми входами второго 257 и третьего 258 узлов REG_COUNT, инверсный выход седьмого 274 триггера соединен со вторым входом девятого 283 элемента И, выход второго 261 элемента ИЛИ соединен со сбросовым входом второго 252 счетчика.

Узел коммутации (УК) 132 содержит счетчик 286, триггер 287, элемент ИЛИ 288, первый 289 элемент И, второй 290 элемент И, коммутатор 291, инвертор 292, выход которого соединен с первым входом первого 290 элемента И, выход которого соединен с первым входом элемента ИЛИ 288, выход которого соединен с первым входом второго 289 элемента И, выход которого соединен с разрешающим входом счетчика 286, группа выходов которого соединена с первой группой входов коммутатора 291, первый и второй выходы которого являются первой 142 группой выходов УК 132, вторая 143 группа выходов которого соединена с третьим и четвертым выходами коммутатора 291, пятый и шестой выходы которого являются третьей 144 группой выходов УК 132, четвертая 145 группа выходов которого соединена с седьмым и восьмым выходами коммутатора 291, первая группа выходов которого является пятой 160 группой выходов УК 132, первый 161 выход которого соединен с девятым выходом коммутатора 291 и вторым входом элемента ИЛИ 288, третий вход которого соединен с первым входом коммутатора 291 и является первым сигналом первой 141 группы входов УК 132, второй сигнал которой соединен со вторым входом коммутатора 291, десятый и одиннадцатый выходы которого являются вторым 162 и третьим 163 выходами УК 132, вторая 146, третья 147, четвертая 148 и пятая 149 группы входов которого соединены со второй, третьей, четвертой и пятой группами входов коммутатора 291, третий, четвертый и пятый входы которого являются шестой 150 группой входов УК 132, седьмая 151 группа входов которого соединена с шестым, седьмым и восьмым входами коммутатора 291, девятый, десятый и одиннадцатый входы которого являются восьмой 152 группой входов УК 132, девятая 153 группа входов которого соединена с двенадцатым, тринадцатым и четырнадцатым входами коммутатора 291, причем десятая 155 группа входов УК 132 соединена со входом инвертора 292 и со вторым входом первого 290 элемента И, первый 156 вход УК 132 соединен с тактовыми входами счетчика 286 и триггера 287, прямой и инверсный выходы которого соединены со вторым входом второго 289 элемента И и с информационным входом триггера 287 соответственно, второй 124 вход УК 132 соединен со сбросовыми входами счетчика 286 и триггера 287.

Таймер синхронизации (ТС) 175 содержит константу 293, группу элементов И 294, первый 295 регистр, второй 296 регистр, узел REG_COUNT 297, группу элементов ИЛИ 298, первый 299 элемент И, второй 300 элемент И, третий 301 элемент И, четвертый 302 элемент И, пятый 303 элемент И, шестой 304 элемент И, седьмой 305 элемент И, восьмой 306 элемент И, девятый 307 элемент И, десятый 308 элемент И, одиннадцатый 309 элемент И, двенадцатый 310 элемент И, тринадцатый 311 элемент И, первый 312 элемент ИЛИ, второй 313 элемент ИЛИ, выход которого соединен с первым входом узла REG_COUNT 297, группа выходов которого соединена с первыми группами входов группы элементов ИЛИ 298 и вторым 296 регистром, группа выходов которого соединена со второй группой входов группы элементов ИЛИ 298, группа выходов которого является первой 138 группой выходов ТС 175, выход 315 которого соединен с выходом узла REG_COUNT 297 и с первыми входами седьмого 305 и девятого 307 элементов И, выходы которых соединены с первыми входами тринадцатого 311 элемента И и первого 312 элемента ИЛИ соответственно, выходы которых соединены с первыми входами двенадцатого 310 и десятого 308 элементов И соответственно, выход которого соединен со вторым входом двенадцатого 310 элемента И, выход которого соединен с разрешающим входом второго 296 регистра, с первым входом четвертого 302 элемента И и со вторым входом узла REG_COUNT 297, третий вход которого соединен с выходом четвертого 302 элемента И, второй вход которого соединен с первыми входами второго 300 и третьего 301 элементов И и является первым сигналом четвертой 141 группы входов, второй сигнал которой соединен с первыми входами пятого 303 и первого 299 элементов И, выходы которых соединены с третьим входом двенадцатого 310 элемента И и с разрешающим входом первого 295 регистра, тактовый вход которого соединен с тактовыми входами второго 296 регистра и узла REG_COUNT 297 и является первым 156 входом ТС 175, второй вход 124 которого соединен со сбросовыми входами первого 295 и второго 296 регистров и четвертым входом узла REG_COUNT 297, причем группа выходов константы 293 соединена с первой группой входов группы элементов И 294, выходы которых соединены с информационной группой входов первого 295 регистра, второй разрешающий вход которого соединен с выходом второго 300 элемента И, второй вход которого соединен со вторым входом первого 299 элемента И и является первым сигналом третьей 140 группы входов, второй сигнал которой соединен со вторым входом третьего 301 элемента И, выход которого соединен с разрешающим входом второго регистра 296, причем первая 139 группа входов ТС 175 соединена со второй группой входов группы элементов И 294, первый сигнал второй 314 группы входов ТС 175 соединен с первыми инверсными входами шестого 304, седьмого 305, восьмого 306 и десятого 308 элементов И, второй сигнал которой соединен со вторыми входами седьмого 305 и девятого 307 элементов И, третий сигнал которой соединен со вторыми инверсными входами шестого 304 и седьмого 305 элементов И, с прямым входом восьмого 306 элемента И и третьим входом девятого 307 элемента И, четвертый сигнал которой соединен со вторым входом первого 312 элемента ИЛИ, пятый сигнал которой соединен со вторым входом пятого 303 элемента И, шестой сигнал которой соединен со вторыми инверсными входами восьмого 306 и десятого 308 элементов И, третий 158 вход ТС 175 соединен с прямым входом шестого 304 элемента И и со вторым входом тринадцатого 311 элемента И, четвертый 7 вход ТС 175 соединен со вторым входом десятого 308 элемента И и первым входом одиннадцатого 309 элемента И, выход которого соединен с первым входом второго 313 элемента ИЛИ, второй вход которого соединен с выходом шестого 304 элемента И, второй вход одиннадцатого 309 элемента И соединен с выходом восьмого 306 элемента И, выход пятого 303 элемента И соединен с третьим входом двенадцатого 310 элемента И, причем группа выходов первого регистра 295 соединена с третьей группой входов группы элементов ИЛИ 298 и с группой входов узла REG_COUNT 297.

Узел 133 RCP-2 содержит входной регистр 316, выходной регистр 317, регистр команд 318, регистр протокола 319, формирователь контрольной суммы CRC 320, формирователь адреса 321, счетчик слов 322, МС 323, узел команд модификации 324, первый 325 мультиплексор, второй 326 мультиплексор, первый 327 элемент ИЛИ, второй 328 элемент ИЛИ, выход которого соединен с первым входом формирователя адреса 321, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами входного регистра 316, выходного регистра 317, формирователя контрольной суммы CRC 320, регистра команд 318, регистра протокола 319, счетчика слов 322, МС 323, узла команд модификации 324, второго 326 мультиплексора и являются первым 156 и вторым 124 входами узла 133 RCP-2, первый 164 выход которого соединен с первым выходом узла команд модификации 324, второй и третий выходы которого являются первым и вторым сигналами третьей 141 группы выходов узла 133 RCP-2, третий сигнал которой соединен с выходом входного регистра 316, первая группа выходов которого соединена с первыми группами входов регистра протокола 319, регистра команд 318, узла команд модификации 324 и второго 326 мультиплексора, группа выходов которого соединена с первыми группами входов формирователя контрольной суммы CRC 320 и выходного регистра 317, первый выход которого соединен с первым входом второго 328 элемента ИЛИ и является четвертым сигналом третьей 141 группы выходов узла 133 RCP-2, первая 139 группа выходов которого соединена с первой группой выходов узла команд модификации 324, вторая группа выходов которого соединена с первой группой входов первого 325 мультиплексора, группа выходов которого соединена со второй группой входов второго 326 мультиплексора, третья группа входов которого соединена с группой выходов формирователя контрольной суммы CRC 320, первый вход которого соединен с первым входом узла команд модификации 324, вторым входом второго 328 элемента ИЛИ и является первым сигналом первой группы выходов МС 323, второй и третий сигналы являются второй группой входов регистра команд 318, вторая группа выходов которого соединена с четвертой группой входов второго 326 мультиплексора, пятая группа входов которого соединена со второй группой выходов МС 323, третья группа выходов которой соединена с группой входов формирователя адреса 321, первая группа выходов которого соединена со второй группой входов выходного регистра 317, группа выходов которого является четвертой 154 группой выходов узла 133 RCP-2, вторая 140 группа выходов которого соединена с третьей группой входов регистра команд 318, четвертая группа выходов которого соединена со второй группой входов узла команд модификации 324, третья группа выходов которого соединена с третьей группой входов регистра команд 318, с третьим входом МС 323 и с первым и вторым входами первого 327 элемента ИЛИ, выход которого соединен с первым входом регистра протокола 319, первая группа выходов которого соединена со второй группой входов первого 325 мультиплексора, вход которого соединен с первым выходом регистра команд 318, вход которого соединен со вторым входом узла команд модификации 324 и с выходом формирователя адреса 321, вторая группа выходов которого соединена со второй группой входов регистра протокола 319, вторая, третья и четвертая группы выходов которого соединены со второй, третьей и четвертой группами входов МС 323, четвертая группа выходов которой соединена с третьей группой входов выходного регистра 317, второй выход которого соединен с первым входом МС 323, пятая группа выходов которой соединена с третьей группой входов узла команд модификации 324, третий, четвертый и пятый входы которого являются второй 159 группой входов узла 133 RCP-2, третья 160 группа входов которого соединена с первой группой входов входного регистра 316, вторая группа выходов которого соединена с третьей группой входов регистра протокола 319 и группой входов счетчика слов 322, группа выходов которого соединена с четвертой группой входов регистра протокола 319 и шестой группой входов второго 326 мультиплексора, выход которого соединен со вторым входом формирователя контрольной суммы CRC 320 и первым входом выходного регистра 317, второй вход которого является пятым 163 входом узла 133 RCP-2, третий 161 и четвертый 162 входы которого являются первым и вторым входами входного регистра 316, вторая группа входов которого соединена с шестой группой выходов МС 323, второй вход которой соединен с выходом регистра протокола 319 и является первым сигналом пятой 155 группы выходов узла 133 RCP-2, второй сигнал которой соединен с третьим выходом выходного регистра 317, причем третий вход первого 327 элемента ИЛИ является первым сигналом первой группы выходов регистра команд 318, которая соединена с первой группой входов МС 323, а второй сигнал первой группы выходов регистра команд 318 соединен с шестым входом узла команд модификации 324, седьмая группа выходов МС 323 соединена с пятой группой входов регистра протокола 319, первая 138 группа входов узла 133 RCP-2 соединена с четвертой группой входов узла команд модификации 324.

Узел команд модификации 324 содержит регистр модификации 329, схему модификации 330, генератор TIMEOUT 331, МС 332, мультиплексор 333 и формирователь чтения 334, группа выходов которого является второй 335 группой выходов узла команд модификации 324, первая 139 группа выходов которого соединена с выходом мультиплексора 333, первая группа входов которого соединена с первой группой входов схемы модификации 330 и является первой 336 группой входов узла команд модификации 324, третья 337 группа выходов которого является первым, вторым и третьим выходами МС 332, четвертый выход которой соединен с первым входом регистра модификации 329, группа выходов которого соединена со второй группой входов схемы модификации 330, группа выходов которой соединена со второй группой входов мультиплексора 333, тактовый вход которого соединен с тактовыми входами регистра модификации 329, генератора TIMEOUT 331, МС 332, формирователя чтения 334 и является тактовым входом 156 узла команд модификации 324, сбросовый вход 124 которого соединен со сбросовыми входами регистра модификации 329, генератора TIMEOUT 331, МС 332 и формирователя чтения 334, первый вход которого соединен с пятым выходом МС 332, группа входов которого является второй 338 группой входов узла команд модификации 324, первый и второй сигналы которой соединены со входами схемы модификации 330 и мультиплексора 333, причем первый 164 выход узла команд модификации 324 соединен с первым входом генератора TIMEOUT 331 и шестым выходом МС 332, седьмой выход которой соединен со вторым входом генератора TIMEOUT 331 и является первым сигналом третьей группы выходов 141 узла команд модификации 324, второй сигнал которой соединен с третьим входом генератора TIMEOUT 331 и восьмым выходом МС 332, первый вход которой является первым сигналом пятой группы входов 159 узла команд модификации 324, третья 339 группа входов которого соединена со вторыми входами формирователя чтения 334 и МС 332, третий вход которой соединен с выходом генератора TIMEOUT 331, четвертый вход которого соединен с четвертым входом МС 332 и является вторым сигналом пятой группы входов 159 узла команд модификации 324, третий сигнал которой соединен с пятыми входами генератора TIMEOUT 331 и МС 332, шестой и седьмой входы которой являются вторым 340 и шестым 341 входами узла команд модификации 324, первый 342 вход которого соединен с шестым входом генератора TIMEOUT 331, причем четвертая 138 группа входов узла команд модификации 324 соединена с группами входов регистра модификации 329 и формирователя чтения 334.

Узел формирования разрешения обмена данными (УФРОД) 178 содержит первый 343 счетчик, второй 344 счетчик, третий 345 счетчик, первый 346 триггер, второй 347 триггер, третий 348 триггер, первый 349 элемент ИЛИ, второй 350 элемент ИЛИ, третий 351 элемент ИЛИ, первый 352 элемент И, второй 353 элемент И, третий 354 элемент И, четвертый 355 элемент И, пятый 356 элемент И, шестой 357 элемент И, седьмой 358 элемент И, восьмой 359 элемент И, выход которого соединен с первым входом третьего 351 элемента ИЛИ, выход которого соединен с информационным входом третьего 348 триггера, выход которого является первым сигналом второй 159 группы выходов УФРОД 178, второй сигнал которой соединен с выходом первого 346 триггера, информационный вход которого соединен с выходом первого 349 элемента ИЛИ, группа входов которого является второй 140 группой входов УФРОД 178, первый и второй сигналы третьей 141 группы входов которого соединены с первыми входами первого 352 и второго 353 элементов И, выходы которых соединены с информационными входами второго 344 и третьего 345 счетчиков соответственно, тактовые входы которых соединены между собой и соединены с тактовыми входами первого 343 счетчика, первого 346, второго 347 и третьего 348 триггеров и является первым 156 входом УФРОД 178, второй 124 вход которого соединен со сбросовыми входами первого 343, второго 344 и третьего 345 счетчиков, первого 346 и третьего 348 триггеров и с первым входом второго 350 элемента ИЛИ, выход которого соединен со сбросовым входом второго 347 триггера, выход которого является третьим сигналом второй 159 группы выходов УФРОД 178, четвертый 164 вход которого соединен с первым входом четвертого 355 элемента И, со вторыми входами первого 352 и второго 353 элементов И, с инверсным входом второго 350 элемента ИЛИ и с информационным входом первого 343 счетчика, выходы которого соединены с инверсными входами третьего 354 элемента И, выход которого соединен со вторым входом четвертого 355 элемента И, выход которого соединен с информационным входом второго 347 триггера, инверсный выход которого соединен с третьим входом четвертого 355 элемента И, причем второй сигнал третьей 141 группы входов УФРОД 178 соединен с первым входом восьмого 359 элемента И, второй вход которого соединен с выходом шестого 357 элемента И, инверсные и прямой входы которого соединены с выходами третьего 345 счетчика, причем первый сигнал третьей 141 группы входов УФРОД 178 соединен с первым входом седьмого 358 элемента И, второй вход которого соединен с выходом пятого 356 элемента И, инверсные и прямой входы которого соединены с выходами второго 344 счетчика, выход седьмого 358 элемента И соединен со вторым входом третьего 351 элемента ИЛИ.

Параллельная вычислительная система с программируемой архитектурой работает следующим образом.

ПВС предназначена для работы в составе многократно резервированной вычислительной структуры комплекса приема и обработки информации бортового оборудования.

Структурная схема ПВС приведена на фиг.1.

ПВС имеет следующий состав:

Каждый из микропроцессоров имеет свое поле памяти, которое состоит из ДОЗУ 512 Мбайт, ОЗУ 8 Мбайт и Flash 4 Мбайт. Микропроцессоры и устройства ввода-вывода связаны между собой через высокоскоростные коммутируемые Link-интерфейсы.

Внешние связи включают в себя:

- прием 8 дублированных сигналов прерываний, в т.ч. метки времени 1 с (7);

- выдачу 2-х дублированных сигналов прерываний (89);

- две группы входов 54,56 и выходов 55,57 Link- интерфейса для обмена с другими ПВС;

- 4-канальный отладочный интерфейс JTAG (8);

- две группы входов-выходов МКО (112, 113);

- четыре группы входов (107, 108, 109, 110) и выходов (103, 104, 105, 106) Fibre channel.

Характеристики управляющей и обрабатывающей подсистем ПВС представлены на фиг.56. Внешние и внутренние интерфейсы представлены на фиг.57.

Важнейший элемент ПВС является система передачи информации.

Обмен информацией между микропроцессорами и системным контроллером осуществляется с помощью интерфейса SpaceWire. Системный контроллер обеспечивает прием запросов на прерывание от четырех микропроцессоров «мультикор» 1, 2, 3, 4, контроллера МКО (Мультиплексного Канала Обмена) 31, контроллера FC (Fibre Channel) 26 и с внешних входов. Имеет собственные внутренние источники прерываний (прерывания от программируемого таймера синхронизации, блока формирования задержанных прерываний и блока формирования обобщенных прерываний) и вырабатывает выходные сигналы запросов на прерывание на микропроцессоры «мультикор» и внешние выходы.

Структурная схема системного контроллера 17 приведена на фиг.2.

Системный контроллер 17 выполняет следующие функции:

- Инициализацию ПВС;

- Счет относительного времени;

- Прием и фиксацию сигналов запроса на прерывание 7 от внешних устройств, микропроцессоров 1, 2, 3, 4, контроллера МКО 31 и контроллера Fibre Channel 26;

- Выдачу сигналов запроса на прерывание в микропроцессоры и внешние устройства.

Системный контроллер 17 состоит из следующих узлов:

- узел формирования зап/чт в регистры коммуникационных систем на основе LINK-интерфейсов (RCP-2) 133;

- узел формирования сигналов инициализации и тактовых сигналов (УФСИТС) 135;

- узел формирования задержанного сигнала реинициализации (УФЗСР) 176;

- таймера синхронизации (ТС) 175;

- узлы приема, фиксации и выдачи сигналов прерывания (УПФВСПi) 171, 172, 173, 174;

- узел формирования повторных сигналов (УФПС);

- узел формирования обобщенных сигналов (УФОС);

- узел формирования задержанных сигналов (УФЗС);

- узел приема и фиксации сигналов инициализации (УПФСИ) 136;

- узел формирования сигнала программной инициализации (УФСПИ) 137.

Системный контроллер имеет 4 канала SpaceWire. Источниками прерываний являются внешние входы и внутрисистемный таймер синхронизации.

SpaceWire - это перспективная системообразующая технология для высокоскоросной коммуникации и комплексирования бортовых систем аэрокосмических аппаратов. SpaceWire разрабатывалась в соответствии с такими требованиями аэрокосмических применений, как высокие скорости передачи информации, малые задержки доставки сообщений, устойчивость к отказам и сбоям, низкое энергопотребление, электромагнитная совместимость, компактная реализация в СБИС, поддержка систем реального времени и системных функций бортовых комплексов. Разработка технологии SpaceWire базировалась на трех стандартах: IEEE 1355-1995 [10], TIA/EIA-644 [11] и IEEE Standard 1596.3-1996 [12].

Микропроцессор 1 с системным контроллером 17 связаны дуплексным прямым каналом связи (точка - точка). S- и D-сигналы передаются каждый по отдельной дифференциальной паре. Линии передачи - однонаправленные, поэтому всего в системном контроллере 17 две дифференциальные пары, для каждого микропроцессора. Микропроцессор 1 принимает данные, кодирует их и отправляет в свой передатчик. На другом конце связи в системном контроллере 17 (блок SW 128) данные принимает приемник 202 и передает девятиразрядный код 200 в узел SW_LPORT 179, где данные преобразуются в 32-разрядные слова и по шине 185 записываются в FIFO 184. Блок SW 128 управляет соединением и потоком данных в канале, обнаруживает рассоединение, восстанавливает соединение после сбоев. Передаваемые данные - непрерывные потоки информации или сообщения - для передачи по сети SpaceWire разбивают на пакеты. Пакет SpaceWire включает поле заголовка, содержащее адрес назначения(в нашем случае его нет), и поле полезной нагрузки с данными пользователя, ограниченное маркером конца пакета. Пакеты передаются по сети друг за другом без каких-либо разделителей и интервалов. В качестве начала заголовка пакета всегда рассматривается его первый символ. Полезная нагрузка - это данные, т.е. информация, от источника к узлу назначения. Закрывает пакет маркер конца пакета, указывая также, является ли пакет правильным (ЕОР, End of Packet) или транслируется с уже обнаруженной ошибкой (ЕЕР, Error End of Packet).

Пакеты формируются последовательностью так называемых символов - элементарных структур данных в стандарте SpaceWire. Определены символы данных и символы управления фиг.30. Они имеют разную длину в битах, что позволяет экономить пропускную способность канала при передаче управляющих кодов.

Байт данных при передаче по каналу SpaceWire кодируется 10-битным «символом данных» фиг.30. К 8 битам исходного байта данных добавляется бит признака символа данных и бит контроля четности. Первый разряд любого символа - это бит контроля четности (P). За ним следует флаг типа символа (данных или управления, 0 или 1 соответственно). Символы передаются по линку SpaceWire младшими битами вперед.

Предусмотрено четыре символа управления - конец пакета (ЕОР), конец пакета с ошибкой (ЕЕР) (он нужен, чтобы пометить пакет, заведомо содержащий ошибки), символ управления потоком (FCT, Flow Control Token) и символ расширения (ESC). Символ расширения ESC используется для создания дополнительных управляющих кодов. Он является признаком того, что следующий за ним один символ данных или один символ управления должен рассматриваться как продолжение данного символа ESC. Сочетание символов ESC и FCT образует NULL - код, который транслируется всегда, если в канале не передаются символы данных и управления (это позволяет сохранять активность канала и определить ошибку рассоединения). В пакеты входят только N-Char, к которым относятся символы данных, а также символы конца пакета ЕОР и ЕЕР.

Дополнительным управляющим кодом является маркер времени, в котором за символом ESC следует информационный символ, в котором два старших разряда со значениями Т6Т7=00 (Т6 - младший разряд) являются индикатором маркера времени. Вторым дополнительным управляющим кодом является код распределенного прерывания, в котором разряды придаваемого одного символа данных Т6Т7=10. Третьим дополнительным управляющим кодом является код подтверждения получения кода распределенного прерывания, в котором разряды придаваемого одного символа данных Т6Т7=01.

Бит проверки четности для каждого передаваемого поддерживает надежность функционирования канала. Поле контроля для бита четности включает 8 предшествующих бит данных(если предыдущим был символ данных) или два символа управления, собственно бит четности и следующий за ним флаг типа символа. Бит четности устанавливается так, чтобы сумма всех единиц в поле контроля была нечетной. Бит контроля четности формируется непосредственно в передатчике и зависит от предыдущих символов.

Уровень обмена в сети SpaceWire обеспечивает инициализацию и перезапуск DS-связи, управление потоком данных между двумя узлами, обнаружение ошибок и сбоев, выполнение процедур восстановления соединения. После того, как соединение восстановлено, оно поддерживается постоянной передачей по нему символов данных, управляющих кодов, а при их отсутствии - кодов NULL. Если сигналы в связи не изменяются в течение 850 нс, это рассматривается как разрыв соединения.

Управление потоком данных в сети во избежание переполнения буферов приемников реализуется с помощью символов управления потоком FCT. Каждый переданный символ FCT указывает на то, что в буфере приемника есть место для приема 8 символов данных (N-Char), но не свыше 7. Передатчику не разрешено передавать символов больше, чем позволяет поместить буфер приемника, о чем последний и сообщает посредством FCT.

На уровне обмена регулируется и очередность передачи символов в канал, обеспечивая приоритетность передачи управляющих кодов, в том числе маркеров времени и кодов прерывания/подтверждения. Управляющие символы L-Char и управляющие коды передаются, не дожидаясь завершения трансляции очередного пакета - они как бы разрезают поток данных, обеспечивая тем самым независимость передачи управляющих кодов от общей загрузки сети. В SpaceWire на сигнальном уровне используется DS-кодирование. При DS-кодировании данные передаются по линии данных (D) в прямом коде, в то время как сигнал на линии строба (S) изменяет свое значение каждый раз, когда данные остаются неизменными в очередном битовом интервале (фиг.30). Таким образом, в каждом такте меняется один из символов - либо D, либо S. DS-кодирование обладает свойством самосинхронизации: в DS-сигналах закодирован синхросигнал, который восстанавливается на приемной стороне элементарной операцией «исключающее ИЛИ» над сигналами D и S. В результате DS-кодирование позволяет передавать данные в широком диапазоне скоростей (в стандарте SpaceWire - от 2 до 400 Мбит/с) без предварительного согласования скоростей между приемником и передатчиком.

Для поддержания единого системного времени в сети введен специальный управляющий код - маркер времени. Он используется для поддержания единого системного времени в сети и передачи изохронных флагов управления. Маркер времени образован символом ESC и символом данных, 6 младших разрядов в символе данных (Т0-Т5) содержат код времени, два старших - признаки маркера времени (00).

Диаграмма состояний интерфейса связи SpaceWire представлена на фиг.31.

Функциональная схема узла SW 181 представлена на фиг.5. Алгоритм работы МС 202 узла SW 181 представлен на фиг.18.

Состояние Error Reset 2 будет установлено после сброса системы, после завершения операции связи по любой причине или если имеется ошибка в течение инициализации связи. В состоянии Error Reset 2 передатчик 204 и приемник 202 установлены в «0». Когда сигнал Reset 124 установится в «0», состояние Error Reset 2 будет оставаться в течение 6.4 мкс, после чего МС 202 перейдет в состояние Error Wait 6. Всякий раз, когда сигнал Reset 124 устанавливается в «1», МС 202 будет немедленно устанавливаться в состояние Error Reset 2, до тех пор пока сигнал Reset 124 установится в «0».

Состояние Error Wait 6 устанавливается только из состояния Error Reset 2. В состоянии Error Wait 6 прием разрешен (enable_rx) 8, передача запрещена (reset_tx) 7. МС 202 будет оставаться в течение 12.8 мкс в состоянии Error Wait 6, а затем переходит в состояние ready 11, приемник 201 принимает первый бит (т.е. первый переход, определенный на D_in 186 и S_in 187 входах приемника 201) и формирует сигнал got_bit. Если принимается код NULL, приемник 201 формирует сигнал got_null, после чего МС 202 перейдет в состояние started 16 и сформирует сигнал send_null. Если пока МС 202 находится в состоянии Error Wait 6 появляется сигнал ошибки rx_err (disconnection) или сигналы got_FCT, got_Nchar, got_time_code, то MC 202 переходит обратно в состояние Error Reset 2.

Состояние ready 11 устанавливается только из состояния Error Wait 6. В состоянии ready 11 прием разрешен (enable_rx) 13, передача запрещена (reset_tx) 7. В состоянии ready 11 интерфейс связи готов к инициализации. Если принимается код NULL, приемник 201 формирует сигнал got_null, после чего MC 202 перейдет в состояние started 16, если есть команда на начало связи. Если пока MC 202 находится в состоянии ready 11 появляется сигнал ошибки rx_err (disconnection) или сигналы got_FCT, got_Nchar, got_time_code, то MC 202 переходит обратно в состояние Error Reset 2.

Состояние started 16 устанавливается только из состояния ready 11. В состоянии started 16 прием разрешен (enable_rx) 17, передатчик 203 посылает один или несколько NULL-ов, MC 202 запускает таймер на 12.8 мкс и формирует сигнал Send_NULL. Если пока MC 202 находится в состоянии started 16, появляется сигнал ошибки rx_err (disconnection) или сигналы got_FCT, got_Nchar, got_time_code или есть переполнение таймера, то MC 202 переходит обратно в состояние Error Reset 2. Если приемник 201 формирует сигнал got_null, то MC 202 перейдет в состояние Connecting.

Состояние connecting 21 устанавливается только из состояния started 16. В состоянии connecting 21 прием разрешен (enable_rx) 22 и передача (enable_tx) 23 также разрешена, чтобы посылать NULL и FCT. Когда интерфейс связи принимает NULL и FCT, это означает, что связь установлена в обоих направлениях. Если FCT неудачно завершается в пределах 12.8 мкс, то что-то неисправно в сети соединения и MC 202 переходит в состояние Error Reset 2. Если пока MC 202 находится в состоянии connecting 21 появляется сигнал ошибки rx_err (disconnection) или сигналы got_FCT, got_Nchar, got_time_code, то MC 202 также переходит обратно в состояние Error Reset 2 и пытается соединиться еще раз. Если принимается сигнал FCT после переполнения счетчика 12.8 мкс, то формируется сигнал got_FCT и MC 202 переходит в состояние RUN 27.

Состояние RUN 27 устанавливается только из состояния connecting 21. В состоянии RUN 27 прием разрешен (enable_rx) 28 и передача (enable_tx) 29 также разрешена, чтобы посылать Time_Codes, FCTs, N-chars, L-chars и NULLs. Состояние RUN 27 является состоянием для нормальных операций, когда соединение связи будет формировать и L-chars, и N-chars, которые могут свободно проходить в обоих направлениях через связь. Связь остается в состоянии RUN 27, пока не случится ошибка или пока не заблокируется связь. Если МС 202 находится в состоянии RUN 27 и появляются сигналы ошибки rx_err (disconnection) или Credit_err, или Link_disable, то МС 202 переходит в состояние Error Reset 2 и пытается соединиться еще раз.

Приемник 201 определит ошибку разъединения err_disconnect, когда временной интервал последней передачи любого из символов D_in 186 и S_in 187 выходит за пределы временного детектора разъединения, который равен 850 нс. Разъединение не может быть обнаружено, если приемник 201 предварительно не получил по крайней мере один бит. Ошибка разъединения rx_err может быть вызвана повреждением конца связи или связь физически повреждена. Если ошибка разъединения err_disconnect случается в состоянии RUN 27, то ошибка снабжается признаком ошибка сети.

Когда YSW 181 выдает данные N-chars 200, узел SW_LPORT принимает данные и сбрасывает сигнал READY 194. Если N-chars 200 принимается, а сигнал READY 194 не сбрасывается, то формируется ошибка кредитования Credit_err (фиг.4 функциональная схема блока SW 128).

Приемник 201 может находиться в одном из четырех состояний:

- RESET - приемник 201 ничего не делает.

- Enabled - прием разрешен и приемник 201 ждет первый бит.

- GOT BIT - приемник 201 принимает первый бит и разрешает определение ошибки разъединения. Приемник 201 разрешает ожидание NULLs.

- GOT NULL - приемник 201 принимает NULL и разрешает прием NULLs, FCTs, Time-codes и N-chars. Разрешается определение ошибки разъединения, четности, отключения.

Функциональная схема блока SW 128 представлена на фиг.4. Алгоритм работы приемника 201 представлен на фиг.20, 20а, 20б.

Когда узел SW_LPORT179 готов к приему данных N-chars от приемника 201 узла SW 181, он посылает сигнал READY 194. Когда приемник 201 принимает N-chars и сигнал READY 194, он помещает N-chars на шину DATA_OUT 200 и формирует сигнал WRITE_OUT 195, по которому данные запишутся в регистр.

На позициях 8…11, 5 и 16, 17 алгоритма работы приемника 201 формируется строб приема данных. На позициях 18, 21…23, 25, 26 формируется прием первого бита. На позициях 24…32 выполняется прием последовательных данных на сдвиговый регистр Reg_in. Далее если это символы, то МС 202 выполняет сравнение принимаемых символов с константами, приведенными на фиг.30, а затем формирует сигналы got_fct, got_nchar, got_null, got_time_code в зависимости от поступающих символов, если это данные, то МС 202 устанавливает data_out (8) в «1», в data-out (7…0) переписывает Reg_in (9…2) и формирует сигнал write _out в «1».

Алгоритм работы передатчика 203 представлен на фиг.19.

Передатчик 203 может находиться в одном из четырех состояний:

- RESET - передатчик 203 ничего не делает (поз.1, 2);

- Состояние Send_null (поз.3…5), передатчик 203 передает маркер nulls;

- Состояние Send_fcts или nulls (поз.6…8), передатчик 203 передает символы управления потоком fcts или маркер NULLs;

- Состояние Send time_codes, fcts, NULLs, Nchars (поз.9…14, 15…17), передатчик готов к приему Nchars (8 символов данных), формирует сигнал Ready_out 191 и, при наличии сигнала write 192 выполняет прием данных Data_out 200 на сдвиговый регистр, а при наличии сигнала Tick выполняет прием маркера времени TIME_IN и Control на сдвиговый регистр и передачу их по выходам D_out 188 и S_out 189, затем сбрасывает сигнал Ready_out 191.

Коммутатор 132 предназначен для приема данных из 4-х микропроцессоров и передачу их в узел формирования зап/чт в регистры коммуникационных систем на основе LINK-интерфейсов (RCP-2) 133.

Функциональная схема узла коммутации 132 представлена на фиг.18.

Функциональная схема таймера синхронизации и узла формирования прерываний представлена на фиг.3.

Узел формирования прерываний состоит из 4-х одинаковых узлов приема, фиксации и выдачи сигналов прерывания (УПФВСПi) 171, 172, 173, 174 по количеству микропроцессоров.

УПФВСП содержит следующие программно-доступные регистры:

- регистр запросов на прерывание (RIRQ);

- регистры масок на прерывание (RMS0-RMS4);