Предлагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла многих устройств автоматики, вычислительной техники, систем связи и приборостроения, в т.ч. работающих при высоких температурах.

В современной микроэлектронике получили широкое распространение двухкаскадные операционные усилители (ОУ) [1-18] с простейшей архитектурой, которая включает входную дифференциальную пару транзисторов с источником опорного тока в общей эмиттерной цепи, простейшее токовое зеркало на биполярных транзисторах и классический эмиттерный повторитель на основе выходного биполярного транзистора с источником опорного тока. Благодаря простоте, такие ОУ обладают хорошими частотными характеристиками. Предлагаемое изобретение относится к данному классу ОУ.

В практических схемах ОУ входная дифференциальная пара и его выходной транзистор реализуются как на n-p-n [8-14], так и на p-n-p [1-7] биполярных транзисторах, что определяется используемыми технологическими процессами. Однако, перспективный арсенид-галлиевый техпроцесс [19], осваиваемый Минским НИИ радиоматериалов (https://mniirm.by/), обеспечивает создание только p-n-p и nJFet транзисторов. Отсутствие n-p-n транзисторов создает схемотехнические проблемы построения GaAs двухкаскадных ОУ с простейшей архитектурой. Кроме этого, данная простейшая архитектура ОУ имеет повышенный уровень систематической составляющей напряжения смещения нуля (Uсм) и требует использования n-p-n биполярных транзисторов, отсутствующих в совмещенном технологическом процессе Минского НИИ радиоматериалов. Это не позволяет создать высокотемпературные GaAs ОУ, востребованные в ряде важных отраслей науки и техники - космическом приборостроении, нефтегазовой, автомобильной и авиационной промышленности.

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в монографии «Операционные усилители для всех / Брюс Картер и Рон Манчини; пер. с англ. А.Н. Рабодзея. - М.: Додэка-XXI, 2011. - С. 445, рис. 25.5». Кроме этого, данное схемотехническое решение используется в серийных операционных усилителях LM2904W, LM2904A, LM2904AW, а также LM258, LM358. ОУ-прототип содержит первый 1 и второй 2 входы устройства, а также потенциальный выход 3, первый 4 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, второй 5 входной биполярный транзистор, база которого подключена ко второму 2 входу устройства, первый 6 токостабилизирующий двухполюсник, включенный между первой 7 шиной источника питания и объединенными эмиттерами первого 4 и второго 5 входных биполярных транзисторов, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых соединены друг с другом, база первого 8 биполярного транзистора токового зеркала соединена с коллектором этого транзистора и подключена к коллектору первого 4 входного биполярного транзистора и к базе второго 9 биполярного транзистора токового зеркала, коллектор второго 5 входного биполярного транзистора соединен с коллектором второго 9 биполярного транзистора токового зеркала и базой выходного биполярного транзистора 10, коллектор выходного биполярного транзистора 10 связан со второй 11 шиной источника питания, а его эмиттер соединен с первой 7 шиной источника питания через второй 12 токостабилизирующий двухполюсник.

Существенный недостаток ОУ - прототипа состоит в том, что он не реализуется в рамках перспективного арсенид-галлиевого технологического процесса, осваиваемого Минским НИИ радиоматериалов, из-за отсутствия n-p-n арсенид-галлиевых транзисторов [19]. Кроме этого, известный ОУ характеризуется повышенным уровнем систематической составляющей напряжения смещения нуля (десятки милливольт), что обусловлено наличием токовой ошибки ΔIΣ1 в его высокоимпедансном узле Σ1:

где gDK - крутизна усиления входного каскада ОУ со входов 1, 2 в высокоимпедансный узел Σ1.

Основная задача предлагаемого изобретения состоит в разработке схемы ОУ, которая реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы с управляющим p-n переходом. Первая дополнительная задача - создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля, что не реализуется в схеме ОУ-прототипа. Вторая дополнительная задача - построение схемы ОУ без применения интегральных резисторов, которые неудовлетворительно работают при высоких температурах. Заявляемая схема может также реализовываться на широкозонных полупроводниках (GaN, SiC).

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, а также потенциальный выход 3, первый 4 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, второй 5 входной биполярный транзистор, база которого подключена ко второму 2 входу устройства, первый 6 токостабилизирующий двухполюсник, включенный между первой 7 шиной источника питания и объединенными эмиттерами первого 4 и второго 5 входных биполярных транзисторов, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых соединены друг с другом, база первого 8 биполярного транзистора токового зеркала соединена с коллектором этого транзистора и подключена к коллектору первого 4 входного биполярного транзистора и к базе второго 9 биполярного транзистора токового зеркала, коллектор второго 5 входного биполярного транзистора соединен с коллектором второго 9 биполярного транзистора токового зеркала и базой выходного биполярного транзистора 10, коллектор выходного биполярного транзистора 10 связан со второй 11 шиной источника питания, а его эмиттер соединен с первой 7 шиной источника питания через второй 12 токостабилизирующий двухполюсник, предусмотрены новые элементы и связи - между коллектором первого 4 входного биполярного транзистора и второй 11 шиной источника питания включен первый 13 дополнительный источник опорного тока, между коллектором второго 5 входного биполярного транзистора и второй 11 шиной источника питания включен второй 14 дополнительный источник опорного тока, объединенные эмиттеры первого 8 и второго 9 биполярных транзисторов токового зеркала связаны с эмиттером выходного биполярного транзистора 10, причем первый 6 и второй 12 токостабилизирующие двухполюсники, первый 13 и второй 14 дополнительные источники опорного тока выполнены на арсенид-галлиевых полевых транзисторах с управляющим p-n переходом, а численные значения токов первого 6 токостабилизирующего двухполюсника, первого 13 и второго 14 дополнительных источников опорного тока приблизительно в 2 раза меньше тока второго 12 токостабилизирующего двухполюсника.

На чертеже фиг. 1 показана схема операционного усилителя-прототипа.

На чертеже фиг. 2 представлена схема заявляемого операционного усилителя в соответствии с формулой изобретения.

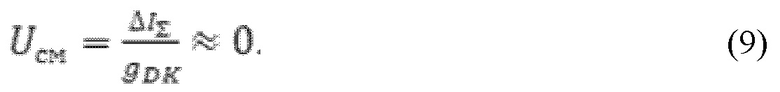

На чертеже фиг. 3 приведена схема заявляемого ОУ фиг. 2, в котором первый 6 и второй 12 токостабилизирующие двухполюсники, первый 13 и второй 14 дополнительные источники опорного тока выполнены на арсенид-галлиевых полевых транзисторах с закороченными выводами затвора и истока.

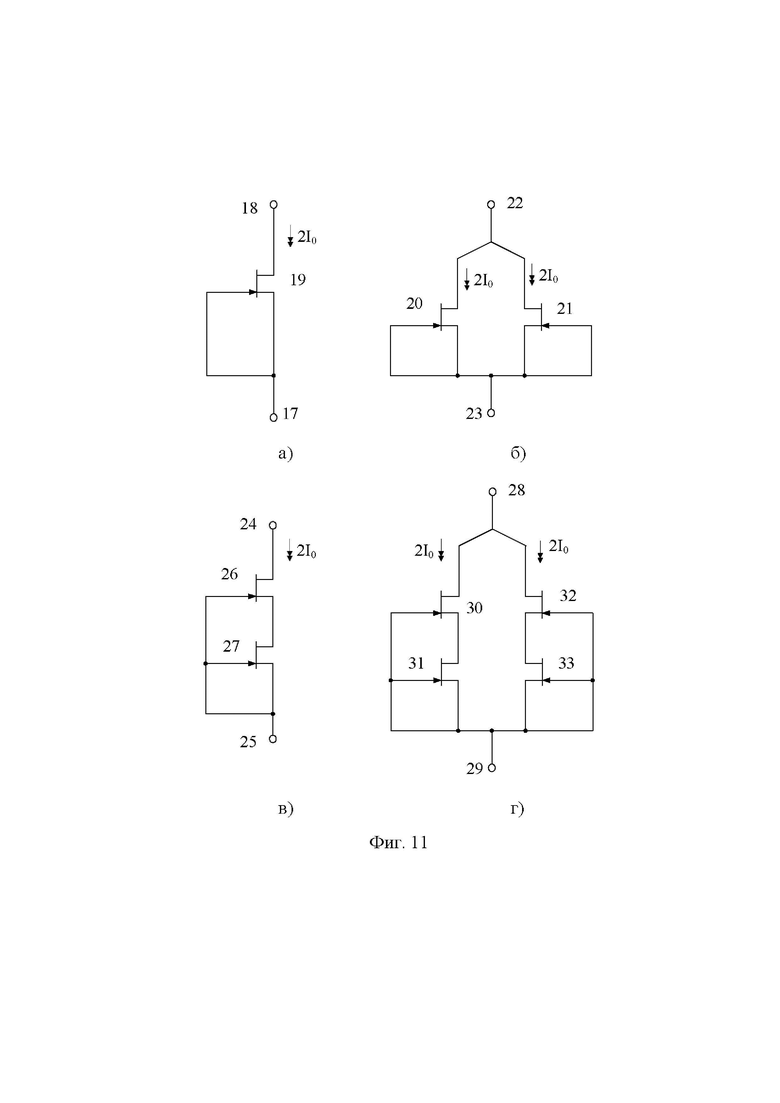

На чертеже фиг. 4 показана схема заявляемого ОУ фиг. 2, в котором первый 6 и второй 12 токостабилизирующие двухполюсники, первый 13 и второй 14 дополнительные источники опорного тока выполнены на идентичных составных арсенид-галлиевых полевых транзисторах, возможные схемы которых представлены на чертеже фиг. 11.

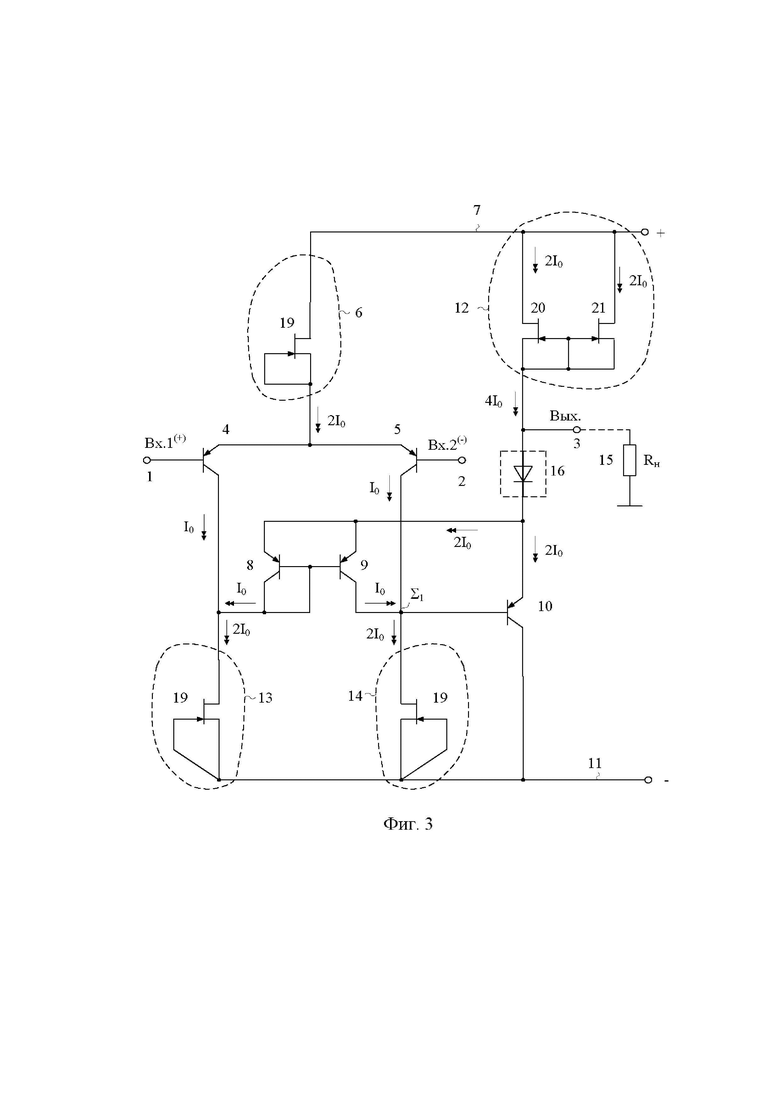

На чертеже фиг. 5 представлена схема ОУ-прототипа для математического анализа ее систематической составляющей напряжения смещения нуля.

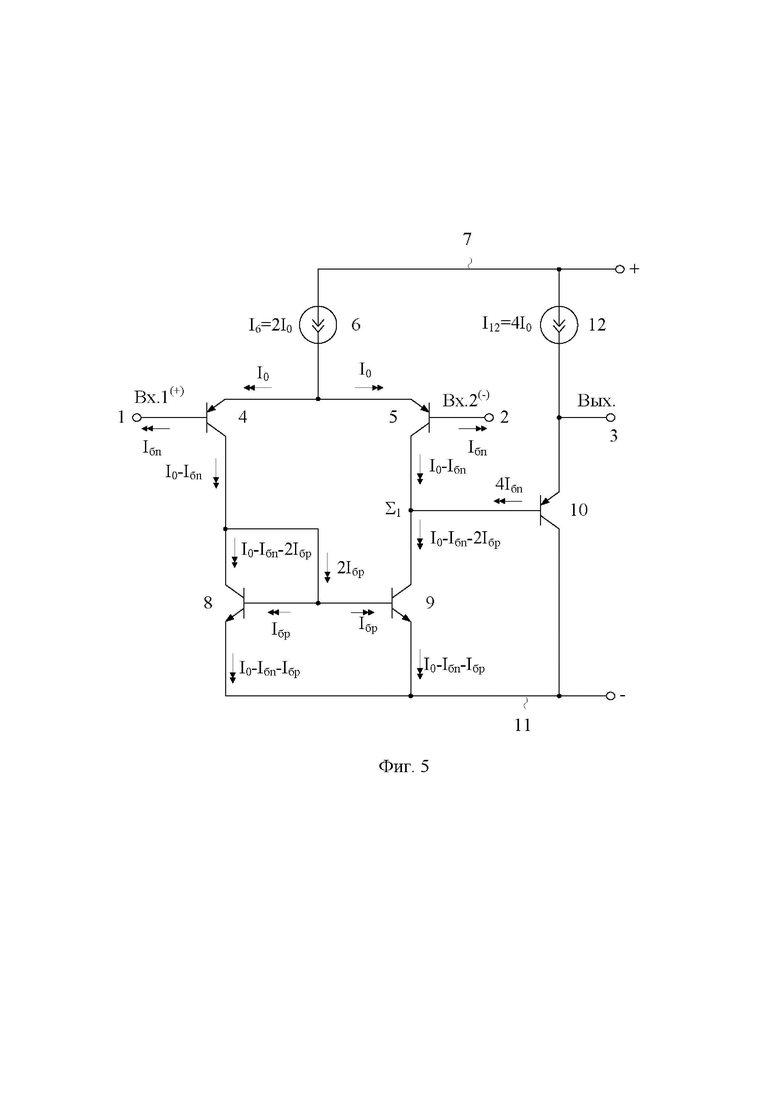

На чертеже фиг. 6 приведена схема заявляемого ОУ для математического анализа его систематической составляющей напряжения смещения нуля.

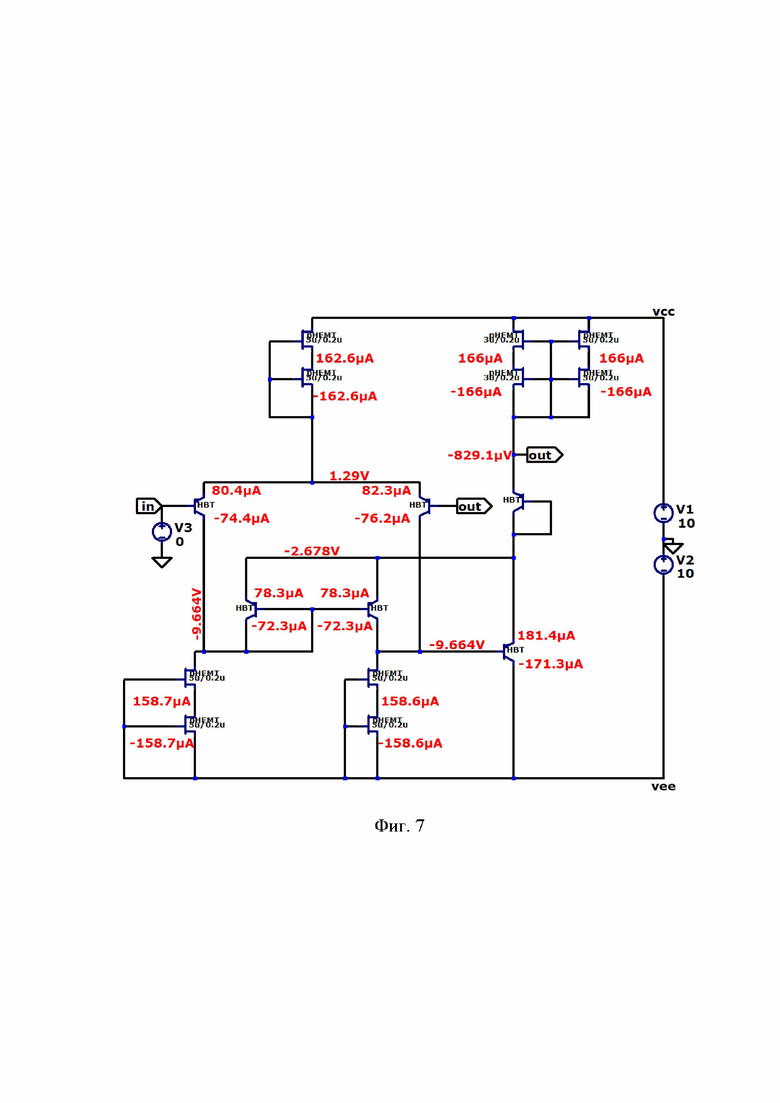

На чертеже фиг. 7 показан статический режим ОУ фиг. 4 в среде LTSpice на GaAs транзисторах при 27°С, ширине их канала 3u, шинах питания V1=V2=±10В.

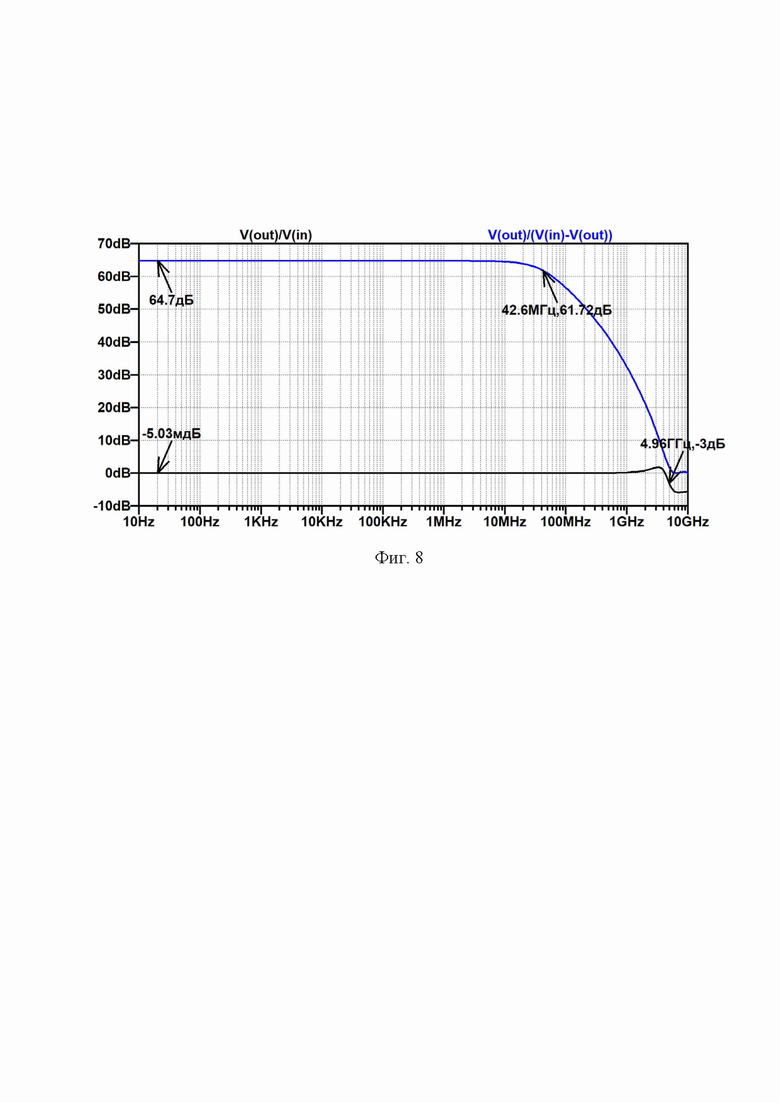

На чертеже фиг. 8 представлена логарифмическая амплитудно-частотная характеристика ОУ фиг. 7.

На чертеже фиг. 9 приведен статический режим ОУ-прототипа в среде LTSpice при одинаковых с заявляемым устройством токах источников опорного тока. Эти результаты моделирования показывают, что систематическая составляющая напряжения смещения нуля (Uсм=14,97 мВ) более чем на порядок превышает аналогичный параметр заявляемого ОУ фиг. 7 (829 мкВ).

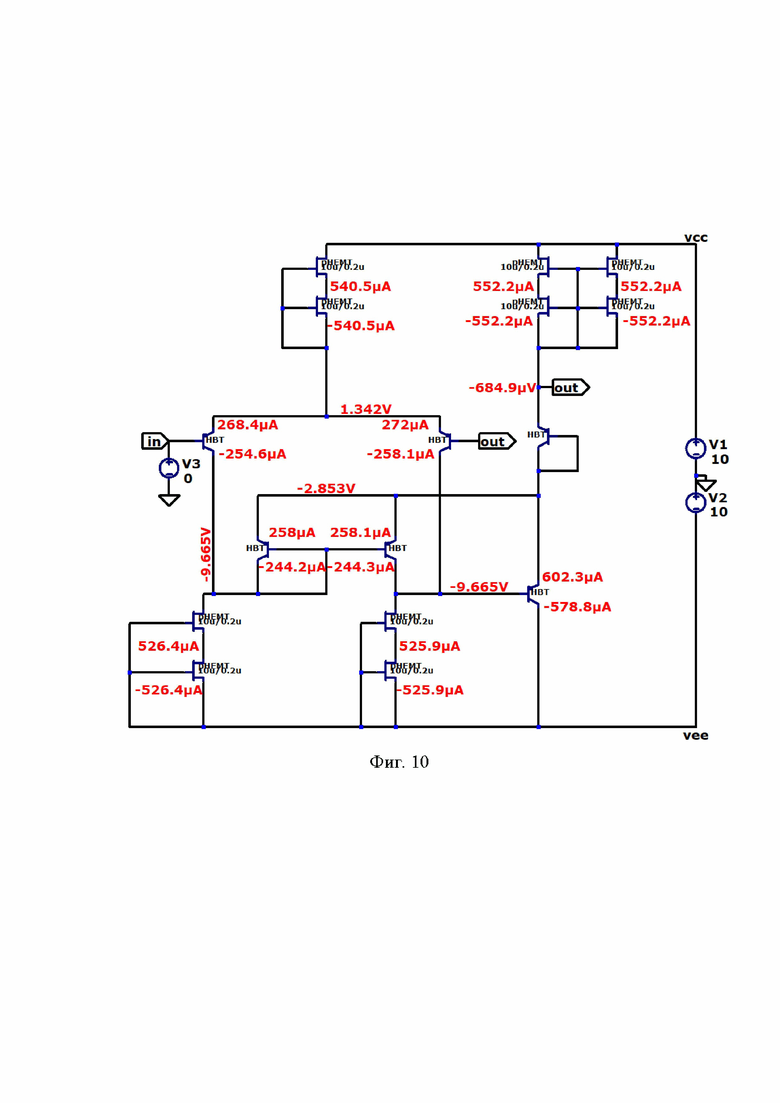

На чертеже фиг. 10 представлен статический режим ОУ фиг. 4 в среде LTSpice на GaAs транзисторах при ширине канала JFET 10u. Данное моделирование показывает, что несмотря на увеличение статического тока JFET транзисторов напряжение смещения нуля ОУ остается малым и не превышает 685 мкВ.

На чертеже фиг. 11 приведены рекомендуемые варианты построения первого 6 токостабилизирующего двухполюсника (а, в), а также второго 12 токостабилизирующего двухполюсника (б, г). Токостабилизирующий двухполюсник фиг. 11а имеет узлы 17 и 18, по которым он включается в конкретную схему ОУ, и содержит арсенид-галлиевый полевой транзистор 19 с закороченным затвором и истоком. Для построения второго 12 токостабилизирующего двухполюсника рекомендуется использовать схему фиг.11б с полевыми транзисторами 20 и 21 и узлами 22, 23 для включения в схему ОУ. На чертеже фиг.11в показан вариант построения первого 6 токостабилизирующего двухполюсника с узлами включения в схему ОУ 24 и 25 и полевыми транзисторами 26, 27. На чертеже фиг.11г показан вариант построения второго 12 токостабилизирующего двухполюсника с узлами включения в схему ОУ 28, 29 и полевыми транзисторами 30-33.

Безрезистивный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля фиг. 2 содержит первый 1 и второй 2 входы устройства, а также потенциальный выход 3, первый 4 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, второй 5 входной биполярный транзистор, база которого подключена ко второму 2 входу устройства, первый 6 токостабилизирующий двухполюсник, включенный между первой 7 шиной источника питания и объединенными эмиттерами первого 4 и второго 5 входных биполярных транзисторов, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых соединены друг с другом, база первого 8 биполярного транзистора токового зеркала соединена с коллектором этого транзистора и подключена к коллектору первого 4 входного биполярного транзистора и к базе второго 9 биполярного транзистора токового зеркала, коллектор второго 5 входного биполярного транзистора соединен с коллектором второго 9 биполярного транзистора токового зеркала и базой выходного биполярного транзистора 10, коллектор выходного биполярного транзистора 10 связан со второй 11 шиной источника питания, а его эмиттер соединен с первой 7 шиной источника питания через второй 12 токостабилизирующий двухполюсник. Между коллектором первого 4 входного биполярного транзистора и второй 11 шиной источника питания включен первый 13 дополнительный источник опорного тока, между коллектором второго 5 входного биполярного транзистора и второй 11 шиной источника питания включен второй 14 дополнительный источник опорного тока, объединенные эмиттеры первого 8 и второго 9 биполярных транзисторов токового зеркала связаны с эмиттером выходного биполярного транзистора 10, причем первый 6 и второй 12 токостабилизирующие двухполюсники, первый 13 и второй 14 дополнительные источники опорного тока выполнены на арсенид-галлиевых полевых транзисторах с управляющим p-n переходом, а численные значения токов первого 6 токостабилизирующего двухполюсника, первого 13 и второго 14 дополнительных источников опорного тока приблизительно в 2 раза меньше тока второго 12 токостабилизирующего двухполюсника.

Двухполюсник 15 моделирует свойства нагрузки.

Определим численные значения систематической составляющей напряжения смещения нуля ОУ-прототипа фиг. 1. Для вывода формул, определяющих Uсм, рассмотрим схему фиг. 5 при таких же уровнях статических токов первого 6 и второго 12 токостабилизирующих двухполюсников, что и в схеме заявляемого ОУ фиг. 6.

Для высокоимпедансного узла Σ1 (фиг. 5) можно составить следующие уравнения по первому закону Кирхгофа

где Iбр - ток базы первого 8 и второго 9 биполярных транзисторов токового зеркала,

Iбn - ток базы первого 4, второго 5 входных p-n-p биполярных транзисторов и выходного p-n-p биполярного транзистора 10 при соответствующих токах эмиттера,

- температурный потенциал,

- температурный потенциал,

I0 - заданный разработчиком статический ток транзисторов,

- крутизна усиления входного дифференциального каскада на транзисторах 4, 5 со входов 1, 2 к высокоимпеданскному узлу Σ1, причем

- крутизна усиления входного дифференциального каскада на транзисторах 4, 5 со входов 1, 2 к высокоимпеданскному узлу Σ1, причем

Таким образом, из уравнения (4) следует, что систематическая составляющая напряжения смещения нуля ОУ-прототипа принимает сравнительно большие значения (фиг. 9), что является недостатком данной архитектуры. Это подтверждается результатами компьютерного моделирования, представленными на чертеже фиг. 9.

Выполним далее аналогичный математический анализ по оценке систематической составляющей напряжения смещения нуля заявляемой схемы ОУ на основе чертежа фиг. 6. Здесь для высокоимпедансного узла Σ1 можно составить следующие уравнения:

где

Поэтому

Таким образом, токовая ошибка в высокоимпедансном узле Σ1 в предлагаемой схеме ОУ близка к нулю ( и, как следствие, эта схема ОУ имеет малые значения систематической составляющей Uсм:

и, как следствие, эта схема ОУ имеет малые значения систематической составляющей Uсм:

Кроме этого, схема ОУ на чертеже фиг. 6 имеет (в отличие от схемы ОУ-прототипа фиг. 1) идентичные напряжения коллектор-база первого 4 и второго 5 входных биполярных транзисторов. Как показано в работе [21], это является необходимым условием минимизации другой составляющей Uсм* в операционных усилителях, обусловленной коэффициентом внутренней обратной связи транзисторов входной дифференциальной пары (4,5).

Предлагаемая схема ОУ имеет несколько вариантов построения (фиг. 3, фиг. 4) первого 6, второго 12 токостабилизирующих двухполюсников, первого 13, второго 14 дополнительных источников опорного тока, которые реализуются по рекомендуемым безрезистивным схемам (фиг. 11) на основе арсенид-галлиевых полевых транзисторов. Как следствие, рассмотренный ОУ не содержит интегральных резисторов, которые имеют неудовлетворительные параметры и стабильность при повышенных температурах.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом и может использоваться для построения высокотемпературных микросхем на GaAs и других широкозонных полупроводниках (GaN, SiC), не содержащих интегральных резисторов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

Двухкаскадные ОУ с p-n-p входными транзисторами

1. Патент US 4517524, 1985 г., фирма Motorola.

2. Патент US 3434069, 1969 г., фиг. 5.

3. Патент SU 970638, 1982 г.

4. Патент US 4922208, 1990 г.

5. Патент US 4342006, 1982 г.

6. Патентная заявка US 2007/0115056, 2007 г., фиг. 2.

7. Патент US 4709216, 1987 г., фиг. 1, фиг. 2.

Двухкаскадные ОУ с n-p-n входными транзисторами

8. Патент US 5144169, 1992 г., фиг. 3.

9. Патент US 5166638, 1992 г., фиг. 1.

10. Патентная заявка US 2006/0202761, 2006 г.

11. Патент US 7541872, 2009 г., фиг. 4.

12. Патент US 4042886, 1977 г., фиг. 1.

13. Патент US 4306198, 1981 г., фиг. 2.

14. Патент ФРГ 2938994, 1980 г., фиг. 2.

ОУ с p-n-p входными транзисторами и инвертирующим выходным каскадом

15. Патент US 7646246, 2010 г., фиг. 6.

16. Патент US 3852679, 1974 г., фиг. 2.

17. Патент US 5663679, 1997 г., фиг.1.

18. Патент US 7221224, 2007 г., фиг. 4.

19. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475-488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488

20. Операционные усилители для всех / Брюс Картер и Рон Манчини; пер. с англ. А.Н. Рабодзея. - М.: Додэка-XXI, 2011. - С. 445, рис. 25.5.

21. Прокопенко Н.Н., Крюков С.В., Хорунжий А.В. Особенности проектирования аналоговых микросхем на транзисторах с малым напряжением Эрли // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов / под общ. ред. А.Л.Стемпковского. М.:ИППМ РАН, 2008. С. 324-329.

Серийные операционные усилители, в которых используется схема ОУ-прототипа

22. LM2904, LM2904A LM2904W, LM2904AW Datasheet. Low-power dual operational amplifier. STMicroelectronics. DS0508 - Rev 21 - June 2023, 28 p., fig. 2. URL: https://www.st.com/resource/en/datasheet/lm2904.pdf

23. Single Supply Dual Operational Amplifiers. LM258, LM358, LM358A, LM358E, LM2904, LM2904A, LM2904E, LM2904V, NCV2904. Semiconductor Components Industries, LLC, 2016, August, 2021 - Rev. 34. URL: https://www.onsemi.com/download/data-sheet/pdf/lm358-d.pdf

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Безрезистивный арсенид-галлиевый дифференциальный каскад и операционный усилитель на его основе с малым напряжением смещения нуля | 2023 |

|

RU2815912C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

Изобретение относится к области радиотехники. Технический результат: создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля. Для этого предложен операционный усилитель, в котором между коллектором первого (4) входного биполярного транзистора и второй (11) шиной источника питания включен первый (13) дополнительный источник опорного тока, между коллектором второго (5) входного биполярного транзистора и второй (11) шиной источника питания включен второй (14) дополнительный источник опорного тока, объединенные эмиттеры первого (8) и второго (9) биполярных транзисторов токового зеркала связаны с эмиттером выходного биполярного транзистора (10), причем первый (6) и второй (12) токостабилизирующие двухполюсники, первый (13) и второй (14) дополнительные источники опорного тока выполнены на арсенид-галлиевых полевых транзисторах с управляющим p-n переходом, а численные значения токов первого (6) токостабилизирующего двухполюсника, первого (13) и второго (14) дополнительных источников опорного тока приблизительно в (2) раза меньше тока второго (12) токостабилизирующего двухполюсника. 11 ил.

Безрезистивный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля, содержащий первый (1) и второй (2) входы устройства, а также потенциальный выход (3), первый (4) входной биполярный транзистор, база которого подключена к первому (1) входу устройства, второй (5) входной биполярный транзистор, база которого подключена ко второму (2) входу устройства, первый (6) токостабилизирующий двухполюсник, включенный между первой (7) шиной источника питания и объединенными эмиттерами первого (4) и второго (5) входных биполярных транзисторов, первый (8) и второй (9) биполярные транзисторы токового зеркала, эмиттеры которых соединены друг с другом, база первого (8) биполярного транзистора токового зеркала соединена с коллектором этого транзистора и подключена к коллектору первого (4) входного биполярного транзистора и к базе второго (9) биполярного транзистора токового зеркала, коллектор второго (5) входного биполярного транзистора соединен с коллектором второго (9) биполярного транзистора токового зеркала и базой выходного биполярного транзистора (10), коллектор выходного биполярного транзистора (10) связан со второй (11) шиной источника питания, а его эмиттер соединен с первой (7) шиной источника питания через второй (12) токостабилизирующий двухполюсник, отличающийся тем, что между коллектором первого (4) входного биполярного транзистора и второй (11) шиной источника питания включен первый (13) дополнительный источник опорного тока, между коллектором второго (5) входного биполярного транзистора и второй (11) шиной источника питания включен второй (14) дополнительный источник опорного тока, объединенные эмиттеры первого (8) и второго (9) биполярных транзисторов токового зеркала связаны с эмиттером выходного биполярного транзистора (10), причем первый (6) и второй (12) токостабилизирующие двухполюсники, первый (13) и второй (14) дополнительные источники опорного тока выполнены на арсенид-галлиевых полевых транзисторах с управляющим p-n переходом, а численные значения токов первого (6) токостабилизирующего двухполюсника, первого (13) и второго (14) дополнительных источников опорного тока приблизительно в 2 раза меньше тока второго (12) токостабилизирующего двухполюсника.

| БРЮС КАРТЕР и др | |||

| "Операционные усилители для всех", М.: Додэка-XXI, 2011, стр | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ АВТОМАТИЧЕСКОЙ БОКОВОЙ СТАБИЛИЗАЦИИ | 1921 |

|

SU445A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| US 4406990 A1, 27.09.1983 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416153C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449465C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

Авторы

Даты

2024-03-04—Публикация

2023-11-03—Подача