ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Иллюстративные варианты осуществления данного изобретения направлены на конструктивные исполнения матрицы битовых ячеек магниторезистивной оперативной памяти (MRAM). Более конкретно, варианты осуществления настоящего изобретения относятся к конструктивным исполнениям матрицы магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM).

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0002] Магниторезистивная оперативная память (MRAM) представляет собой технологию энергонезависимой памяти, использующей магнитные элементы. Например, магниторезистивная оперативная память с переносом спинового момента (STT-MRAM) использует электроны, которые становятся поляризованными по спину, когда электроны проходят через тонкую пленку (спиновый фильтр). STT-MRAM также известна как RAM с переносом спинового момента (STT-RAM), RAM переключения намагниченности с переносом спинового момента (спиновая-RAM), и перенос спинового момента (SMT-RAM).

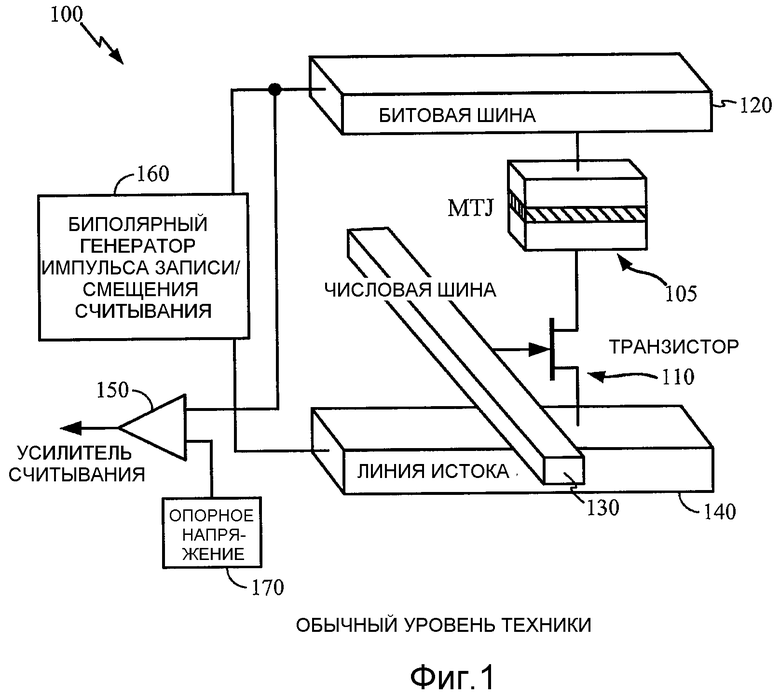

[0003] Касательно фиг.1, проиллюстрирована диаграмма обычной ячейки 100 STT-MRAM. Данная битовая ячейка 100 STT-MRAM включает элемент 105 памяти магнитного туннельного перехода (MTJ), транзистор 110, битовую шину 120 и числовую шину 130. Элемент памяти MTJ формируется, например, из связанного слоя и свободного слоя, каждый из которых может удерживать магнитное поле, отделенное посредством изолирующего слоя (слоя туннельного барьера), как проиллюстрировано на фиг.1. Битовая ячейка 100 STT-MRAM также включает линию 140 истока, усилитель 150 считывания, схему 160 считывания/записи и опорное напряжение 170 битовой шины. Специалисты в области техники в полной мере поймут, что работа и конструкция ячейки 100 памяти известна из области техники. Дополнительные детали обеспечиваются, например, в работе M. Hosomi, et al., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM, материалы конференции IEDM (2005), полностью включенной в настоящий документ по ссылке.

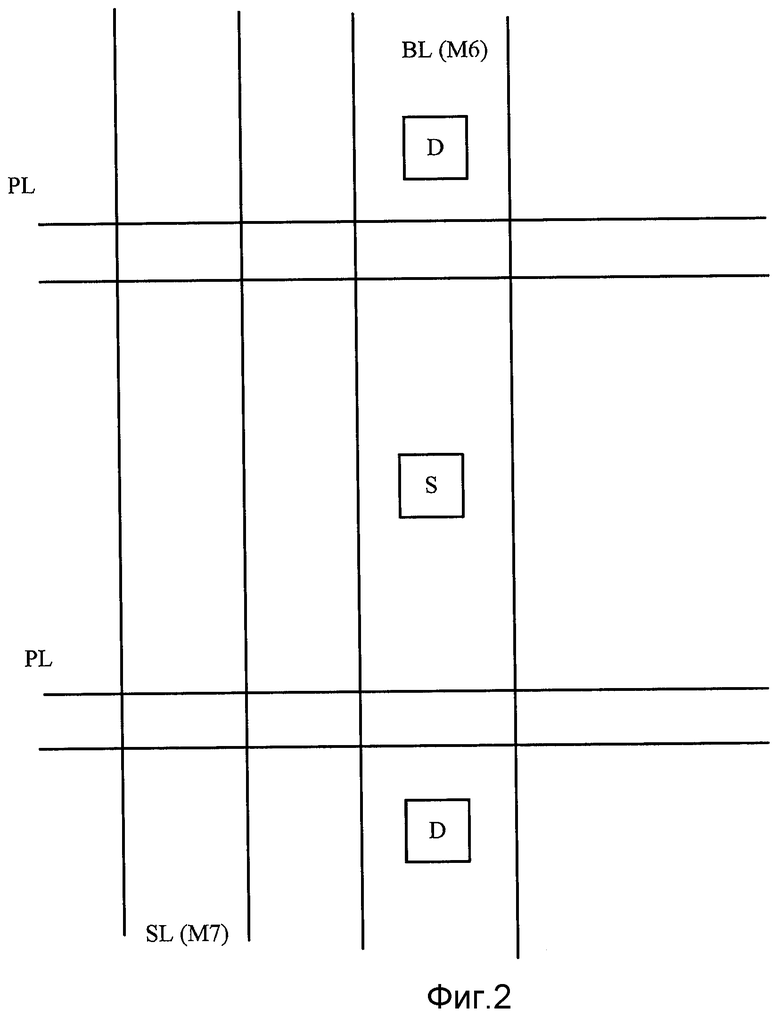

[0004] Касательно фиг.2, в обычных исполнениях линии истока (SL) матриц битовых ячеек магнитного туннельного перехода (MTJ) выполнены с возможностью быть параллельными либо битовой шине (BL), либо числовой шине. Однако в обычных исполнениях не существует непосредственного и параллельного наложения между линией истока (SL) и битовой шиной (BL) по причине правил пространственного распределения переходного отверстия и металла. Таким образом, минимальный размер битовой ячейки в обычных исполнениях не может быть уменьшен или минимизирован как результат правил пространственного распределения металла и переходного отверстия.

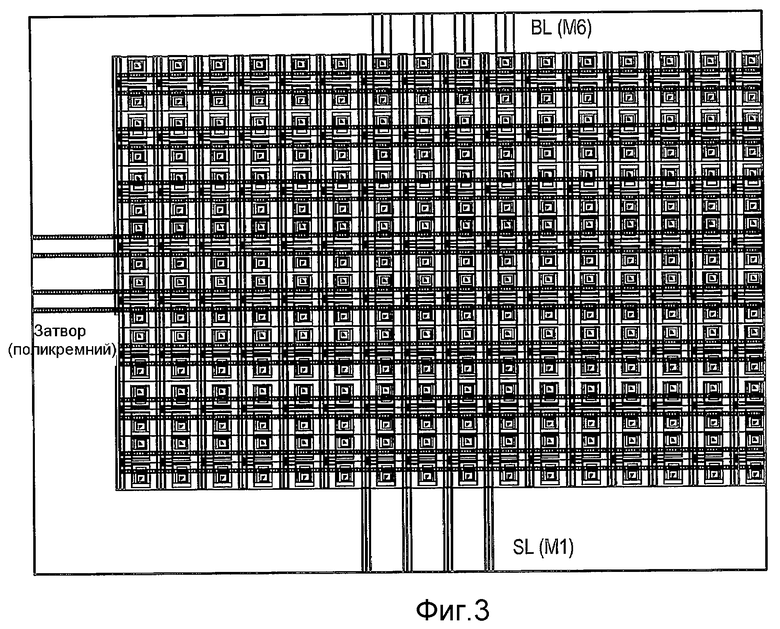

[0005] Фиг.3 представляет собой вид сверху сетки обычной матрицы битовой ячейки магнитного туннельного перехода (MTJ), имеющей линии истока (SL), выполненные параллельно к битовым шинам (BL). Как продемонстрировано на фиг.3, данные линии истока (SL) не накладываются на битовые шины (BL), и, таким образом, размер битовой ячейки является ограниченным правилами пространственного распределения между линиями истока (SL) и битовыми шинами (BL).

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] Иллюстративные варианты осуществления настоящего изобретения направлены на конструктивные исполнения битовых ячеек магниторезистивной оперативной памяти (MRAM). Более конкретно, варианты осуществления настоящего изобретения относятся к конструктивным исполнениям матрицы магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM). Соответственно один иллюстративный вариант осуществления настоящего изобретения может включать битовую ячейку магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), включающую линию истока, сформированную в первой плоскости, и битовую шину, сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока, причем данная линия истока накладывается на по меньшей мере один участок битовой шины.

[0007] Другой иллюстративный вариант осуществления настоящего изобретения может включать битовую ячейку магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), включающую первый металлический слой, формирующий битовую шину, имеющую продольную ось в первой плоскости, и второй металлический слой, формирующий линию истока, имеющую продольную ось во второй плоскости, причем данная продольная ось первого металлического слоя является параллельной данной продольной оси второго металлического слоя, и причем первый металлический слой накладывается на по меньшей мере один участок второго металлического слоя.

[0008] Другой иллюстративный вариант осуществления настоящего изобретения может включать матрицу битовых ячеек магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), включающую множество битовых ячеек. Каждая битовая ячейка может включать линию истока, сформированную в первой плоскости, и битовую шину, сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока, причем данная линия истока накладывается на по меньшей мере один участок битовой шины.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0009] Сопроводительные чертежи представлены с целью обеспечения поддержки в описании вариантов осуществления изобретения и обеспечиваются только для иллюстрации вариантов осуществления, а не их ограничения.

[0010] Фиг.1 иллюстрирует обычную ячейку магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM).

[0011] Фиг.2 представляет собой иллюстрацию обычной матрицы битовых ячеек MRAM.

[0012] Фиг.3 представляет собой вид сверху обычной матрицы битовых ячеек MRAM.

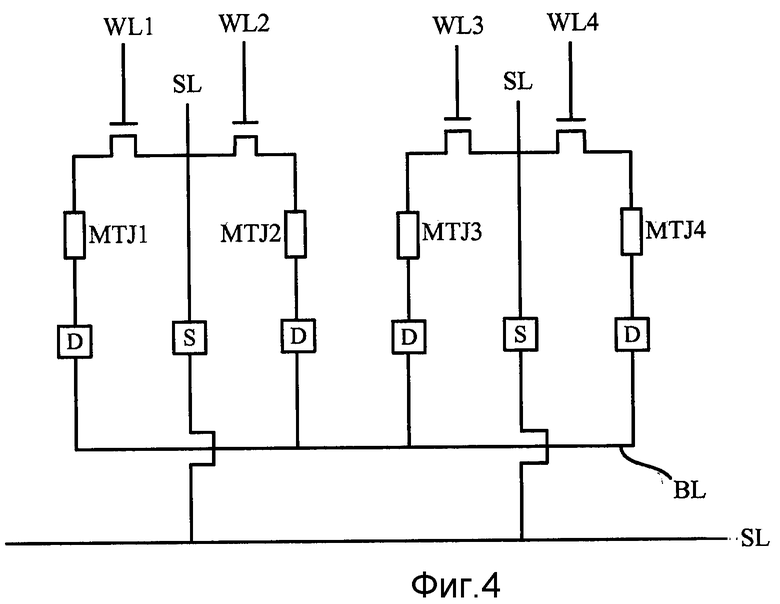

[0013] Фиг.4 представляет собой схему одного варианта осуществления матрицы битовых ячеек MRAM.

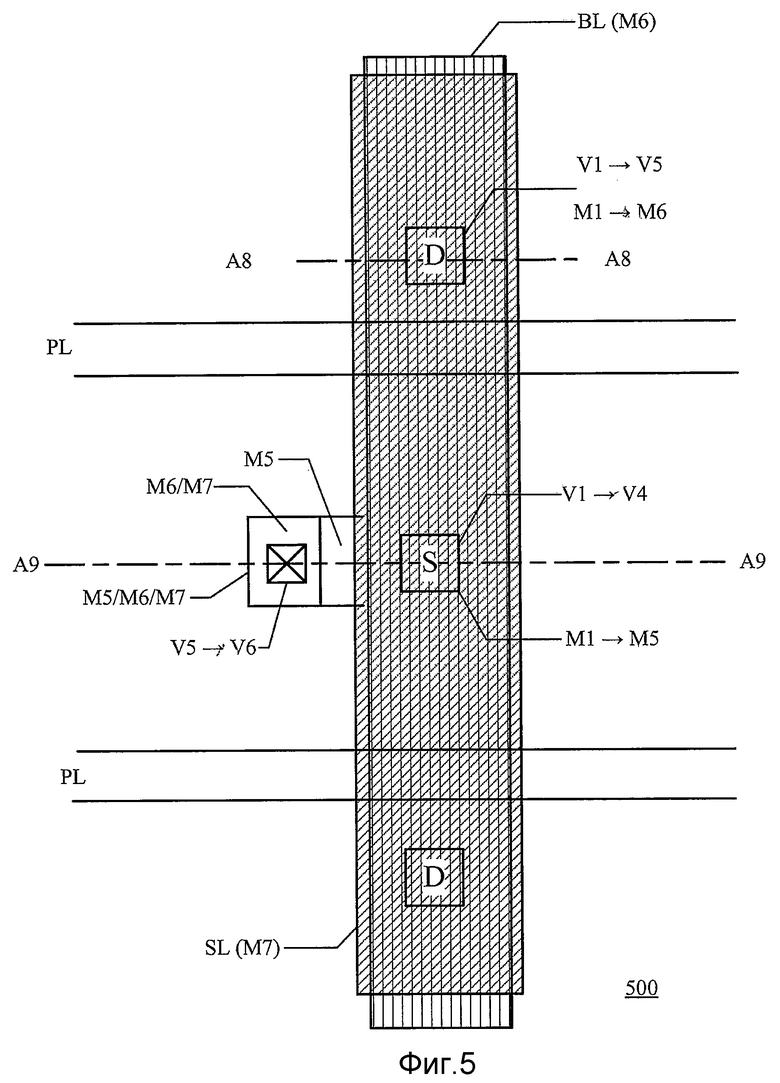

[0014] Фиг.5 представляет собой иллюстрацию сверху одного варианта осуществления матрицы битовых ячеек MRAM.

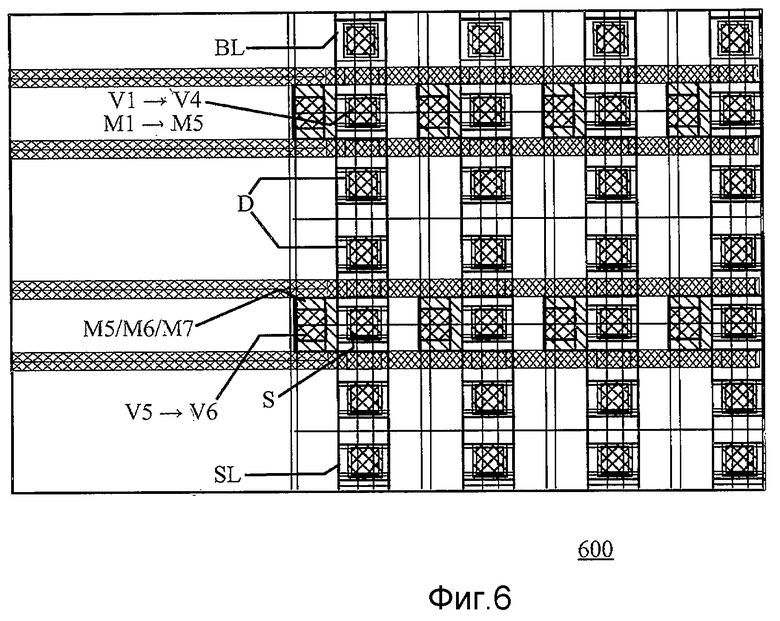

[0015] Фиг.6 представляет собой вид сверху одного варианта осуществления матрицы битовых ячеек MRAM.

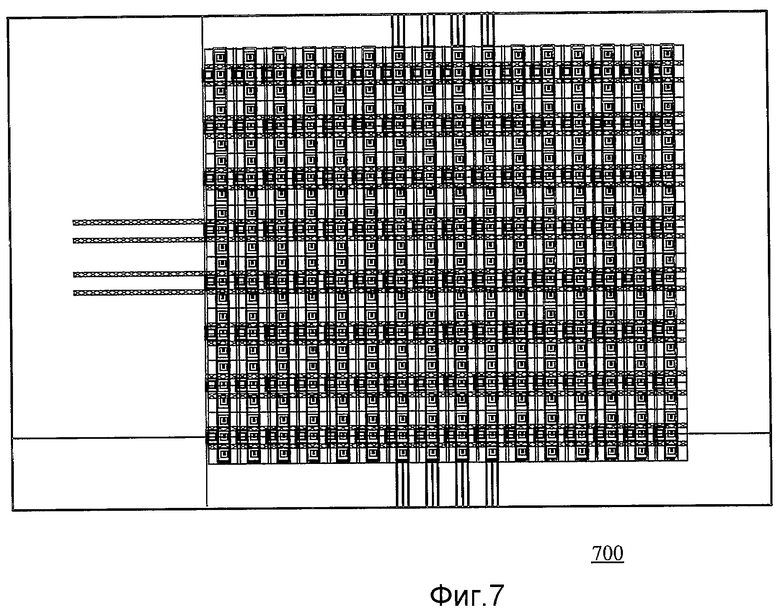

[0016] Фиг.7 представляет собой другой вид сверху одного варианта осуществления матрицы битовых ячеек MRAM.

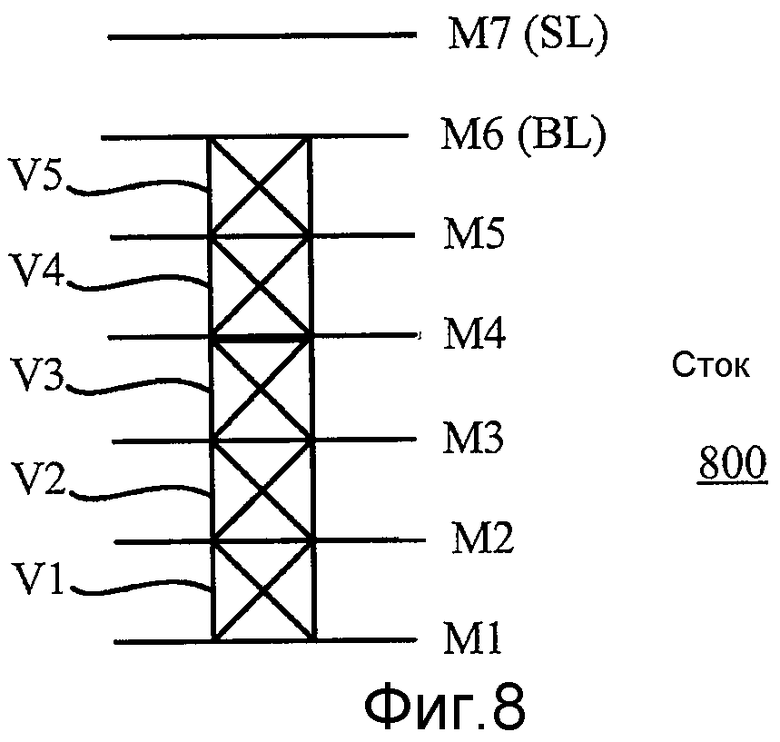

[0017] Фиг.8 представляет собой иллюстрацию в поперечном разрезе варианта осуществления матрицы битовых ячеек MRAM согласно фиг.5 по сечению А8-А8.

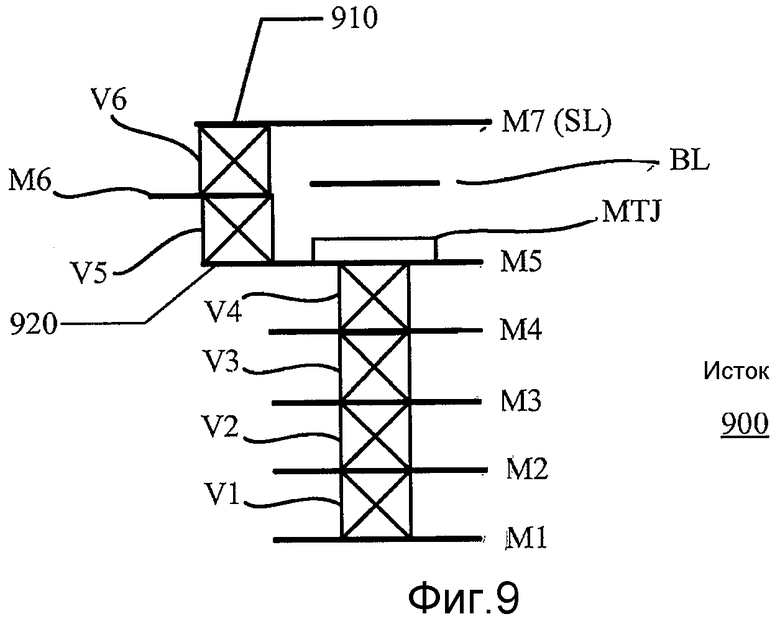

[0018] Фиг.9 представляет собой иллюстрацию в поперечном разрезе варианта осуществления матрицы битовых ячеек MRAM согласно фиг.5 по сечению А9-А9.

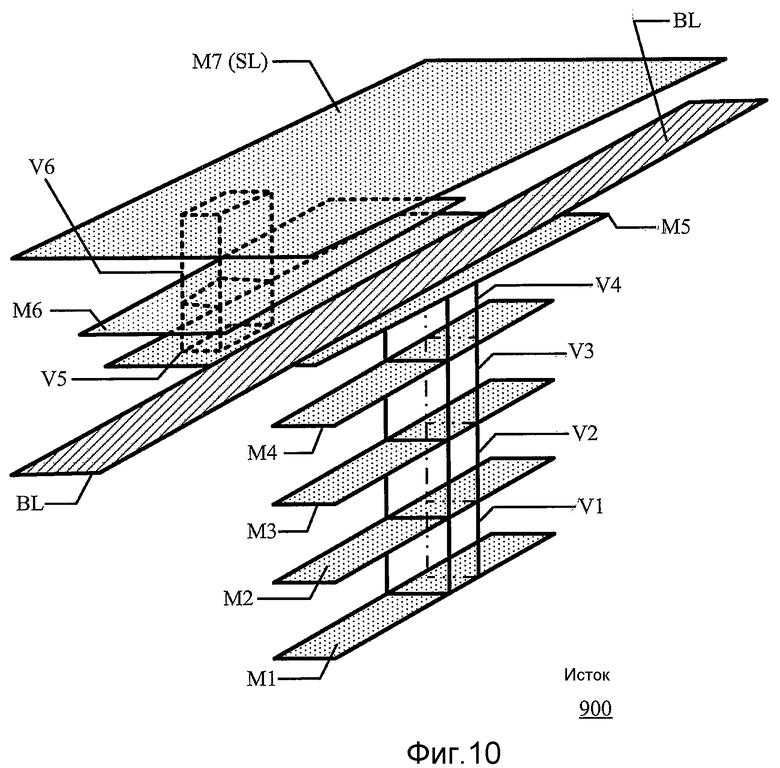

[0019] Фиг.10 представляет собой иллюстрацию в перспективе одного варианта осуществления матрицы битовых ячеек MRAM.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0020] Аспекты настоящего изобретения раскрываются в нижеследующем описании и сопутствующих чертежах относительно специфических вариантов осуществления изобретения. Иные варианты осуществления могут быть разработаны, не выходя из объема настоящего изобретения. Дополнительно, хорошо известные элементы данного изобретения не будут описаны в деталях или будут опущены, с тем чтобы не затенять значимые детали изобретения.

[0021] Термин «иллюстративный» используется в настоящем документе для обозначения «служащий в качестве примера, варианта или иллюстрации». Любой вариант осуществления, описанный в настоящем документе как «иллюстративный», не должен обязательно интерпретироваться как предпочтительный или более выгодный по отношению к другим вариантам осуществления. Аналогичным образом, термин «варианты осуществления данного изобретения» не требует того, чтобы все варианты осуществления данного изобретения включали описанный признак, преимущество или принцип действия.

[0022] Терминология, используемая в настоящем документе, применяется только в целях описания конкретных вариантов осуществления и не предназначена быть ограничивающей по отношению к вариантам осуществления данного изобретения. Как использовано в настоящем документе, формы единственного числа элемента предназначены включать также и формы множественного числа, если только контекст ясно не указывает на иное. Будет дополнительно понятным, что термины «содержит», «содержащий», «включает» и/или «включающий», при использовании в настоящем документе, специфицируют наличие заявленных признаков, целых чисел, этапов, действий, элементов и/или компонентов, но не исключают наличия или добавления одного или более других признаков, целых чисел, этапов, действий, элементов, компонентов, и/или их групп.

[0023] Варианты осуществления настоящего изобретения могут обеспечивать матрицу битовых ячеек MRAM, которая может уменьшить размер битовых ячеек. Например, вариант осуществления матрицы битовых ячеек STT-MRAM может уменьшить размер битовых ячеек посредством размещения по меньшей мере участка линии истока (SL) сверху битовой шины (BL), так чтобы можно было преодолеть ограничения, накладываемые обычными правилами пространственного распределения металла и межсоединения посредством переходного отверстия.

[0024] Варианты осуществления настоящего изобретения могут решать проблемы обычных матриц битовых ячеек MRAM. Варианты осуществления настоящего изобретения могут уменьшить размеры битовых ячеек MTJ посредством добавления межсоединений посредством переходного отверстия к линии истока (SL) и добавления верхнего тонкого металлического слоя (например, М7), так чтобы линия истока (SL) была сконфигурирована с возможностью находиться непосредственно сверху или над (например, накладываясь и параллельно к) битовой шине (BL) с целью преодоления обычных основных ограничений согласно правилам пространственного распределения металла и межсоединения посредством переходного отверстия, тем самым экономя пространство кремниевой подложки.

[0025] Касательно фиг.4-10, варианты осуществления настоящего изобретения могут обеспечивать матрицу битовых ячеек MRAM, которая уменьшает или минимизирует размер битовых ячеек. Например, фиг.4 схематически иллюстрирует вариант осуществления матрицы битовых ячеек MRAM. Вариант осуществления матрицы битовых ячеек STT-MRAM может уменьшать средний размер битовых ячеек посредством размещения линии истока (SL), накладывающейся на и параллельной к (например, располагающейся над) битовой шине (BL) с целью решения и преодоления ограничений, вытекающих из обычных правил пространственного распределения металла и межсоединения посредством переходного отверстия.

Как продемонстрировано на фиг.5, иллюстративная битовая ячейка 500 STT-MRAM включает линию истока (SL), сформированную в первой плоскости, и битовую шину (BL), сформированную во второй плоскости. Данная битовая шина (BL) имеет продольную ось, параллельную продольной оси линии истока (SL). В соответствии с иллюстративными вариантами осуществления, данная линия истока (SL) накладывается на по меньшей мере один участок ширины битовой шины (BL), тем самым уменьшая размер битовой ячейки. В одном варианте осуществления линия истока (SL) может по существу накладываться на ширину битовой шины (BL), тем самым дополнительно уменьшая размер битовой ячейки. В качестве другого примера, как показано в иллюстративном варианте осуществления по фиг.5, линия истока (SL) может полностью накладываться на битовую шину (BL), тем самым дополнительно уменьшая размер битовой ячейки.

[0026] В иллюстративном варианте осуществления, проиллюстрированном на фиг.5, размер битовой ячейки MTJ уменьшается посредством добавления верхнего тонкого металлического слоя (М7) с целью формирования линии истока (SL) непосредственно сверху или над (например, накладываясь на и параллельно к) битовой шине (BL). Данные металлические слои М5 и М7 продлеваются в направлении, перпендикулярном продольным осям линии истока (SL) и битовой шины (BL), и в той же плоскости, что и соответствующие металлические слои М5 и М7, так чтобы по меньшей мере один участок металлического слоя М5 и один участок металлического слоя М7 не накладывались на битовую шину (BL). Межсоединение посредством переходного отверстия соединяет (например, электрически соединяет) данные участки металлических слоев М5 и М7, не накладывающиеся на битовую шину (BL), друг с другом.

[0027] Например, в одном варианте осуществления один участок металлического слоя М5 и один участок металлического слоя М7 продлеваются в направлении, перпендикулярном продольным осям линии истока (SL) и битовой шины (BL), и в той же плоскости, что и соответствующие металлические слои М5 и М7 с целью формирования боковых выступов (например, первого и второго боковых выступов). Межсоединение посредством переходного отверстия соединяет (например, электрически соединяет) данные участки боковых выступов друг с другом.

[0028] В одном варианте осуществления металлический слой М6 формируется в области боковых выступов между металлическими слоями М5 и М7. Данный иллюстративный вариант осуществления, продемонстрированный на фиг.5, включает межсоединение V5 посредством переходного отверстия для соединения металлического слоя М5 с металлическим слоем М6 и межсоединение V6 посредством переходного отверстия для соединения металлического слоя М6 с боковым выступом металлического слоя М7. Таким образом, данный вариант осуществления может избегать перемыкания или межсоединения линии истока (например, М7) и битовой шины (BL), которое в ином случае могло бы происходить в результате параллельного наложения линии истока (SL) и битовой шины (BL). Иллюстрации в поперечном разрезе варианта осуществления матрицы битовых ячеек MRAM по фиг.5 описываются ниже со ссылкой на фиг.8 и 9.

[0029] В другом иллюстративном варианте осуществления настоящего изобретения ячейка MTJ может быть сдвинута на один металлический слой вниз, так чтобы существующий верхний тонкий металл (например, М6) мог быть использован в качестве линии истока (SL). Соответственно в данном иллюстративном варианте осуществления дополнительный металлический слой (например, М7) не включается в битовую ячейку.

[0030] Фиг.6 представляет собой вид сверху одного варианта осуществления матрицы 600 битовых ячеек MRAM, в общем соответствующую варианту осуществления, проиллюстрированному на фиг.5, со схожими элементами, обозначающимися так же. Фиг.7 представляет собой другой вид сверху одного варианта осуществления матрицы 700 битовых ячеек MRAM, иллюстрирующего более масштабную интеграцию битовых ячеек.

[0031] Фиг.8 представляет собой иллюстрацию в поперечном разрезе варианта осуществления стока 800 матрицы битовых ячеек MRAM согласно фиг.5, по сечению А8-А8. Как продемонстрировано на фиг.8, металлические слои М1, М2, М3, М4, М5 и М6 (BL) соединяются друг с другом с помощью межсоединений посредством переходных отверстий V1, V2, V3, V4 и V5 соответственно. Линия истока М7 сконфигурирована с возможностью быть параллельной к и накладываться на металлический слой М6 (BL), но не межсоединяться.

[0032] Фиг.9 представляет собой иллюстрацию в поперечном разрезе варианта осуществления истока 900 матрицы битовых ячеек MRAM согласно фиг.5, по сечению А9-А9. Как продемонстрировано на фиг.9, металлические слои М1, М2, М3, М4 и М5 соединяются друг с другом с помощью межсоединений посредством переходных отверстий V1, V2, V3 и V4 соответственно. Металлические слои М5 и М7 продлеваются в направлении, перпендикулярном продольным осям линии истока (SL) и битовой шины (BL), и в той же плоскости, что и соответствующие металлические слои М5 и М7 с целью формирования боковых выступов (например, первый боковой выступ 910 и второй боковой выступ 920). Металлический слой (например, М6 на фиг.9) формируется в области боковых выступов между металлическими слоями М5 и М7, Например, как продемонстрировано в варианте осуществления по фиг.9, данный металлический слой (например, М6) может быть сформирован в той же плоскости, что и битовая шина (BL), но электрически изолирован от данной битовой шины (BL). Вариант осуществления включает межсоединения V5 и V6 посредством переходного отверстия для соединения бокового выступа 920 металлического слоя М5 с металлическим слоем М6, и металлического слоя М6 с боковым выступом 910 металлического слоя М7 соответственно.

[0033] Как продемонстрировано на фиг.10, представляющей собой иллюстрацию в перспективе одного варианта осуществления истока 900 матрицы битовых ячеек MRAM, линия истока (SL) (например, М7) сконфигурирована с возможностью быть параллельной к и накладывающейся на битовую шину (BL), но не межсоединенной (например, электрически межсоединенной). Таким образом, иллюстративные варианты осуществления могут избегать перемыкания линии истока (например, М7) и битовой шины (BL), которое в ином случае могло бы происходить в результате параллельного наложения линии истока (SL) и битовой шины (BL), одновременно минимизируя или уменьшая средний размер битовой ячейки по сравнению с обычным исполнением битовой ячейки.

[0034] В соответствии с одним вариантом осуществления настоящего изобретения одно или более межсоединений посредством переходного отверстия (например, V5 и V6) и верхний металлический слой (М7) могут быть выполнены с возможностью соединения линии истока (SL) транзистора доступа в битовой ячейке MTJ, так чтобы линия истока (SL) могла быть размещена непосредственно сверху или над (например, накладываясь на и параллельно к) битовой шиной (BL), без перемыкания или межсоединения линии истока (SL) (например, М7) и битовой шины (BL), тем самым уменьшая обычную область битовой ячейки.

[0035] Соответственно один вариант осуществления настоящего изобретения может представлять собой битовую ячейку магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), включающую линию истока (SL), сформированную в первой плоскости, и битовую шину (BL), сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока (SL), причем данная линия истока (SL) накладывается на по меньшей мере один участок битовой шины (BL). В одном варианте осуществления линия истока (SL) может по существу накладываться на битовую шину (BL).

[0036] В одном варианте осуществления линия истока (SL) включает первый боковой выступ 910, продлевающийся в первой плоскости в направлении, перпендикулярном продольной оси линии истока (SL), так чтобы участок первого бокового выступа 910 не накладывался на битовую шину (BL).

[0037] В другом варианте осуществления линия истока представляет собой первый металлический слой (например, М7 (SL)), и битовая шина представляет собой второй металлический слой (например, BL). Битовая ячейка также может включать третий металлический слой (например, М5), сформированный в третьей плоскости и имеющий продольную ось, параллельную продольной оси первого металлического слоя (например, М7), причем второй металлический слой (например, BL) помещается между первым металлическим слоем (например, М7) и третьим металлическим слоем (например, М5). Первый металлический слой (например, М7) и/или второй металлический слой (например, BL) могут накладываться на по меньшей мере один участок третьего металлического слоя (например, М5).

[0038] Третий металлический слой (например, М5) может включать второй боковой выступ 920, продлевающийся в третьей плоскости в направлении, перпендикулярном продольной оси третьего бокового выступа (например, М5). Первый боковой выступ 910 может накладываться на второй боковой выступ 920, и может быть электрически соединен со вторым боковым выступом 920.

[0039] В одном варианте осуществления по меньшей мере одно межсоединение посредством переходного отверстия (например, V5, V6 и так далее) соединяет первый боковой выступ 910 со вторым боковым выступом 920. В другом варианте осуществления четвертый металлический слой (например, М6) помещается между первым боковым выступом 910 и вторым боковым выступом 920. Первое межсоединение посредством переходного отверстия (например, V6) соединяет первый боковой выступ 910 с четвертым металлическим слоем (например, М6), а второе межсоединение посредством переходного отверстия (например, V5) соединяет четвертый металлический слой (например, М6) со вторым боковым выступом 920. В одном варианте осуществления четвертый металлический слой (например, М6) формируется во второй плоскости и может быть электрически изолирован от второго металлического слоя (например, BL).

[0040] В других вариантах осуществления битовая ячейка STT-MRAM может включать числовую шину, элемент памяти и транзистор числовой шины, соединенный с элементом памяти. Данный элемент памяти может представлять собой магнитный туннельный переход (MTJ), как проиллюстрировано, например, на фиг.9, и данный транзистор числовой шины может быть соединен в ряды с MTJ.

[0041] В другом варианте осуществления битовая ячейка магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM) может включать первый металлический слой (например, М7), формирующий линию истока, имеющую продольную ось, в первой плоскости, и второй металлический слой (например, BL), формирующий битовую линию, имеющую продольную ось, во второй плоскости, причем данная продольная ось первого металлического слоя (например, М7) является параллельной продольной оси второго металлического слоя (например, BL).

[0042] В другом варианте осуществления матрица битовых ячеек магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM) включает множество битовых ячеек. Каждая битовая ячейка включает линию истока, сформированную в первой плоскости, и битовую шину, сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока, причем данная линия истока накладывается (например, сверху или снизу) по меньшей мере на один участок битовой шины. Иллюстративные варианты осуществления матрицы битовых ячеек STT-MRAM могут уменьшить средний размер битовых ячеек посредством размещения линии истока (SL) с наложением на и в общем параллельно к битовой шине (BL) с целью уменьшения области, используемой в обычных конфигурациях металла и межсоединений посредством переходного отверстия. Варианты осуществления матрицы битовых ячеек MRAM могут уменьшать размеры битовых ячеек путем добавления межсоединений посредством переходного отверстия к линии истока (SL) и добавления верхнего тонкого металлического слоя (например, М7), так чтобы линия истока (SL) была сконфигурирована с возможностью находиться непосредственно сверху или над битовой шиной (BL) с целью преодоления обычных основных ограничений по правилам пространственного распределения металла и межсоединения посредством переходного отверстия, экономя тем самым пространство.

[0043] В то время как вышеизложенное раскрытие демонстрирует иллюстративные варианты осуществления изобретения, следует отметить, что различные изменения и модификации могут быть сделаны в настоящем документе, не выходя из объема данного изобретения, как определено посредством прилагаемой формулы изобретения. Функции, этапы и/или действия по заявке в соответствии с вариантами осуществления данного изобретения, описанными в настоящем документе, не нуждаются быть выполненными в каком-либо конкретном порядке. Более того, хотя элементы данного изобретения могут быть описаны или заявлены в форме единственного числа, предполагается и форма множественного числа, если только ограничение до единственного числа не является четко обозначенным.

Изобретение относится к битовым ячейкам магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM). Технический результат - уменьшение площади полупроводниковой подложки, занимаемой ячейкой STT-MRAM. Данные битовые ячейки включают линию истока, сформированную в первой плоскости, и битовую шину, сформированную во второй плоскости. Битовая шина имеет продольную ось, параллельную продольной оси данной линии истока, и линия истока накладывается на по меньшей мере участок битовой шины. 3 н. и 20 з.п. ф-лы, 10 ил.

1. Битовая ячейка магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), содержащая:

линию истока, сформированную в первой плоскости; и

битовую шину, сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока,

причем данная линия истока накладывается на по меньшей мере участок битовой шины.

2. Битовая ячейка STT-MRAM по п.1, в которой линия истока включает в себя первый боковой выступ, продолжающийся в первой плоскости и в направлении, перпендикулярном продольной оси линии истока, так, чтобы участок первого бокового выступа не накладывался на битовую шину.

3. Битовая ячейка STT-MRAM по п.2, в которой линия истока представляет собой первый металлический слой и битовая шина представляет собой второй металлический слой,

причем битовая ячейка дополнительно содержит:

третий металлический слой, сформированный в третьей плоскости и имеющий продольную ось, параллельную продольной оси первого металлического слоя,

причем второй металлический слой помещается между первым металлическим слоем и третьим металлическим слоем.

4. Битовая ячейка STT-MRAM по п.3, в которой первый металлический слой и/или второй металлический слой накладываются на по меньшей мере участок третьего металлического слоя.

5. Битовая ячейка STT-MRAM по п.3, в которой третий металлический слой включает в себя второй боковой выступ, продолжающийся в третьей плоскости и в направлении, перпендикулярном продольной оси третьего металлического слоя, и

в которой первый боковой выступ накладывается на второй боковой выступ и электрически соединен со вторым боковым выступом.

6. Битовая ячейка STT-MRAM по п.5, дополнительно содержащая:

по меньшей мере одно межсоединение посредством сквозного отверстия, которое соединяет первый боковой выступ со вторым боковым выступом.

7. Битовая ячейка STT-MRAM по п.5, дополнительно содержащая:

четвертый металлический слой, помещающийся между первым боковым выступом и вторым боковым выступом;

первое межсоединение посредством сквозного отверстия, соединяющее первый боковой выступ с четвертым металлическим слоем;

и второе межсоединение посредством сквозного отверстия, соединяющее четвертый металлический слой со вторым боковым выступом.

8. Битовая ячейка STT-MRAM по п.7, в которой четвертый металлический слой формируется во второй плоскости и электрически изолирован от второго металлического слоя.

9. Битовая ячейка STT-MRAM по п.1, в которой линия истока, по существу, накладывается на битовую шину.

10. Битовая ячейка STT-MRAM по п.1, дополнительно содержащая:

числовую шину;

элемент памяти и

транзистор числовой шины, соединенный с элементом памяти.

11. Битовая ячейка STT-MRAM по п.10, в которой данный элемент памяти представляет собой магнитный туннельный переход (MTJ) и в которой данный транзистор числовой шины соединен последовательно с MTJ.

12. Битовая ячейка магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), содержащая:

первый металлический слой, формирующий линию истока, имеющую продольную ось в первой плоскости; и

второй металлический слой, формирующий битовую линию, имеющую продольную ось во второй плоскости,

причем данная продольная ось первого металлического слоя параллельна продольной оси второго металлического слоя и

причем первый металлический слой накладывается на по меньшей мере участок второго металлического слоя.

13. Битовая ячейка STT-MRAM по п.12, в которой первый металлический слой включает в себя первый боковой выступ, продолжающийся в направлении, перпендикулярном продольной оси первого металлического слоя, так, чтобы участок первого бокового выступа не накладывался на второй металлический слой.

14. Битовая ячейка STT-MRAM по п.13, дополнительно содержащая:

третий металлический слой, сформированный в третьей плоскости и имеющий продольную ось, параллельную продольной оси первого металлического слоя,

причем второй металлический слой помещается между первым металлическим слоем и третьим металлическим слоем.

15. Битовая ячейка STT-MRAM по п.14, в которой первый металлический слой и/или второй металлический слой накладываются на по меньшей мере участок третьего металлического слоя.

16. Битовая ячейка STT-MRAM по п.14, в которой третий металлический слой включает в себя второй боковой выступ, продолжающийся в направлении, перпендикулярном продольной оси третьего металлического слоя, и

в которой первый боковой выступ накладывается на второй боковой выступ и электрически соединен со вторым боковым выступом.

17. Битовая ячейка STT-MRAM по п.16, дополнительно содержащая:

по меньшей мере одно межсоединение посредством сквозного отверстия, которое соединяет первый боковой выступ со вторым боковым выступом.

18. Битовая ячейка STT-MRAM по п.16, дополнительно содержащая:

четвертый металлический слой, помещающийся между первым боковым выступом и вторым боковым выступом;

первое межсоединение посредством сквозного отверстия, соединяющее первый боковой выступ с четвертым металлическим слоем;

и второе межсоединение посредством сквозного отверстия, соединяющее четвертый металлический слой со вторым боковым выступом.

19. Битовая ячейка STT-MRAM по п.18, в которой четвертый металлический слой формируется во второй плоскости и электрически изолирован от второго металлического слоя.

20. Битовая ячейка STT-MRAM по п.12, в которой первый металлический слой, по существу, накладывается на второй металлический слой.

21. Битовая ячейка STT-MRAM по п.12, дополнительно содержащая:

числовую шину;

элемент памяти и

транзистор числовой шины, соединенный с элементом памяти.

22. Битовая ячейка STT-MRAM по п.21, в которой данный элемент памяти представляет собой магнитный туннельный переход (MTJ) и в которой данный транзистор числовой шины соединен последовательно с MTJ.

23. Матрица битовой ячейки магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM), содержащая:

множество битовых ячеек, причем каждая битовая ячейка включает в себя:

линию истока, сформированную в первой плоскости; и

битовую шину, сформированную во второй плоскости и имеющую продольную ось, параллельную продольной оси данной линии истока,

причем линия истока накладывается на по меньшей мере участок битовой шины.

| М.HOSOMI et al | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Парлифтный насос | 1986 |

|

SU1321941A1 |

| УСОВЕРШЕНСТВОВАННОЕ МНОГОРАЗРЯДНОЕ МАГНИТНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ И СПОСОБЫ ЕГО ФУНКЦИОНИРОВАНИЯ И ПРОИЗВОДСТВА | 2005 |

|

RU2310928C2 |

Авторы

Даты

2012-10-20—Публикация

2009-03-23—Подача