ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

Эта заявка заявляет преимущество приоритета предварительной заявки на патент США № 62/173,779, поданной 10 июня 2015, полное содержание которой включено сюда посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Варианты осуществления, описанные здесь, относятся, в общем, к запоминающему устройству с изменением сопротивления.

УРОВЕНЬ ТЕХНИКИ

Ячейка памяти запоминающего устройства с изменением сопротивления, например, магниторезистивного запоминающего устройства с произвольным доступом с переносом спинового момента (STT-MRAM), содержит транзистор выбора и элемент изменения сопротивления, которые соединены последовательно, и присоединена между разрядной линией (шиной) и линией истока (питающей линией). В случае такого запоминающего устройства с изменением сопротивления, когда сопротивление питающей линии увеличивается в результате миниатюризации ячейки памяти, во время считывания/записи возникает явление, при котором потенциал истока транзистора выбора изменяется согласно положению ячейки памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

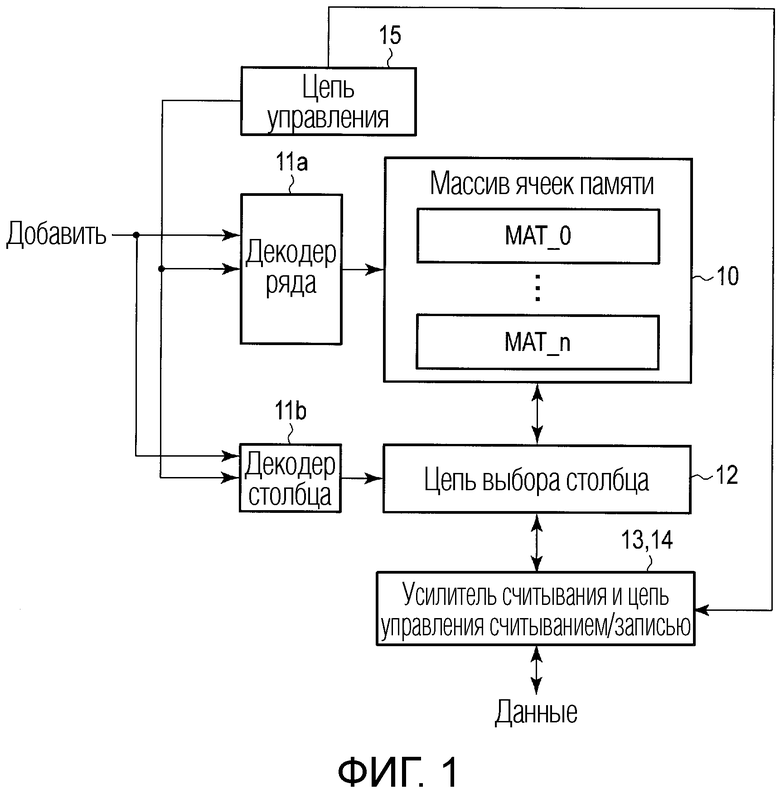

Фиг. 1 является схемой, показывающей пример запоминающего устройства с изменением сопротивления.

Фиг. 2 является схемой, показывающей пример блока.

Фиг. 3 является схемой, показывающей пример массива ячеек памяти.

Фиг. 4 является видом сверху, показывающим устройство в качестве сравнительного примера.

Фиг. 5А является сечением по линии VA-VA по фиг. 4.

Фиг. 5В является сечением по линии VB-VB по фиг. 4.

Фиг. 6 и 7 являются иллюстрациями, показывающими пример изменения потенциала питающей линии во время считывания.

Фиг. 8 является видом сверху, показывающим устройство в качестве первого варианта осуществления.

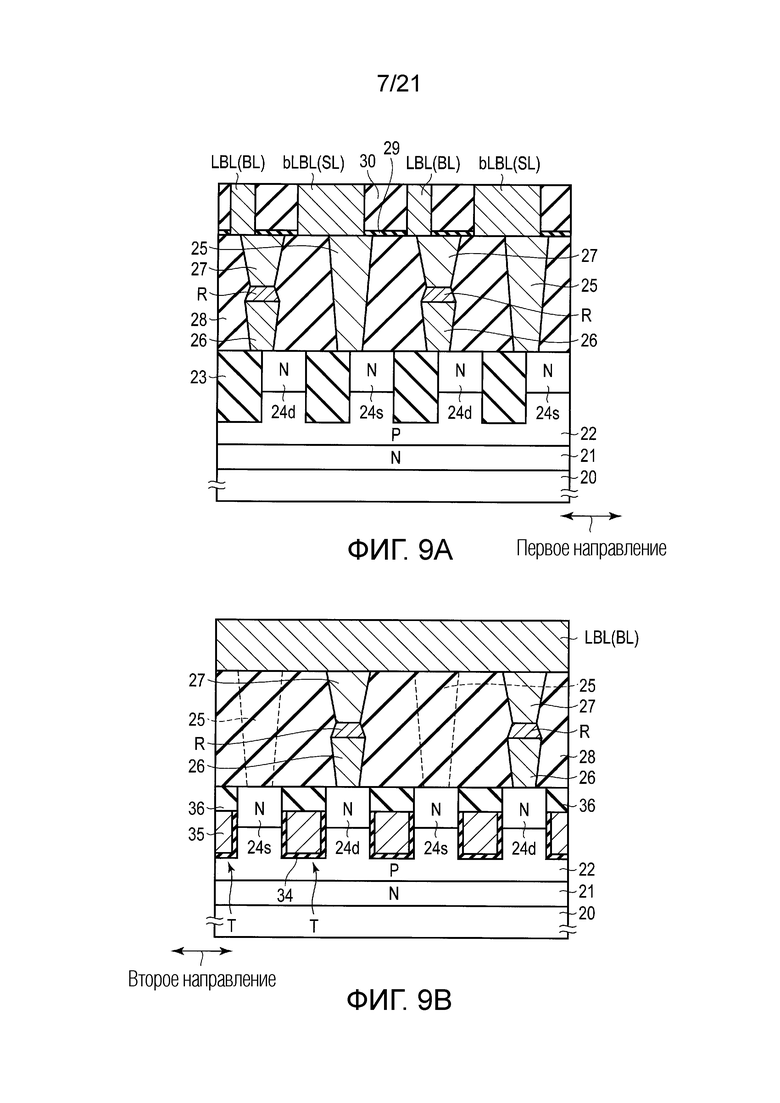

Фиг. 9А является сечением по линии IXA-IXA фиг. 8.

Фиг. 9В является сечением по линии IXB-IXB фиг. 8.

Фиг. 10 и 11 являются иллюстрациями, показывающими изменение в потенциале питающей линии во время считывания.

Фиг. 12 является иллюстрацией, показывающей преимущество в отношении ошибки считывания и ошибки записи.

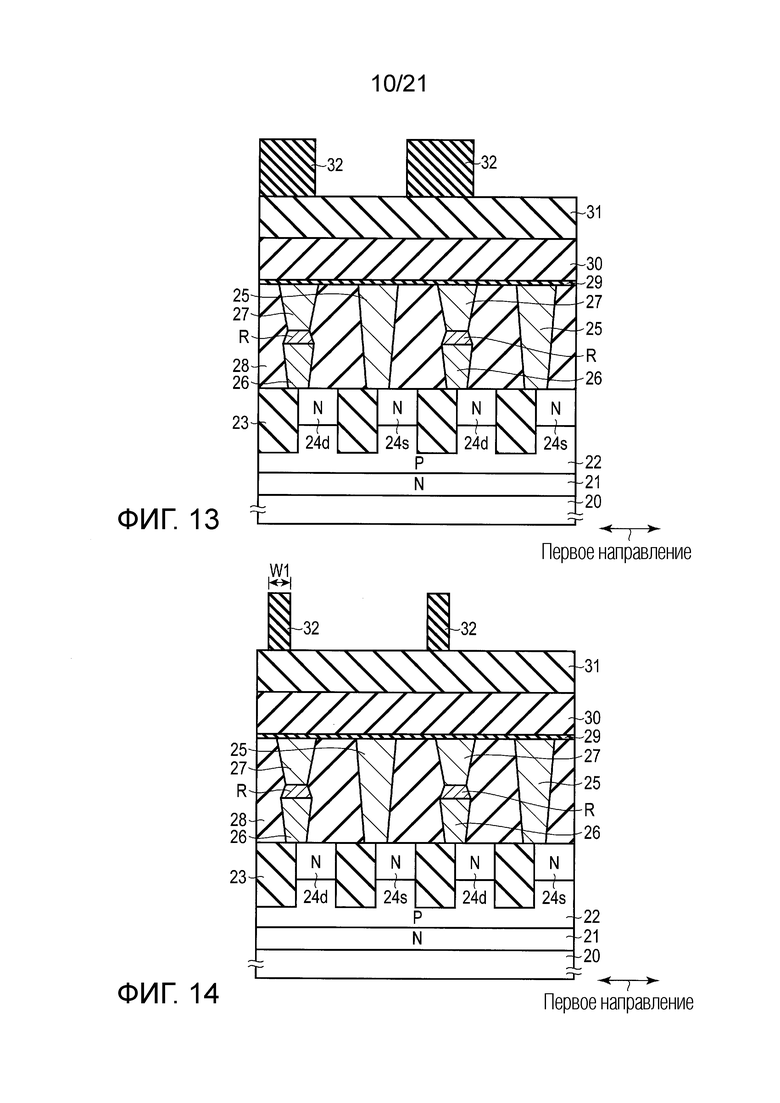

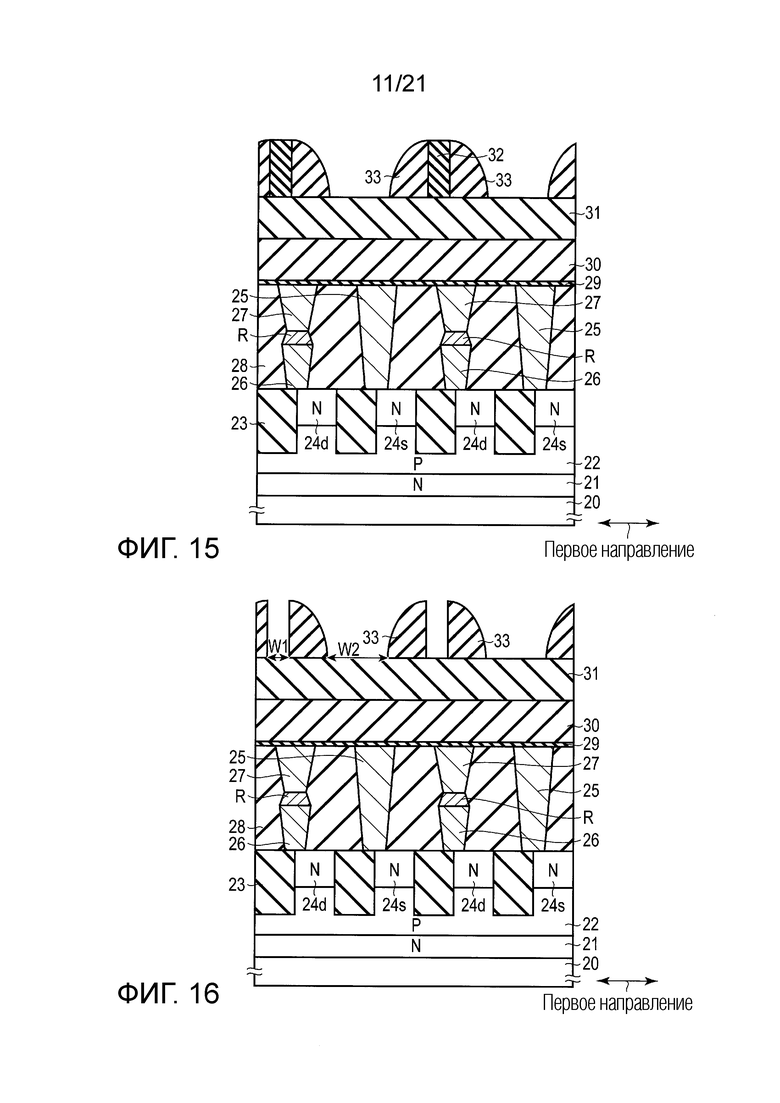

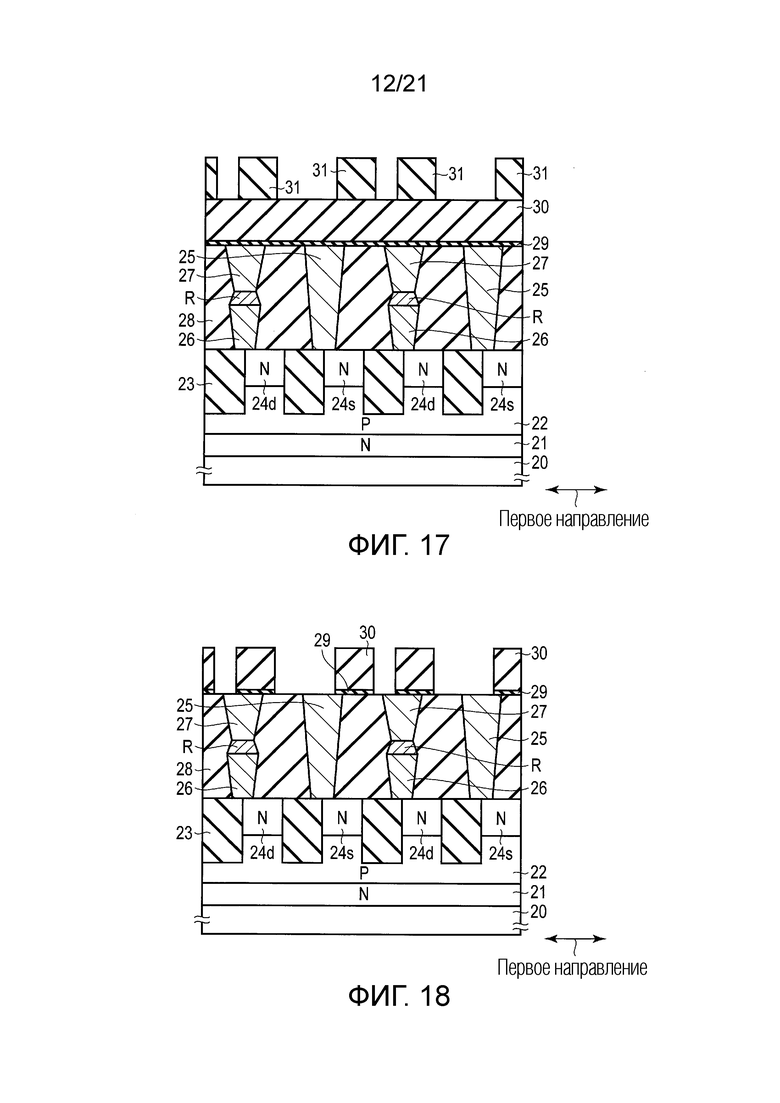

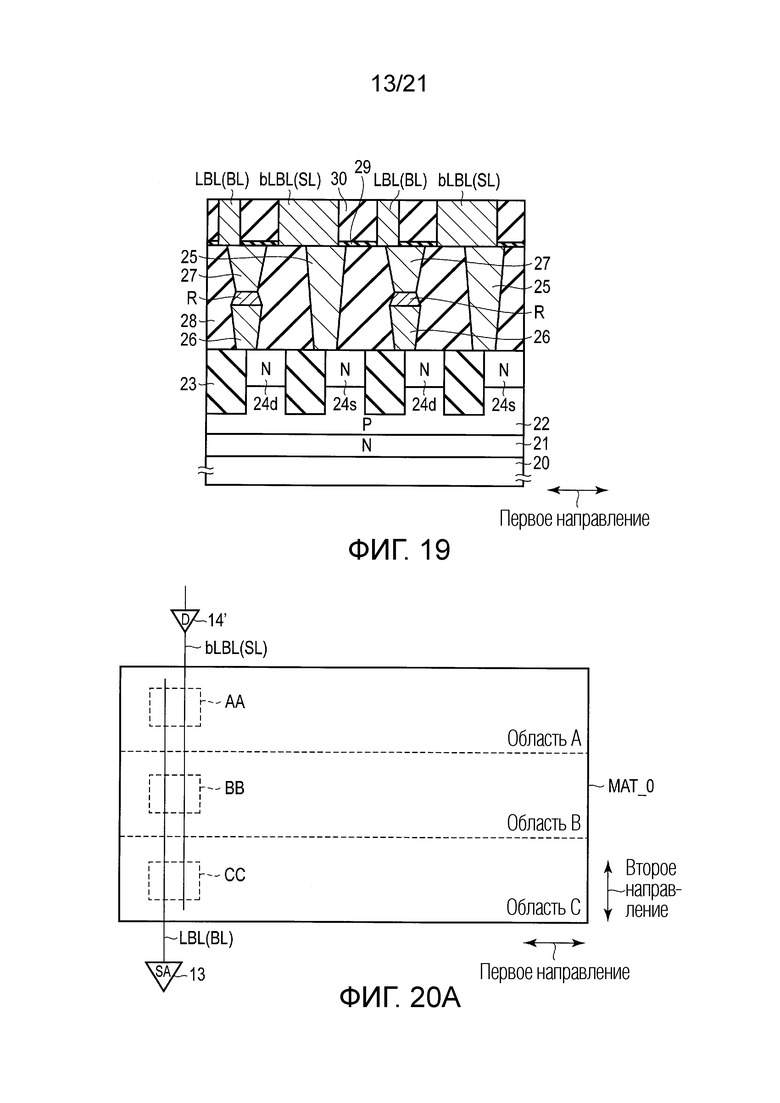

Фиг. 13-19 являются сечениями, показывающими пример способа изготовления устройства по фиг. 8, 9А и 9В.

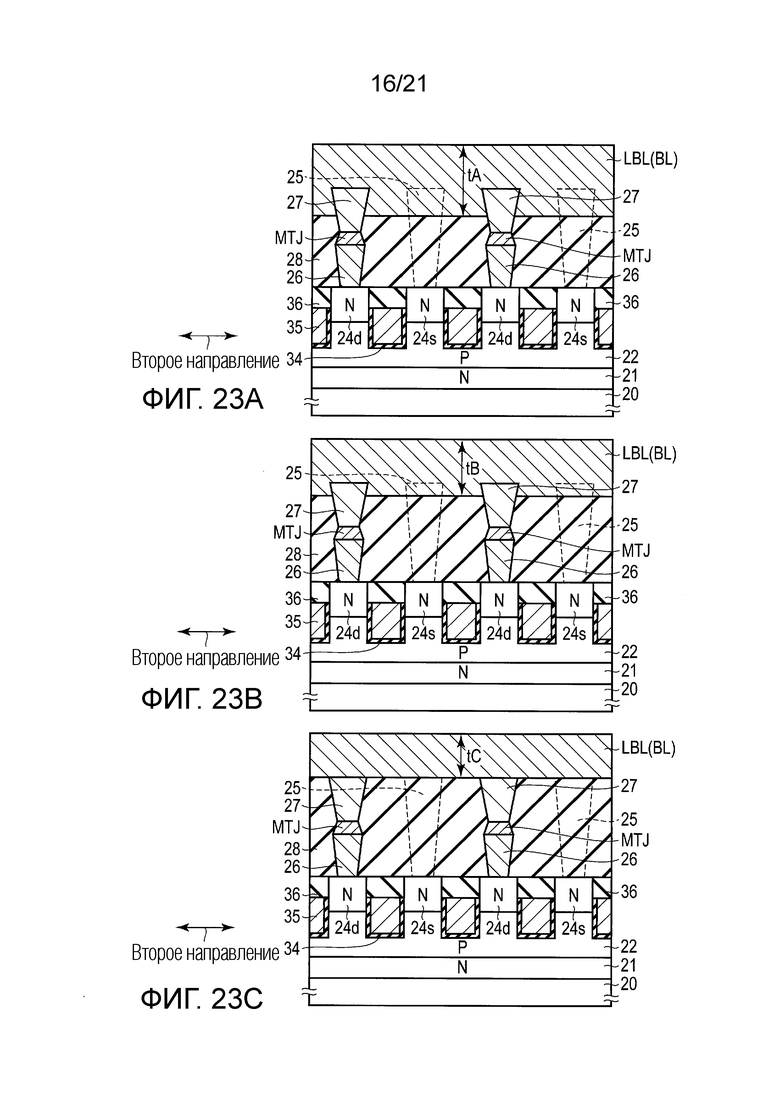

Фиг. 20А и 20В являются видами сверху, показывающими устройство в качестве второго варианта осуществления.

Фиг. 21 является видом сверху, показывающим пример областей AA, BB, и CC по фиг. 20A и 20B.

Фиг. 22A, 22B, и 22C являются сечениями по линии XXII-XXII фиг. 21.

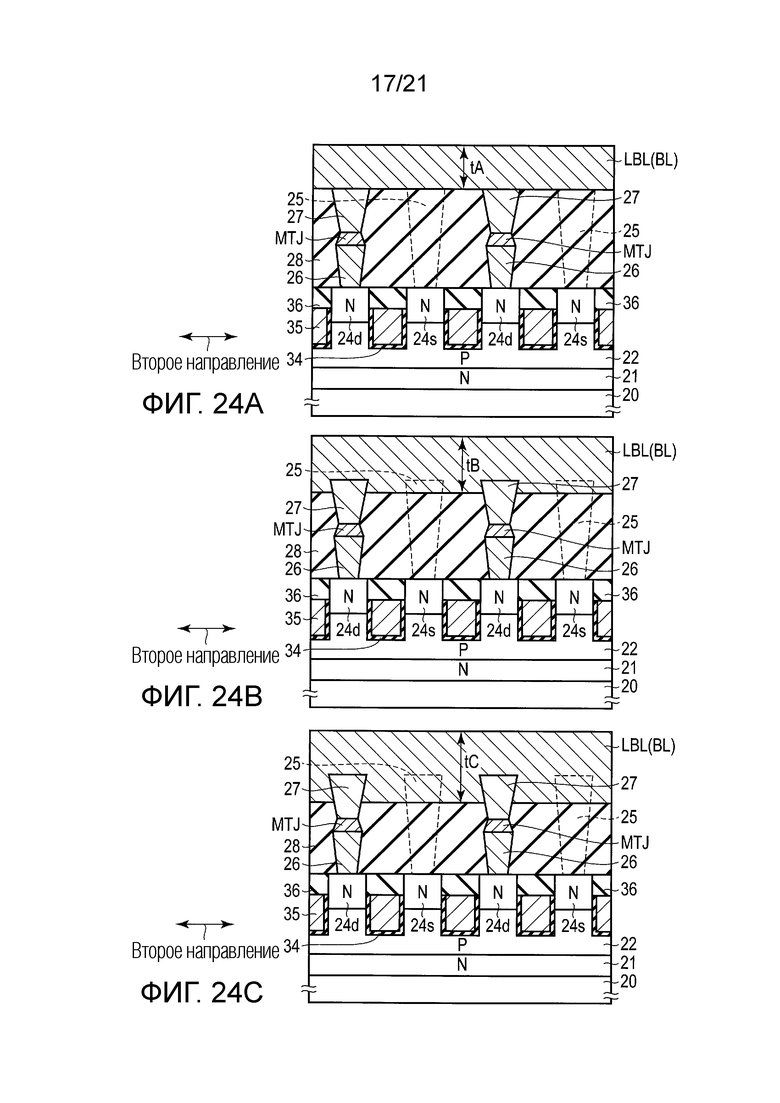

Фиг. 23A, 23B, и 23C являются сечениями по линии XXIII-XXIII фиг. 21.

Фиг. 24A, 24B, и 24C являются сечениями по линии XXIII-XXIII фиг. 21.

Фиг. 25 является видом сверху, показывающим устройство в качестве третьего варианта осуществления.

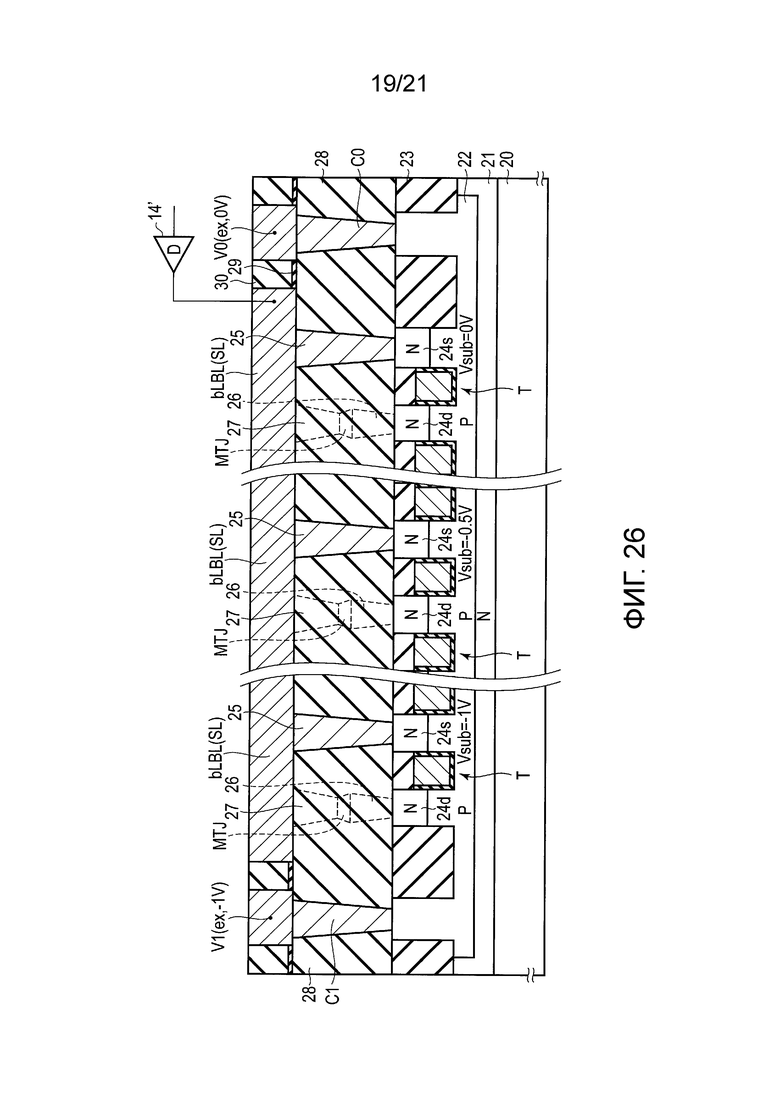

Фиг. 26 является сечением по линии XXVI-XXVI фиг. 25.

Фиг. 27 является видом сверху, показывающим устройство в качестве четвертого варианта осуществления.

Фиг. 28 является таблицей, показывающей пример потенциалов считывания/записи, подаваемых на выбранную числовую шину.

Фиг. 29 является схемой, показывающей пример процессорной системы.

Фиг. 30 и 31 являются сечениями, показывающими пример магниторезистивного элемента.

ПОДРОБНОЕ ОПИСАНИЕ

В общем, согласно одному варианту осуществления, запоминающее устройство с изменением сопротивления содержит: полупроводниковую подложку; транзистор с управляющим выводом, первым выводом и вторым выводом, причем транзистор обеспечен на полупроводниковой подложке; изолирующий слой, покрывающий транзистор; первую проводящую линию, соединенную с первым выводом и обеспеченную на изолирующем слое; вторую проводящую линию, обеспеченную на изолирующем слое; и элемент изменения сопротивления, присоединенный между вторым выводом и второй проводящей линией. Первая проводящая линия имеет большую ширину, чем ширина второй проводящей линии в направлении, в котором расположены первая и вторая проводящие линии.

(Варианты осуществления)

(1) Запоминающее устройство с изменением сопротивления

Фиг. 1 показывает пример запоминающего устройства с изменением сопротивления.

Массив 10 ячеек памяти включает в себя множество блоков MAT_0,..., MAT_n (где n является натуральным числом, большим или равным 1). Каждый из множества блоков MAT_0,..., MAT_n содержит множество ячеек памяти. Каждая из множества ячеек памяти содержит элемент изменения сопротивления и транзистор выбора.

Элемент изменения сопротивления является элементом, чье сопротивление изменяется напряжением, током, теплом, магнитным полем и т.д., и включает в себя элементы, такие как магниторезистивный элемент и элемент изменения фазы. Сопротивление элемента изменения сопротивления, т.е. данные, хранимые в элементе изменения сопротивления, считываются при прохождении тока считывания через элемент изменения сопротивления.

Транзистор выбора имеет функцию, например, подачи тока считывания на элемент изменения сопротивления во время считывания. Транзистор выбора является, например, полевым транзистором (FET).

Декодер 11а ряда и декодер 11b столбца реализуют произвольный доступ к множеству ячеек памяти в пределах множества блоков MAT_0,..., MAT_n на основе адресного сигнала Add (Добавить).

Цепь 12 выбора столбца имеет функцию электрического соединения, например, одного из блоков MAT_0,..., MAT_n и усилителя 13 считывания друг с другом, на основе сигнала выбора от декодера 11b столбца.

Цепь 14 управления считыванием/записью подает ток считывания на выбранную ячейку памяти во время считывания. Значение тока считывания изменяется сопротивлением выбранной ячейки памяти. А именно, при детектировании тока считывания усилитель 13 считывания может определить данные, хранимые в выбранной ячейке памяти.

Также, когда элемент изменения сопротивления является элементом, чье сопротивление изменяется током записи, подобным, например, магниторезистивному элементу, цепь 14 управления считыванием/записью подает ток записи на выбранную ячейку памяти во время записи.

Цепь 15 управления управляет работой декодера 11а ряда, декодера 11b столбца, усилителя 13 считывания и цепи 14 управления считыванием/записью.

Фиг. 2 показывает пример блока.

Здесь будет описан пример блока MAT_0 по фиг. 1. Другие блоки являются такими же, как блок MAT_0.

Блок MAT_0 содержит множество наборов, например, 256 наборов.

Один набор в пределах блока MAT_0 содержит множество локальных разрядных линий LBL (разрядных линий BL) и множество локальных разрядных линий bLBL (питающих линий SL). Множество локальных разрядных линий LBL и bLBL выровнено в первом направлении, и продолжается во втором направлении, пересекающем первое направление, соответственно.

Цепь 16а периферийных устройств расположена на первом краю блока MAT_0 во втором направлении. Цепь 16а периферийных устройств соединена с множеством локальных разрядных линий LBL (разрядных линий BL). Цепь 16b периферийных устройств расположена на втором краю блока MAT_0 во втором направлении. Цепь 16b периферийных устройств соединена с множеством локальных разрядных линий bLBL (питающих линий SL).

Глобальные разрядные линии GBL и bGBL и глобальная разрядная линия GRBL считывания расположены поверх множества локальных разрядных линий LBL (разрядных линий BL) и множества локальных разрядных линий bLBL (питающих линий SL).

Глобальная разрядная линия GBL продолжается во втором направлении и соединяется с цепью 16а периферийных устройств. Глобальная разрядная линия bGBL продолжается во втором направлении и соединяется с цепью 16b периферийных устройств. Глобальная разрядная линия GRBL считывания продолжается во втором направлении и соединяется с цепью 16а периферийных устройств. Для каждого набора обеспечивается группа из глобальной разрядной линии GBL, глобальной разрядной линии bGBL и глобальной разрядной линии GRBL считывания.

Фиг. 3 показывает пример массива ячеек памяти.

Блоки MAT_0,..., MAT_n соответствуют блокам MAT_0,..., MAT_n по фиг. 1. Каждый блок имеет схему размещения, показанную, например, на фиг. 2.

Каждый блок содержит ячейки U памяти (единичные ячейки), каждая из которых включает в себя элемент R изменения сопротивления и транзистор T выбора, соединенные последовательно.

Первый край на стороне элемента R изменения сопротивления в каждой ячейке U памяти соединен с локальной разрядной линией LBL (разрядной линией BL). Локальные разрядные линии LBL (разрядные линии BL) соединены с усилителем 13 считывания через цепь 12 выбора столбца (переключающий элемент) и глобальную разрядную линию GRBL считывания. Дополнительно локальные разрядные линии LBL (разрядные линии BL) соединены с цепью 14 управления записью (возбудителем). Цепь 14 управления записью (возбудитель) соединена с глобальной разрядной линией GBL.

Второй край на стороне транзистора T выбора каждой ячейки U памяти соединен с локальной разрядной линией bLBL (питающей линией SL). Локальные разрядные линии bLBL (питающие линии SL) соединены с цепью 14' управления считыванием/записью (возбудителем) через цепь 12 выбора столбца (переключающий элемент). Цепь 14' управления считыванием/записью (возбудитель) соединена с глобальной разрядной линией bGBL.

В этом случае один набор содержит восемь столбцов, т.е. восемь локальных разрядных линий LBL (разрядных линий BL) и восемь локальных разрядных линий bLBL (питающих линий SL). Цепь 12 выбора столбца выбирает один из восьми столбцов на основе сигналов CSL0,..., CSL7 выбора столбцов. Также один набор содержит 256 рядов, т.е. 256 числовых шин WLO,..., WL 255. Усилитель 13 считывания сравнивает сигнал от глобальной разрядной линии GRBL считывания с сигналом из эталонной линии RL и выдает выходной сигнал VOUT.

(2) Сравнительный пример

Будет описан пример структуры массива ячеек памяти.

Фиг. 4 показывает устройство в качестве сравнительного примера. Фиг. 5А является сечением по линии VA-VA по фиг. 4, и фиг. 5В является сечением по линии VB-VB по фиг. 4.

Полупроводниковая подложка 20 является, например, кремниевой подложкой. Карман 21 n-типа и карман 22 p-типа расположены в пределах полупроводниковой подложки 20. Изолирующий слой 23 для изоляции элементов расположен в пределах кармана 22 p-типа. Изолирующий слой 23 для изоляции элементов имеет структуру изоляции мелкими канавками (STI).

Область, окруженная изолирующим слоем 23 для изоляции элементов, является активной областью. Транзистор T выбора расположен в кармане 22 p-типа в активной области. Транзистор T выбора содержит истоковую область (S) 24s n-типа, стоковую область (D) 24d n-типа и электрод 35 затвора, расположенный между истоковой и стоковой областями 24s и 24d.

Электрод 35 затвора также служит в качестве числовой шины WL. Изолирующий слой 34 затвора расположен между карманом 22 p-типа и электродом 35 затвора. Накрывающий изолирующий слой 36 покрывает верхнюю поверхность электрода 35 затвора. Электрод 35 затвора имеет структуру со скрытым затвором, которая скрыта, например, в кармане 22 p-типа.

Изолирующий слой 28 покрывает транзистор T выбора. Локальные разрядные линии LBL (разрядные линии BL) и локальные разрядные линии bLBL (питающие линии SL) расположены на изолирующем слое 28.

Каждая из локальных разрядных линий LBL (разрядных линий BL) соединена с элементом R изменения сопротивления через контактный стержень (межсоединение) 27. Элемент R изменения сопротивления соединен со стоковой областью 24d n-типа через контактный стержень 26. Локальная разрядная линия bLBL (питающая линия SL) соединена с истоковой областью 24s n-типа через контактный стержень 25.

Контактные стержни 25, 26 и 27 включают в себя, например, одно из W, Ta, Ti, TaN и TiN.

Изолирующие слои 29 и 30 расположены между локальной разрядной линией LBL (разрядной линией BL) и локальной разрядной линией bLBL (питающей линией SL).

В данном случае, в то время как истоковая область (S) 24s и стоковая область (D) 24d являются n-типом, они могут быть заменены на p-тип. В таком случае истоковые области (S) 24s и стоковые области (D) 24d могут быть образованы в кармане n-типа.

Фиг. 6 и 7 показывают пример изменения в потенциале питающей линии во время считывания.

В запоминающем устройстве с изменением сопротивления, показанном на фиг. 1-3, эквивалентная цепь во время считывания представлена в упрощенном виде, как показано на фиг. 6.

Таким образом, чем больше миниатюризирована ячейка U памяти (единичная ячейка), тем выше становится сопротивление локальной разрядной линии bLBL (питающей линии SL). В этом случае, например, когда ток Ir считывания протекает через ячейку U памяти во время считывания, согласно положения ячейки U памяти (точка Х) возникает явление, при котором потенциал Vs истока транзистора T выбора изменяется.

Например, как показано на фиг. 7, согласно положению точки Х, потенциал в точке Х (потенциал Vs истока транзистора T выбора) изменяется в диапазоне от VL до VH. Однако предполагается, что VL<VH.

Вышеупомянутое означает, что существуют изменения в разнице между потенциалом Vg затвора и потенциалом Vs истока транзистора T выбора в зависимости от положения ячейки U памяти во время считывания, т.е. существуют изменения в токе Ir считывания, который протекает в ячейке U памяти.

Эти изменения обусловливают ошибки считывания во время считывания. Также то же самое можно сказать, когда данные записываются на элемент R изменения сопротивления током записи. Таким образом, во время записи, когда возникают изменения в потенциале Vs истока транзистора T выбора, возникают изменения в токе записи, и это обусловливает ошибки записи.

(3) Первый вариант осуществления

Фиг. 8 показывает устройство в качестве первого варианта осуществления. Фиг. 9А является сечением по линии IXA-IXA по фиг. 8, и фиг. 9В является сечением по линии IXB-IXB по фиг. 8.

Первый вариант осуществления имеет признак, заключающийся в том, что в отличие от сравнительного примера (фиг. 6 и 7), ширина локальной разрядной линии bLBL (питающей линии SL) больше, чем ширина локальной разрядной линии LBL (разрядной линии BL) в первом направлении, в котором локальные разрядные линии LBL (разрядные линии BL) и локальные разрядные линии bLBL (питающие линии SL) выровнены.

Поскольку другие части являются такими же, как части сравнительного примера, те же самые ссылочные позиции присвоены элементам, которые являются такими же, как элементы сравнительного примера, и подробное объяснение их опущено.

В сравнительном примере, причина наличия изменений в токе считывания/записи во время считывания/записи состоит в том, что потенциал истока транзистора выбора изменяется согласно положению ячейки памяти.

Следовательно, в первом варианте осуществления при увеличении ширины локальной разрядной линии bLBL (питающей линии SL) таким образом, чтобы она была больше ширины локальной разрядной линии LBL (разрядной линии BL), сопротивление локальной разрядной линии bLBL (питающей линии SL) может быть уменьшено.

Вследствие этого, поскольку изменения в потенциале Vs истока транзистора T выбора уменьшаются, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

Фиг. 10 и 11 показывают пример изменения в потенциале питающей линии во время считывания.

Согласно первому варианту осуществления, разница между VL и VH может быть выполнена меньшей, чем эта разница в сравнительном примере.

Следует отметить, что VL является потенциалом Vs истока транзистора T выбора ячейки памяти, которая соединена с начальной точкой (Точкой Х_нач) локальной разрядной линии bLBL (питающей линии SL), т.е. ячейка памяти, которая является ближайшей к возбудителю, который подает потенциал заземления на локальную разрядную линию bLBL (питающую линию SL).

Также VH является потенциалом Vs истока транзистора T выбора ячейки памяти, которая соединена с конечной точкой (Точкой Х_кон) локальной разрядной линии bLBL (питающей линии SL), т.е. ячейки памяти, которая является самой дальней от возбудителя, который подает потенциал заземления на локальную разрядную линию bLBL (питающую линию SL).

В этом случае может быть уменьшена разница между током Ir_VL считывания, который протекает в ячейке памяти, соединенной с Точкой Х_нач, и током Ir_VH считывания, который протекает в ячейке памяти, соединенной с Точкой Х_кон. Поскольку это означает, что изменение αr в токе считывания, показанное на фиг. 12, уменьшается, например, ошибка считывания может быть уменьшена.

Подобным образом может быть уменьшена разница между током Iw_VL записи, который протекает в ячейке памяти, соединенной с Точкой Х_нач, и током Iw_VH записи, который протекает в ячейке памяти, соединенной с Точкой Х_кон. Поскольку это означает, что изменение αw в токе записи, показанное на фиг. 12, уменьшается, например, ошибка записи может быть уменьшена.

Следует отметить, что на фиг. 12 I представляет значение тока, который подается на ячейку памяти, и R представляет сопротивление элемента изменения сопротивления в пределах ячейки памяти. Ir представляет эталонное значение тока считывания, Iw_L представляет эталонное значение тока записи, когда элемент изменения сопротивления изменяется таким образом, что его сопротивление становится низким, и Iw_H представляет эталонное значение тока записи, когда элемент изменения сопротивления изменяется таким образом, что его сопротивление становится высоким.

Дополнительно, Ir_VL, Ir_VH, Iw_VL, и Iw_VH по фиг. 12 соответствуют Ir_VL, Ir_VH, Iw_VL, и Iw_VH по фиг. 10.

Фиг. 13-19 показывают способ изготовления устройства по фиг. 8, 9A, и 9B. Поскольку устройство по фиг. 8, 9A, и 9B имеет упомянутый признак в структуре локальной разрядной линии LBL (разрядной линии BL) и локальной разрядной линии bLBL (питающей линии SL), будет описан способ изготовления этой структуры.

Сначала, как показано на фиг. 13, посредством обычной технологии изготовления полупроводниковых приборов выполняют этапы образования транзистора выбора и элемента изменения сопротивления на полупроводниковой подложке 20, покрытия их изолирующим слоем 28 (например, слоем оксида кремния) и образования контактных стержней 25 и 26. На фиг. 13 таким же элементам, как элементы, показанные на фиг. 8, 9A, и 9B, присвоены те же самые ссылочные позиции.

После вышеупомянутых этапов на изолирующем слое 28 в качестве ограничителя травления образуют изолирующий слой 29 (например, слой нитрида кремния). После этого на изолирующем слое 29 образуют изолирующий слой 30 (например, слой оксида кремния) и изолирующий слой 31 (например, слой нитрида кремния).

Дополнительно на изолирующем слое 31 в качестве стойкой маски образуют изолирующий слой 32 (например, слой оксида кремния).

Далее, как показано на фиг. 14, осуществляют усадку изолирующего слоя 32, например, изотропным травлением с использованием химического раствора. В результате ширина W1 изолирующего слоя 32 может быть задана меньшей, чем минимальная ширина обработки, получаемая, например, при фотолитографии. Ширина W1 изолирующего слоя 32 оказывается шириной локальной разрядной линии (разрядной линии), которая будет описана ниже.

Далее, как показано на фиг. 15, в качестве боковой стенки на боковой стенке изолирующего слоя 32 образуют изолирующий слой 33 (например, слой нитрида кремния). Дополнительно, когда изолирующий слой 32 выборочно удаляют, как показано на фиг. 16, два типа ширины, т.е. ширина W1 и ширина W2, образуются изолирующим слоем 33. После этого, когда изолирующий слой 31 травят методом реактивного ионного травления (RIE) с изолирующим слоем 33, используемым в качестве маски, получают структуру, показанную на фиг. 17.

Дополнительно, когда изолирующий слой 30 травят методом RIE с изолирующим слоем 33, используемым в качестве маски, получают структуру, показанную на фиг. 18. В этом травлении изолирующий слой 29 служит в качестве ограничителя травления. Соответственно, изолирующий слой 28 не будет протравлен при этом травлении. После этого изолирующий слой 29, как ограничитель травления, выборочно удаляют.

Наконец, как показано на фиг. 19, на изолирующем слое 28 образуют проводящий слой, который заполняет пространство в изолирующих слоях 29 и 30. Дополнительно, например, методом химико-механического полирования (CMP) проводящим слоем заполняют пространство в изолирующих слоях 29 и 30.

В результате образуют, соответственно, локальную разрядную линию LBL (разрядную линию BL) с шириной W1 и локальную разрядную линию bLBL (питающую линию SL) с шириной W2.

Посредством вышеупомянутых этапов завершают изготовление устройства по фиг. 8, 9A, и 9B.

Согласно первому варианту осуществления, явление, при котором возникают изменения в токе считывания/записи, который может пропускать транзистор выбора, может быть ограничено увеличением ширины локальной разрядной линии bLBL (питающей линии SL). Соответственно, могут быть предотвращены ошибки считывания и ошибки записи, и т.д.

(4) Второй вариант осуществления

Фиг. 20A и 20B показывают устройство в качестве второго варианта осуществления. Фиг. 21 является видом сверху областей AA, BB, и CC по фиг. 20A и 20B.

Второй вариант осуществления имеет признак, заключающийся в том, что в отличие от сравнительного примера (фиг. 6 и 7), толщина локальной разрядной линии bLBL (питающей линии SL) является постепенно увеличивающейся по мере того, как она отдаляется от возбудителя 14' во втором направлении, в котором продолжаются локальные разрядные линии LBL (разрядные линии BL) и локальные разрядные линии bLBL (питающие линии SL).

Таким образом, локальная разрядная линия bLBL (питающая линия SL) содержит первый участок, имеющий первую толщину, и второй участок, имеющий вторую толщину, которая больше первой толщины.

Поскольку другие части являются такими же, как части сравнительного примера, те же самые ссылочные позиции присвоены элементам, которые являются такими же, как элементы сравнительного примера, и подробное объяснение их опущено.

В сравнительном примере причина наличия изменений в токе считывания/записи во время считывания/записи состоит в том, что потенциал истока транзистора выбора изменяется согласно положению ячейки памяти.

Следовательно, во втором варианте осуществления при постепенном увеличении толщины локальной разрядной линии bLBL (питающей линии SL) по мере того, как она отдаляется от возбудителя 14', который возбуждает локальную разрядную линию bLBL (питающую линию SL), сопротивление локальной разрядной линии bLBL (питающей линии SL) может быть уменьшено.

Вследствие этого, поскольку изменения в потенциале Vs истока транзистора T выбора уменьшаются, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

Например, фиг. 22А является сечением по линии XXII-XXII по фиг. 21 в качестве вида сверху области AA по фиг. 20A и 20B. Дополнительно, фиг. 22B является сечением по линии XXII-XXII по фиг. 21 в качестве вида сверху области ВВ по фиг. 20A и 20B. Дополнительно, фиг. 22С является сечением по линии XXII-XXII по фиг. 21 в качестве вида сверху области СС по фиг. 20A и 20B.

Как ясно из фиг. 22A, 22B, и 22C, в области А (области, которая является ближайшей к возбудителю 14') по фиг. 20A и 20B, локальная разрядная линия bLBL (питающая линия SL) имеет толщину tA. Дополнительно, в области В по фиг. 20A и 20B локальная разрядная линия bLBL (питающая линия SL) имеет толщину tB. Кроме того, в области С (области, которая является самой дальней от возбудителя 14') по фиг. 20A и 20B локальная разрядная линия bLBL (питающая линия SL) имеет толщину tC. Однако соотношение толщин составляет tA<tB<tC.

Здесь толщина локальной разрядной линии LBL (разрядной линии BL) может также постепенно увеличиваться по мере того, как она отдаляется от усилителя 13 считывания.

Например, фиг. 23А является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области АА по фиг. 20А. Дополнительно, фиг. 23В является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области ВВ по фиг. 20А. Кроме того, фиг. 23С является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области СС по фиг. 20А.

Как ясно из фиг. 23A, 23B, и 23C, в области A (области, которая является самой дальней от усилителя 13 считывания) по фиг. 20А, локальная разрядная линия LBL (разрядная линия BL) имеет толщину tA. Дополнительно, в области В по фиг. 20А локальная разрядная линия LBL (разрядная линия BL) имеет толщину tB. Кроме того, в области С (области, которая является ближайшей к усилителю 13 считывания) по фиг. 20А локальная разрядная линия LBL (разрядная линия BL) имеет толщину tC. Однако соотношение толщин составляет tA>tB>tC.

Локальная разрядная линия LBL (разрядная линия BL), имеющая множественные толщины, или локальная разрядная линия bLBL (питающая линия SL), имеющая множественные толщины, как описано выше, могут быть легко изготовлены при выполнении литографии несколько раз при образовании локальной разрядной линии LBL (разрядной линии BL) и локальной разрядной линии bLBL (питающей линии SL).

Однако в примере по фиг. 20А направление, в котором толщина локальной разрядной линии LBL (разрядной линии BL) постепенно увеличивается, и направление, в котором толщина локальной разрядной линии bLBL (питающей линии SL) постепенно увеличивается, являются противоположными друг другу.

В этом случае этап литографии локальной разрядной линии LBL (разрядной линии BL) или локальной разрядной линии bLBL (питающей линии SL) становится усложненным.

Соответственно, как показано, например, на фиг. 20В, край на стороне усилителя 13 считывания локальной разрядной линии LBL (разрядной линии BL) следует предпочтительно выполнить соответствующим краю на стороне возбудителя 14' локальной разрядной линии bLBL (питающей линии SL).

Это связано с тем, что при схеме размещения по фиг. 20В, направление, в котором толщина локальной разрядной линии LBL (разрядной линии BL) постепенно увеличивается, становится таким же, как направление, в котором толщина локальной разрядной линии bLBL (питающей линии SL) постепенно увеличивается. Таким образом может быть обеспечена унифицированность для этапа литографии локальной разрядной линии LBL (разрядной линии BL) и этапа литографии локальной разрядной линии bLBL (питающей линии SL).

Например, фиг. 24А является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области АА по фиг. 20В. Дополнительно, фиг. 24В является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области ВВ по фиг. 20В. Кроме того, фиг. 24С является сечением по линии XXIII-XXIII по фиг. 21 в качестве вида сверху области СС по фиг. 20В.

Как ясно из фиг. 24A, 24B, и 24C, в области A (области, которая является ближайшей к усилителю 13 считывания) по фиг. 20В, локальная разрядная линия LBL (разрядная линия BL) имеет толщину tA. Дополнительно, в области В по фиг. 20В локальная разрядная линия LBL (разрядная линия BL) имеет толщину tB. Кроме того, в области С (области, которая является самой дальней от усилителя 13 считывания) по фиг. 20В локальная разрядная линия LBL (разрядная линия BL) имеет толщину tC. Однако соотношение толщин составляет tA<tB<tC.

Соотношение толщин локальной разрядной линии LBL (разрядной линии BL) этого случая является таким же, как соотношение толщин (tA<tB<tC) локальной разрядной линии bLBL (питающей линии SL), показанной на фиг. 22A, 22B, и 22C.

Согласно второму варианту осуществления, явление, при котором возникают изменения в токе считывания/записи, который может пропускать транзистор выбора, может быть ограничено при изменении толщины локальной разрядной линии LBL (разрядной линии BL) или локальной разрядной линии bLBL (питающей линии SL). Соответственно, могут быть предотвращены ошибки считывания и ошибки записи, и т.д.

(5) Третий вариант осуществления

Фиг. 25 показывает устройство в качестве третьего варианта осуществления. Фиг. 26 является сечением по линии XXVI-XXVI по фиг. 25.

Третий вариант осуществления имеет признак, заключающийся в том, что в отличие от сравнительного примера (фиг. 6 и 7), в кармане 22 p-типа, в котором транзистор T выбора (например, FET) ячейки памяти расположен во втором направлении, в котором продолжаются локальные разрядные линии LBL (разрядные линии BL) и локальные разрядные линии bLBL (питающие линии SL), обеспечен градиент потенциалов.

Таким образом, при операции считывания с использованием усилителя 13 считывания, когда возбудитель 14' подает потенциал Vss заземления к концу локальных разрядных линий bLBL (питающих линий SL), на краевом участке, который ближе к возбудителю 14' во втором направлении в пределах кармана 22 p-типа расположен первый контакт C0, который подает первый потенциал, а на краевом участке, который дальше от возбудителя 14' во втором направлении в пределах кармана 22 p-типа расположен второй контакт C1, который подает второй потенциал, меньший, чем первый потенциал.

Например, когда первый потенциал является потенциалом Vss заземления, второй потенциал является отрицательным потенциалом (например, -1В).

В этом случае потенциал кармана 22 p-типа постепенно изменяется от первого потенциала до второго потенциала в направлении перехода ко второму контакту С1 от первого контакта С0.

Это означает, что чем дальше находится транзистор T выбора от возбудителя 14', т.е. чем выше становится потенциал истока транзистора T выбора, тем большим постепенно становится абсолютное значение напряжения смещения нижнего затвора транзистора T выбора (отрицательного потенциала, когда транзистор T выбора является FET с каналом n-типа).

Соответственно, напряжение смещения нижнего затвора транзистора выбора может компенсировать уменьшение тока считывания/записи, обусловленное увеличением потенциала истока транзистора выбора. Таким образом, даже если возникнут изменения в потенциале истока транзистора T выбора, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

Поскольку другие части являются такими же, как части сравнительного примера, те же самые ссылочные позиции присвоены элементам, которые являются такими же, как элементы сравнительного примера, и подробное объяснение их опущено.

Согласно третьему варианту осуществления, явление, при котором возникают изменения в токе считывания/записи, который может пропускать транзистор выбора, может быть ограничено при изменении напряжения смещения нижнего затвора транзистора выбора. Соответственно, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

(6) Четвертый вариант осуществления

Фиг. 27 показывает устройство в качестве четвертого варианта осуществления. Фиг. 28 показывает потенциал считывания/записи, который подается на выбранную числовую шину во время считывания/записи.

Четвертый вариант осуществления имеет признак, заключающийся в том, что в отличие от сравнительного примера (фиг. 6 и 7), ячейка памяти разделена на множество областей A, B, и C во втором направлении, в котором продолжаются локальные разрядные линии LBL (разрядные линии BL) и локальные разрядные линии bLBL (питающие линии SL), и потенциал считывания/записи выбранной числовой шины изменяется для каждой из областей A, B, и C.

Например, в операции считывания с использованием усилителя 13 считывания предполагается случай, когда возбудитель 14' подает потенциал Vss заземления на конец локальной разрядной линии bLBL (питающей линии SL).

В этом случае, когда выбранная числовая шина существует в области А (адрес Ayy+1-Azz), которая является ближайшей к возбудителю 14', потенциалы считывания и записи, подлежащие подаче на выбранную числовую шину, задаются равными Vr2 и Vw2, соответственно. Дополнительно, когда выбранная числовая шина существует в области В (адрес Axx+1-Ayy), потенциалы считывания и записи, подлежащие подаче на выбранную числовую шину, задаются равными Vr1 и Vw1, соответственно. Кроме того, когда выбранная числовая шина существует в области С (адрес A00-Axx), которая является самой дальней от возбудителя 14', потенциалы считывания и записи, подлежащие подаче на выбранную числовую шину, задаются равными Vr0 и Vw0, соответственно. Однако соотношение потенциалов составляет Vr0>Vr1>Vr2, а также Vw0>Vw1>Vw2.

Как можно увидеть, постепенное увеличение потенциала затвора транзистора выбора по мере того, как он отдаляется от возбудителя 14', может компенсировать уменьшение тока считывания/записи, обусловленное отдалением возбудителя 14' от транзистора выбора, т.е. увеличением потенциала истока транзистора выбора. Таким образом, даже если возникнут изменения в потенциале истока транзистора T выбора, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

Поскольку другие части являются такими же, как части сравнительного примера, те же самые ссылочные позиции присвоены элементам, которые являются такими же, как элементы сравнительного примера, и подробное объяснение их опущено.

Согласно четвертому варианту осуществления, явление, при котором возникают изменения в токе считывания/записи, который может пропускать транзистор выбора, может быть ограничено при изменении потенциала затвора транзистора выбора согласно положению транзистора выбора. Соответственно, могут быть эффективно предотвращены ошибки считывания и ошибки записи, и т.д.

(Пример применения)

Запоминающее устройство с изменением сопротивления согласно вышеупомянутым вариантам осуществления может быть применено для STT-MRAM (магниторезистивного запоминающего устройства с произвольным доступом с переносом спинового момента). Далее будет описано STT-MRAM.

Требуется, чтобы процессор, используемый для персонального цифрового секретаря, имел низкое энергопотребление. В качестве одного пути уменьшения энергопотребления процессора, один способ, который может быть выбран, состоит в замене кэш-памяти на основе статической памяти с произвольным доступом (SRAM), имеющей высокое энергопотребление в режиме ожидания, на STT-MRAM.

Таким образом, согласно миниатюризации транзистора, в SRAM мощность утечки стремится быть большей как во время работы, так и во время ожидания (нерабочего времени). Соответственно, при использовании STT-MRAM в качестве кэш-памяти становится возможным прерывать питание во время режима ожидания, и может быть реализована процессорная система с низким энергопотреблением, в которой энергопотребление во время режима ожидания очень мало.

Фиг. 29 показывает пример процессорной системы с низким энергопотреблением.

CPU 41 управляет SRAM 42, DRAM 43, флэш-памятью 44, ROM 45 и MRAM 46.

MRAM 46 соответствует запоминающему устройству с изменением сопротивления согласно вышеупомянутым вариантам осуществления.

MRAM 46 может быть использовано в качестве замены для SRAM 42, DRAM 43, флэш-памяти 44 и ROM 45. Соответственно, по меньшей мере одна из SRAM 42, DRAM 43, флэш-памяти 44 и ROM 45 может быть опущена.

MRAM 46 используют в качестве энергонезависимой кэш-памяти (например, L2-кэша).

Фиг. 30 показывает пример магниторезистивного элемента в качестве ячейки памяти MRAM.

Магниторезистивный элемент MTJ имеет слоистую структуру, в которой слой 51 хранения (данных) (ферромагнитный слой) с перпендикулярной и изменяемой намагниченностью, туннельный барьерный слой 52 (немагнитный слой) и эталонный слой 53 (ферромагнитный слой) с перпендикулярной и неизменяемой намагниченностью расположены в этом порядке в направлении, перпендикулярном поверхности пленки (т.е. перпендикулярном направлении).

Здесь неизменяемая намагниченность означает, что направление намагниченности не изменяется до и после записи, а изменяемая намагниченность означает, что направление намагниченности может быть изменено на противоположное направление до и после записи.

Дополнительно, запись означает запись с переносом спина, в которой спиновый момент прикладывается к намагниченности слоя 51 хранения при прохождении тока записи (электронов с поляризованными спинами) в магниторезистивном элементе MTJ.

Например, когда ток записи проходит от слоя 51 хранения к эталонному слою 53, электрон, который поляризован по спину в том же самом направлении, что и намагниченность эталонного слоя 53, инжектируется в слой 51 хранения, и спиновый момент прикладывается к намагниченности в слое 51 хранения. Таким образом, направление намагниченности слоя 51 хранения становится таким же, как направление намагниченности эталонного слоя 53 (т.е. возникает параллельное состояние).

Дополнительно, когда ток записи протекает от эталонного слоя 53 к слою 51 хранения, электрон, который поляризован по спину в направлении, противоположном намагниченности эталонного слоя 53, из электронов, переходящих в эталонный слой 53 из слоя 51 хранения, возвращается в слой 51 хранения, и к намагниченности в слое 51 хранения прикладывается спиновый момент. Таким образом, направление намагниченности слоя 51 хранения становится противоположным направлению намагниченности эталонного слоя 53 (т.е. возникает антипараллельное состояние).

Сопротивление магниторезистивного элемента MTJ изменяется в зависимости от относительных направлений намагниченности слоя 51 хранения и эталонного слоя 53 посредством магниторезистивного эффекта. Таким образом, сопротивление магниторезистивного элемента MTJ является низким в параллельном состоянии и высоким в антипараллельном состоянии.

Слой 51 хранения и эталонный слой 53 содержат, например, CoFeB, MgFeO, FeB, слоистую структуру из них и т.д. В случае магниторезистивных элементов с вертикальной намагниченностью, слой 51 хранения и эталонный слой 53 должны предпочтительно содержать TbCoFe, имеющий перпендикулярную магнитную анизотропию, искусственную решетку, в которой послойно размещены Co и Pt, FePt, упорядоченный L1o и т.п. В этом случае CoFeB или FeB могут быть обеспечены в виде промежуточных слоев между слоем 51 хранения и туннельным барьерным слоем 52 и между туннельным барьерным слоем 52 и эталонным слоем 53.

Например, предпочтительно, чтобы слой 51 хранения включал в себя CoFeB или FeB, а эталонный слой 53 включал в себя CoPt, CoNi, или CoPd.

Туннельный барьерный слой 52 содержит, например, MgO, AlO и т.п. Туннельный барьерный слой 52 может быть оксидом Al, Si, Be, Mg, Ca, Sr, Ba, Sc, Y, La, Zr, Hf и т.д. Когда для туннельного барьерного слоя 52 используется MgO, вследствие ограничения на сопротивление толщина задается составляющей приблизительно 1 нм.

Следует отметить, что в то время как намагниченность эталонного слоя 53 является фиксированной в направлении к слою 51 хранения в этом случае, она может быть фиксированной в направлении от слоя 51 хранения. Дополнительно, при расположении магниторезистивного элемента MTJ на полупроводниковой подложке конкретно не ограничивается, какой из эталонного слоя 53 и слоя 51 хранения должен быть верхним.

Например, когда эталонный слой 53 расположен поверх слоя 51 хранения, магниторезистивный элемент MTJ называют магниторезистивным элементом с верхним контактом, а когда эталонный слой 53 расположен ниже слоя 51 хранения, магниторезистивный элемент MTJ называют магниторезистивным элементом с нижним контактом.

Фиг. 31 показывает пример магниторезистивного элемента, имеющего слой устранения сдвига.

Магниторезистивный элемент MTJ имеет слоистую структуру, в которой слой 51 хранения (ферромагнитный слой) с перпендикулярной и изменяемой намагниченностью, туннельный барьерный слой 52 (немагнитный слой) и эталонный слой 53 (ферромагнитный слой) с перпендикулярной и неизменяемой намагниченностью расположены в этом порядке в перпендикулярном направлении.

Также магниторезистивный элемент MTJ содержит слой 54 устранения сдвига (ферромагнитный слой), имеющий перпендикулярную и неизменяемую намагниченность, на стороне эталонного слоя 53. Между эталонным слоем 53 и слоем 54 устранения сдвига расположен немагнитный слой 55 (например, металлический слой).

В настоящем случае эталонный слой 53 и слой 51 хранения имеют перпендикулярную намагниченность. В этом случае, поскольку магнитное поле рассеяния из эталонного слоя 53 соответствует направлению намагниченности слоя 51 хранения (перпендикулярному направлению), магнитное поле рассеяния, имеющее большую перпендикулярную составляющую, прикладывается к слою 51 хранения. Это магнитное поле рассеяния имеет функцию, заключающуюся в том, чтобы сделать направление намагниченности слоя 51 хранения таким же, как направление намагниченности эталонного слоя 53 (таким образом, чтобы получить параллельное состояние).

Соответственно, кривая гистерезиса (характеристика перемагничивания) слоя 51 хранения сдвигается.

Таким образом, хотя при изменении состояния магниторезистивного элемента MTJ с антипараллельного состояния на параллельное состояние в магниторезистивном элементе MTJ достаточно протечь небольшому току записи, в случае изменения состояния магниторезистивного элемента MTJ с параллельного состояния на антипараллельное состояние, в магниторезистивном элементе MTJ должен протечь большой ток записи.

Кроме того, антипараллельное состояние является неустойчивым из-за магнитного поля рассеяния от эталонного слоя 53.

Таким образом, когда магнитное поле рассеяния становится больше коэрцитивной силы слоя 51 хранения, слой 51 хранения не может сохранять антипараллельное состояние. Также, даже если магнитное поле рассеяния меньше коэрцитивной силы слоя 51 хранения, с учетом флуктуаций намагниченности, обусловленных тепловым перемешиванием, намагниченность слоя 51 хранения может быть обращена магнитным полем рассеяния из антипараллельного состояния в параллельное состояние.

Для решения такой проблемы обеспечен слой 54 устранения сдвига.

В настоящем случае эталонный слой 53 и слой 54 устранения сдвига уложены один над другим. В этом случае направление намагниченности слоя 54 устранения сдвига задается противоположным направлению намагниченности эталонного слоя 53. Таким образом, в слое 51 хранения магнитное поле рассеяния из эталонного слоя 53 смещено устраняющим магнитным полем из слоя 54 устранения сдвига, и сдвиг кривой гистерезиса слоя 51 хранения может быть устранен.

Слой 54 устранения сдвига является магнитным слоем, подобным слою 51 хранения и эталонному слою 53, и имеет направление намагниченности, противоположное направлению намагниченности эталонного слоя 53. Слой 54 устранения сдвига, таким образом, устраняет сдвиг характеристики перемагничивания (кривой гистерезиса) слоя 51 хранения вследствие магнитного поля рассеяния из эталонного слоя 53. Например, предпочтительно, чтобы слой 54 устранения сдвига включал в себя CoPt, CoNi или CoPd. Например, слой 54 устранения сдвига содержит структуру [Co/Pt]n, получаемую наложением n слоев Co и n слоев Pt.

Немагнитный слой 55 функционирует в качестве буферного слоя, который разделяет эталонный слой 53 и слой 54 устранения сдвига. Немагнитный слой 55 содержит, например, металлический слой из Pt, W, Ta, Ru или подобного.

(Заключение)

Как описано выше, согласно настоящим вариантам осуществления, поскольку явление, при котором возникают изменения в токе считывания/записи, который может пропускать транзистор выбора, может быть ограничено, могут быть предотвращены ошибки считывания и ошибки записи, и т.д.

В то время как были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений. Действительно, новые варианты осуществления, описанные здесь, могут быть реализованы во множестве других форм; кроме того, различные опущения, замены и изменения в форме вариантов осуществления, описанных здесь, могут быть выполнены без выхода за рамки сущности изобретений. Предполагается, что прилагаемые пункты формулы изобретения и их эквиваленты охватывают такие формы или модификации, как находящиеся в пределах объема и сущности изобретений.

Изобретение относится к вычислительной технике. Технический результат заключается в предотвращении ошибок считывания и записи. Запоминающее устройство с изменением сопротивления содержит полупроводниковую подложку; обеспеченный на полупроводниковой подложке транзистор с управляющим выводом, первым выводом и вторым выводом; первый изолирующий слой, покрывающий транзистор и содержащий первый материал; второй изолирующий слой, обеспеченный на первом изолирующем слое и содержащий отличный от первого материала второй материал; третий изолирующий слой, обеспеченный на втором изолирующем слое и содержащий первый материал; первый контактный стержень, пронизывающий первый изолирующий слой и соединенный с первым выводом; первую и вторую проводящие линии; элемент изменения сопротивления, обеспеченный в первом изолирующем слое и присоединенный между вторым выводом и второй проводящей линией; второй контактный стержень, обеспеченный в первом изолирующем слое и присоединенный между элементом изменения сопротивления и второй проводящей линией; и третий контактный стержень, обеспеченный в первом изолирующем слое и присоединенный между элементом изменения сопротивления и вторым выводом. 4 з.п. ф-лы, 40 ил.

1. Запоминающее устройство с изменением сопротивления, содержащее:

полупроводниковую подложку;

обеспеченный на полупроводниковой подложке транзистор с управляющим выводом, первым выводом и вторым выводом;

первый изолирующий слой, покрывающий транзистор и содержащий первый материал;

второй изолирующий слой, обеспеченный на первом изолирующем слое и содержащий отличный от первого материала второй материал;

третий изолирующий слой, обеспеченный на втором изолирующем слое и содержащий первый материал;

первый контактный стержень, пронизывающий первый изолирующий слой и соединенный с первым выводом;

первую проводящую линию, пронизывающую третий изолирующий слой и второй изолирующий слой, соединенную с первым выводом через первый контактный стержень и обеспеченную на первом изолирующем слое;

вторую проводящую линию, пронизывающую третий изолирующий слой и второй изолирующий слой и обеспеченную на первом изолирующем слое;

элемент изменения сопротивления, обеспеченный в первом изолирующем слое и присоединенный между вторым выводом и второй проводящей линией;

второй контактный стержень, обеспеченный в первом изолирующем слое и присоединенный между элементом изменения сопротивления и второй проводящей линией; и

третий контактный стержень, обеспеченный в первом изолирующем слое и присоединенный между элементом изменения сопротивления и вторым выводом, при этом

первая проводящая линия и вторая проводящая линия расположены соприкасающимися с по существу одной и той же плоскостью, которая включает верхнюю поверхность первого контактного стержня, верхнюю поверхность второго контактного стержня и верхнюю поверхность первого изолирующего слоя, и

первая проводящая линия имеет большую ширину, чем ширина второй проводящей линии в направлении, в котором расположены первая и вторая проводящие линии.

2. Запоминающее устройство по п. 1, дополнительно содержащее:

усилитель считывания, соединенный со второй проводящей линией.

3. Запоминающее устройство по п. 2, дополнительно содержащее:

возбудитель, соединяющий первую проводящую линию с выводом заземления при операции считывания с использованием усилителя считывания.

4. Запоминающее устройство по п. 1, в котором

управляющий вывод обеспечен в полупроводниковой подложке.

5. Запоминающее устройство по п. 1, в котором

элемент изменения сопротивления содержит первый магнитный слой с неизменяемой намагниченностью, второй магнитный слой с изменяемой намагниченностью и немагнитный слой, обеспеченный между ними.

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| JP 2006303150 A, 02.11.2006 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| СПОСОБ ФОРМИРОВАНИЯ МАГНИТОРЕЗИСТИВНОГО ЭЛЕМЕНТА ПАМЯТИ НА ОСНОВЕ ТУННЕЛЬНОГО ПЕРЕХОДА И ЕГО СТРУКТУРА | 2012 |

|

RU2522714C2 |

Авторы

Даты

2019-10-07—Публикация

2016-03-14—Подача