ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение в общем относится к системе и способу регулирования параметров схемы памяти на основе сопротивления.

УРОВЕНЬ ТЕХНИКИ

Совершенствование техники в результате привело к созданию меньших по размеру и более мощных персональных вычислительных устройств. Например, в настоящее время существует множество портативных персональных вычислительных устройств, включая беспроводные вычислительные устройства, такие как портативные беспроводные телефоны, персональные цифровые помощники (PDA) и пейджинговые устройства, являющиеся небольшими, легкими и легко переносимыми пользователями. Более конкретно, портативные беспроводные телефоны, такие как сотовые телефоны и IP-телефоны, могут передавать голос и пакеты данных по беспроводным сетям. Дополнительно многие такие беспроводные телефоны включают другие типы встроенных в них устройств. Например, беспроводной телефон может также включать цифровую фотокамеру, цифровую видеокамеру, цифровое записывающее устройство и проигрыватель аудиофайлов. Также такие беспроводные телефоны могут обрабатывать выполнимые инструкции, включая программные приложения, такие как приложение вэб-браузера, которое может быть использовано для доступа в Интернет. Однако потребление мощности такими портативными устройствами может быстро истощать запас батареи и сокращать опыт пользователя.

Уменьшение потребления мощности привело к меньшим размерам элементов схемы и меньшим рабочим напряжениям внутри таких портативных устройств. Уменьшение размера элементов и рабочих напряжений при уменьшении потребления мощности также увеличивает чувствительность к шуму и к изменениям производственного процесса. Такая увеличенная чувствительность к шуму и изменениям процесса может быть трудной для преодоления при создании устройств памяти, использующих усилители считывания.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Исследования, проведенные профессором Seong-Ook Jung, Jisu Kim и Jee-Hwan Song из Университета Yonsei, совместно с Seung H. Kang и Sei Seung Yoon из Qualcomm Inc., привели в результате к новым системам и способам регулирования параметров схемы памяти на основе сопротивления.

В конкретном варианте осуществления раскрывается способ определения набора параметров схемы памяти на основе сопротивления. Данный способ включает в себя выбор первого параметра на основе первого предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления и выбор второго параметра на основе второго предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Способ дополнительно включает в себя выполнение итеративной методики для регулирования, по меньшей мере, одного параметра схемы участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного назначения и регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра или второго параметра.

В другом конкретном варианте осуществления раскрывается способ определения набора параметров схемы памяти на основе сопротивления. Данный способ включает в себя выбор первого параметра на основе первого предварительно заданного ограничения по конструкции магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM) и выбор второго параметра на основе второго предварительно заданного ограничения по конструкции STT-MRAM. Способ дополнительно включает в себя выполнение итеративной методики для регулирования, по меньшей мере, одного параметра схемы для участка усилителя считывания STT-MRAM посредством выборочного регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания, но без изменения первого параметра или второго параметра.

В другом конкретном варианте осуществления раскрывается считываемый процессором носитель хранения инструкций процессора. Инструкции процессора выполняются для предписания приема процессором первого ввода первого параметра на основе первого предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Инструкции процессора также выполняются для предписания приема процессором второго ввода второго параметра на основе второго предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Инструкции процессора дополнительно выполняются для предписания выполнения процессором итеративной методики для регулирования, по меньшей мере, одного параметра схемы участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра или второго параметра. Инструкции процессора также выполняются для предписания сохранения процессором значения, связанного с физической характеристикой, после того, как достигается желаемое граничное значение усилителя считывания с учетом предварительно заданного первого и второго ограничения по конструкции.

Конкретное преимущество, обеспечиваемое посредством раскрываемых вариантов осуществления, заключается в том, что параметры схемы могут определяться для достижения желаемой границы усилителя считывания в схеме памяти на основе сопротивления, имеющей другие ограничения по конструкции. Параметры схемы могут итеративно регулироваться на основе физических характеристик устройства и схемы для эффективного улучшения границ усилителя считывания.

Другие аспекты, преимущества и признаки по настоящему изобретению станут очевидны после анализа всей заявки, включающей в себя следующие разделы: «Краткое описание чертежей», «Подробное описание вариантов осуществления» и «Формула изобретения».

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

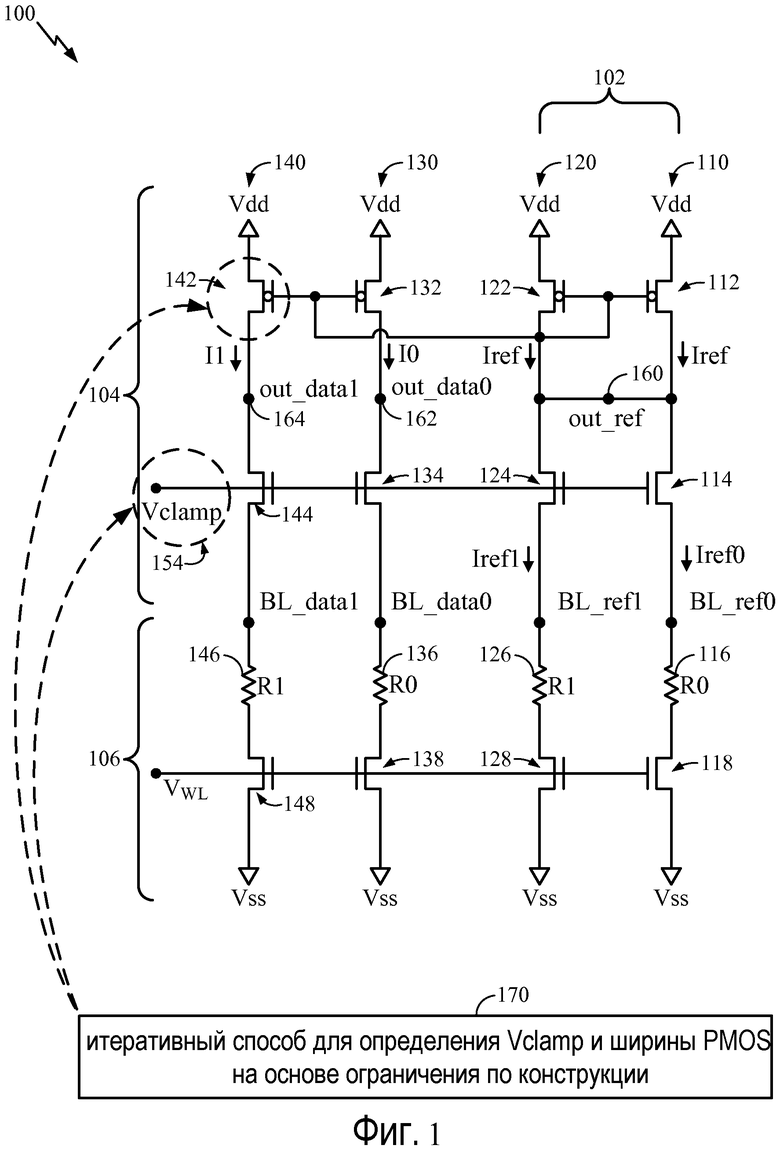

Фиг.1 представляет собой принципиальную схему конкретного иллюстративного варианта осуществления памяти на основе сопротивления;

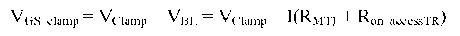

Фиг.2 представляет собой структурную иллюстрацию конкретного иллюстративного варианта осуществления системы для определения параметров схемы памяти на основе сопротивления для памяти, такой как память по Фиг.1;

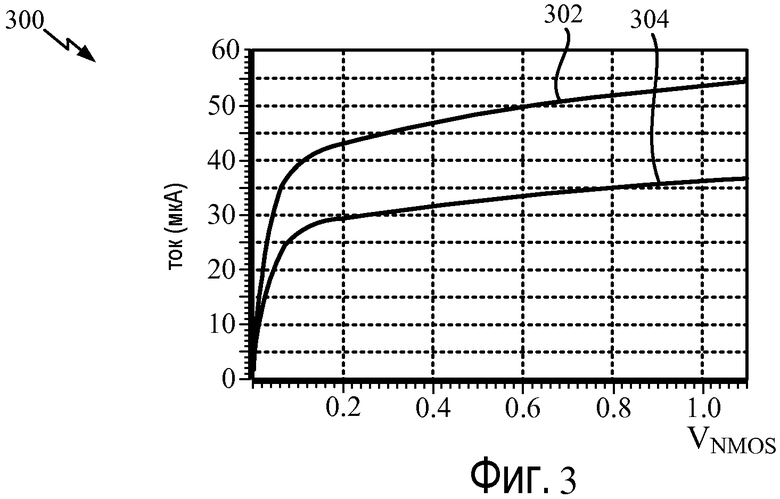

Фиг.3 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления вольтамперных характеристик фиксирующего устройства памяти на основе сопротивления;

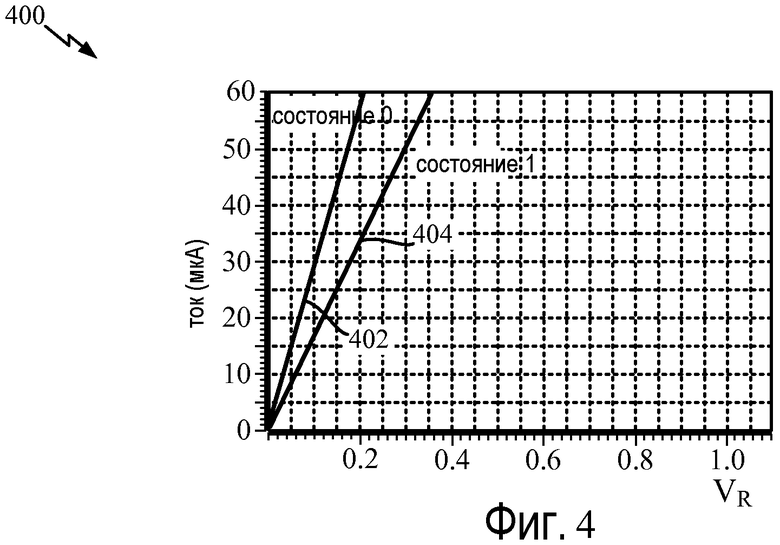

Фиг.4 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления вольтамперных характеристик комбинированного сопротивления и транзистора доступа;

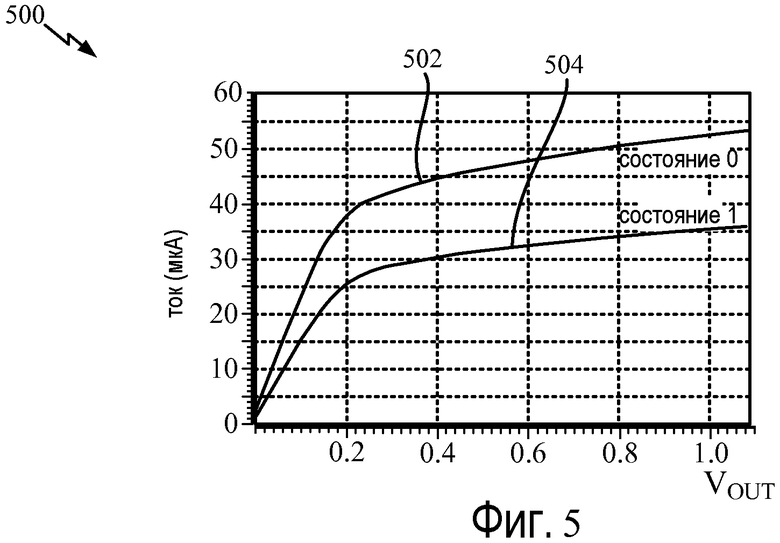

Фиг.5 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления вольтамперных характеристик фиксирующего устройства по Фиг.3, последовательно соединенного с элементом памяти на основе сопротивления по Фиг.4;

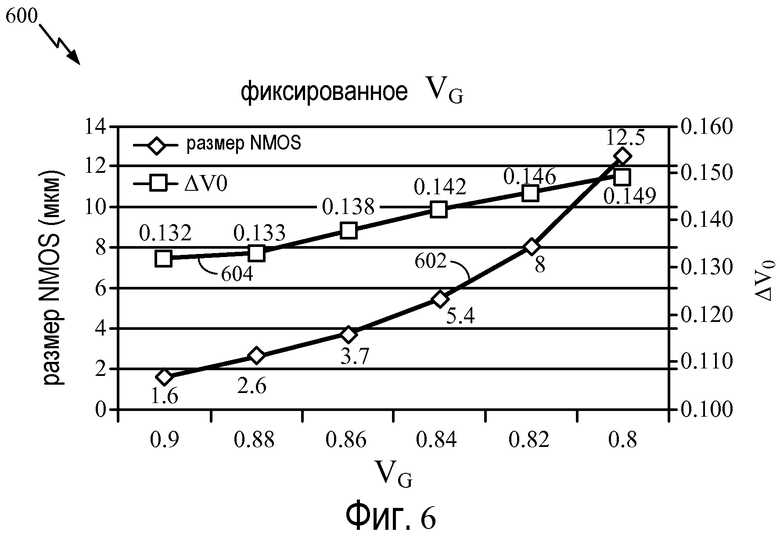

Фиг.6 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления характеристик памяти на основе сопротивления с переменным напряжением затвора фиксирующего устройства;

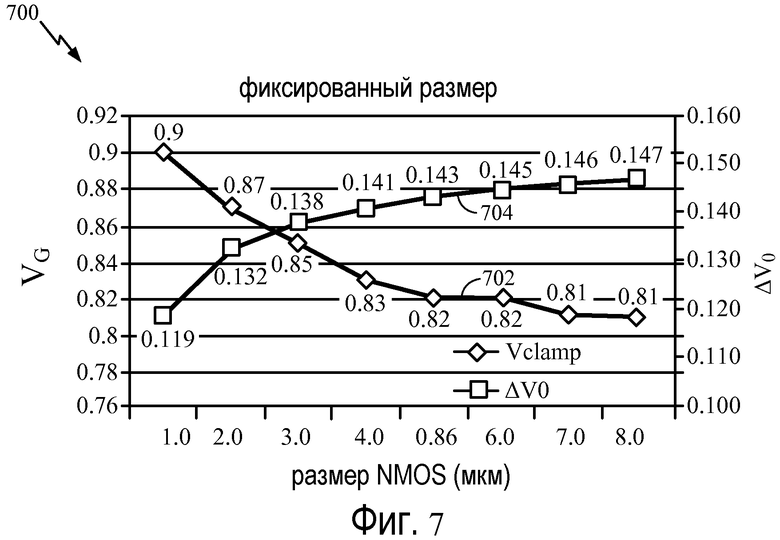

Фиг.7 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления характеристик памяти на основе сопротивления с изменяющимся размером фиксирующего устройства;

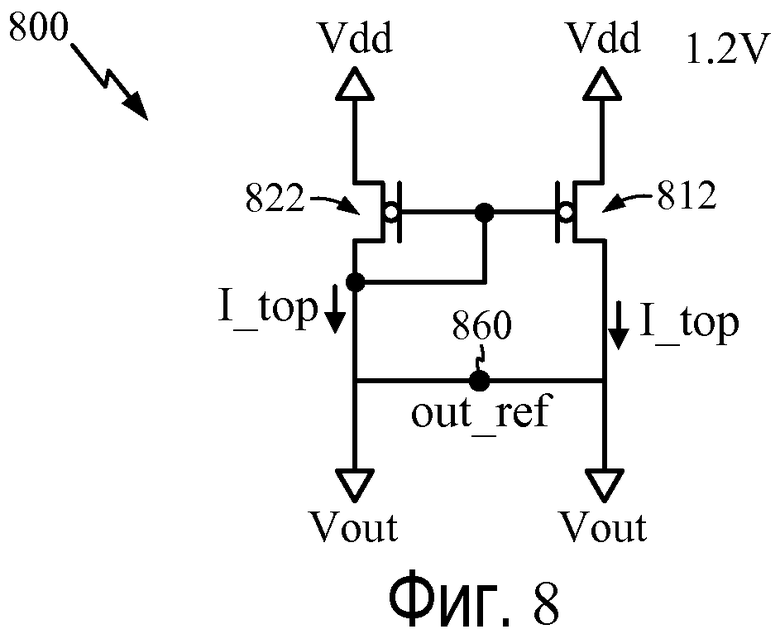

Фиг.8 представляет собой принципиальную схему конкретного иллюстративного варианта осуществления участка нагрузки схемы, соединенной с опорной ячейкой устройства памяти на основе сопротивления;

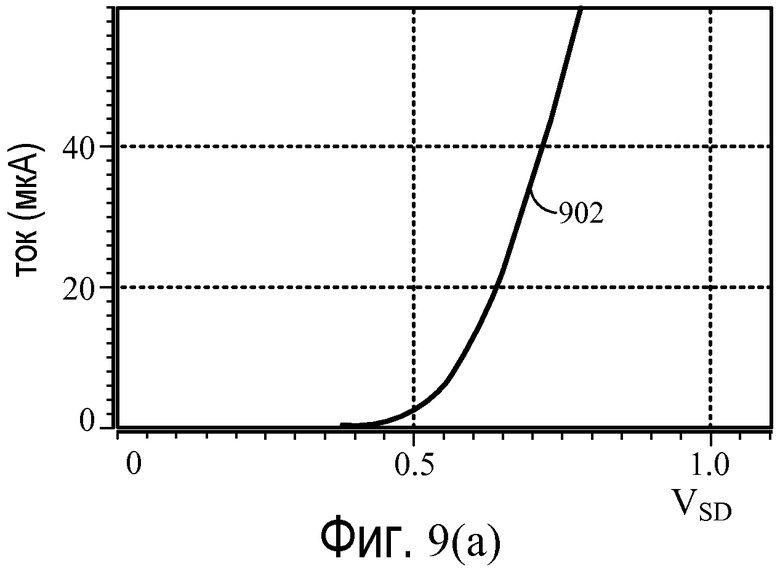

Фиг.9 включает в себя диаграммы конкретного иллюстративного варианта осуществления вольтамперных характеристик участка устройства нагрузки схемы, соединенной с опорной ячейкой устройства памяти на основе сопротивления;

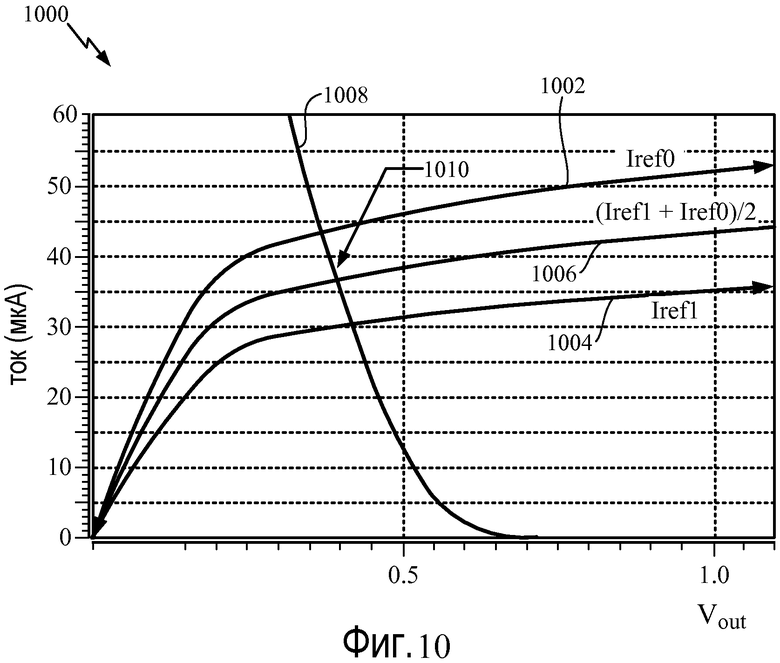

Фиг.10 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления характеристики линии нагрузки опорной схемы, изображенной на Фиг.1;

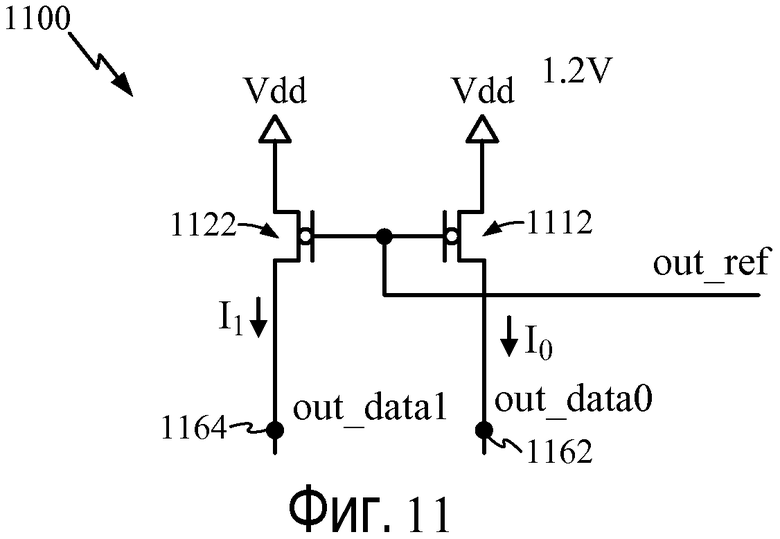

Фиг.11 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления участка нагрузки схемы, соединенной с ячейкой данных памяти на основе сопротивления;

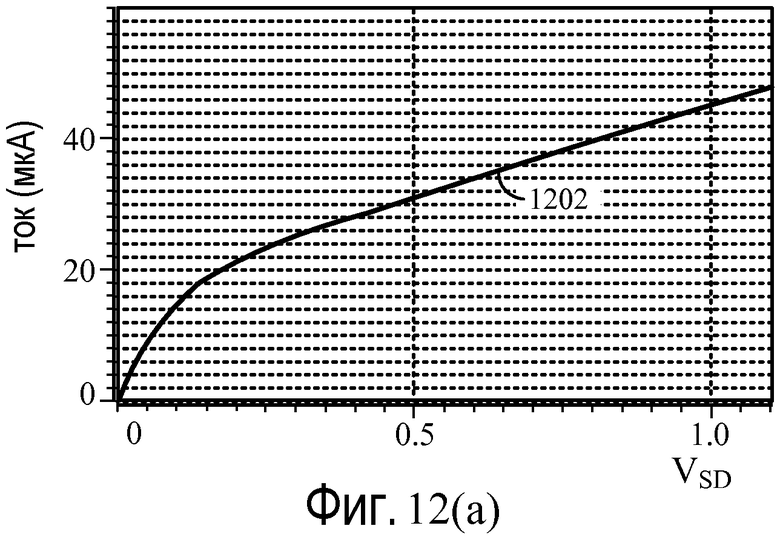

Фиг.12 включает в себя диаграммы конкретного иллюстративного варианта осуществления вольтамперных характеристик участка устройства нагрузки схемы, соединенной с ячейкой данных устройства памяти на основе сопротивления;

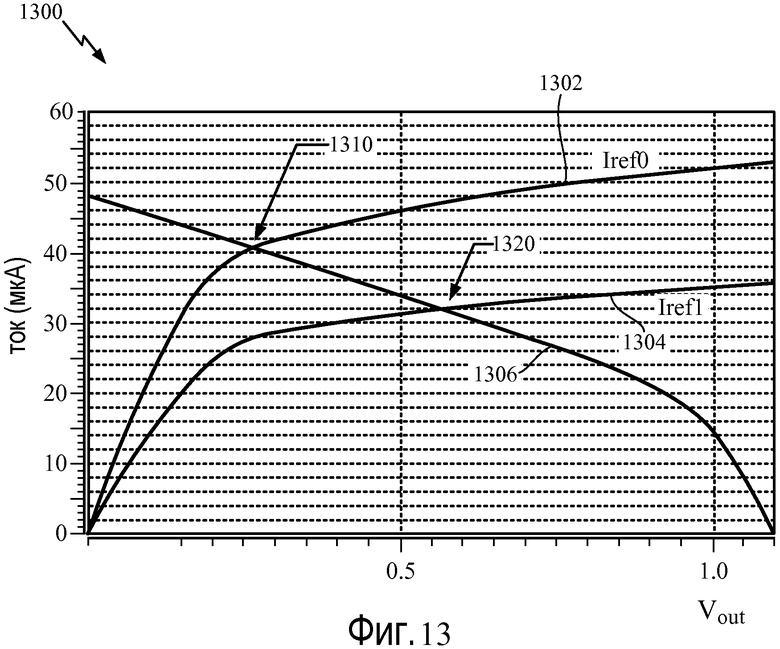

Фиг.13 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления характеристик прямых нагрузки трактов прохождения данных, изображенных на Фиг.1;

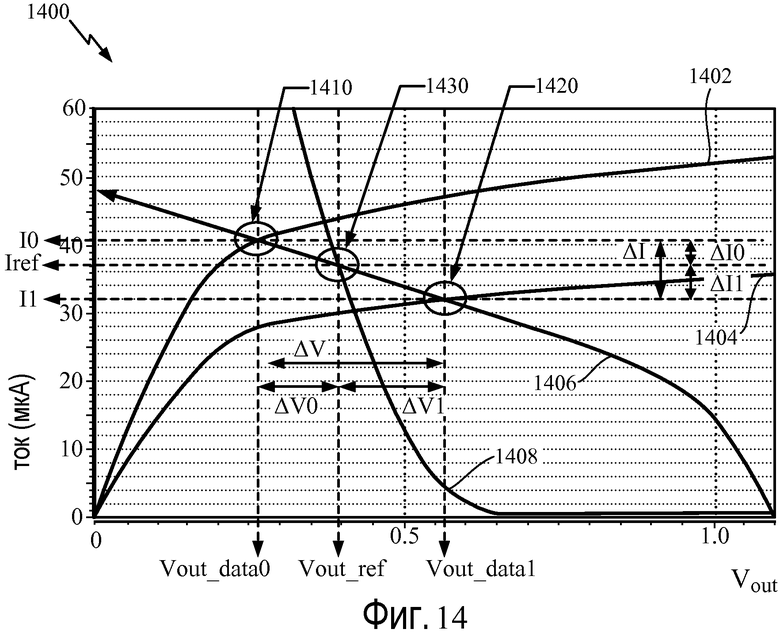

Фиг.14 представляет собой иллюстрацию, графически изображающую конкретный иллюстративный вариант осуществления значений рабочих параметров, связанных с характеристиками прямых нагрузки, изображенными на Фиг.10 и Фиг.13;

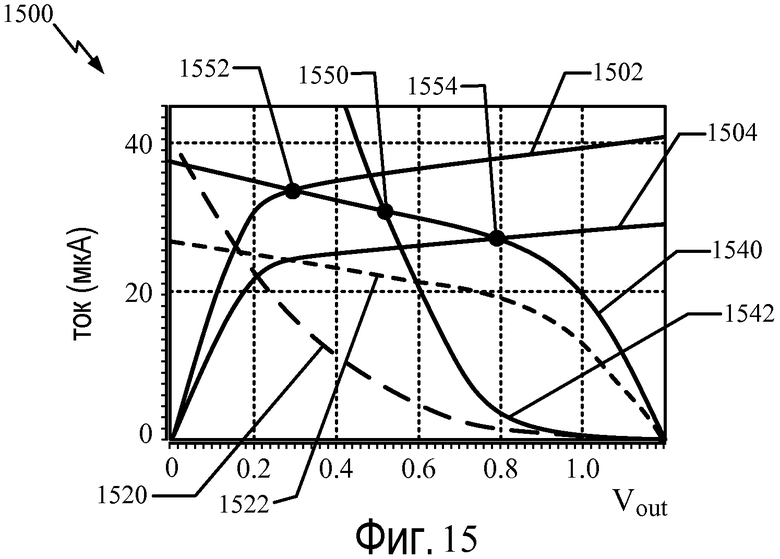

Фиг.15 представляет собой иллюстрацию первого конкретного иллюстративного варианта осуществления характеристик памяти, изображенной на Фиг.1;

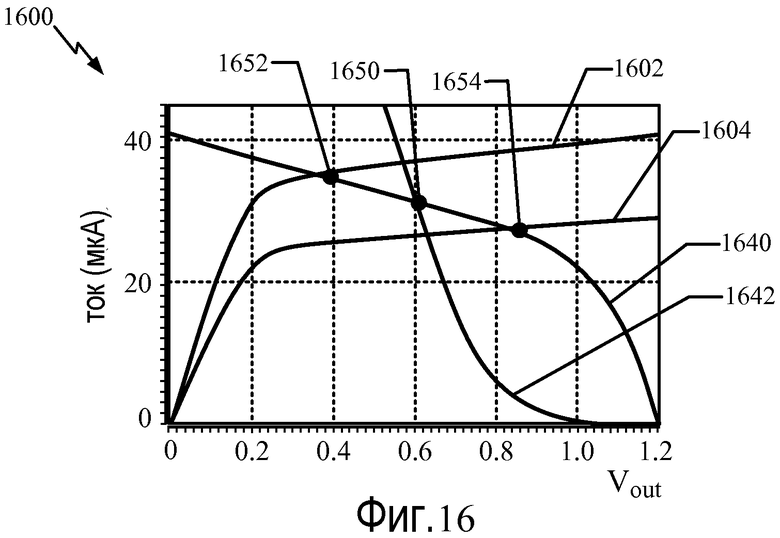

Фиг.16 представляет собой иллюстрацию второго конкретного иллюстративного варианта осуществления характеристик памяти, изображенной на Фиг.1;

Фиг.17 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления характеристик устройства памяти на основе сопротивления, имеющего ток, превышающий пороговое значение;

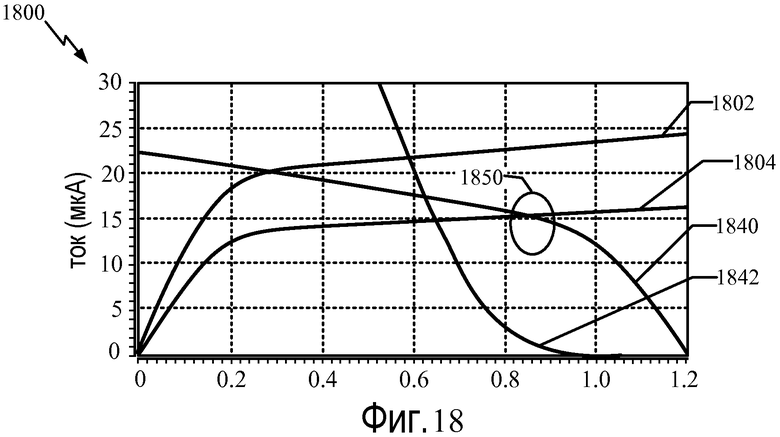

Фиг.18 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления устройства памяти на основе сопротивления по Фиг.17 с уменьшенным напряжением затвора фиксирующего устройства;

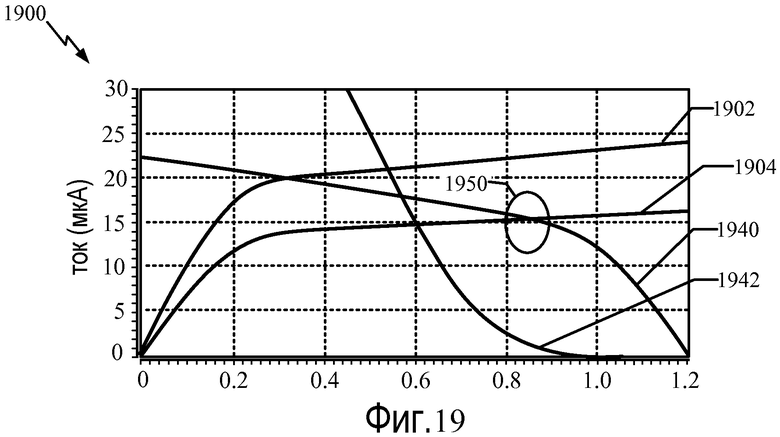

Фиг.19 представляет собой иллюстрацию конкретного иллюстративного варианта осуществления устройства памяти на основе сопротивления по Фиг.17 с уменьшенным размером фиксирующего устройства;

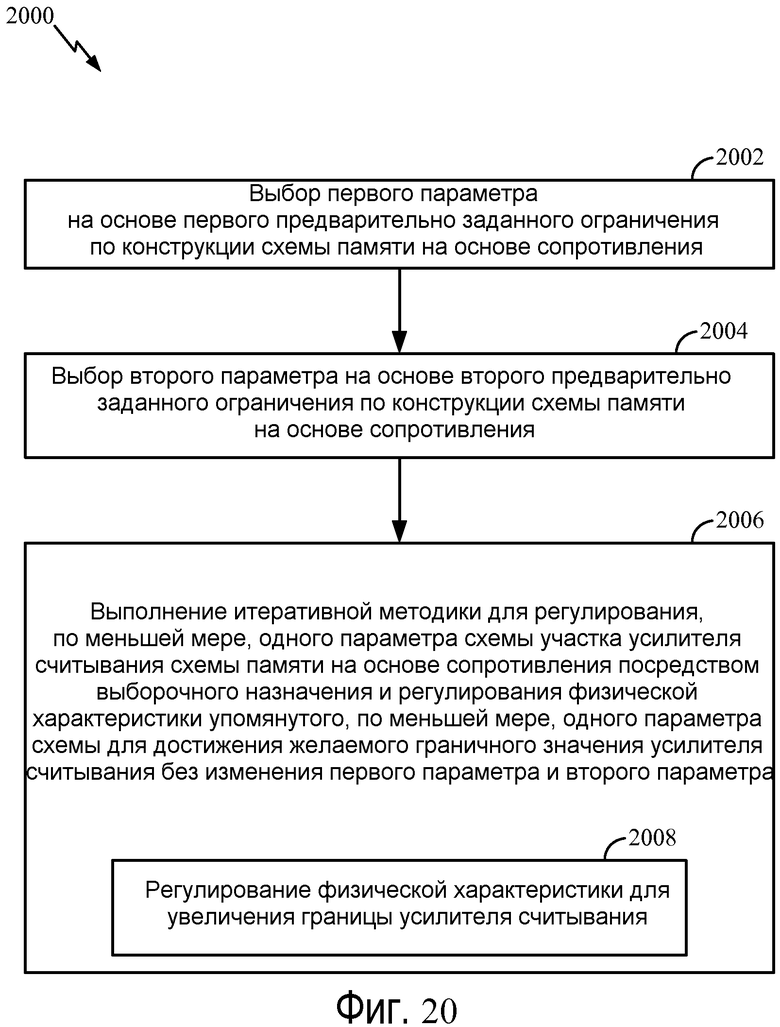

Фиг.20 представляет собой блок-схему последовательности операций первого конкретного варианта осуществления способа определения набора параметров схемы памяти на основе сопротивления;

Фиг.21 представляет собой блок-схему последовательности операций второго конкретного варианта осуществления способа определения набора параметров схемы памяти на основе сопротивления; и

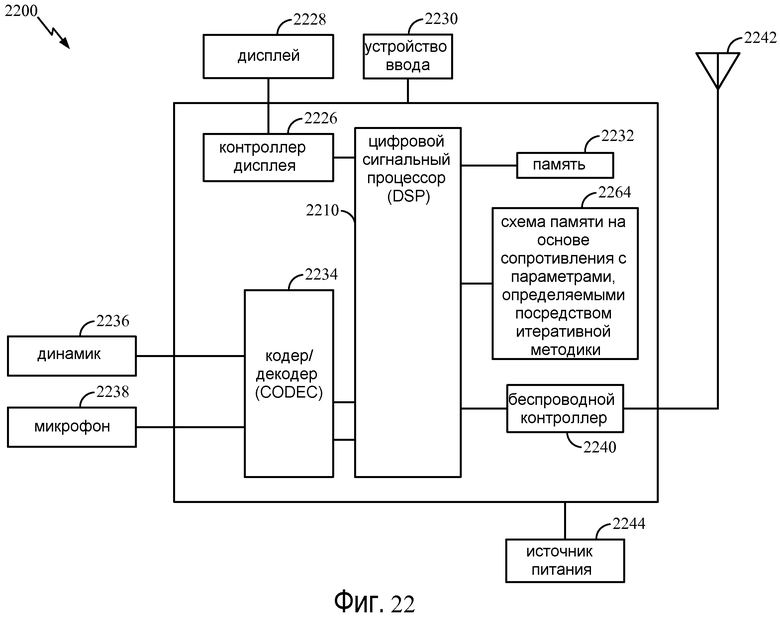

Фиг.22 представляет собой структурную иллюстрацию конкретного иллюстративного варианта осуществления электронного устройства, включающего схему памяти на основе сопротивления, имеющую параметры, определенные посредством итеративной методики.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

На Фиг.1 изображен и в общем обозначен ссылочной позицией 100 конкретный иллюстративный вариант осуществления памяти на основе сопротивления. Данная память 100 включает в себя опорную схему 102, имеющую первый опорный тракт 110 и второй опорный тракт 120. Память 100 также включает в себя репрезентативный тракт 130 прохождения данных с нулевым значением бита и репрезентативный тракт 140 прохождения данных с единичным значением бита. Опорные тракты 110 и 120 и тракты 130 и 140 прохождения данных в общем определяются как имеющие участок 104 усилителя считывания, обеспечивающий элементы нагрузки на участок 106 ячейки памяти для генерирования выходного сигнала для сравнения на втором усилителе считывания (не показан). В конкретном варианте осуществления память 100 представляет собой магниторезистивную оперативную память (MRAM), оперативную память на основе фазового перехода (PRAM) или память MRAM с переносом спинового момента (STT-MRAM).

Первый опорный тракт 110 включает в себя устройство нагрузки, такое как нагрузка 112 p-канального полевого транзистора типа металл-оксид-полупроводник (PMOS). Нагрузка 112 PMOS является соединенной с опорным узлом 160 (out_ref), который в свою очередь является соединенным с фиксирующим транзистором 114. Сопротивление R0 116, соответствующее состоянию логического нуля элемента памяти на основе сопротивления, является соединенным с фиксирующим транзистором 114. Элемент памяти на основе сопротивления представляет собой устройство, имеющее первое сопротивление, соответствующее значению логической единицы, и второе сопротивление, соответствующее значению логического нуля, такое как устройство магнитного туннельного перехода (MTJ) или ячейка памяти PRAM в качестве иллюстративных, не ограничивающих примеров. Транзистор 118 доступа является соединенным с сопротивлением R0 116.

Второй опорный тракт 120 включает в себя устройство нагрузки, такое как нагрузка 122 PMOS. Нагрузка 122 PMOS является соединенной с опорным узлом 160 (out_ref), который в свою очередь является соединенным с фиксирующим транзистором 124. Сопротивление R1 126, соответствующее состоянию логической единицы элемента памяти на основе сопротивления, является соединенным с фиксирующим транзистором 124. Транзистор 128 доступа является соединенным с сопротивлением R1 126.

Репрезентативный тракт 130 прохождения данных с нулевым значением бита включает в себя устройство нагрузки, такое как нагрузка 132 PMOS. Нагрузка 132 PMOS является соединенной с опорным узлом 162 (out_data0), который в свою очередь является соединенным с фиксирующим транзистором 134. Элемент памяти на основе сопротивления, имеющий состояние логической единицы, представлен в качестве сопротивления R0 136, соединенного с фиксирующим транзистором 134. Транзистор 138 доступа является соединенным с сопротивлением R0 136.

Репрезентативный тракт 140 прохождения данных с единичным значением бита включает в себя устройство нагрузки, такое как нагрузка 142 PMOS. Нагрузка 142 PMOS является соединенной с опорным узлом 164 (out_data1), который в свою очередь является соединенным с фиксирующим транзистором 144. Элемент памяти на основе сопротивления, имеющий состояние логического нуля, представлен в качестве сопротивления R1 146, соединенного с фиксирующим транзистором 144. Транзистор 148 доступа является соединенным с сопротивлением R1 146.

В общем, соответствующие компоненты каждого из трактов 110, 120, 130, 140 могут иметь схожие конфигурации и могут работать по существу схожим способом. Каждый из фиксирующих транзисторов 114, 124, 134 и 144 функционирует для ограничения тока и напряжения через соответствующие тракты 110, 120, 130 и 140 на основе сигнала Vclamp 144. Vclamp 144 представляет общее напряжение затвора, обеспечивающее фиксирующим транзисторам 114, 124, 134 и 144 возможность функционирования в качестве фиксирующих транзисторов. Каждый из транзисторов 118, 128, 138 и 148 доступа выборочно допускает протекание тока через соответствующие тракты 110, 120, 130 и 140 на основе общего сигнала VWL, представляющего общее напряжение затвора для транзисторов доступа 118, 128, 138 и 148. Каждое из устройств 112, 122, 132 и 142 нагрузки PMOS имеет терминал затвора, соединенный с узлом out_ref 160.

В конкретном варианте осуществления граница сигнала ∆V, такая как граница усилителя считывания, соответствует разности между напряжением на узле out_data1 164 и напряжением на узле out_ref 160 (∆V1) или разности между напряжением на узле out_ref 160 и напряжением на узле out_data0 162 (∆V0) в зависимости от того, какая из них меньше. Данная граница сигнала может быть улучшена посредством увеличения разности между напряжением на узле out_data1 164 и напряжением на узле out_data0 162. Итеративный способ для определения значения для Vclamp и ширины нагрузок 112, 122, 132 и 142 PMOS на основе одного или более ограничения по конструкции может обеспечивать конструктору памяти 100 возможность регулирования параметров схемы способом, удовлетворяющим ограничениям по конструкции, одновременно обеспечивая для границы сигнала ∆V возможность достижения физически максимального значения с учетом данных ограничений по конструкции.

На Фиг.2 изображена и в общем обозначена ссылочной позицией 200 структурная диаграмма конкретного иллюстративного варианта осуществления системы для определения параметров схемы памяти на основе сопротивления. В конкретном варианте осуществления данная система 200 может быть сконфигурирована с возможностью выполнения итеративного способа 170, изображенного на Фиг.1. Система 200 включает в себя устройство 202, имеющее, по меньшей мере, один процессор 204 и память 206, доступную для процессора 204. Память 206 включает в себя среду, считываемую посредством процессора 204 и сохраняющую данные и программные инструкции, выполняемые посредством процессора 204, включая инструкции 208 автоматизированных средств проектирования, инструкции 210 итерации параметров, инструкции 212 моделирования схемы, а также файл 218 данных, включающий значения 214 параметров и раскладку 216 схемы. Устройство 230 ввода и дисплей 240 являются соединенными с устройством 202. В конкретном варианте осуществления данное устройство 230 ввода может включать клавиатуру, указательное устройство, сенсорный экран, речевой интерфейс, некоторое другое устройство для приема ввода пользователя или любую их комбинацию.

В конкретном варианте осуществления инструкции 208 автоматизированных средств проектирования являются выполняемыми посредством процессора 204 для обеспечения для пользователя возможности конструирования схемы через устройство 230 и дисплей 240 и хранения данных, связанных с элементами и соединениями схемы, в виде топологии 216 схемы. Один или более параметров устройства или схемы, связанный со схемой, могут быть сохранены в виде значений 214 параметров. Инструкции 212 моделирования схемы могут выполняться посредством процессора 204 для считывания данных из файла 218 данных и выполнения одного или более моделирований для моделирования поведения схемы. Инструкции 210 итерации параметров могут выполняться посредством процессора 204 для предписания выполнения процессором 204 итеративных регулирований параметров одной или более схем, таких как схема памяти 100, изображенная на Фиг.1, совместно с инструкциями 212 моделирования схемы.

В иллюстративном варианте осуществления инструкции 210 итерации параметров являются выполняемыми посредством процессора 204 для приема первого ввода первого параметра на основе первого предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Инструкции 210 итерации параметров являются выполняемыми посредством процессора 204 для приема второго ввода второго параметра на основе второго предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Например, первый и второй параметры могут включать параметр процесса обработки, такой как значение сопротивления, связанного с одним или более элементов 116, 126, 136 и 146 памяти, или параметр устройства, такой как ширина фиксирующих транзисторов 114, 124, 134 и 144, ширина транзисторов 118, 128, 138 и 148 доступа, напряжение затвора Vclamp, прилагаемое к фиксирующим транзисторам 114, 124, 134 и 144, и ширина нагрузок 112, 122, 132 и 142 PMOS, изображенных на Фиг.1. Иллюстративные примеры предварительно заданных ограничений по конструкции включают логическое нулевое значение сопротивления устройства магнитного туннельного перехода (MTJ) для максимизации границы сигнала по существу, ограничение тока считывания устройства MTJ в нулевом состоянии бита для препятствования разрушению записи током считывания, при котором операция считывания записывает значение на устройство MTJ, максимальное напряжение битовой шины VBL на участке ячейки памяти, такое как на узле BL_data1 по Фиг.1, для поддержания приемлемого отношения магнитных сопротивлений (MR) устройства MTJ, и максимальный размер транзистора участка усилителя считывания, удовлетворяющего схеме мультиплексора битовая шина-ввод/вывод.

Инструкции 210 итерации параметров могут также выполняться посредством процессора 204 для выполнения итеративной методики для регулирования, по меньшей мере, одного параметра схемы участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра или второго параметра. Например, данная итеративная методика может начинаться с определения начального значения напряжения затвора фиксирующего транзистора участка усилителя считывания, такого как Vclamp по Фиг.1, и начального значения ширины транзистора нагрузки участка усилителя считывания, такой как ширина нагрузок 112, 122, 132 и 142 PMOS по Фиг.1, которые вместе приводят в результате к по существу максимальному граничному значению усилителя считывания с учетом первого параметра и второго параметра. Ток участка усилителя считывания может быть определен посредством использования начального значения напряжения затвора и начального значения ширины транзистора нагрузки, и данный ток участка усилителя считывания может быть сравнен с предварительно заданным пороговым значением тока. Напряжение битовой шины VBL на участке ячейки памяти может также быть определено и сравнено с предварительно заданным пороговым значением напряжения битовой шины (VBLmax).

Физическая характеристика, такая как напряжение затвора или ширина транзистора нагрузки, может быть выборочно отрегулирована, когда ток превышает предварительно заданное пороговое значение тока или напряжение битовой шины превышает предварительно заданное пороговое значение напряжения, посредством определения уменьшенного напряжения затвора и определения второй ширины транзистора нагрузки, что приведет в результате к по существу максимальному граничному значению усилителя считывания с учетом первого параметра, второго параметра и уменьшенного напряжения затвора. Скорректированный ток участка усилителя считывания также может быть определен посредством использования уменьшенного напряжения затвора и второй ширины транзистора нагрузки. Данный процесс обработки может быть повторен посредством уменьшения напряжения затвора и повторного определения ширины транзистора нагрузки до тех пор, пока ток, проходящий через схему, не превысит пороговое значение и напряжение битовой шины не превысит предварительно заданное пороговое значение напряжения битовой шины.

Инструкции 210 итерации параметров могут также выполняться посредством процессора 204 для сохранения значения, связанного с физической характеристикой, после того, как достигнуто желаемое граничное значение усилителя считывания с учетом предварительно заданных первого и второго ограничений по конструкции. Например, одно или более значений, связанных с физической характеристикой, такой как ширина нагрузок 112, 122, 132 и 142 PMOS, напряжение, прилагаемое к фиксирующим транзисторам 114, 124, 134 и 144, другие значения, связанные с физическими характеристиками элементов схемы, или любая их комбинация, могут быть сохранены вместе со значениями 214 параметров. В качестве одного другого примера может быть выведен файл 218 данных для представления конструкции схемы для схемы памяти на основе сопротивления, имеющей желаемую границу усилителя считывания.

Несмотря на то что изображены в качестве отдельных компонентов, инструкции 208 автоматизированных средств проектирования, инструкции 210 итерации параметров, инструкции 212 моделирования схемы или любая их комбинация могут быть встроены в один пакет программного обеспечения или в программные приложения, совместимые с возможностью взаимодействия друг с другом. В качестве иллюстративного, не ограничивающего примера инструкции 208 автоматизированных средств проектирования и инструкции 212 моделирования схемы могут представлять собой участки коммерческого средства автоматизированного проектирования (CAD), а инструкции 210 итерации параметров могут быть выполнены в качестве сценариев или других инструкций, совместимых с возможностью использования вместе с коммерческим средством CAD.

На Фиг.3 изображена и в общем обозначена ссылочной позицией 300 диаграмма конкретного иллюстративного варианта осуществления вольтамперных характеристик фиксирующего устройства памяти на основе сопротивления. Данное фиксирующее устройство может представлять собой фиксирующий транзистор, такой как фиксирующие транзисторы 134 или 144, изображенные на Фиг.1. Первая кривая 302 представляет ток, проходящий через фиксирующий транзистор, когда элемент памяти на основе сопротивления находится в состоянии логического нуля, такой как ток, проходящий через R0 136 R0 116, а вторая кривая 304 представляет ток, проходящий через фиксирующий транзистор, когда элемент памяти на основе сопротивления находится в состоянии логической единицы, такой как ток, проходящий через R1 146 R1 126.

В конкретном варианте осуществления элемент памяти на основе сопротивления состоит из сопротивления и транзистора доступа. Данный транзистор доступа может быть моделирован в виде сопротивления, Ron_accessTR, если транзистор доступа действует в линейной области. Таким образом, характеристика транзистора доступа может быть скомбинирована с характеристикой сопротивления. Например, касательно Фиг.4, изображена и в общем обозначена ссылочной позицией 400 диаграмма конкретного иллюстративного варианта осуществления вольтамперных характеристик комбинированного сопротивления и транзистора доступа. Первая прямая 402 представляет ток, проходящий через элемент памяти на основе сопротивления в состоянии логического нуля, а вторая прямая 404 представляет ток, проходящий через элемент памяти на основе сопротивления в состоянии логической единицы.

На Фиг.5 изображена и в общем обозначена ссылочной позицией 500 диаграмма конкретного иллюстративного варианта осуществления вольтамперных характеристик фиксирующего устройства, изображенного на Фиг.3, последовательно соединенного с элементом памяти на основе сопротивления, имеющего характеристики, изображенные на Фиг.4. Первая кривая 502 представляет ток, такой как I0 или Iref0 по Фиг.1, проходящий через фиксирующий транзистор и элемент памяти на основе сопротивления в состоянии логического нуля, без нагрузки 132 PMOS или нагрузки 112 PMOS по Фиг.1. Вторая кривая 504 представляет ток, такой как I1 или Iref1 по Фиг.1, проходящий через фиксирующий транзистор и элемент памяти на основе сопротивления в состоянии логической единицы, без нагрузки 142 PMOS или нагрузки 122 PMOS по Фиг.1. Обе первая кривая 502 и вторая кривая 504 демонстрируют крутую линейную область при низких напряжениях и относительно плоскую область насыщения при более высоких напряжениях.

В общем, в системе, демонстрирующей поведение, изображенное на Фиг.5, такой как память 100 по Фиг.1, граница сигнала ∆V может быть увеличена посредством (1) уменьшения наклона первой и второй кривых 502 и 504 в области насыщения, (2) увеличения разности между током, представленным посредством первой кривой 502, и током, представленным посредством второй кривой 504, в области насыщения, и (3) увеличения размера области насыщения первой и второй кривых 502 и 504.

Наклон первой и второй кривых 502 и 504 в области насыщения может быть уменьшен посредством уменьшения напряжения затвор-исток (VGSclamp) фиксирующего транзистора, поскольку наклон  . Используя фиксирующий транзистор 144 по Фиг.1 в качестве иллюстративного примера,

. Используя фиксирующий транзистор 144 по Фиг.1 в качестве иллюстративного примера,

где VBL представляет собой напряжение на узле BL_data1, соединенном с терминалом истока фиксирующего транзистора 144 и с сопротивлением R1 146, I представляет собой ток, проходящий через сопротивление R1 146, RMTJ представляет собой сопротивление R1 146, где устройство памяти на основе сопротивления представляет собой устройство магнитного туннельного перехода (MTJ), и Ron_accessTR представляет собой сопротивление транзистора доступа 148. VGSclamp уменьшается с повышением RMTJ.

Наклон первой и второй кривых 502 и 504 в области насыщения может также быть уменьшен посредством уменьшения размера (W) и напряжения затвора (VG) фиксирующего транзистора для увеличения выходного сопротивления  .

.

Разность между током, представленным посредством первой кривой 502, и током, представленным посредством второй кривой 504, в области насыщения (∆I) может быть увеличена посредством регулирования значения элемента памяти (например, RMTJ) в сторону приближения к оптимальному значению Ropt. Разность между током, представленным посредством первой кривой 502, и током, представленным посредством второй кривой 504, в области насыщения может быть увеличена посредством увеличения размера (W) и напряжения затвора (VG) фиксирующего транзистора.

Область насыщения первой кривой 502 и второй кривой 504 может быть увеличена посредством уменьшения напряжения затвора (VG) фиксирующего транзистора и увеличения размера (W) фиксирующего транзистора для сохранения тока (I) неизменным:

где VG представляет собой напряжение затвора фиксирующего транзистора, Vt представляет собой пороговое напряжение фиксирующего транзистора, а VD представляет собой напряжение стока фиксирующего транзистора.

Таким образом, граница сигнала ∆V может регулироваться посредством изменения RMTJ, а также ширины W и напряжения затвора VG фиксирующего транзистора. По мере того как RMTJ увеличивается, граница сигнала ∆V также увеличивается. Однако в ситуации, когда RMTJ увеличивается сверх определенного значения Ropt, выходное сопротивление фиксирующего транзистора и транзистора нагрузки (такого, как нагрузка 142 PMOS по Фиг.1) увеличивается, но разность тока области насыщения ∆I уменьшается. Таким образом, граница сигнала ∆V увеличивается с RMTJ, но является насыщенной для большого RMTJ.

Размер и напряжение затвора для фиксирующего транзистора также влияют на границу сигнала ∆V: малый размер и низкое напряжение приводит в результате к большому выходному импедансу, уменьшая наклон в области насыщения; большой размер и высокое напряжение увеличивает разность тока области насыщения ∆I; а большой размер и низкое напряжение приводит в результате к большой области насыщения.

Фиг.6 и 7 иллюстрируют влияния ширины фиксирующего транзистора и напряжения затвора фиксирующего транзистора на границу сигнала ∆V. На Фиг.6 изображена и в общем обозначена ссылочной позицией 600 диаграмма конкретного иллюстративного варианта осуществления характеристик памяти на основе сопротивления с переменным напряжением затвора VG фиксирующего устройства. Первая кривая 602 представляет размер фиксирующего устройства для максимизации разности напряжений ∆V0 между эталоном и состоянием логического нуля элемента памяти на основе сопротивления. Данный размер фиксирующего устройства проиллюстрирован на левой оси в виде ширины фиксирующего транзистора NMOS, такого как фиксирующий транзистор 144 по Фиг.1. Вторая кривая 604 представляет разность напряжений ∆V0. Данная разность напряжений ∆V0 проиллюстрирована на правой оси в виде разности напряжений между узлом 162 out_data0 и узлом 160 out_ref по Фиг.1.

Фиг.6 изображает для каждого заданного значения напряжения затвора VG максимальную моделированную разность напряжений ∆V0, достигнутую посредством изменения размера фиксатора, и конкретный размер фиксатора, приведший в результате к максимальной моделированной ∆V0. Значения максимальной моделированной разности напряжений ∆V0 в области значений напряжения затвора VG интерполируются в виде второй кривой 604, а значения размера фиксатора, приведшие в результате к максимальной моделированной ∆V0, интерполируются в виде первой кривой 602.

Аналогичным образом Фиг.7 изображает иллюстрацию 700 конкретного иллюстративного варианта осуществления характеристик памяти на основе сопротивления с изменяющимся размером фиксирующего устройства. Первая кривая 702 представляет напряжение затвора VG фиксирующего устройства для максимизации разности напряжений ∆V0 между эталоном и состоянием логического нуля элемента памяти на основе сопротивления. Данное напряжение затвора VG фиксирующего устройства проиллюстрировано на левой оси в виде напряжения затвора фиксирующего транзистора NMOS, такого как фиксирующий транзистор 144 по Фиг.1. Вторая кривая 704 представляет разность напряжений ∆V0. Данная разность напряжений ∆V0 проиллюстрирована на правой оси в виде разности напряжений между узлом 160 out_ref и узлом 162 out_data0 по Фиг.1.

Фиг.7 изображает для каждого заданного значения ширины фиксирующего транзистора максимальную моделированную ∆V0, достигнутую посредством изменения напряжения затвора фиксатора VG, и напряжение затвора, приведшее в результате к максимальной моделированной ∆V0. Значения максимальной моделированной разности напряжений ∆V0 в области значений напряжения затвора VG интерполируются в виде второй кривой 704, а значения напряжения затвора VG фиксирующего транзистора, приведшие в результате к максимальной моделированной ∆V0, интерполируются в виде первой кривой 702. В целях сравнения моделированные данные, представленные на Фиг.6, были сгенерированы с использованием тех же параметров схемы, что и моделированные данные, представленные на Фиг.7, кроме изменений, отмеченных выше.

Сравнение значений первой кривой 602 по Фиг.6 (размер фиксатора, производящий максимальную ∆V0) с соответствующими размерами фиксатора на Фиг.7 иллюстрирует, что для конкретного размера фиксатора максимальная моделированная ∆V0 на Фиг.6 может быть приблизительно равной максимальной моделированной ∆V0 на Фиг.7. Например, размер фиксатора 2,6 мкм соответствует ∆V0 0,133 на Фиг.6 (при VG=0,88 В), в то время как размер фиксатора 2,6 мкм соответствует ∆V0 приблизительно 0,135 на Фиг.7. Аналогичным образом размер фиксатора 3,7 мкм соответствует ∆V0 0,138 на Фиг.6 (при VG=0,86 В), в то время как размер фиксатора 3,7 мкм соответствует ∆V0 приблизительно 0,139 на Фиг.7 и размер фиксатора в 5,4 мкм соответствует ∆V0 в 0,142 на Фиг.6 (при VG=0,84 В), в то время как размер фиксатора 5,4 мкм соответствует ∆V0 приблизительно 0,144 на Фиг.7.

Поскольку оба способа регулирования параметров для достижения по существу максимальной разности напряжений сигнала ∆V0, изображенной на Фиг.6 и 7, могут обеспечивать схожие результаты, предпочтение в регулировании параметров может быть определено на основе дополнительных критериев. Например, ограничение по размеру фиксатора может в общем быть более жестким, чем ограничение по напряжению затвора фиксатора VG. В дополнение управление напряжением затвора фиксатора VG может достигать более высокой границы сигнала в течение регулирования параметров в ситуации, когда ток состояния логической единицы превышает пороговое значение тока. Таким образом, определение напряжения затвора фиксатора VG для максимизации границы сигнала ∆V по существу с фиксированным размером фиксатора является в общем предпочтительным.

Касательно Фиг.8, изображена и в общем обозначена ссылочной позицией 800 диаграмма конкретного иллюстративного варианта осуществления участка нагрузки схемы, соединенной с опорной ячейкой устройства памяти на основе сопротивления. Данный участок нагрузки включает в себя первый транзистор 812 PMOS, имеющий первый терминал, соединенный с источником питания Vdd, и второй терминал, соединенный с опорным узлом 860 (out_ref). Второй транзистор 822 PMOS имеет первый терминал, соединенный с источником питания Vdd, и второй терминал, соединенный с узлом 860 out_ref. Терминал затвора каждого из первого транзистора 812 PMOS и второго транзистора 822 PMOS соединен с опорным выходным узлом 860 (out_ref). В иллюстративном варианте осуществления транзисторы 812 и 822 PMOS и узел 860 out_ref могут соответствовать устройствам нагрузки 112 и 122 PMOS и узлу 160 out_ref, соответственно изображенным на Фиг.1. Работа участка 800 нагрузки проиллюстрирована в диаграммах линий нагрузки по Фиг.9-10.

На Фиг.9 изображены диаграммы конкретного иллюстративного варианта осуществления вольтамперных характеристик участка устройства нагрузки схемы, соединенной с опорной ячейкой устройства памяти на основе сопротивления. Фиг.9(а) включает в себя кривую 902, изображающую диодоподобное поведение тока I_top, проходящего через транзисторы 812 и 822 PMOS по Фиг.8 в качестве функции напряжения исток-к-стоку, VSD=Vdd-Vout, где Vout представляет собой напряжение узла 860 out_ref. Фиг.9(b) изображает кривую 904, соответствующую току, проходящему через транзисторы 812 и 822 PMOS по Фиг.8 в качестве функции Vout=Vdd - VSD. В конкретном варианте осуществления I_top соответствует Iref по Фиг.1.

На Фиг.10 диаграмма конкретного иллюстративного варианта осуществления характеристики линии нагрузки опорной схемы по Фиг.1 графически иллюстрирует рабочую точку опорной схемы 102. Первая кривая 1002 иллюстрирует первый опорный ток Iref0, проходящий через опорный тракт 110 в состоянии логического нуля, включающий транзистор 118 доступа, элемент 116 памяти и фиксирующий транзистор 114, согласно Фиг.1, без нагрузки 112 PMOS. Вторая кривая 1004 иллюстрирует второй опорный ток Iref1, проходящий через опорный тракт 120 в состоянии логической единицы, включающий транзистор 128 доступа, элемент 126 памяти и фиксирующий транзистор 124, согласно Фиг.1, без нагрузки 122 PMOS. В конкретном варианте осуществления первая кривая 1002 и вторая кривая 1004 соответствуют кривым 502 и 504 по Фиг.5 соответственно. Третья кривая 1006 иллюстрирует среднее арифметическое Iref0 и Iref1, заданное как (Iref0+Iref1)/2. Четвертая кривая 1008 соответствует кривой 904 по Фиг.9(b) и иллюстрирует ток Iref, проходящий через нагрузку 122 PMOS и нагрузку 112 PMOS в качестве функции напряжения на узле 160 out_ref (Vout).

Применяя закон токов Кирхгофа на узле 160 out_ref по Фиг.1, сумма тока Iref, проходящего через нагрузку 112 PMOS, и тока Iref, проходящего через нагрузку 122 PMOS, равна сумме первого опорного тока Iref0 и второго опорного тока Iref1, так что Iref=1/2(Iref1+Iref2). Таким образом, пересечение 1010 третьей кривой 1006 и четвертой кривой 1008 обозначает рабочую точку опорной схемы 102 по Фиг.1.

На Фиг.11 изображена и в общем обозначена ссылочной позицией 1100 диаграмма конкретного иллюстративного варианта осуществления участка нагрузки схемы, соединенной с ячейкой данных памяти на основе сопротивления. Данный участок нагрузки включает в себя первый транзистор 1112 PMOS, имеющий первый терминал, соединенный с источником питания Vdd, и второй терминал, соединенный с узлом 1162 вывода данных (out_data0). Второй транзистор 1122 PMOS имеет первый терминал, соединенный с источником питания Vdd, и второй терминал, соединенный с узлом 1164 вывода данных (out_data0). Терминал затвора каждого из первого транзистора 1112 PMOS и второго транзистора 1122 PMOS соединен с опорным выходным узлом (out_ref). В иллюстративном варианте осуществления транзисторы 1112 и 1122 PMOS могут соответствовать устройствам нагрузки 132 и 142 PMOS тракта 130 прохождения данных с нулевым значением бита и тракта 140 прохождения данных с единичным значением бита по Фиг.1 соответственно, а узел 1162 out_data0 и узел 1164 out_data1 соответствуют узлам 162 и 164 по Фиг.1 соответственно. Работа участка 1100 нагрузки проиллюстрирована в диаграммах линий нагрузки по Фиг.12-14.

На Фиг.12 изображены и в общем обозначены ссылочной позицией 1200 диаграммы конкретного иллюстративного варианта осуществления вольтамперных характеристик участка устройства нагрузки схемы, соединенной с ячейкой данных устройства памяти на основе сопротивления. Фиг.12(а) включает в себя кривую 1202, изображающую вольтамперную характеристику транзистора 1112 PMOS или транзистора 1122 PMOS по Фиг.8 в качестве функции напряжения исток-к-стоку, VSD=Vdd-Vout, где Vout представляет собой напряжение на узле 1162 out_data0 или узле 1164 out_data1 соответственно. Фиг.12(b) изображает кривую 1204, соответствующую току, проходящему через транзистор 1112 PMOS или транзистор 1122 PMOS по Фиг.11 в качестве функции Vout=Vdd - VSD.

На Фиг.13 конкретный иллюстративный вариант осуществления графически иллюстрирует рабочие точки тракта 130 прохождения данных с нулевым значением бита и тракта 140 прохождения данных с единичным значением бита по Фиг.1. Первая кривая 1302 иллюстрирует первый ток I0, проходящий через тракт 130 прохождения данных с нулевым значением бита, включающий транзистор 138 доступа, элемент 136 памяти и фиксирующий транзистор 134, согласно Фиг.1, без нагрузки 132 PMOS. Вторая кривая 1304 иллюстрирует второй ток I1, проходящий через тракт 140 прохождения данных с единичным значением бита, включающий транзистор 148 доступа, элемент 146 памяти и фиксирующий транзистор 144 по Фиг.1, без нагрузки 142 PMOS. В конкретном варианте осуществления первая кривая 1302 и вторая кривая 1304 соответствуют кривым 502 и 504 по Фиг.5 соответственно. Третья кривая 1306 соответствует кривой 1204 по Фиг.12(b) и иллюстрирует ток, проходящий через нагрузку 132 PMOS или нагрузку 142 PMOS по Фиг.1 в качестве функции напряжения Vout на узле 162 out_data0 или узле 164 out_data1 соответственно.

Первое пересечение 1310 первой кривой 1302 и третьей кривой 1306 обозначает рабочую точку, когда в элементе памяти на основе сопротивления сохраняется значение логического нуля, такую как рабочая точка тракта 130 прохождения данных с нулевым значением бита по Фиг.1. Второе пересечение 1320 второй кривой 1304 и третьей кривой 1306 обозначает рабочую точку, когда в элементе памяти на основе сопротивления сохраняется значение логической единицы, такую как рабочая точка тракта 140 прохождения данных с единичным значением бита по Фиг.1.

Фиг.14 изображает рабочие параметры, связанные с характеристиками линий нагрузки по Фиг.10 и Фиг.13. Первая кривая 1402 иллюстрирует первый ток I0, проходящий через тракт 130 с нулевым значением бита, или ток Iref0, проходящий через первый опорный тракт 110 по Фиг.1, включающий транзистор 138 доступа или транзистор 118 доступа, элемент 136 памяти или элемент 116 памяти и фиксирующий транзистор 134 или фиксирующий транзистор 114, без нагрузки 132 PMOS или нагрузки 112 PMOS соответственно, рассматриваемый в качестве «схемы нижней стороны в состоянии логического нуля». Вторая кривая 1404 иллюстрирует второй ток I1, проходящий через тракт 140 с единичным значением бита, или ток Iref1, проходящий через второй опорный тракт 120, включающий транзистор 148 доступа или транзистор 128 доступа, элемент 146 памяти или элемент 126 памяти и фиксирующий транзистор 144 или фиксирующий транзистор 124, без нагрузки 142 PMOS или нагрузки 122 PMOS, рассматриваемый в качестве «схемы нижней стороны в состоянии логической единицы».

Третья кривая 1406 иллюстрирует ток, проходящий через нагрузку 132 PMOS или нагрузку 142 PMOS в качестве функции напряжения на узле 162 out_data0 или узле 164 out_data1 соответственно, рассматриваемую в качестве «схемы прохождения данных верхней стороны». Четвертая кривая 1408 иллюстрирует ток Iref, проходящий через нагрузку 112 PMOS или нагрузку 122 PMOS опорной схемы 102 по Фиг.1, рассматриваемую в качестве «опорной схемы верхней стороны», в качестве функции напряжения на узле 160 out_ref, и в конкретном варианте осуществления может соответствовать кривой 904 по Фиг.9(b).

Первое пересечение 1410 первой кривой 1402 и третьей кривой 1406 обозначает напряжение (Vout_data0 1414) на узле 162 out_data0 и ток (I0 1412), соответствующий рабочей точке тракта 130 с нулевым значением бита по Фиг.1. Второе пересечение 1420 второй кривой 1404 и третьей кривой 1406 обозначает напряжение (Vout_data1 1424) на узле 164 out_data1 и ток (I1 1422), соответствующий рабочей точке тракта 140 с единичным значением бита по Фиг.1. Третье пересечение 1430 третьей кривой 1406 и четвертой кривой 1408 обозначает напряжение (Vout_ref 1434) на узле 160 out_ref и ток (Iref 1432) на рабочей точке опорной схемы 102. Данная рабочая точка опорной схемы 102, обозначенная посредством третьего пересечения 1430, является эквивалентной рабочей точке, определенной посредством метода, описанного со ссылкой на Фиг.10.

Разность напряжений ∆V0 между напряжением на узле 160 out_ref (Vout_ref) и напряжением на узле 162 out_data0 (Vout_data0) обозначает нечувствительность памяти 100 к шуму или к изменению параметров процесса обработки при обнаружении значения логического нуля, сохраненного в элементе памяти на основе сопротивления. Разность напряжений ∆V1 между напряжением на узле 164 out_data1 (Vout_data1) и напряжением на узле 160 out_ref (Vout_ref) обозначает нечувствительность памяти 100 к шуму или к изменению параметров процесса обработки при обнаружении значения логической единицы, сохраненного в элементе памяти на основе сопротивления. Граница сигнала памяти 100 является равной ∆V0, как меньшей из ∆V0 и ∆V1. Аналогичным образом разности токов ∆I0 ∆I1 соответствуют разностям между Iref и I0 и между I1 и Iref соответственно.

На Фиг.15 изображена и в общем обозначена ссылочной позицией 1500 диаграмма первого конкретного иллюстративного варианта осуществления характеристик памяти 100 по Фиг.1. Первая кривая 1502 и вторая кривая 1504 иллюстрируют вольтамперные (I-V) характеристики для схемы нижней стороны с логическим нулем и схемы нижней стороны с логической единицей соответственно. Первый набор из линии 1520 нагрузки и линии 1522 нагрузки соответствует I-V характеристикам опорной схемы верхней стороны и схемы прохождения данных верхней стороны соответственно, с первой шириной транзисторов 112, 122, 132 и 142 PMOS. Второй набор из линии 1540 нагрузки и линии 1542 нагрузки соответствует I-V характеристикам опорной схемы верхней стороны и схемы прохождения данных верхней стороны соответственно, где транзисторы 112, 122, 132 и 142 PMOS имеют вторую ширину, являющуюся большей, чем первая ширина.

Первый набор из линии 1520 нагрузки и линии 1522 нагрузки демонстрирует, что транзисторы PMOS, имеющие первую ширину, ограничивают ток, так что фиксирующие устройства работают в линейной области, приводя в результате к нежелательно малой ∆V. Второй набор из линии 1540 нагрузки и линии 1542 нагрузки демонстрирует, что транзисторы PMOS, имеющие вторую ширину, пропускают достаточное количество тока для обеспечения обоим фиксирующим устройствам возможности работы в области насыщения. Пересечение 1550 линии 1540 нагрузки и линии 1542 нагрузки обозначает напряжение на узле 160 out_ref по Фиг.1. Пересечение 1552 линии 1540 нагрузки и первой кривой 1502 обозначает выходное напряжение с нулевым значением бита, а пересечение 1554 линии 1540 нагрузки и второй кривой 1504 обозначает выходное напряжение с единичным значением бита. Оба из данных пересечений 1552 и 1554 обозначают, что фиксирующие устройства работают в области насыщения, хотя пересечение 1552, соответствующее нулевому состоянию бита, находится внутри, но на границе области насыщения.

На Фиг.16 изображена и в общем обозначена ссылочной позицией 1600 диаграмма второго конкретного иллюстративного варианта осуществления характеристик памяти 100 по Фиг.1. Первая кривая 1602 и вторая кривая 1604 иллюстрируют вольтамперные (I-V) характеристики для схемы нижней стороны с логическим нулем и схемы нижней стороны с логической единицей соответственно. Линия 1640 нагрузки и линия 1642 нагрузки соответствуют I-V характеристикам опорной схемы верхней стороны и схемы прохождения данных верхней стороны соответственно. Пересечение 1650 линии 1640 нагрузки и линии 1642 нагрузки обозначает напряжение на узле 160 out_ref. Пересечение 1652 линии 1640 нагрузки и первой кривой 1602 обозначает выходное напряжение с нулевым значением бита, а пересечение 1654 линии 1640 нагрузки и второй кривой 1604 обозначает выходное напряжение с единичным значением бита. Оба из данных пересечений 1652 и 1654 обозначают, что фиксирующие устройства работают в области насыщения. Однако нагрузка PMOS имеет сниженное выходное сопротивление r0, чем напряжение, проиллюстрированное на Фиг.15, как продемонстрировано посредством наклона линии 1640 нагрузки.

Фиг.17-19 иллюстрируют конкретный иллюстративный вариант осуществления работы памяти на основе сопротивления, имеющей ток со значением логической единицы, превышающий пороговое значение тока (Фиг.17), и памяти на основе сопротивления после того, как данный ток со значением логической единицы был уменьшен посредством уменьшения напряжения затвора фиксирующего транзистора (Фиг.18) или посредством уменьшения ширины фиксирующего транзистора (Фиг.19), а также соответствующих границ сигнала, полученных в результате.

На Фиг.17 изображена и в общем обозначена ссылочной позицией 1700 диаграмма конкретного иллюстративного варианта осуществления характеристик устройства памяти на основе сопротивления, имеющего ток, превышающий пороговое значение. Первая кривая 1702 и вторая кривая 1704 иллюстрируют вольтамперные (I-V) характеристики для схемы нижней стороны с логическим нулем и схемы нижней стороны с логической единицей соответственно. Линия 1740 нагрузки и линия 1742 нагрузки соответствуют I-V характеристикам опорной схемы верхней стороны и схемы прохождения данных верхней стороны соответственно. Область 1750 в общем обозначает рабочую точку тракта 140 прохождения данных с единичным значением бита. В конкретном варианте осуществления ток, связанный с состоянием логической единицы (I1), имеет значение приблизительно в девятнадцать микроампер (мкА), превышающее пороговое значение тока в пятнадцать мкА, в качестве иллюстративного, не ограничивающего примера порогового значения тока. Данное пороговое значение тока Imax может обозначать максимальный пропускаемый ток для предотвращения неверных команд записи в течение операций считывания.

Разность напряжений ∆V0 между пересечением линии 1740 нагрузки и линии 1742 нагрузки и пересечением первой кривой 1702 и линии 1740 нагрузки представляет собой приблизительно 267 милливольт (мВ). Разность напряжений ∆V1 между пересечением первой кривой 1702 и линии 1740 нагрузки и пересечением линии 1740 нагрузки и линии 1742 нагрузки представляет собой приблизительно 298 милливольт (мВ). Граница сигнала, определенная как меньшее из ∆V0 и ∆V1, задается, таким образом, посредством ∆V0 и имеет значение в 267 мВ.

На Фиг.18 изображена и в общем обозначена ссылочной позицией 1800 диаграмма конкретного иллюстративного варианта осуществления характеристик устройства памяти на основе сопротивления по Фиг.17, имеющего уменьшенное напряжение затвора фиксирующего устройства. Начиная от варианта осуществления по Фиг.17, для уменьшения тока в единичном состоянии бита до значения, меньшего чем или равного Imax (15 мкА), сначала уменьшается напряжение затвора VG фиксирующего устройства, после чего уменьшается ширина транзисторов 112, 122, 132 и 142 PMOS для достижения по существу максимального значения ∆V0 в 262 мВ при токе с единичным битовым значением в пятнадцать мкА. Как проиллюстрировано, ∆V1 равняется 297 мВ, и граница сигнала, таким образом, задается посредством ∆V0 и имеет значение в 267 мВ.

На Фиг.19 изображена и в общем обозначена ссылочной позицией 1900 диаграмма конкретного иллюстративного варианта осуществления характеристик устройства памяти на основе сопротивления по Фиг.17 с уменьшенным размером фиксирующего устройства. Начиная от варианта осуществления по Фиг.17, для уменьшения тока в единичном состоянии бита до значения, меньшего чем или равного Imax (15 мкА), сначала уменьшается ширина фиксирующего устройства, после чего уменьшается ширина транзисторов 112, 122, 132 и 142 PMOS для достижения по существу максимального значения ∆V0 241 мВ при токе с единичным битовым значением 15 мкА. Как проиллюстрировано, значение ∆V1 равняется 274 мВ, и граница сигнала, таким образом, задается посредством ∆V0 и имеет значение в 241 мВ. Граница сигнала по Фиг.19 является меньшей и, таким образом, менее желаемой, чем граница сигнала по Фиг.18, в первую очередь потому, что большая область насыщения получается в результате от уменьшения ∆V0 для снижения I1 до Imax, чем от уменьшения размера фиксатора для снижения I1 до Imax.

Как проиллюстрировано на Фиг.3-19, параметры памяти на основе сопротивления, такой как память 100 по Фиг.1, могут выборочно регулироваться способом, предназначенным для создания наибольшей достижимой границы сигнала, задаваемой как меньшее из ∆V0 и ∆V1. Другие соображения по определению параметров устройства включают признание того, что большое сопротивление элемента памяти вызывает высокую плотность тока. В дополнение, максимальный ток считывания данных с единичным битовым значением должен быть достаточно низким для предотвращения неверной записи данных в течение операции считывания, а напряжение битовой шины не должно превышать пороговое значение напряжения битовой шины (VBLmax) для поддержания приемлемых значений отношения магнитных сопротивлений (MR).

На Фиг.20 изображена и в общем обозначена ссылочной позицией 2000 блок-схема последовательности операций первого конкретного варианта осуществления способа определения набора параметров схемы памяти на основе сопротивления. В качестве иллюстративных примеров схема памяти на основе сопротивления может включать магниторезистивную оперативную память (MRAM), оперативную память на основе фазового перехода (PRAM), память MRAM с переносом спинового момента (STT-MRAM) или другие устройства памяти на основе сопротивления.

На этапе 2002 выбирается первый параметр на основе первого предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Переходя к этапу 2004, выбирается второй параметр на основе второго предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. В конкретном варианте осуществления первое предварительно заданное ограничение по конструкции может включать параметр процесса обработки, такой как значение сопротивления, связанного с элементом памяти на основе сопротивления. Ограничения по конструкции процесса обработки могут не быть изменяемыми или могут быть трудными для удовлетворения, поскольку параметр процесса обработки может быть фиксированным или менее подвижным, чем параметры конструкции схемы. Второй параметр может включать параметр конструкции схемы, такой как максимальный размер устройства или максимальная ширина транзистора с учетом физического ограничения пространства. Например, максимальный размер транзистора участка усилителя считывания может быть ограничен с учетом схемы мультиплексора от битовой шины к вводу/выводу.

На этапе 2006 выполняется итеративная методика для регулирования, по меньшей мере, одного параметра схемы участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного назначения и регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра и второго параметра. Физические характеристики, которые могут регулироваться, включают размеры транзистора и напряжения смещения затвора в качестве иллюстративных примеров. В конкретном варианте осуществления выполнение итеративной методики включает в себя регулирование физической характеристики для увеличения границы усилителя считывания на этапе 2008. Данная желаемая граница усилителя считывания может представлять собой предварительно заданное граничное значение или может представлять собой по существу максимальную границу сигнала усилителя с учетом первого и второго предварительно заданных ограничений по конструкции.

Параметр конструкции схемы может включать ширину транзистора нагрузки, подсоединенного для работы в качестве нагрузки. Например, параметр конструкции схемы может включать ширину устройств 112, 122, 132 и 134 нагрузки, изображенных на Фиг.1. Параметр конструкции схемы может включать напряжение затвора фиксирующего транзистора внутри участка усилителя считывания схемы памяти. Например, параметр конструкции схемы может включать значение Vclamp, изображенного на Фиг.1.

Фиксирующий транзистор может работать в режиме насыщения и может ограничивать ток в тракте считывания данных элемента магнитного туннельного перехода (MTJ) схемы памяти на основе сопротивления. В конкретном варианте осуществления опорная ячейка включает в себя нагрузку p-канального полевого транзистора типа металл-оксид-полупроводник (PMOS), соединенную с фиксирующим транзистором. Элемент MTJ может быть соединен с фиксирующим транзистором и дополнительно соединен с транзистором доступа. Данная схема памяти на основе сопротивления может дополнительно включать ячейку данных, имеющую вторую нагрузку PMOS, второй фиксирующий транзистор, второй элемент MTJ и второй транзистор доступа, такую как тракты 130 и 140 прохождения данных согласно Фиг.1.

На Фиг.21 изображена и в общем обозначена ссылочной позицией 2100 диаграмма второго конкретного варианта осуществления способа определения набора параметров схемы памяти на основе сопротивления. Значение сопротивления RMTJ элемента магнитного туннельного перехода устанавливается на предварительно заданное значение RMTJ_opt на этапе 2102. В конкретном варианте осуществления RMTJ_opt представляет собой оптимальное значение R0 для максимизации границы сигнала. На этапе 2104 ширина фиксирующего транзистора Wnclamp магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM) устанавливается на значение Wnclamp_max. Wnclamp_max может представлять собой предварительно заданное ограничение по конструкции, выбранное с возможностью являться по существу наибольшей шириной, удовлетворяющей пространственному ограничению STT-MRAM. Например, данное пространственное ограничение может быть определено посредством схемы мультиплексирования от битовой шины к вводу/выводу STT-MRAM, такой как 4:1 или 8:1, которая ограничивает ширину транзистора участка усилителя считывания STT-MRAM. Граница сигнала ∆V0 может увеличиваться и насыщаться с увеличением ширины фиксирующего транзистора, такого как проиллюстрированный на Фиг.7, а ширина фиксирующего транзистора может выбираться на основе границы сигнала и ограничения области.

В дополнение на основе предварительно заданных ограничений могут выбираться или иным образом определяться другие параметры, такие как сопротивление RMTJ магнитного туннельного перехода (MTJ) памяти STT-MRAM в нулевом состоянии бита, максимальный ток считывания Imax для предотвращения изменения состояния бита «один» в состояние бита «ноль» в течение операции считывания единичного состояния бита, другие параметры конструкции процесса обработки и схемы или любая их комбинация. В конкретном варианте осуществления один или более выбранных параметров могут включать параметры процесса обработки, определенные посредством технологии процесса обработки, такой как сопротивление MTJ.

После того как параметры выбраны, начинается итеративная методика. Данная итеративная методика в общем включает в себя регулирование, по меньшей мере, одного параметра конструкции схемы участка усилителя считывания STT-MRAM посредством выборочного регулирования физической характеристики, по меньшей мере, одного параметра конструкции схемы для достижения желаемого граничного значения усилителя считывания, но без изменения ранее определенных параметров, таких как RMTJ или Wnload, испытывающих влияние со стороны ограничений по конструкции. Переходя к этапу 2106, определяются начальные значения напряжения затвора VG фиксирующего транзистора и ширина Wpload транзистора нагрузки для максимизации по существу границы сигнала ∆V STT-MRAM.

На этапе 2108 ток (I) в нулевом состоянии бита MTJ сравнивается с предварительно заданным пороговым значением тока Imax и напряжение (VBL) битовой шины сравнивается с предварительно заданным пороговым значением напряжения VBLmax. На этапе 2110 принятия решения определяется, является ли ток I в единичном состоянии бита меньшим, чем Imax, и является ли VBL меньшим, чем VBLmax. В ситуации, когда I<Imax и VBL<VBLmax, способ заканчивается на этапе 2116. В ситуации, когда I превышает Imax или VBL превышает VBLmax, процесс обработки переходит на этап 2112 для начала итеративного уменьшения напряжения затвора VG фиксирующего транзистора и определения ширины Wpload транзистора нагрузки, приводящей к по существу максимальной границе усилителя считывания с учетом напряжения затвора VG. В иллюстративном варианте осуществления, изображенном на Фиг.21, в случае, когда I является равным Imax или VBL является равным VBLmax, процесс обработки также переходит к этапу 2112, хотя в другом варианте осуществления процесс обработки может вместо этого переходить к этапу 2116, где способ заканчивается.

На этапе 2112 уменьшается напряжение затвора VG. VG может быть уменьшено на предварительно заданное количество или на вычисленный размер шага. После уменьшения VG на этапе 2114 определяется следующее значение Wpload для максимизации ∆V0 по существу. Процесс обработки возвращается к этапу 2108, на котором вычисляются I и VBL с использованием значений, определенных на этапах 2112 и 2114.

Общая зависимость ∆V0 от Wnclamp и VG, проиллюстрированная на Фиг.17-19, предполагает, что уменьшение тока I при одновременной поддержке наибольшей возможной границы сигнала, определяемой как меньшее из ∆V0 и ∆V1, может быть достигнуто посредством установки наибольшего приемлемого Wnclamp и посредством итеративного уменьшения VG, а также регулирования Wpload до тех пор, пока I не будет меньше, чем Imax. Конструкции схемы, определяемые без следования последовательностям операций проектирования, описанным со ссылкой на Фиг.1-21, могут иметь локальные оптимумы в некоторых аспектах, но могут страдать от проблем на границе сигнала и низкой результативности. По меньшей мере, часть итеративной методики, проиллюстрированной на Фиг.20-21, может быть выполнена посредством автоматизированного средства проектирования, такого как описанные со ссылкой на систему 200 по Фиг.2. Одному или более параметрам, физическим характеристикам или любой их комбинации может быть назначено начальное значение до выполнения итеративной методики на автоматизированном средстве проектирования, таком как через устройство 230 ввода или файл 218 данных по Фиг.2. Средство проектирования может выполнять итерации для генерирования конструкции схемы, являющейся по существу глобально оптимизированной для границы сигнала, с учетом точности моделей устройства и алгоритмов моделирования средства проектирования, а также других факторов выполнения, таких как размеры шага и ошибки округления.

На Фиг.22 изображена и в общем обозначена ссылочной позицией 2200 структурная диаграмма конкретного иллюстративного варианта осуществления электронного устройства, включающего схему памяти на основе сопротивления, с параметрами, определенными посредством итеративной методики, как описано в настоящем документе. Данное устройство 2200 включает в себя процессор, такой как цифровой сигнальный процессор (DSP) 2210, соединенный с памятью 2232 и также соединенный со схемой 2264 памяти на основе сопротивления с параметрами, определяемыми посредством итеративной методики. В иллюстративном примере данная схема 2264 памяти на основе сопротивления с параметрами, определяемыми посредством итеративной методики, включает в себя память, изображенную на Фиг.1, и имеет параметры схемы, определяемые посредством использования одного или более способов по Фиг.20 и 21, с использованием устройства 202 по Фиг.2 или любой их комбинации. В конкретном варианте осуществления схема 2264 памяти на основе сопротивления с параметрами, определяемыми посредством итеративной методики, включает в себя устройство памяти магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM).

Фиг.22 также демонстрирует контроллер 2226 дисплея, соединенный с цифровым сигнальным процессором 2210 и дисплеем 2228. Кодер/декодер (CODEC) 2234 также может быть соединен с цифровым сигнальным процессором 2210. Динамик 2236 и микрофон 2238 могут быть соединены с кодером/декодером 2234.

Фиг.22 также обозначает, что беспроводной контроллер 2240 может быть соединен с цифровым сигнальным процессором 2210 и с беспроводной антенной 2242. В конкретном варианте осуществления DSP 2210, контроллер 2226 дисплея, память 2232, CODEC 2234, беспроводной контроллер 2240 и схема 2264 памяти на основе сопротивления с параметрами, определяемыми посредством итеративной методики, включены в систему в комплексе или систему на кристалле 2222. В конкретном варианте осуществления устройство ввода 2230 и источник питания 2244 соединены с системой на кристалле 2222. Более того, в конкретном варианте осуществления, как проиллюстрировано на Фиг.22, дисплей 2228, устройство ввода 2230, динамик 2236, микрофон 2238, беспроводная антенна 2242 и источник питания 2244 являются внешними относительно системы на кристалле 2222. Однако каждое из устройств может быть соединено с компонентом системы на кристалле 2222, таким как интерфейс или контроллер.

Специалистам в данной области техники должно быть понятно, что различные иллюстративные логические блоки, конфигурации, модули, схемы и алгоритмические этапы, описанные в связи с вариантами осуществления настоящего изобретения, могут быть выполнены в виде электронного аппаратного оборудования, компьютерного программного обеспечения или комбинации того и другого. Для ясной иллюстрации этой взаимозаменяемости аппаратного оборудования и программного обеспечения выше были в общих чертах описаны различные иллюстративные компоненты, блоки, конфигурации, модули, схемы и этапы с точки зрения их функциональности. Будет ли такая функциональность выполнена в виде аппаратного оборудования или программного обеспечения, зависит от конкретного варианта осуществления и ограничений по конструкции, накладываемых на всю систему. Специалисты могут выполнить описанную функциональность различными способами для каждого конкретного варианта осуществления, но такие решения по реализации не должны рассматриваться как выходящие за рамки описываемого изобретения.

Этапы способа или алгоритма, описанные в связи с вариантами осуществления настоящего раскрываемого изобретения, могут быть осуществлены непосредственно в аппаратном оборудовании, в модуле программного обеспечения, выполняемого процессором, или в комбинации обоих. Модуль программного обеспечения может находиться в оперативной памяти (RAM), флэш-памяти, постоянной памяти (ROM), программируемой постоянной памяти (PROM), стираемой программируемой постоянной памяти (EPROM), электрически стираемой программируемой постоянной памяти (EEPROM), регистрах, на жестком диске, съемном диске, в памяти только для чтения компактного диска (CD-ROM) или в любой другой форме среды для хранения, известной в уровне техники. Иллюстративный носитель для хранения соединяется с процессором, причем такой процессор может считывать информацию с и записывать информацию в среду. В качестве альтернативы носитель для хранения может быть встроен в процессор. Процессор и носитель для хранения могут находиться внутри специализированной интегральной схемы (ASIC). ASIC может находиться в вычислительном устройстве или в терминале пользователя. В качестве альтернативы процессор и носитель могут находиться как дискретные компоненты в вычислительном устройстве или в терминале пользователя.

Приведенное описание раскрытых вариантов осуществления настоящего изобретения призвано обеспечить специалисту в области техники возможность выполнения или использования раскрытых вариантов осуществления настоящего изобретения. Различные модификации данных вариантов осуществления будут явно очевидны для специалистов, и основные принципы, описанные в настоящем изобретении, могут быть применены к другим вариантам осуществления без изменения сущности или объема настоящего изобретения. Таким образом, настоящее изобретение не предназначено быть ограниченным описанными вариантами осуществления, но должно соответствовать самому широкому объему, согласующемуся с принципами и новыми признаками, раскрытыми в нижеследующей формуле изобретения.

Изобретение относится к области регулирования параметров схемы памяти на основе сопротивления. Техническим результатом является повышение эффективности улучшения границ усилителя считывания. Способ определения набора параметров схемы памяти на основе сопротивления включает в себя выбор первого параметра на основе первого предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления и выбор второго параметра на основе второго предварительно заданного ограничения по конструкции схемы памяти на основе сопротивления. Данный способ дополнительно включает в себя выполнение итеративной методики для регулирования, по меньшей мере, одного параметра схемы участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного назначения и регулирования физической характеристики упомянутого, по меньшей мере, одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра или второго параметра. 6 н. и 35 з.п. ф-лы, 24 ил.

1. Реализуемый процессором способ определения набора параметров схемы памяти на основе сопротивления, содержащий этапы, на которых:

принимают выбор первого параметра на основе первого ограничения по конструкции схемы памяти на основе сопротивления;

принимают выбор второго параметра на основе второго ограничения по конструкции схемы памяти на основе сопротивления; и

выполняют итеративный метод для регулирования по меньшей мере одного параметра схемы для участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного назначения и регулирования физической характеристики по меньшей мере одного параметра схемы для достижения желательного граничного значения усилителя считывания без изменения первого параметра или второго параметра, при этом по меньшей мере один параметр схемы включает в себя напряжение затвора фиксирующего транзистора опорной схемы внутри участка усилителя считывания.

2. Способ по п.1, в котором схема памяти на основе сопротивления включает в себя магниторезистивную оперативную память (MRAM), оперативную память на основе фазового перехода (PRAM) или память MRAM с переносом спинового момента (STT-MRAM).

3. Способ по п.1, в котором желательное граничное значение усилителя считывания представляет собой, по существу, максимальную границу сигнала усилителя считывания с учетом первого и второго ограничений по конструкции.

4. Способ по п.1, в котором выполнение итеративного метода заключается в регулировании физической характеристики для увеличения границы усилителя считывания.

5. Способ по п.1, в котором по меньшей мере один параметр схемы включает в себя ширину транзистора нагрузки, подсоединенного с возможностью работы в качестве опорного сопротивления к опорной схеме или представляющего собой нагрузку опорной схемы.

6. Способ по п.1, в котором фиксирующий транзистор работает в режиме насыщения и обеспечивает изменяемое сопротивление в тракте считывания данных элемента магнитного туннельного перехода (MTJ) схемы памяти на основе сопротивления.

7. Способ по п.6, в котором упомянутая опорная схема включает в себя нагрузку p-канального полевого транзистора типа металл-оксид-полупроводник (PMOS), соединенную с фиксирующим транзистором, в котором элемент MTJ соединен с фиксирующим транзистором и дополнительно соединен с транзистором числовой шины, и в котором схема памяти на основе сопротивления дополнительно включает в себя ячейку данных, имеющую вторую нагрузку PMOS, второй фиксирующий транзистор, второй элемент MTJ и второй транзистор числовой шины.

8. Способ по п.1, в котором схема памяти на основе сопротивления включает в себя магниторезистивную оперативную память с переносом спинового момента (STT-MRAM), и в котором первое ограничение по конструкции включает в себя сопротивление элемента магнитного туннельного перехода (MTJ) памяти STT-MRAM в нулевом состоянии бита.

9. Способ по п.8, в котором второе ограничение по конструкции включает в себя ширину фиксирующего транзистора опорной схемы участка усилителя считывания.

10. Реализуемый процессором способ определения набора параметров, содержащий этапы, на которых:

выбирают первый параметр на основе первого ограничения по конструкции магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM);

выбирают второй параметр на основе второго ограничения по конструкции STT-MRAM; и

выполняют итеративный метод для регулирования по меньшей мере одного параметра схемы для участка усилителя считывания STT-MRAM посредством выборочного регулирования физической характеристики упомянутого по меньшей мере одного параметра схемы для достижения желаемого граничного значения усилителя считывания, но без изменения первого параметра или второго параметра.

11. Способ по п.10, в котором второе ограничение по конструкции включает в себя сопротивление магнитного туннельного перехода (MTJ) памяти STT-MRAM в нулевом состоянии бита.

12. Способ по п.11, в котором второе ограничение по конструкции включает в себя ширину фиксирующего транзистора опорной схемы участка усилителя считывания, и в котором ширина фиксирующего транзистора выбирается с возможностью быть, по существу, наибольшей шириной, удовлетворяющей пространственному ограничению STT-MRAM.

13. Способ по п.11, в котором второе ограничение по конструкции включает в себя ширину фиксирующего транзистора опорной схемы участка усилителя считывания, и в котором сопротивление MTJ является параметром процесса обработки, в котором граница сигнала увеличивается и насыщается при увеличении ширины фиксирующего транзистора, и в котором ширина фиксирующего транзистора выбирается на основе границы сигнала и ограничения области.

14. Способ по п.11, в котором второе ограничение по конструкции включает в себя ширину фиксирующего транзистора опорной схемы участка усилителя считывания, и в котором выполнение итеративного метода включает в себя:

определение значения напряжения затвора фиксирующего транзистора и ширины транзистора нагрузки, приводящей в результате к, по существу, максимальной границе усилителя считывания; и

сравнение тока MTJ в единичном состоянии бита с пороговым значением тока.

15. Способ по п.14, в котором выполнение итеративного метода дополнительно включает в себя:

когда ток MTJ в единичном состоянии бита превышает предварительно заданное пороговое значение тока, итеративное уменьшение напряжения затвора фиксирующего транзистора и определение ширины транзистора нагрузки, приводящей в результате к, по существу, максимальной границе усилителя считывания с учетом напряжения затвора.

16. Способ по п.15, в котором по меньшей мере часть итеративного метода выполняется посредством автоматизированного средства проектирования, и в котором физической характеристике назначается начальное значение перед выполнением итеративного метода.

17. Постоянный считываемый процессором носитель, имеющий инструкции процессора, выполняемые для побуждения процессора:

принимать первый ввод первого параметра на основе первого ограничения по конструкции схемы памяти на основе сопротивления;

принимать второй ввод второго параметра на основе второго ограничения по конструкции схемы памяти на основе сопротивления;

выполнять итеративный метод для регулирования по меньшей мере одного параметра схемы для участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного регулирования физической характеристики упомянутого по меньшей мере одного параметра схемы для достижения желаемого граничного значения усилителя считывания без изменения первого параметра или второго параметра, причем первое ограничение по конструкции включает в себя ширину фиксирующего транзистора опорной схемы участка усилителя считывания; и

сохранять значение, связанное с физической характеристикой после того, как достигается желательная граница усилителя считывания с учетом первого и второго ограничения по конструкции.

18. Постоянный считываемый процессором носитель по п.17, в котором выполняемые процессором инструкции дополнительно выполняются для:

определения начального значения напряжения затвора фиксирующего транзистора участка усилителя считывания и начального значения ширины транзистора нагрузки участка усилителя считывания, приводящего в результате к, по существу, максимальному граничному значению усилителя считывания с учетом первого параметра и второго параметра.

19. Постоянный считываемый процессором носитель по п.18, при этом выборочное регулирование физической характеристики дополнительно включает в себя:

определение тока участка усилителя считывания посредством использования начального значения напряжения затвора и начального значения ширины транзистора нагрузки; и

сравнение тока участка усилителя считывания с пороговым значением тока.

20. Постоянный считываемый процессором носитель по п.19, при этом выборочное регулирование физической характеристики дополнительно включает в себя, когда ток превышает предварительно заданное пороговое значение тока:

определение уменьшенного напряжения затвора;

определение второй ширины транзистора нагрузки, приводящей в результате к, по существу, максимальному граничному значению усилителя считывания с учетом первого параметра, второго параметра и уменьшенного напряжения затвора; и

определение скорректированного тока участка усилителя считывания с использованием уменьшенного напряжения затвора и второй ширины транзистора нагрузки.

21. Постоянный считываемый процессором носитель по п.17, в котором инструкции процессора дополнительно выполняются, чтобы побуждать процессор выводить файл данных, представляющий конструкцию схемы для схемы памяти на основе сопротивления, имеющую желательную границу усилителя считывания.

22. Постоянный считываемый процессором носитель по п.17, в котором инструкции процессора являются совместимыми со средством автоматизированного проектирования.

23. Устройство определения набора параметров схемы памяти на основе сопротивления, содержащее

средство для приема выбора первого параметра на основе первого ограничения по конструкции схемы памяти на основе сопротивления;

средство для приема выбора второго параметра на основе второго ограничения по конструкции схемы памяти на основе сопротивления; и

средство для выполнения итеративного метода для регулирования по меньшей мере одного параметра схемы для участка усилителя считывания схемы памяти на основе сопротивления посредством выборочного назначения и регулирования физической характеристики упомянутого по меньшей мере одного параметра схемы для достижения желательного граничного значения усилителя считывания без изменения первого параметра или второго параметра, при этом по меньшей мере один параметр схемы включает в себя напряжение затвора фиксирующего транзистора опорной схемы внутри участка усилителя считывания.

24. Устройство по п.23, в котором схема памяти на основе сопротивления включает в себя магниторезистивную оперативную память (MRAM), оперативную память на основе фазового перехода (PRAM) или память MRAM с переносом спинового момента (STT-MRAM).

25. Устройство по п.23, в котором желательное граничное значение усилителя считывания представляет собой, по существу, максимальную границу сигнала усилителя считывания с учетом первого и второго ограничений по конструкции.

26. Устройство по п.23, в котором выполнение итеративного метода заключается в регулировании физической характеристики для увеличения границы усилителя считывания.

27. Устройство по п.23, в котором по меньшей мере один параметр схемы включает в себя ширину транзистора нагрузки, подсоединенного с возможностью работы в качестве опорного сопротивления к опорной схеме или представляющего собой нагрузку опорной схемы.

28. Устройство по п.23, в котором фиксирующий транзистор работает в режиме насыщения и обеспечивает изменяемое сопротивление в тракте считывания данных элемента магнитного туннельного перехода (MTJ) схемы памяти на основе сопротивления.

29. Устройство по п.28, в котором опорная схема включает в себя нагрузку p-канального полевого транзистора типа металл-оксид-полупроводник (PMOS), соединенную с фиксирующим транзистором, в котором элемент MTJ соединен с фиксирующим транзистором и дополнительно соединен с транзистором числовой шины, и в котором схема памяти на основе сопротивления дополнительно включает в себя ячейку данных, имеющую вторую нагрузку PMOS, второй фиксирующий транзистор, второй элемент MTJ и второй транзистор числовой шины.