I. Область техники, к которой относится изобретение

Настоящее изобретение в целом направлено на запоминающее устройство, включающее в себя усилитель и ячейку памяти, включающую в себя основанный на сопротивлении элемент памяти.

II. Уровень техники

Достижения в технологии энергонезависимой памяти включают в себя технологии основанной на сопротивлении памяти, такие как магнитная оперативная память (MRAM). Технология MRAM является развивающейся энергонезависимой технологией памяти, которая применяет основанные на ферромагнитных материалах магнитные туннельные переходы (MTJ) в качестве основных элементов памяти. Общеупотребительной матричной архитектурой для MRAM является однотранзисторная архитектура с одним туннельным переходом (1T1MTJ). Как следует из названия, каждая битовая ячейка в этой архитектуре состоит из MTJ, последовательно соединенного с n-МОП входным транзистором. Для того чтобы использовать преимущества повышенной плотности и уменьшения площади, ассоциированные с МОП-технологиями, уменьшающими масштабы, желательно использовать транзисторы ядра в пределах MRAM-битовой ячейки. Однако хотя МОП-технологии, уменьшающие масштаб в глубоком субмикронном режиме, дают преимущество в площади и плотности в MRAM-битовых ячейках, использование этих субмикронных устройств в MRAM-усилителе считывания понижает производительность чтения (выходной размах) MRAM-усилителя считывания из-за ограничений рабочего напряжения этих глубоких субмикронных устройств.

Традиционные конструкции MRAM-усилителей считывания для архитектуры 1T1MTJ используют транзисторы ядра. Однако по соображениям выхода из строя и надежности напряжение питания для транзисторов ядра типично ограничено до около 1 вольта (В) для передовых глубоких субмикронных технологий. Следующие устройства скомпонованы между шинами питания в традиционных конструкциях MRAM-усилителя считывания для архитектуры 1T1MTJ: битовая ячейка, содержащая входной транзистор, и MTJ-устройство, mux(мультиплексорный)-транзистор, фиксирующий транзистор и p-канальный МОП-нагрузочный транзистор. Входной и mux-транзисторы должны управляться как переключатели (в линейной области), между тем как фиксирующий и p-канальный МОП-нагрузочный транзисторы должны оставаться в насыщении для усилителя считывания, чтобы показывать удовлетворительное усиление. Однако требование низкого напряжения питания, которое происходит от применения устройств ядра в усилителе считывания, вместе с пороговым напряжением транзистора, являющимся значительной частью этого напряжения питания, может сделать трудным поддержание фиксирующего и p-канального МОП-нагрузочного транзисторов в насыщении, что, в свою очередь, ухудшает усиление и имеет результатом недостаточный оптимальный размах сигнала на выходе усилителя считывания.

III. Раскрытие изобретения

В частном варианте осуществления раскрыто запоминающее устройство, которое включает в себя ячейку памяти, включающую в себя основанный на сопротивлении элемент памяти, соединенный с входным транзистором. Входной транзистор имеет первую толщину оксида для того, чтобы дать возможность работы ячейки памяти при рабочем напряжении. Запоминающее устройство также включает в себя первый усилитель, выполненный с возможностью прикладывать напряжение питания к ячейке памяти, которое больше, чем предел напряжения, для генерации сигнала данных на основе тока через ячейку памяти. Первый усилитель включает в себя фиксирующий транзистор, который имеет вторую толщину оксида, которая больше, чем первая толщина оксида. Фиксирующий транзистор выполнен с возможностью предотвращать превышение предела напряжения рабочим напряжением в ячейке памяти.

В другом варианте осуществления раскрыто запоминающее устройство, которое включает в себя тракт чтения данных, включающий в себя первое нагрузочное устройство, соединенное с ячейкой хранения данных через первый фиксирующий транзистор. Первое нагрузочное устройство имеет конфигурацию первого устройства для работы при первом напряжении питания. Ячейка хранения данных включает в себя входной транзистор, имеющий конфигурацию второго устройства для работы при напряжении, которое не должно превышать предел напряжения, который меньше, чем первое напряжение питания. На управляющий вывод фиксирующего транзистора подается напряжение смещения для предотвращения превышения предела напряжения напряжением в ячейке хранения данных.

В другом варианте осуществления раскрыт способ, который включает в себя соединение первой ступени (каскада) усиления с матрицей памяти. Первая ступень усиления включает в себя транзисторы, имеющие допустимый предел напряжения питания ввода/вывода (IO). Матрица памяти включает в себя транзисторы, имеющие допустимый предел напряжения питания ядра, который меньше, чем допустимый предел напряжения питания IO. Способ включает в себя применение управляющего напряжения на фиксирующем транзисторе, соединенном с матрицей памяти для установки напряжения матрицы памяти, так что напряжение матрицы памяти меньше, чем допустимый предел напряжения питания ядра.

Одно частное преимущество, предоставленное раскрытыми вариантами осуществления, состоит в улучшении производительности чтения усилителя считывания MRAM, потому что более высокое напряжение питания дает возможность более высокого выходного размаха для того, чтобы различать логические значения во время операций считывания.

Другие аспекты, преимущества и признаки настоящего изобретения станут очевидными после просмотра в целом заявки, включающей в себя секции: Краткое описание чертежей, Детальное описание и Формула изобретения.

IV. Краткое описание чертежей

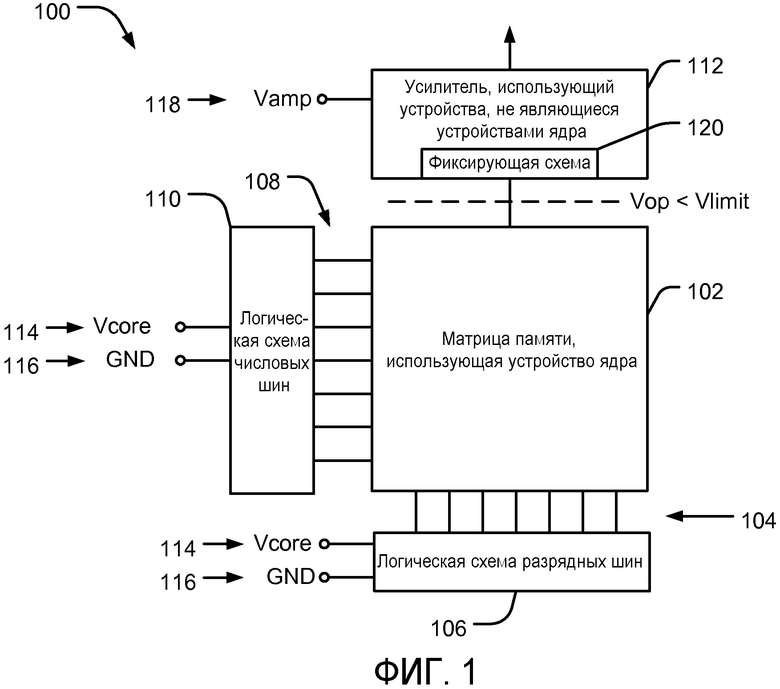

Фиг.1 - схема частного иллюстративного варианта осуществления запоминающего устройства с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства.

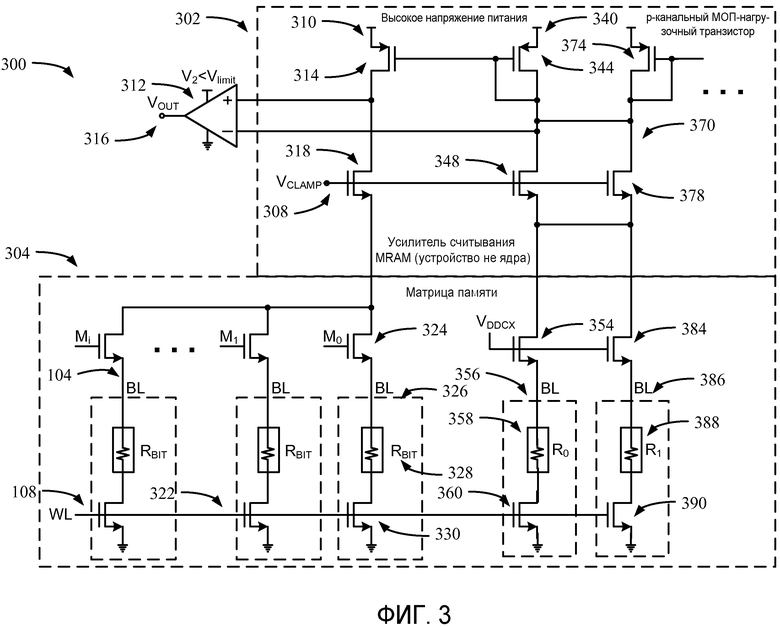

Фиг.2 - схема второго иллюстративного варианта осуществления запоминающего устройства с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства.

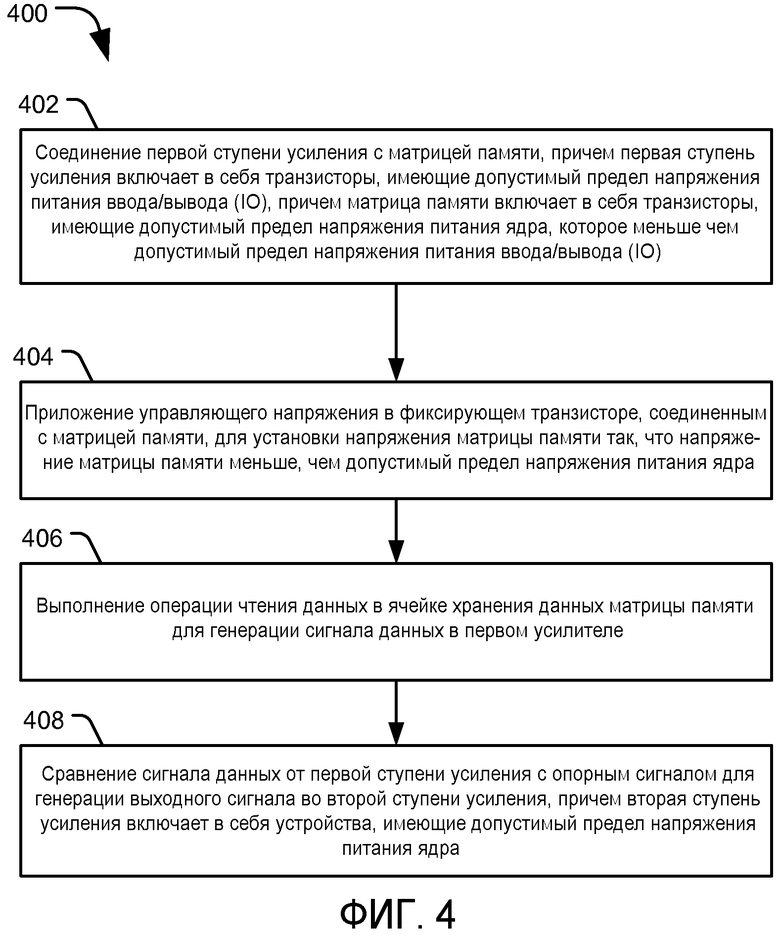

Фиг.3 - схема третьего иллюстративного варианта осуществления запоминающего устройства с усилителем, использующим первый тип устройства, и матрицей памяти, использующей второй тип устройства; и

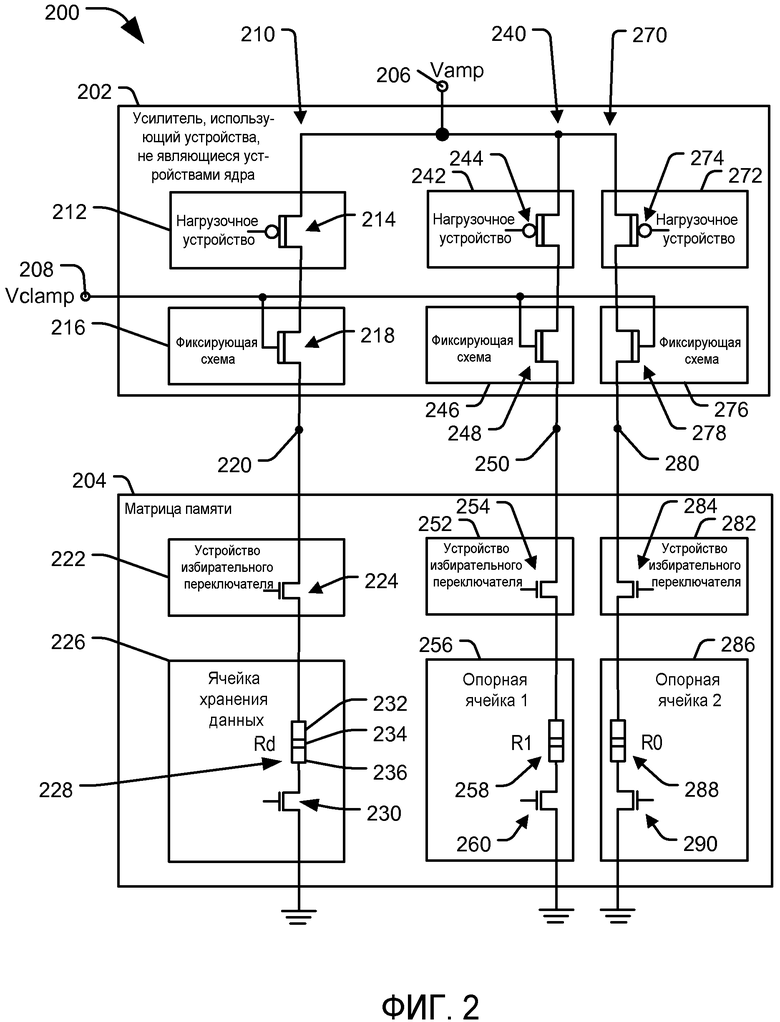

фиг.4 - блок-схема последовательности операций частного иллюстративного варианта осуществления способа работы запоминающего устройства с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства.

V. Подробное описание

Со ссылкой на фиг.1 показан и в целом обозначен частный иллюстративный вариант осуществления запоминающего устройства 100 с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства. Запоминающее устройство 100 может включать в себя матрицу 102 памяти, использующую устройства ядра. В частном варианте осуществления устройства ядра могут работать при напряжении Vcore питания ядра вплоть до около 1 вольта (В). Матрица 102 памяти может быть соединена разрядными шинами 104 с логической схемой 106 разрядных шин. Матрица 102 памяти может быть соединена числовыми шинами 108 с логической схемой 110 числовых шин. Логическая схема 106 разрядных шин и логическая схема 110 числовых шин могут быть подключены к напряжению Vcore питания ядра, как указано 114, и земле, как указано 116. Матрица 102 памяти также может быть соединена с усилителем 112, который использует устройства, не являющиеся устройствами ядра. В частном варианте осуществления устройства, не являющиеся устройствами ядра, могут работать при напряжениях Vamp питания ввода-вывода (IO) вплоть до около 1,8 В. Усилитель 112 может быть подключен к напряжению Vamp питания IO, как указано 118. Усилитель может включать в себя фиксирующую схему 120, соединенную с матрицей 102 памяти, для поддержания рабочего напряжения Vop, подаваемого матрице 102 памяти усилителем ниже предела Vlimit напряжения.

Применяя более высокое напряжение Vamp питания и допускающие высокое напряжение устройства ввода-вывода (IO) для транзисторов в усилителе 112 считывания, тогда как продолжая использовать устройства ядра с эффективными площадями в матрице 102 памяти, например, для транзисторов битовых ячеек MRAM, как например, входных транзисторов и MUX-транзисторов, производительность чтения может быть улучшена, поддерживая высокую плотность матрицы. Поскольку допускающие высокое напряжение устройства ввода/вывода используют более толстый оксид затвора, их минимальный размер элемента также является большим, чем у устройств ядра, что подразумевает более высокое влияние на площадь. Как проиллюстрировано, система 100 предоставляет улучшение в производительности чтения (выходной размах) усилителя 112 считывания MRAM без значительного ухудшения в площади для оконечного запоминающего устройства 100 потому, что (1) более высокое напряжение питания имеет в результате больший выходной размах, таким образом значительно улучшая производительность чтения, и (2) допускающие высокое напряжение устройства ввода/вывода могут быть использованы только в усилителе 112 считывания, при этом битовые ячейки MRAM, которые образуют намного большую часть площади запоминающего устройства 100, используют высокоплотные устройства ядра. Поскольку количество усилителей 112 считывания на чипе памяти гораздо меньше, чем количество битовых ячеек, расплата площадью, которая образуется от использования допускающих высокое напряжение устройств ввода/вывода для фиксирующих и p-канальных МОП-нагрузочных транзисторов в усилителе 112 считывания, может быть минимальной по сравнению со значительно улучшенной производительностью чтения, которая ассоциирована с использованием более высокого напряжения питания.

Со ссылкой на фиг.2 отображена и в целом обозначена 200 схема второго иллюстративного примера запоминающего устройства с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства. В частном варианте осуществления запоминающее устройство 200 работает по существу подобно запоминающему устройству 100, проиллюстрированному на фиг.1. Запоминающее устройство 200 может включать в себя ячейку 226 памяти (или хранения данных), которая может включать в себя основанный на сопротивлении элемент 228 памяти, соединенный с входным транзистором 230. Входной транзистор 230 может иметь первую толщину оксида для того, чтобы дать возможность работы ячейки 226 памяти при рабочем напряжении Vop. В конкретном варианте осуществления ячейка 226 памяти может быть ячейкой магниторезистивной оперативной памяти с передачей спинового вращательного момента. Ячейка 226 памяти может быть включена в матрицу 204 памяти (STT-MRAM). Запоминающее устройство 200 может также включать в себя первый усилитель 202, выполненный с возможностью вводить в ячейку 226 памяти напряжение Vamp питания в питающем выводе 206 источника питания, где напряжение Vamp питания больше, чем предел напряжения Vlimit для генерации сигнала данных на основе тока через ячейку 226 памяти. Первый усилитель 202 может включать в себя первый фиксирующий транзистор 218, который имеет вторую толщину оксида, которая больше, чем первая толщина оксида входного транзистора 230. Фиксирующий транзистор 218 может быть выполнен с возможностью предотвращения превышения предела напряжения Vlimit рабочим напряжением Vop в ячейке 226 памяти. Предоставляя подходящее фиксирующее напряжение Vclamp управления на управляющем выводе 208 для защиты матрицы 204 памяти от напряжений, превышающих Vlimit, матрица 204 памяти может использовать меньшие устройства для более высокой плотности и меньших размеров. В дополнение первый усилитель 202 может использовать более робастные устройства для улучшения работы, используя большее напряжение Vamp питания.

В частном варианте осуществления входной транзистор 230 может иметь конфигурацию устройства ядра, а первый фиксирующий транзистор 218 может иметь конфигурацию устройства ввода/вывода (IO). В этих частных вариантах осуществления первый фиксирующий транзистор 218 может быть выполнен с возможностью работать при напряжении Vamp питания ввода-вывода (IO), а входной транзистор 230 может быть выполнен с возможностью работать при напряжении Vcore питания ядра. В этих частных вариантах осуществления напряжение Vcore питания ядра может быть приблизительно 1 В, а напряжение Vamp питания IO может быть приблизительно 1,8 В. В частном варианте осуществления входной транзистор 230 может иметь конфигурацию устройства ядра с первой толщиной оксида в диапазоне от около 1 нм до около 3 нм. В этих частных вариантах осуществления первый фиксирующий транзистор 218 может иметь конфигурацию устройства ввода/вывода (IO) со второй толщиной оксида в диапазоне от около 3,5 нм до около 10 нм.

Тракт 210 чтения данных может включать в себя первое нагрузочное устройство 212, которое может включать в себя первый нагрузочный транзистор 214. В частном варианте осуществления первый нагрузочный транзистор 214 может быть p-канальным МОП-нагрузочным транзистором. Первое нагрузочное устройство 212 может быть соединено с первым фиксирующим устройством 216, которое может включать в себя первый фиксирующий транзистор 218, где первый нагрузочный транзистор 214 может быть соединен с первым фиксирующим транзистором 218. Первый фиксирующий транзистор 218 может быть соединен с управляющим выводом 208, на который может быть подано фиксирующее напряжение Vclamp смещения. Первое фиксирующее устройство 216 может быть соединено через первый узел 220 с первым устройством 222 избирательного переключателя, которое может включать в себя первый MUX-транзистор 224, где первый фиксирующий транзистор 218 может быть соединен с первым MUX-транзистором 224. Первое устройство 222 избирательного переключателя может быть включено в матрицу 204 памяти. Первое устройство 222 избирательного переключателя может быть соединено с ячейкой 226 памяти, где первый MUX-транзистор 224 может быть соединен с входным транзистором 230 через основанный на сопротивлении элемент 228 памяти, имеющий сопротивление Rd. В частном варианте осуществления основанный на сопротивлении элемент 228 памяти может включать в себя магнитный туннельный переход (MTJ), который может включать в себя опорный слой 232, туннельный слой 234 и свободный слой 236. Входной транзистор 230 может быть соединен с землей.

Первый опорный тракт 240 может включать в себя второе нагрузочное устройство 242, которое может включать в себя второй нагрузочный транзистор 244. В частном варианте осуществления второй нагрузочный транзистор 244 может быть p-канальным МОП-нагрузочным транзистором. Второе нагрузочное устройство 242 может быть соединено со вторым фиксирующим устройством 246, которое может включать в себя второй фиксирующий транзистор 248, где второй нагрузочный транзистор 244 может быть соединен со вторым фиксирующим транзистором 248. Второй фиксирующий транзистор 248 может быть соединен с управляющим выводом 208, на который может быть подано фиксирующее напряжение Vclamp смещения. Второе фиксирующее устройство 246 может быть соединено через второй узел 250 со вторым устройством 252 избирательного переключателя, которое может включать в себя второй MUX-транзистор 254, где второй фиксирующий транзистор 248 может быть соединен со вторым MUX-транзистором 254. Второе устройство 252 избирательного переключателя может быть включено в матрицу 204 памяти. Второе устройство 252 избирательного переключателя может быть соединено с первой опорной ячейкой 256, где второй MUX-транзистор 254 может быть соединен с первым опорным входным транзистором 260 через первый, основанный на сопротивлении опорный элемент 258, имеющий сопротивление R1. В частном варианте осуществления основанный на сопротивлении элемент 258 памяти может включать в себя магнитный туннельный переход (MTJ). Первый опорный входной транзистор 260 может быть соединен с землей.

Второй опорный тракт 270 может включать в себя третье нагрузочное устройство 272, которое может включать в себя третий нагрузочный транзистор 274. В частном варианте осуществления третий нагрузочный транзистор 274 может быть p-канальным МОП-нагрузочным транзистором. Третье нагрузочное устройство 272 может быть соединено с третьим фиксирующим устройством 276, которое может включать в себя третий фиксирующий транзистор 278, где третий нагрузочный транзистор 274 может быть соединен с третьим фиксирующим транзистором 278. Третий фиксирующий транзистор 278 может быть соединен с управляющим выводом 208, на который может быть подано фиксирующее напряжение Vclamp смещения. Третье фиксирующее устройство 276 может быть соединено через второй узел 280 с третьим устройством 282 избирательного переключателя, которое может включать в себя третий MUX-транзистор 284, где третий фиксирующий транзистор 278 может быть соединен с третьим MUX-транзистором 284. Третье устройство 282 избирательного переключателя может быть включено в матрицу 204 памяти. Третье устройство 282 избирательного переключателя может быть соединено со второй опорной ячейкой 286, где третий MUX-транзистор 284 может быть соединен со вторым опорным входным транзистором 290 через второй, основанный на сопротивлении опорный элемент 288, имеющий сопротивление R0. В частном варианте осуществления основанный на сопротивлении элемент 288 памяти может включать в себя магнитный туннельный переход (MTJ). Второй опорный входной транзистор 290 может быть соединен с землей.

Первый усилитель 202 может включать в себя первый нагрузочный транзистор 214, соединенный с первым фиксирующим транзистором 218 для генерации сигнала данных. Первый усилитель 202 может включать в себя второй нагрузочный транзистор 244, соединенный со вторым фиксирующим транзистором 248, и третий нагрузочный транзистор 274, соединенный с третьим фиксирующим транзистором 278. Второй фиксирующий транзистор 248 и третий фиксирующий транзистор 278 могут быть выполнены с возможностью соединяться с первой опорной ячейкой 256 и со второй опорной ячейкой 286 соответственно для генерации опорного сигнала. Первый фиксирующий транзистор 218, второй фиксирующий транзистор 248, третий фиксирующий транзистор 278, первый нагрузочный транзистор 214, второй нагрузочный транзистор 244 и третий нагрузочный транзистор 274 могут иметь конфигурацию устройства ввода/вывода (IO). По меньшей мере, один транзистор 230, 260, 290 ячейки 226 памяти, первой опорной ячейки 256 и второй опорной ячейки 286 могут иметь конфигурацию устройства ядра. В частном варианте осуществления первый MUX-транзистор 224, второй MUX-транзистор 254 и третий MUX-транзистор 284 могут иметь конфигурацию устройства ядра.

Как описано выше, тракт 210 чтения данных может включать в себя первое нагрузочное устройство 212, соединенное с ячейкой 226 хранения данных через первый фиксирующий транзистор 218. Первое нагрузочное устройство 212 может иметь конфигурацию первого устройства для работы при первом напряжении Vamp питания, подаваемом на питающем выводе 206. В частном варианте осуществления конфигурации первого устройства может быть конфигурацией устройства, не являющегося устройством ядра. В этих частных вариантах осуществления конфигурация первого устройства может быть конфигурацией устройства ввода/вывода (IO). Ячейка 226 хранения данных может включать в себя входной транзистор 230, который может иметь конфигурацию второго устройства, чтобы работать при рабочем напряжении Vop в узле 220, которое не превышает предел напряжения Vlimit, который меньше чем первое напряжение Vamp питания. В частном варианте осуществления конфигурация второго устройства может быть конфигурацией устройства ядра. В этих частных вариантах осуществления конфигурация устройства ядра может иметь меньший физический размер, чем конфигурация устройства, не являющегося устройством ядра. На управляющий вывод 208 первого фиксирующего транзистора 218 может быть подано напряжение смещения для предотвращения превышения предела напряжения Vlimit напряжением Vop в ячейке 226 хранения данных. В частном варианте осуществления предел напряжения Vlimit может быть приблизительно 1 В.

Как описано выше, первый опорный тракт 240 может включать в себя второе нагрузочное устройство 242, соединенное с первой опорной ячейкой 256, а второй опорный тракт 270 может включать в себя третье нагрузочное устройство 272, соединенное со второй опорной ячейкой 286. Второе нагрузочное устройство 242 и третье нагрузочное устройство 272 могут иметь конфигурацию первого устройства. Первая опорная ячейка 256 и вторая опорная ячейка 286 каждая может включать в себя, по меньшей мере, один транзистор 260, 290, который может иметь конфигурацию второго устройства. Второй фиксирующий транзистор 248 может предотвращать превышение предела напряжения Vlimit вторым напряжением в первой опорной ячейке 256. Третий фиксирующий транзистор 278 может предотвращать превышение предела напряжения Vlimit третьим напряжением во второй опорной ячейке 286. Первое устройство 222 избирательного переключателя в тракте 210 чтения данных может выборочно соединять ячейку 226 хранения данных с первым фиксирующим транзистором 218. Второе устройство 252 избирательного переключателя в первом опорном тракте 240 может выборочно соединять первую опорную ячейку 256 со вторым фиксирующим транзистором 248. Третье устройство 282 избирательного переключателя во втором опорном тракте 270 может выборочно соединять вторую опорную ячейку 286 с третьим фиксирующим транзистором 278. Каждое из первого устройства 222 избирательного переключателя, второго устройства 252 избирательного переключателя и третьего устройства 282 избирательного переключателя может иметь конфигурацию второго устройства.

Со ссылкой на фиг.3 показан и в целом обозначен 300 третий иллюстративный вариант осуществления запоминающего устройства с усилителем, использующим первый тип устройства, и матрицей памяти, использующей второй тип устройства. В частном варианте осуществления запоминающее устройство 300 работает по существу подобно запоминающему устройству 100, проиллюстрированному на фиг.1, и запоминающему устройству 200, проиллюстрированному на фиг.2. Запоминающее устройство 300 может включать в себя множество ячеек 326 памяти (хранения данных), которые каждая могут включать в себя основанный на сопротивлении элемент 328 памяти, соединенный с входным транзистором 330. Входной транзистор может 330 иметь первую толщину оксида, для того чтобы дать возможность работы ячеек 326 памяти при рабочем напряжении Vop. В частном варианте осуществления ячейки 326 памяти могут быть ячейками магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM). Ячейки 326 памяти могут быть включены в матрицу 304 памяти. Запоминающее устройство 300 может также включать в себя первую ступень 302 усиления, выполненную с возможностью соединять ячейки 326 памяти с высоким напряжением Vamp питания, где напряжение Vamp питания больше, чем предел напряжения Vlimit для генерации сигнала данных на основе тока через одну из ячеек 326 памяти. Первая ступень 302 усиления может включать в себя первый фиксирующий транзистор 318, который имеет вторую толщину оксида, которая больше, чем первая толщина оксида входного транзистора 330. Первый фиксирующий транзистор 318 может быть выполнен с возможностью предотвращать превышение предела напряжения Vlimit рабочим напряжением Vop в ячейках 326 памяти. В частном варианте осуществления первый фиксирующий транзистор 318 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства, не являющегося устройством ядра.

В частном варианте осуществления входной транзистор 330 может иметь конфигурацию устройства ядра, а первый фиксирующий транзистор 318 может иметь конфигурацию устройства ввода/вывода (IO). В этих частных вариантах осуществления первый фиксирующий транзистор 318 может быть выполнен с возможностью работать при напряжении Vamp питания ввода-вывода (IO), а входной транзистор 330 может быть выполнен с возможностью работать при напряжении Vcore питания ядра. В этих частных вариантах осуществления напряжение Vcore питания ядра может находиться в пределах диапазона от около 0,9 В до около 1,2 В, как, например, 1 В, а напряжение Vamp питания IO может находиться в пределах диапазона от около 1,5 В до около 2,0 В, как, например, приблизительно 1,8 В.

Первая ступень 302 усиления может быть дополнительно выполнена с возможностью прикладывать, по меньшей мере, к одной опорной ячейке 356, 386 напряжение Vamp питания для генерации опорного сигнала. Запоминающее устройство 300 может включать в себя вторую ступень 312 усиления, соединенную с первой ступенью 302 усиления. Вторая ступень 312 усиления может быть выполнена с возможностью предоставлять выходной сигнал Vout на выводе 316 на основе разницы между сигналом данных и опорным сигналом. Вторая ступень 312 усиления может включать в себя, по меньшей мере, один транзистор, который имеет первую толщину оксида входного транзистора 330 и на который подается второе напряжение V2 питания, которое не превышает предел напряжения Vlimit.

Матрица 304 памяти может включать в себя множество MUX-транзисторов 324, M0, Ml, ..., Mi, соответствующих множеству ячеек 326 памяти на соответствующем множестве разрядных шин 104 (фиг.1). В частном варианте осуществления MUX-транзисторы 324 могут быть n-канальными МОП-транзисторами, имеющими конфигурацию устройства ядра. Каждый из множества MUX-транзисторов 324 M0, Ml, ..., Mi может соединять соответствующую одну из множества ячеек 326 памяти с первым фиксирующим транзистором 318, предоставляя один из множества трактов 310 чтения данных.

Каждый из трактов 310 чтения данных может включать в себя первый нагрузочный транзистор 314. В частном варианте осуществления первый нагрузочный транзистор 314 может быть p-канальным МОП-нагрузочным транзистором. Первый нагрузочный транзистор 314 может быть соединен с первым фиксирующим транзистором 318. Первый фиксирующий транзистор 318 может быть соединен с управляющим выводом 308, на который может быть подано фиксирующее напряжение Vclamp смещения. Первый фиксирующий транзистор 318 может быть соединен с MUX-транзисторами 324. MUX-транзисторы 324 могут быть соединены с входными транзисторами 330 через основанные на сопротивлении элементы 328 памяти соответствующих ячеек 326 памяти. Основанные на сопротивлении элементы 328 памяти могут каждый включать в себя магнитный туннельный переход (MTJ), проиллюстрированный как сопротивление Rbit, которое может включать в себя величину сопротивления логического "0" или логической "1". Входные транзисторы 330 могут быть соединены с землей. Затворы входных транзисторов 330 могут быть соединены с одной из множества числовых шин 108 (фиг.1). В частном варианте осуществления входные транзисторы 330 могут быть n-канальными МОП-транзисторами, имеющими конфигурацию устройства ядра.

Первый опорный тракт 340 может включать в себя второй нагрузочный транзистор 344. В частном варианте осуществления второй нагрузочный транзистор 344 может быть p-канальным МОП-нагрузочным транзистором в диодном включении. Второй нагрузочный транзистор 344 может быть соединен со вторым фиксирующим транзистором 348. Второй фиксирующий транзистор 348 может быть соединен с управляющим выводом 308, на который может быть подано фиксирующее напряжение Vclamp смещения. В частном варианте осуществления второй фиксирующий транзистор 348 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства, не являющегося устройством ядра. Второй фиксирующий транзистор 348 может быть соединен с MUX-транзистором 354. MUX-транзистор 354 может быть включен в матрицу 304 памяти. В частном варианте осуществления MUX-транзистор 354 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства ядра. Затвор MUX-транзистора 354 может быть соединен с источником напряжения, имеющим напряжение Vddcx, которое меньше, чем предел напряжения устройства ядра. MUX-транзистор 354 может быть соединен с первой опорной ячейкой 356, где MUX-транзистор 354 может быть соединен с первым опорным входным транзистором 360 через первый, основанный на сопротивлении опорный элемент 358, имеющий сопротивление R0. В частном варианте осуществления основанный на сопротивлении элемент 358 памяти может включать в себя магнитный туннельный переход (MTJ). Первый опорный входной транзистор 360 может быть соединен с землей. Затвор первого опорного входного транзистора 360 может быть соединен с числовой шиной 322, как, например, одной из множества числовых шин 108, показанных на фиг.1. В частном варианте осуществления первый опорный входной транзистор 360 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства ядра.

Второй опорный тракт 370 может включать в себя третий нагрузочный транзистор 374. В частном варианте осуществления третий нагрузочный транзистор 374 может быть p-канальным МОП-нагрузочным транзистором. Третий нагрузочный транзистор 274 может быть соединен с третьим фиксирующим транзистором 278. Третий фиксирующий транзистор 278 может быть соединен с управляющим выводом 208, на который может быть подано фиксирующее напряжение Vclamp смещения. В частном варианте осуществления третий фиксирующий транзистор 378 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства, не являющимся устройством ядра. Третий фиксирующий транзистор 278 может быть соединен с MUX-транзистором 384. MUX-транзистор 384 может быть включен в матрицу 304 памяти. В частном варианте осуществления MUX-транзистор 384 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства ядра. Затвор MUX-транзистора 384 может быть соединен с затвором MUX-транзистора 354 и может быть также соединен с источником напряжения, имеющим напряжение Vddcx. MUX-транзистор 284 может быть соединен со второй опорной ячейкой 386, где MUX-транзистор 384 может быть соединен со вторым опорным входным транзистором 390 через второй, основанный на сопротивлении опорный элемент 388, имеющий сопротивление R1. В частном варианте осуществления основанный на сопротивлении элемент 358 памяти может включать в себя магнитный туннельный переход (MTJ). Второй опорный входной транзистор 390 может быть соединен с землей. Затвор второго опорного входного транзистора 390 может быть соединен с одной из множества числовых шин 108 (фиг.1). В частном варианте осуществления второй опорный входной транзистор 390 может быть n-канальным МОП-транзистором, имеющим конфигурацию устройства ядра.

Первая ступень 302 усиления может включать в себя первый нагрузочный транзистор 314, соединенный с первым фиксирующим транзистором 318 для генерации сигнала данных. Первая ступень 302 усиления может включать в себя второй нагрузочный транзистор 344, соединенный со вторым фиксирующим транзистором 348, и третий нагрузочный транзистор 374, соединенный с третьим фиксирующим транзистором 378. Второй фиксирующий транзистор 348 и третий фиксирующий транзистор 378 могут быть выполнены с возможностью соединяться с первой опорной ячейкой 356 и со второй опорной ячейкой 386 соответственно для генерации опорного сигнала. Вторая ступень 312 усиления может быть соединена с каждым из: трактов 310 чтения данных, первого опорного тракта 340 и второго опорного тракта 370. Вторая ступень 312 усиления может быть выполнена с возможностью предоставлять выходной сигнал Vout на выводе 316 на основе разницы между сигналом данных и опорным сигналом. Первый фиксирующий транзистор 318, второй фиксирующий транзистор 348, третий фиксирующий транзистор 378, первый нагрузочный транзистор 314, второй нагрузочный транзистор 344 и третий нагрузочный транзистор 374 могут иметь конфигурацию устройства ввода/вывода (IO). По меньшей мере, один из транзисторов 330, 360, 390 ячеек 326 памяти, первая опорная ячейка 356 и вторая опорная ячейка 386 могут иметь конфигурацию устройства ядра. В частном варианте осуществления MUX-транзисторы 324, MUX-транзистор 354 и MUX-транзистор 384 могут иметь конфигурацию устройства ядра. Вторая ступень 312 усиления может включать в себя, по меньшей мере, один транзистор, который имеет конфигурацию устройства ядра и к которому приложено второе напряжение V2 питания, которое не превышает предел напряжения Vlimit.

Как описано выше, каждый из трактов 310 чтения данных может включать в себя первый нагрузочный транзистор 314, соединенный с ячейками 326 памяти через первый фиксирующий транзистор 318. Первый нагрузочный транзистор 314 может иметь конфигурацию первого устройства для работы при первом напряжении Vamp питания. В частном варианте осуществления конфигурация первого устройства может быть конфигурацией устройства, не являющегося устройством ядра. В этих частных вариантах осуществления конфигурация первого устройства может быть конфигурацией устройства ввода/вывода (IO). Ячейки 326 памяти могут включать в себя входные транзисторы 330, которые могут иметь конфигурацию второго устройства для работы при рабочем напряжении Vop, которое не превышает предел напряжения Vlimit, который меньше, чем первое напряжение Vamp питания. В частном варианте осуществления конфигурация второго устройства может быть конфигурацией устройства ядра. В этих частных вариантах осуществления конфигурация устройства ядра может иметь более маленький физический размер, чем конфигурация устройства, не являющегося устройством ядра. На управляющий вывод 308 первого фиксирующего транзистора 318 может быть подано напряжение смещения для предотвращения превышения предела напряжения Vlimit напряжением Vop в ячейках 326 памяти. В частном варианте осуществления предел напряжения Vlimit может быть приблизительно 1 В.

Как описано выше, первый опорный тракт 340 может включать в себя второй нагрузочной транзистор 344, соединенный с первой опорной ячейкой 356, а второй опорный тракт 370 может включать в себя третий нагрузочный транзистор 374, соединенный со второй опорной ячейкой 386. Второй нагрузочный транзистор 344 и третий нагрузочный транзистор 374 могут иметь конфигурацию первого устройства. Первая опорная ячейка 356 и вторая опорная ячейка 386 каждая может включать в себя, по меньшей мере, один транзистор 360, 390, который может иметь конфигурацию второго устройства. Второй фиксирующий транзистор 348 может предотвращать превышение предела напряжения Vlimit вторым напряжением в первой опорной ячейке 356. Третий фиксирующий транзистор 378 может предотвращать превышение предела напряжения Vlimit третьим напряжением во второй опорной ячейке 386. MUX-транзисторы 324 в трактах 310 чтения данных могут выборочно соединять ячейки 326 памяти с первым фиксирующим транзистором 318. На MUX-транзистор 354 в первом опорном тракте 340 может быть подано напряжение смещения для соединения первой опорной ячейки 356 со вторым фиксирующим транзистором 348. На MUX-транзистор 384 во втором опорном тракте 370 может быть подано напряжение смещения для соединения второй опорной ячейки 386 с третьим фиксирующим транзистором 378. Каждый из MUX-транзисторов 324, 354, 384 может иметь конфигурацию второго устройства.

Со ссылкой на фиг.4 показана и в целом обозначена 400 блок-схема последовательности операций частного иллюстративного варианта осуществления способа работы запоминающего устройства с усилителем, использующим первый тип устройства, и с матрицей памяти, использующей второй тип устройства. На этапе 402 первая ступень усиления может быть соединена с матрицей памяти. Первая ступень усиления может включать в себя транзисторы, имеющие допустимый предел напряжения питания ввода-вывода (IO). Матрица памяти может включать в себя транзисторы, имеющие допустимый предел напряжения питания, который меньше, чем допустимый предел напряжения питания IO. В частном варианте осуществления первая ступень усиления может быть усилителем 112, а матрица памяти может быть матрицей 102 памяти по фиг.1. В другом частном варианте осуществления первая ступень усиления может быть первым усилителем 202, а матрица памяти может быть матрицей 204 памяти фиг.2. В другом частном варианте осуществления первая ступень усиления может быть первой ступенью 302 усиления, а матрица памяти может быть матрицей 304 памяти по фиг.3.

Продолжая к этапу 404, управляющее напряжение может быть приложено к фиксирующему транзистору, соединенному с матрицей памяти для установления напряжения матрицы памяти так, что напряжение матрицы памяти меньше, чем допустимый предел напряжения питания ядра. Например, управляющее напряжение Vclamp может быть приложено к фиксирующим транзисторам 218, 248 и 278, соединенным с матрицей 204 памяти для установления напряжения в узлах 220, 250 и 280 так, что напряжение матрицы памяти меньше, чем допустимый предел напряжения питания ядра так, как проиллюстрировано на фиг.2. В частном варианте осуществления управляющее напряжение Vclamp может быть приложено к фиксирующему транзистору 318, 348, 378, соединенному с матрицей 304 памяти для установления напряжения Vop (фиг.1) матрицы памяти так, что напряжение Vop матрицы памяти меньше, чем допустимый предел Vlimit напряжения питания ядра, как проиллюстрировано на фиг.3. Одно последствие неуправляемого Vclamp в том, что напряжение матрицы памяти может превысить допустимый предел напряжения питания ядра, что является причиной отказа устройств ядра в матрице памяти.

Двигаясь к этапу 406, операция чтения данных может быть выполнена в ячейке хранения данных матрицы памяти для генерации сигнала данных в первом усилителе. В частном варианте осуществления операция чтения данных может быть выполнена в ячейке 226 хранения данных матрицы 204 памяти для генерации сигнала данных в первом усилителе 202, используя тракт 210 чтения данных, так как проиллюстрировано на фиг.2. В частном варианте осуществления операция чтения данных может быть выполнена в одной из ячеек 326 памяти матрицы 304 памяти для генерации сигнала данных на первой ступени 302 усиления, используя один из трактов 310 чтения данных, так, как проиллюстрировано на фиг.3.

Переходя к этапу 408, сигнал данных от первой ступени усиления может быть сравнен с опорным сигналом для генерации выходного сигнала во второй ступени усиления. Вторая ступень усиления может включать в себя устройства, имеющие допустимый предел напряжения питания. В частном варианте осуществления сигнал данных от первой ступени 302 усиления может быть сравнен с опорным сигналом для генерации выходного сигнала Vout во второй ступени 312 усиления, причем опорный сигнал генерируется, используя первый опорный тракт 340 и второй опорный тракт 370, так, как проиллюстрировано на фиг.3. В частном варианте осуществления вторая ступень 312 усиления может включать в себя устройства, имеющие допустимый предел напряжения питания ядра, так, как проиллюстрировано на фиг.3.

В частном варианте осуществления ячейка хранения данных может быть соединена с первым фиксирующим транзистором через избирательный транзистор для того, чтобы дать возможность току протекать от источника напряжения первого усилителя через ячейку хранения данных. Например, ячейка 226 хранения данных может быть соединена с первым фиксирующим транзистором 218 через избирательный транзистор, такой как первый MUX-транзистор 224 для того, чтобы дать возможность току протекать от источника 206 напряжения первого усилителя 202 через ячейку 226 хранения данных, так как проиллюстрировано на фиг.2. В качестве другого примера одна из ячеек 326 памяти может быть соединена с первым фиксирующим транзистором 318 через избирательный транзистор, такой как один соответствующий из MUX-транзисторов для того, чтобы дать возможность току протекать от источника напряжения первой ступени 302 усиления через соответствующую одну из ячеек 326 памяти, как проиллюстрировано на фиг.3. В этих частных вариантах осуществления избирательный транзистор, такой как первый MUX-транзистор 224 и/или MUX-транзисторы 324, может иметь допустимый предел Vlimit напряжения питания ядра. В этих частных вариантах осуществления увеличение подачи напряжения Vamp первого усилителя 202 и/или первой ступени 302 усиления увеличивает границу чтения операции чтения данных.

Специалисты, кроме того, могли бы принять во внимание, что различные иллюстративные логические блоки, конфигурации, модули, схемы и этапы алгоритмов, описанные в связи с вариантами осуществления, раскрытыми в материалах настоящей заявки, могут быть реализованы в виде электронных аппаратных средств, компьютерного программного обеспечения или сочетания обоих. Квалифицированные специалисты могут реализовать описанные функциональные возможности отличающимися способами для каждого конкретного применения, но такие реализационные решения не должны интерпретироваться в качестве служащих причиной выхода из объема настоящего изобретения.

Этапы способа или алгоритма, описанные в связи с вариантами осуществления, раскрытыми в материалах настоящей заявки, могут быть воплощены непосредственно в аппаратных средствах, в программном модуле, выполняемом процессором, или в сочетании этих двух. Программно реализованный модуль может находиться в оперативном запоминающем устройстве (ОЗУ, RAM), флэш-памяти, постоянном запоминающем устройстве (ПЗУ, ROM), программируемом постоянном запоминающем устройстве (ППЗУ, PROM), стираемом программируемом постоянном запоминающем устройстве (СППЗУ, EPROM), электрически стираемом и программируемом постоянном запоминающем устройстве (ЭСППЗУ, EEPROM), регистрах, жестком диске, съемном диске, постоянном запоминающем устройстве на компакт-диске (CD-ROM) или любом другом виде запоминающего носителя, известном в данной области техники. Примерный запоминающий носитель соединяют с процессором так, что процессор может считывать информацию с и записывать информацию на запоминающий носитель. В альтернативном варианте запоминающий носитель может быть интегральным по отношению к процессору. Процессор и запоминающий носитель могут находиться в специализированной интегральной схеме (ASIC). ASIC может находиться в вычислительном устройстве или пользовательском терминале. В альтернативном варианте процессор и запоминающий носитель могут находиться в виде дискретных компонентов в вычислительном устройстве или пользовательском терминале.

Предшествующее описание раскрытых вариантов осуществления предоставлено, чтобы дать любому специалисту в данной области техники возможность изготовить или использовать раскрытые варианты осуществления. Различные модификации по отношению к этим вариантам осуществления будут легко очевидны специалистам в данной области техники, а общие принципы, определенные в материалах настоящей заявки, могут быть применены к другим вариантам осуществления, не выходя из объема изобретения. Таким образом, настоящее изобретение не имеет намерением быть ограниченным вариантами осуществления, показанными в материалах настоящей заявки, а должно удовлетворять самому широкому объему, по возможности согласующемуся с принципами и новейшими признаками, определенными следующей формулой изобретения.

Изобретение относится к вычислительной технике. Технический результат заключается в улучшении производительности чтения усилителя считывания MRAM. Запоминающее устройство, содержащее ячейку памяти, включающую в себя основанный на сопротивлении элемент памяти, соединенный с входным транзистором, причем входной транзистор имеет первую толщину оксида так, чтобы дать возможность работы ячейки памяти при рабочем напряжении; и первый усилитель, выполненный с возможностью приложения напряжения питания к ячейке памяти, которое больше, чем предел напряжения для генерации сигнала данных на основе тока через ячейку памяти, в котором первый усилитель включает в себя фиксирующий транзистор, который имеет вторую толщину оксида, которая больше, чем первая толщина оксида, и в котором фиксирующий транзистор выполнен с возможностью предотвращать превышение предела напряжения рабочим напряжением в ячейке памяти. 3 н. и 17 з.п. ф-лы, 4 ил.

1. Запоминающее устройство, содержащее:

ячейку памяти, включающую в себя основанный на сопротивлении элемент памяти, соединенный с входным транзистором, причем входной транзистор имеет первую толщину оксида так, чтобы дать возможность работы ячейки памяти при рабочем напряжении; и

первый усилитель, выполненный с возможностью приложения напряжения питания к ячейке памяти, которое больше, чем предел напряжения, для генерации сигнала данных на основе тока через ячейку памяти,

в котором первый усилитель включает в себя фиксирующий транзистор, который имеет вторую толщину оксида, которая больше, чем первая толщина оксида, и в котором фиксирующий транзистор выполнен с возможностью предотвращать превышение предела напряжения рабочим напряжением в ячейке памяти.

2. Запоминающее устройство по п.1, в котором входной транзистор имеет конфигурацию устройства ядра и в котором фиксирующий транзистор имеет конфигурацию устройства ввода/вывода (IO).

3. Запоминающее устройство по п.2, в котором фиксирующий транзистор выполнен с возможностью работать при напряжении питания ввода/вывода (IO) и в котором входной транзистор выполнен с возможностью работать при напряжении питания ядра.

4. Запоминающее устройство по п.3, в котором напряжение питания ядра равно приблизительно 1 В и в котором напряжение питания IO равно приблизительно 1,8 В.

5. Запоминающее устройство по п.1, в котором ячейка памяти является ячейкой магниторезистивной оперативной памяти с передачей спинового вращательного момента (STT-MRAM).

6. Запоминающее устройство по п.1, в котором первый усилитель дополнительно выполнен с возможностью приложения, по меньшей мере, к одной опорной ячейке напряжения питания для генерации опорного сигнала, и дополнительно содержащее:

второй усилитель, соединенный с первым усилителем и выполненный с возможностью предоставлять выходной сигнал на основе разницы между сигналом данных и опорным сигналом, причем второй усилитель включает в себя, по меньшей мере, один транзистор, который имеет первую толщину оксида и к которому приложено второе напряжение питания, которое не превосходит предел напряжения.

7. Запоминающее устройство по п.1, в котором первый усилитель дополнительно содержит:

первый нагрузочный транзистор, соединенный с фиксирующим транзистором для генерации сигнала данных;

второй нагрузочный транзистор, соединенный со вторым фиксирующим транзистором; и

третий нагрузочный транзистор, соединенный с третьим фиксирующим транзистором, причем второй фиксирующий транзистор и третий фиксирующий транзистор выполнены с возможностью соединяться с первой опорной ячейкой и со второй опорной ячейкой для генерации опорного сигнала,

в котором фиксирующий транзистор, второй фиксирующий транзистор, третий фиксирующий транзистор, первый нагрузочный транзистор, второй нагрузочный транзистор и третий нагрузочный транзистор имеют конфигурацию устройства ввода/вывода (IO), и в котором, по меньшей мере, один транзистор каждой ячейки памяти, первой опорной ячейки и второй опорной ячейки имеет конфигурацию устройства ядра.

8. Запоминающее устройство, содержащее:

тракт чтения данных, включающий в себя первое нагрузочное устройство, соединенное с ячейкой хранения данных через первый фиксирующий транзистор, причем первое нагрузочное устройство имеет конфигурацию первого устройства для работы при первом напряжении питания, ячейка хранения данных включает в себя входной транзистор, имеющий конфигурацию второго устройства для работы при напряжении, не превышающем предел напряжения, который меньше, чем первое напряжение питания, в котором первый фиксирующий транзистор имеет толщину оксида больше, чем толщина оксида входного транзистора, и в котором на управляющий вывод первого фиксирующего транзистора подается напряжение смещения для предотвращения превышения предела напряжения напряжением в ячейке хранения данных.

9. Запоминающее устройство по п.8, в котором конфигурация второго устройства является конфигурацией устройства ядра.

10. Запоминающее устройство по п.9, в котором конфигурация первого устройства является конфигурацией устройства ввода/вывода (IO).

11. Запоминающее устройство по п.10, в котором конфигурация устройства ядра имеет меньшие физические размеры, чем конфигурация устройства IO.

12. Запоминающее устройство по п.8, в котором предел напряжения равен приблизительно одному вольту.

13. Запоминающее устройство по п.8, дополнительно содержащее:

первый опорный тракт, включающий в себя второе нагрузочное устройство, соединенное с первой опорной ячейкой; и

второй опорный тракт, включающий в себя третье нагрузочное устройство, соединенное со второй опорной ячейкой,

в котором второе нагрузочное устройство и третье нагрузочное устройство имеют конфигурацию первого устройства и в котором первая опорная ячейка и вторая опорная ячейка каждая включает в себя, по меньшей мере, один транзистор, имеющий конфигурацию второго устройства.

14. Запоминающее устройство по п.13, дополнительно содержащее:

второй фиксирующий транзистор для предотвращения превышения предела напряжения вторым напряжением в первой опорной ячейке и

третий фиксирующий транзистор для предотвращения превышения предела напряжения третьим напряжением в первой опорной ячейке.

15. Запоминающее устройство по п.14, дополнительно содержащее:

первое устройство избирательного переключателя в тракте чтения данных для выборочного соединения ячейки хранения данных с первым фиксирующим транзистором;

второе устройство избирательного переключателя, подсоединенное между вторым фиксирующим транзистором и первой опорной ячейкой; и

третье устройство избирательного переключателя, подсоединенное между третьим фиксирующим транзистором и второй опорной ячейкой,

в котором каждое из первого устройства избирательного переключателя, второго устройства избирательного переключателя и третьего устройства избирательного переключателя имеет конфигурацию второго устройства.

16. Способ работы запоминающего устройства, содержащий этапы, на которых:

соединяют первую ступень усиления с матрицей памяти, причем первая ступень усиления включает в себя транзисторы, имеющие допустимый предел напряжения питания ввода/вывода (IO), матрица памяти включает в себя транзисторы, имеющие допустимый предел напряжения питания ядра, который меньше, чем допустимый предел напряжения питания IO; и

прикладывают управляющее напряжение на фиксирующем транзисторе, соединенном с матрицей памяти для установки напряжения матрицы памяти так, что напряжение матрицы памяти меньше, чем допустимый предел напряжения питания ядра, причем толщина оксида фиксирующего транзистора больше, чем толщина оксида транзисторов, включенных в матрицу памяти.

17. Способ по п.16, дополнительно содержащий этапы, на которых:

выполняют операцию чтения данных в ячейке хранения данных матрицы памяти для генерации сигнала данных в первой ступени усиления; и сравнивают сигнал данных из первой ступени усиления с опорным сигналом для генерации выходного сигнала во второй ступени усиления, причем вторая ступень усиления включает в себя устройства, имеющие допустимый предел напряжения питания ядра.

18. Способ по п.17, дополнительно содержащий этап, на котором соединяют ячейку хранения данных с фиксирующим транзистором через избирательный транзистор, чтобы дать возможность току протекать от источника напряжения первой ступени усиления через ячейку хранения данных.

19. Способ по п.18, в котором избирательный транзистор имеет допустимый предел напряжения питания ядра.

20. Способ по п.18, в котором увеличение подачи напряжения первой ступени усиления превышает границу чтения операции чтения данных.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 6999345 В1, 14.02.2006 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2013-02-27—Публикация

2009-09-01—Подача