Предлагаемое изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам радиочастотных идентификационных устройств, и может быть использовано преимущественно для записи индивидуального кода микросхемы радиочастотного идентификатора путем занесения заряда на плавающий затвор элементов памяти постоянного запоминающего устройства (ПЗУ).

В настоящее время устройства радиочастотной идентификации находят все большее применение, например, в сфере здравоохранения, страхования, транспортной сфере, в области торговли как платежные средства, так и средства идентификации товара и в других областях. Каждое радиочастотное идентификационное устройство должно нести уникальный информационный код. Поэтому основной проблемой при производстве микросхем радиочастотной идентификации является запись индивидуального кода в постоянное запоминающее устройство. Интегральные микросхемы радиочастотного идентификатора должны иметь минимальное количество элементов и внешних выводов, а также реализовывать возможность записи индивидуального кода не только групповым или индивидуальным способом, но и в собранном виде.

Известны многочисленные устройства радиочастотной идентификации [1] серий Н4002, Н4100, Н4200 фирмы ЕМ MICROELECTRONIC-MARIN SA [СН] и бесконтактная интегральная микросхема идентификатора [2] Т5557 фирмы ATMEL CORP [US], использующих лазерное пережигание плавких перемычек постоянного запоминающего устройства.

Однако запись индивидуального кода путем лазерного пережигания плавких перемычек ПЗУ каждого кристалла идентификатора требует использования дорогостоящего оборудования и больших временных затрат, а также не реализует возможность записи индивидуального кода в собранном устройстве.

Известны также устройство бесконтактной идентификации [3] 4100D фирмы ОАО «НИИМЭ и завод Микрон» [RU] и интегральная микросхема индукционного преобразователя [4] КБ5004ХК2-4,5 фирмы ОАО «Ангстрем» [RU], в которых запись информации в ПЗУ производится путем электрического пережигания плавких перемычек.

Однако бесконтактные идентификационные устройства данного типа обладают рядом недостатков по отношению к заявленному изобретению:

- в цепи пережигания каждой плавкой перемычки используются два мощных адресных транзистора с шириной канала более 100 мкм;

- в процессе программирования при пережигании через перемычку и, соответственно, через цепи микросхемы протекают большие токи (более 20 миллиампер), что требует применения мощных элементов и защиты от перегрузок;

- программирование индивидуального кода возможно только в процессе тестирования кристаллов на пластине.

Наиболее близким к заявленному изобретению является гибридная интегральная схема [5], состоящая из платы, ячеек памяти, расположенных на плате для хранения данных, контактной площадки, расположенной на плате и использующей напряжение первого типа для записи данных в ячейки памяти, внешний контактирующий терминал, подключенный к плате и использующий напряжение второго типа для чтения данных из ячеек памяти, и схемы электропитания, предназначенной для обеспечения ячеек памяти упомянутым напряжением первого или второго типа посредством (p-n-p транзистора, эмиттер которого подключен к шине питания с напряжением второго типа, коллектор которого подключен к шине питания с напряжением первого типа, база которого подключена к узлу резистивного делителя), p-канального МОП-транзистора, затвор которого подключен к шине питания с напряжением первого типа, исток которого через резистор подключен к шине питания с напряжением второго типа, затвор которого подключен к узлу резистивного делителя, находящегося между двумя внешними резисторами, предназначенными для деления напряжения.

Прототип работает следующим образом: в режиме записи внешнее напряжение с вывода через открытый p-n-p транзистор поступает на шину высоковольтного питания Vpp, при этом p-канальный МОП-транзистор (p-n-p транзистор) закрыт и низковольтное напряжение Vdd поступает в схему с внешнего вывода. В режиме чтения из ЭППЗУ, когда внешнее высокое напряжение на вывод не подается, p-n-p транзистор закрыт, а p-канальный МОП транзистор (p-n-p транзистор) открывается и передает внешнее напряжение Vdd на шину Vpp.

К недостаткам этого устройства можно отнести следующие:

- необходимость использования 2-х источников питания,

- необходимость использования сложной БиКМОП технологии,

- использование 2-х дополнительных внешних резисторов.

Задача, на решение которой направлено заявленное изобретение, заключается в том, чтобы обеспечить запись индивидуального кода в блок ЭППЗУ радиочастотного идентификационного устройства с использованием минимального количества элементов и наименьшим количеством дополнительных выводов микросхемы.

Технический результат заявленного изобретения заключается в значительном уменьшении размеров кристалла интегральной микросхемы радиочастотного идентификатора, а также возможности записи индивидуального кода в блок ЭППЗУ после того, когда микросхема собрана в радиочастотный идентификатор и к ней подключен антенный контур.

Данный технический результат достигается тем, что интегральная микросхема радиочастотного идентификатора, выполненная на подложке из полупроводникового материала, состоящая из контактных площадок (2, 3), которые предназначены для подключения к резонансному антенному контуру, к упомянутой контактной площадке (2) подключены стоки n-канальных МОП-транзисторов (7), (9), (11) и затвор n-канального МОП-транзистора (8), к упомянутой контактной площадке (3) подключены стоки n-канальных МОП-транзисторов (8), (10), (12) и затвор n-канального МОП-транзистора (7), истоки упомянутых n-канальных МОП- транзисторов (7, 8) подключены к шине земли (⊥) (18), истоки диодно-включенных МОП-транзисторов (11, 12) подключены к шине положительного питания (+Еп) (19), а истоки диодно-включенных n-канальных транзисторов (9 и 10) подключены к контактной площадке (1), МОП-транзисторы с плавающим затвором запоминающих элементов (13), стоки которых подключены к входу модулятора (20), истоки которых подключены к стокам адресных n-канальных МОП-транзисторов (14), затворы которых подключены к входам дешифраторов строк (16), а истоки подключены стоками адресных n-канальных МОП-транзисторов (15), затворы которых подключены к входам дешифраторов столбцов (16), а истоки подключены к шине земли (⊥) (18), согласно изобретению с целью записи индивидуального кода интегральной микросхемы радиочастотного идентификатора к контактной площадке (1) подключены управляющие затворы упомянутых МОП-транзисторов с плавающим затвором запоминающих элементов (13) и исток p-канального МОП- транзистора (4), затвор которого подключен к шине питания (+Еп) (19), а сток подключен к стоку диодно-смещенного n-канального транзистора (5), исток которого подключен к стоку упомянутого МОП-транзистора с плавающим затвором запоминающего элемента (13), к входу модулятора (20) и к стоку диодно-включенного n-канального транзистора (6), исток которого подключен к шине положительного питания (+Еп) (19).

Таким образом, для реализации возможности записи индивидуального кода в ЭППЗУ интегральной микросхемы радиочастотного идентификатора требуется ввести в схему три дополнительных транзистора (4, 5, 6) и дополнительный вывод (1), при этом существенно уменьшаются геометрические размеры элементов ПЗУ из-за уменьшения токов записи.

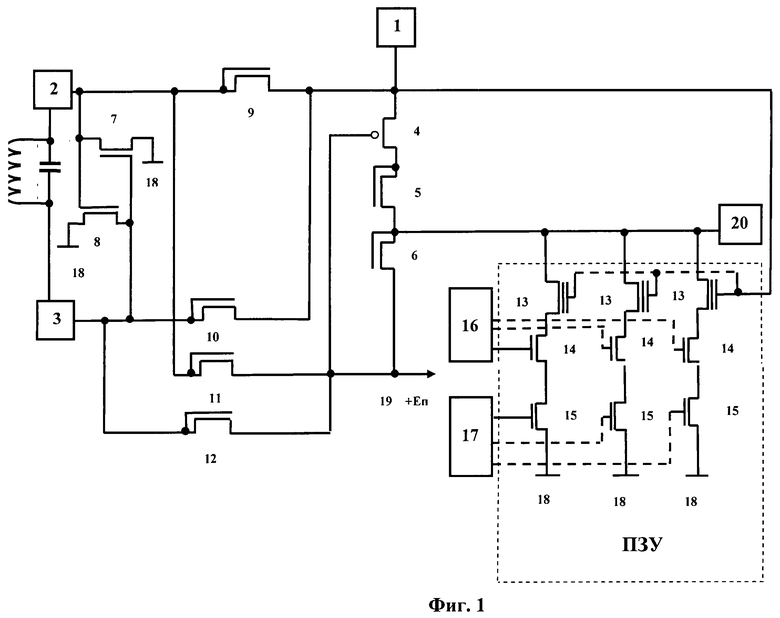

Предлагаемое изобретение поясняется фиг.1, где изображена принципиальная схема устройства программирования информации для интегральной микросхемы радиочастотного идентификатора.

Заявляемое устройство состоит из контактной площадки (1), связанной с управляющими затворами МОП-транзисторов с плавающим затвором запоминающих элементов (13), с истоком p-канального МОП транзистора (4), с истоками диодно-включенных n-канальных транзисторов (9 и 10), сток p-канального МОП-транзистора (4) связан со стоком диодно-включенного n-канального транзистора (5), исток которого связан со стоком МОП-транзистора с плавающим затвором запоминающего элемента (13), со входом модулятора (20) и со стоком диодно-включенного n-канального транзистора (6), исток которого подключен к шине положительного питания (+Еп) (19). Затвор p-канального МОП-транзистора (4) подключен к шине положительного питания (19). Выводы контактных площадок (2 и 3) подключены к резонансному антенному контуру. Вывод (2) связан со стоками n-канальных МОП-транзисторов (7), (9), (11) и затвором транзистора (8), вывод (3) связан со стоками n-канальных МОП-транзисторов (8), (10), (12) и затвором транзистора (7). Стоки транзисторов (7) и (8) подключены к шине земли (⊥) (18), стоки диодно-включенных МОП-транзисторов (11 и 12) подключены к шине положительного питания (+Еп) (19). Истоки МОП-транзисторов с плавающим затвором запоминающих элементов (13) связаны со стоками адресных n-канальных МОП-транзисторов (14), истоки которых связаны со стоками адресных n-канальных МОП-транзисторов (15). Истоки транзисторов (15) подключены к шине земли (⊥) (18). Затворы транзисторов (14) и(15) подключены к выходам дешифраторов строк (16) и столбцов (17) соответственно.

Устройство работает следующим образом.

В режиме чтения информации по радиоканалу, когда вывод (1) отключен, а на выводы (2 и 3) поступает синусоидальный сигнал из антенного контура, на шине положительного питания (19) и на управляющих затворах запоминающих элементов (13) через диодно-включенные транзисторы (9, 10, 11, 12) поступают одинаковые уровни напряжения, благодаря чему p-канальный МОП транзистор (4) запирается и стоки запоминающих элементов (13) отключаются от всех элементов, кроме входа модулятора. В зависимости от уровня порогового напряжения запоминающего элемента (13) на входе модулятора по определенному адресу (выводы 16 и 17) формируется логический уровень «нуля» или «единицы», который после преобразования передается модулятором в антенный контур.

В режиме программирования при подаче на вывод (1) положительного напряжения относительно шины земли (18) при отсутствии тока в антенном контуре микросхема автоматически переходит в режим программирования, т.к. напряжение питания (19) всегда ниже напряжения, подаваемого на вывод (1), за счет падения напряжения на диодно-смещенных транзисторах (5) и (6), и p-канальный транзистор (4) открывается. Напряжение с вывода (1) поступает на управляющие затворы запоминающих МОП-транзисторов с плавающим затвором (13), и через открытые p-канальный транзистор (4) и диодно-смещенный n-канальный транзистор (5) на стоки запоминающих транзисторов (13) и далее через диодно-смещенный n-канальный транзистор (6) на шину питания (19). Если по данному адресу, определяемому состоянием дешифраторов строк (16) и столбцов (17), транзисторы 14 и 15 открываются, то через канал транзистора (13) протекает ток. Если напряжение на выводе (1) составляет от 12 до 14 вольт, то при протекании тока через канал транзистора (13) происходит захват «горячих» электронов на плавающий затвор, пороговое напряжение n-канального транзистора (13) увеличивается с +0,5 вольт до 4÷5 вольт и запоминающий элемент переходит в состояние логической единицы. Если же напряжение, подаваемое на вывод (1), составляет от 4 до 6 вольт, протекание тока через канал транзистора (13) не обеспечивает формирование и захват «горячих» электронов и запоминающий элемент остается в исходном состоянии логического нуля.

Источники информации

1. Информационный биллютень №Rev. В, 10/09 фирмы ЕМ MICROELECTRONIC-MARIN SA [СН] для изделий серии ЕМ4200.

2. Описание №4517J1-RFID-03/06 фирмы ATMEL CORP [US] на изделие №Т5557 «Мультифункциональная 330-битная бесконтактная интегральная микросхема идентификатора с функциями чтения и записи».

3. Описание №557 фирмы ОАО «НИИМЭ и Микрон» [RU] на изделие №4100D «Интегральная микросхема RFID метки», май 2010 г.

4. Индукционный преобразователь КБ5004ХК2-4,5, свидетельство о регистрации топологии №2011630007 зарегистрировано в реестре топологий интегральных микросхем 11.01.2011 г. Авт. Гуминов В.Н., Абрамов С.Н., Тюрина О.Н.

5. Hibrid integrated circuit device (Патент Японии № JP 10069792, дата публикации 10.03.1998 г., МПК G11C 7/00, Авт. NUMAZAKI KOJI [JP]; KOYASU TAKAHISA [JP]; BAN HIROYUKI [JP], также опубликован как патент США № US 5889722 от 30.03.1999 г.).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КНС (КРЕМНИЙ НА САПФИРЕ), КНИ (КРЕМНИЙ НА ИЗОЛЯТОРЕ) СТРУКТУРАХ | 2011 |

|

RU2467431C1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ЭЛЕКТРИЧЕСКИ СТИРАЕМАЯ И ПРОГРАММИРУЕМАЯ ЭНЕРГОНЕЗАВИСИМАЯ НАКОПИТЕЛЬНАЯ ЯЧЕЙКА | 1996 |

|

RU2168242C2 |

| ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2014 |

|

RU2560822C1 |

| ИСТОЧНИК СТАБИЛЬНОГО ТОКА ИЛИ НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 2022 |

|

RU2795478C1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

Изобретение относится к интегральным микросхемам радиочастотных идентификационных устройств. Техническим результатом является обеспечение уменьшения размеров кристалла интегральной микросхемы радиочастотного идентификатора, а также возможности записи индивидуального кода в блок элементов памяти постоянного запоминающего устройства. Устройство содержит вывод контактной площадки (1), связанный с управляющими затворами МОП-транзисторов с плавающим затвором запоминающих элементов (13), с истоками диодно-включенных n-канальных транзисторов (9 и 10), р-канального МОП транзистора (4), сток которого связан со стоком диодно-включенного n-канального транзистора (5), исток которого связан со стоком транзистора (13), со входом модулятора (20) и со стоком диодно-включенного n-канального транзистора (6), исток которого и затвор транзистора (4) подключены к шине положительного питания (+Еп) (19). Выводы контактных площадок (2 и 3) подключены к резонансному антенному контуру. Вывод (2) связан со стоками транзисторов (7), (9), (11) и затвором транзистора (8), вывод (3) связан со стоками транзисторов (8), (10), (12) и затвором транзистора (7). Стоки транзисторов (11 и 12) подключены к шине положительного питания (+Еп) (19). Истоки транзисторов (13) связаны со стоками адресных n-канальных МОП-транзисторов (14), истоки которых связаны со стоками адресных n-канальных МОП-транзисторов (15), истоки которых и стоки транзисторов (7) и (8) подключены к шине земли (⊥) (18). Затворы транзисторов (14) и (15) подключены к выходам дешифраторов строк (16) и столбцов (17) соответственно. 1 ил.

Интегральная микросхема радиочастотного идентификатора, выполненная на подложке из полупроводникового материала, состоящая из контактных площадок (2, 3), которые предназначены для подключения к резонансному антенному контуру, к упомянутой контактной площадке (2) подключены стоки n-канальных МОП-транзисторов (7), (9), (11) и затвор n-канального МОП-транзистора (8), к упомянутой контактной площадке (3) подключены стоки n-канальных МОП-транзисторов (8), (10), (12) и затвор n-канального МОП-транзистора (7), истоки упомянутых n-канальных МОП-транзисторов (7, 8) подключены к шине земли (⊥) (18), истоки диодно-включенных МОП-транзисторов (11, 12) подключены к шине положительного питания (+Еп) (19), а истоки диодно-включенных n-канальных транзисторов (9, 10) подключены к контактной площадке (1), МОП-транзисторы с плавающим затвором запоминающих элементов (13), стоки которых подключены к входу модулятора (20), истоки которых подключены к стокам адресных n-канальных МОП-транзисторов (14), затворы которых подключены к входам дешифраторов строк (16), а истоки подключены стоками адресных n-канальных МОП-транзисторов (15), затворы которых подключены к входам дешифраторов столбцов (17), а истоки подключены к шине земли (⊥) (18), отличающаяся тем, что, с целью записи индивидуального кода интегральной микросхемы радиочастотного идентификатора, к контактной площадке (1) подключены управляющие затворы МОП-транзисторов с плавающим затвором запоминающих элементов (13), исток р-канального МОП транзистора (4), затвор которого подключен к шине положительного питания (+Еп) (19), а сток подключен к стоку диодно-смещенного n-канального транзистора (5), исток которого подключен к стокам упомянутых МОП-транзисторов с плавающим затвором запоминающего элемента (13), к входу модулятора (20) и к стоку диодно-включенного n-канального транзистора (6), исток которого подключен к шине положительного питания (+Еп) (19).

| JP 10069792 А, 10.03.1998 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| БЕСПРОВОДНОЕ УСТРОЙСТВО НА ИНТЕГРАЛЬНОЙ СХЕМЕ И КОМПОНЕНТ БЕСПРОВОДНОГО УСТРОЙСТВА НА ИНТЕГРАЛЬНОЙ СХЕМЕ | 2007 |

|

RU2378746C1 |

| РАДИОПРИЕМНИК ДЛЯ ПРИЕМА ВЫСОКОЧАСТОТНОГО СИГНАЛА | 1994 |

|

RU2123236C1 |

Авторы

Даты

2012-10-27—Публикация

2011-11-01—Подача