Изобретение относится к области микроэлектроники, в частности к радиационно-стойким энергонезависимым программируемым логическим интегральным схемам, программируемым логическим матрицам и запоминающим устройствам с элементами программирования на основе электрического разрушения диэлектрика.

Конструкция программируемых логических интегральных схем и программируемых логических матриц включает в себя функциональные (логические) блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек (элементов), в которой программируемые ячейки конфигурационной матрицы могут быть выполнены на основе триггеров, электрически стираемых перепрограммируемых постоянных запоминающих устройств (EEPROM), перемычек типа antifuse (Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Петербург, 2004. - 394-425 с.[1]). Перемычки типа antifuse, представляют собой структуру, содержащую два электрода, разделенных диэлектриком, а программирование перемычки типа antifuse основано на электрическом разрушении (пробое) диэлектрика при котором создается проводящий канал и электроды перемычек antifuse замыкаются.

В программируемых логических интегральных схемах, в которых программируемые ячейки конфигурационной матрицы выполнены на основе триггеров, программируемые ячейки управляют состоянием ключей, задающих конфигурацию межсоединений формируемой схемы. Достоинством таких интегральных схем является возможность многократного перепрограммирования конфигурационной матрицы, что значительно облегчает процесс разработки проекта. Недостатком таких программируемых логических интегральных схем является то, что они не являются энергонезависимыми, так как при отключении питания теряются данные, записанные в программируемые ячейки конфигурационной матрицы.

Энергонезависимыми являются программируемые логические интегральные схемы, конфигурационная матрица которых состоит из программируемых ячеек на базе элементов с накоплением заряда EEPROM, так как при отключении напряжения питания данные, хранящиеся в программируемых ячейках конфигурационной матрицы, не теряются. Недостатком таких программируемых ячеек является низкая радиационная стойкость.

Энергонезависимые программируемые логические интегральные схемы, в которых программируемые ячейки представляют собой перемычки типа antifuse и содержат два электрода, разделенных диэлектриком, имеют высокую радиационную стойкость. Программирование ячеек основано на электрическом разрушении (пробое) диэлектрика при котором создается проводящий канал и электроды перемычек antifuse замыкаются. Такая однократно программируемая ячейка сохраняет свое состояние при отключении напряжения питания и является радиационно стойкой. Недостатком данной конструкции программируемой логической интегральной схемы является то, что программируемые ячейки позволяют выполнить только однократное программирование конфигурационной матрицы. Кроме того, перемычки типа antifuse, в отличие от микросхем с конфигурационной матрицей на основе триггерных программируемых ячеек, расположены непосредственно на пересечении шин межсоединений и при программировании замыкают их. Поэтому конечное сопротивление перемычек antifuse влияет на сопротивление межсоединений.

Такие недостатки, за счет формирования программируемых ячеек конфигурационной матрицы на основе комбинации триггерной ячейки памяти и перемычек типа antifuse устраняет конструкция программируемой логической интегральной схемы, описанная в патенте США №5426614 «Метогу cell with programmable antifuse technology)) МПК G11C 17/16, 1995 г. [2], являющаяся наиболее близкой по технической сути и достигаемому результату к заявляемой.

Данная радиационно-стойкая энергонезависимая программируемая логическая интегральная схема включает функциональные блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек, схема программируемой ячейки которой представлена на фиг.1. Программируемая ячейка содержит первый инвертор 1, состоящий из подключенного истоком к шине питания Vdd p-канального транзистора 2 и подключенного истоком к шине с потенциалом земли Gnd n-канального транзистора 3, соединенные затворы которых являются входом 4 первого инвертора 1, соединенные стоки являются выходом 5 первого инвертора 1, который подключен ко входу второго инвертора 6, состоящего из подключенного истоком к шине питания Vdd p-канального транзистора 7 и подключенного истоком к шине земли Gnd n-канального транзистора 8, соединенные затворы которых являются входом 5 второго инвертора 6, соединенные стоки являются выходом 4 второго инвертора 6, который подключен ко входу инвертора 1. Ячейка содержит первую 9 и вторую 10 перемычки antifuse, которые включают первые 11, 12 и вторые 13, 14 электроды, соответственно. Первый электрод 11 перемычки antifuse 9 подключен к шине питания Vdd, второй электрод 13 перемычки antifuse 9 подключен к выходу 5 инвертора 1, входу инвертора 6 и второму электроду 14 перемычки antifuse 10, первый электрод 12 перемычки antifuse 10 подключен к шине земли Gnd. Вход 4 первого инвертора 1 и выход второго инвертора 6 соединены со стоком первого адресного транзистора 15, исток которого подключен к первой разрядной шине 16. Вход 5 второго инвертора 6, выход 5 инвертора 1 и электроды 13, 14 перемычек antifuse 9, 10, соответственно, подключены к стоку второго адресного транзистора 17, исток которого подключен ко второй разрядной шине 18. Затворы адресных транзисторов 15, 17 подключены к адресной шине 19.

Программируемые ячейки объединяются в конфигурационную матрицу ячеек, в которой строки формируются программируемыми ячейками, объединенными адресными шинами 19, подключенными к затворам транзисторов 15, 17, а столбцы формируются программируемыми ячейками, объединенными разрядными шинами 16 и 18, подключенными к истокам транзисторов 15, 17, соответственно. Логическое состояние программируемых ячеек конфигурационной матрицы определяет состояние (проводящее или не проводящее), в котором находятся ключи, задающие конфигурацию межсоединений формируемой схемы. Ключи известным образом подключены к выходу первого инвертора и второго инвертора программируемой ячейки.

Такая программируемая логическая интегральная схема имеет следующие режимы функционирования: режим отладки проекта с возможностью многократной перезаписи конфигурационной матрицы, режим однократного программирования конфигурационной матрицы микросхемы в соответствии с разработанным проектом и рабочий режим, в котором функционирование программируемой логической интегральной схемы задается однократно запрограммированной конфигурационной матрицей.

Для записи данных в программируемую ячейку на разрядную шину 16 подается потенциал земли Gnd или напряжения питания Vdd, на разрядную шину 18 подается напряжение питания Vdd или потенциал земли Gnd, соответственно, на затворы 19 адресных транзисторов 15, 17 подается напряжение питания Vdd, которое переводит транзисторы в проводящее состояние, и ячейка переводится в состоянии логического «О» или «1». При этом на выходе 5 первого инвертора 1 устанавливается соответственно потенциал питания Vdd или земли Gnd, на выходе 4 второго инвертора 6 устанавливается соответственно потенциал земли Gnd или напряжения питания Vdd. Потенциалы на выходах 4, 5 инверторов 1, 6 управляют состоянием ключей (на фиг.1 не показаны), задающих конфигурацию межсоединений формируемой схемы. При считывании записанного в ячейке логического состояния открываются адресные транзисторы 15 и 17 и разрядные шины 16, 18 заряжаются до потенциалов в соответствии с потенциалами выходов 4, 5 инверторов 1, 6.

В процессе отладки проектов при многократном перепрограммировании ячеек конфигурационной матрицы величина напряжения на разрядных шинах 16, 18 и величина напряжения питания Vdd задаются меньшей величины, чем необходимо для пробоя диэлектрика перемычек antifuse 9, 10. При этом перемычки antifuse 9, 10 находятся в непроводящем состоянии и не влияют на процесс записи данных в программируемую ячейку и чтения данных из программируемой ячейки.

После окончания отладки конфигурации проводится однократное программирование ячейки памяти. При этом в ячейку может быть записано только одно логическое состояние - логический «0» или логическая «1».

Для однократного программирования ячейки в состояние логического «0» на вторую разрядную шину 18 подается потенциал земли Gnd, на первую разрядную шину 16, затворы 19 адресных транзисторов и шину питания Vdd, подается повышенное напряжение (напряжение программирования). При этом на выходе инвертора 1 и на вторых электродах 13, 14 перемычек antifuse 9, 10, подключенных к выходу инвертора 1, устанавливается потенциал земли Gnd. Разности потенциалов между электродами перемычки antifuse 9 становится достаточно для пробоя диэлектрика перемычки и электроды 11 и 13 замыкаются, то есть происходит программирование перемычки antifuse. Так как разность потенциалов на электродах перемычки antifuse 10 меньше напряжения пробоя диэлектрика перемычки antifuse 10, программирование перемычки 10 не происходит. Процесс однократного программирования завершается снижением напряжения на разрядной шине 16 и шине питания Vdd. Закрывают адресные транзисторы 15, 17 и, так как, электроды 11 и 13 замкнуты, на выходе 5 инвертора 1 ячейки памяти устанавливается потенциал напряжения питания Vdd, и, следовательно, на выходе инвертора 6 устанавливается потенциал земли Gnd.

Однократное программирование ячейки в состояние логической «1» проводится с помощью подачи на затворы 19 адресных транзисторов, вторую разрядную шину 18 повышенного напряжения и подачи на первую разрядную шину 16 потенциала земли Gnd. На выходе 5 инвертора 1 и на вторых электродах 13, 14 перемычек antifuse 9, 10, подключенных к выходу 5 инвертора 1 и стоку транзистора 17 устанавливается высокий потенциал, величина которого достаточна для пробоя диэлектрика перемычки antifuse 10 и электроды 12 и 14 замыкаются. При этом разность потенциалов на электродах 11, 13 перемычки antifuse 9 не достаточна для пробоя диэлектрика перемычки antifuse 9. По окончании программирования снижают напряжение на разрядной шине 18 и закрывают транзисторы 15, 17.

Таким образом, программируемая ячейка [2] позволяет реализовать как режим многократного программирования данных конфигурационной матрицы, который используется при отладке проекта, так и режим однократной записи (программирования) данных в конфигурационную матрицу микросхемы, который обеспечивает энергонезависимость микросхемы, так как при подаче потенциала земли Gnd и напряжения питания Vdd на соответствующие выводы микросхемы, за счет проводимости одной из перемычек antifuse 9 или 10, в программируемой ячейке, управляющей состоянием ключей, формирующих межсоединения программируемой логической интегральной схемы, устанавливается состояние логического «0» или логической «1». При этом перемычки antifuse не расположены непосредственно на пересечении шин межсоединений и их конечное сопротивление после программирования не влияет на сопротивление шин межсоединений.

Недостатком программируемых ячеек конфигурационной матрицы данной конструкции является сложность их технической реализации так, как при программировании ячейки в состояние логической «1» возникают повышенные токи потребления микросхем из-за прямого смещения p-n перехода стока транзистора 7 на карман p-канальных транзисторов. Кроме того, что бы избежать падения напряжения на адресном n-канальном транзисторе 17, на адресную 19 шину необходимо подавать большее напряжение, чем необходимо для пробоя перемычки antifuse 10. При программировании повышенное напряжение подается как на транзисторы программируемой ячейки, так и на управляемые ячейкой ключи, задающие конфигурацию межсоединений формируемой схемы. Это предъявляет повышенные требования к пробивному напряжению р-n переходов, изолирующих слоев топологических элементов схемы, к необходимости использования высоковольтных n- и p-канальных транзисторов, а также к необходимости задавать большую, чем необходимо для программирования, величину напряжения, что усложняет технологическую реализацию микросхемы. Необходимость формирования транзисторов программируемых ячеек конфигурационной матрицы и управляемых ячейкой ключей на основе имеющих повышенные топологические размеры высоковольтных n- и p-канальных, приводит к увеличению топологических размеров кристаллов.

Кроме того, после проведения процесса программирования, при радиационном воздействии на микросхему, программируемые ячейки, представляющие триггерную схему, могут изменить свое логическое состояние на противоположное и перейти в режим хранения такого состояния (защелкнутся). Время, необходимое для восстановления первоначального логического состояния программируемой ячейки после радиационного воздействия зависит от сопротивления перемычки antifuse, полученного после ее программирования. Чем меньше проводимость перемычки, тем больше необходимо время для восстановления логического состояния программируемой ячейки. Это обуславливает необходимость формирования запрограммированных перемычек antifuse с низким сопротивлением и требует тщательного контроля сопротивления перемычек после программирования, что также усложняет техническую реализацию конструкции.

Также недостатком конструкции [2] является то, что при программировании ячейки в состояние логического «0» на подключенные к шине питания Vdd истоки p-канальных транзисторов 2, 7 и n-карманы, в которых сформированы p-канальные транзисторы, последовательно для каждой строки матрицы ячеек подается напряжение программирования повышенной величины. При этом в программируемых ячейках, расположенных в других строках матрицы, напряжение питания Vdd должно оставаться низким, что бы избежать ошибочного программирования ячеек другой строки, поэтому n-карманы и истоки p-канальных транзисторов 2, 7 ячеек в разных строках матрицы находятся под разными потенциалами и должны быть отдалены друг от друга, что увеличивает площадь кристаллов микросхем. Кроме того, для формирования напряжения питания Vdd разной величины в соседних строках матрицы программируемых ячеек необходимо использовать буферные схемы задания напряжения для каждой строки. При программировании ячеек строки матрицы, общая для строки шина питания Vdd должна проводить значительный ток, что обуславливает необходимость использования в таких буферных схемах транзисторов с большой шириной канала. Это также снижает степень интеграции микросхем.

При однократном программировании одной из перемычек antifuse за счет проводимости запрограммированной перемычки на выходе 5 инвертора 1 может возникнуть потенциал, который приведет к пробою или снижению надежности второй перемычки antifuse. Поэтому транзисторы инвертора 1 должны поддерживать на выходе 5 инвертора напряжение, предотвращающее негативное воздействие на непрограммируемую перемычку antifuse. Это повышает требование к точности задания соотношения проводимость инвертора 1 - конечное сопротивление программируемой перемычки antifuse, что усложняет реализацию данной конструкции.

После проведения однократного программирования ячейки [2], невозможно провести повторное программирование с использованием триггеров ячейки памяти (в режиме отладки проекта) конфигурационной матрицы микросхемы для изменения логического состояния ячеек. Это ограничивает область применения ячейки.

Задачами заявляемого решения являются повышение степени интеграции кристаллов программируемых логических интегральных схем и упрощение технической реализации конструкции программируемых логических интегральных схем.

Технические результаты достигают тем, что в радиационно-стойкой энергонезависимой программируемой логической интегральной схеме, включающей функциональные блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек, программируемые ячейки конфигурационной матрицы содержат первый инвертор, состоящий из подключенного истоком к шине питания Vdd p-канального транзистора и подключенного истоком к шине земли Gnd n-канального транзистора, соединенные затворы которых являются входом первого инвертора, соединенные стоки являются выходом первого инвертора, и подключены к входу второго инвертора, состоящего из подключенного истоком к шине питания Vdd p-канального транзистора и подключенного истоком к шине земли Gnd n-канального транзистора, затворы которых являются входом второго инвертора, соединенные стоки являются выходом второго инвертора. Выходы первого и второго инвертора подключены к ключам конфигурации межсоединений. Программируемая ячейка содержит первый n-канальный транзистор управления режимом работы ячейки, исток которого подключен к выходу второго инвертора, затвор подключен к первой шине управления режимом работы ячейки, а сток подключен ко входу первого инвертора и стоку адресного транзистора, исток которого подключен к первой разрядной шине, а затвор соединен с адресной шиной. Программируемая ячейка содержит первую и вторую перемычки antifuse, каждая из которых имеет по два электрода. Первые электроды первой и второй перемычек antifuse подключены к стоку p-канального транзистора программирования перемычек antifuse, исток которого подключен к общей для всей конфигурационной матрицы шине питания программирования, а затвор к шине управления программированием перемычек antifuse. Второй электрод первой перемычки antifuse подключен к первой разрядной шине, второй электрод второй перемычки antifuse подключен ко второй разрядной шине. Первые электроды первой и второй перемычек antifuse также подключены к истоку второго n-канального транзистора управления режимом работы программируемой ячейки, затвор которого подключен к второй шине управления режимом работы программируемой ячейки, а сток ко входу первого инвертора.

Сопоставимый с прототипом анализ показывает, что новизна заявляемой конструкции состоит в том, что с целью повышения степени интеграции кристаллов радиационно-стойкой энергонезависимой программируемой логической интегральной схемы за счет снижения ограничений на расстояние между программируемыми ячейками в строках матрицы, исключения необходимости использования в триггерной части программируемых ячеек высоковольтных n- и p-канальных транзисторов и исключения необходимости использования мощных буферных схем задания напряжения программирования, упрощения технической реализации конструкции программируемых логических интегральных схем за счет снижения требований к сопротивлению перемычек antifuse и пробивным напряжениям изолирующих и диффузионных слоев, исключения падения величины программирования на стоке n-канальных адресных транзисторов и снижения токов р-n переходов при программировании, программируемые ячейки конфигурационной матрицы дополнительно содержат первый n-канальный транзистор управления режимом работы ячейки, исток которого подключен к выходу второго инвертора, сток ко входу первого инвертора, а затвор подключен к первой шине управления режимом работы ячейки, p-канальный транзистор программирования перемычек antifuse, исток которого подключен к общей для всей конфигурационной матрицы шине питания программирования, сток к первым электродам первой и второй перемычек antifuse, затвор к шине управления программированием перемычек antifuse, второй n-канальный транзистор управления режимом работы ячейки, исток которого подключен к стоку p-канального транзистора программирования перемычек antifuse и первым электродам первой и второй перемычек antifuse, затвор подключен ко второй шине управления режимом работы ячейки, сток ко входу первого инвертора, второй электрод первой перемычки antifuse подключен к первой разрядной шине, второй электрод второй перемычки antifuse подключен ко второй разрядной шине.

Формирование общей для всей конфигурационной матрицы шины программирования позволяет уменьшить площадь кристаллов микросхем, так как истоки p-канальных транзисторов задания напряжения программирования и карманы n-типа таких транзисторов для всей конфигурационной матрицы во всех режимах работы микросхемы находятся под одним и тем же потенциалом, что позволяет объединить диффузионные области истоков и n-карманов таких транзисторов в соседних ячейках и сформировать шину напряжения программирования необходимой суммарной ширины без увеличения площади кристалла и использования отдельных мощных буферных схем задания напряжения в каждой строке матрицы.

Напряжение программирования на электродах перемычек antifuse и ток программирования в каждой программируемой ячейке задается только p-канальным транзистором. При этом величина падения положительного напряжения программирования на стоке p-канального транзистора значительно меньше, чем на стоке адресного n-канального транзистора в конструкции-прототипе. Это снижает необходимую величину напряжения программирования, что упрощает техническую реализацию кристаллов микросхем.

Первый n-канальный транзистор управления режимом работы программируемой ячейки, расположенный между выходом второго инвертора и входом первого инвертора в рабочем режиме (после проведения однократного программирования) микросхемы отключает обратную связь первого и второго инверторов, тем самым предотвращая защелкивание триггерной части ячейки при радиационном воздействии. Это значительно снижает требования к проводимости перемычек antifuse после программирования и уменьшает время, необходимое для восстановления логического состояния программируемой ячейки после радиационного воздействия, что упрощает технологическую реализацию кристаллов микросхем.

Второй n-канальный транзистор управления режимом работы ячейки, разделяет высоковольтную часть программируемой ячейки, которая при программировании находится под повышенным напряжением, и триггерную часть программируемой ячейки, управляющую состоянием ключей, задающих конфигурацию межсоединений формируемой схемы. Поэтому на триггерную часть программируемой ячейки не воздействует высокое напряжение программирования, к ее транзисторам не предъявляются требования обеспечения режимов высоковольтного процесса однократного программирования, а все транзисторы триггерных частей всех программируемых ячеек конфигурационной матрицы находятся под одним потенциалом. Это позволяет снизить требования к пробивным напряжениям изолирующих и диффузионных слоев, исключить токи утечек р-n переходов при программировании и выполнить низковольтными, имеющими минимальные топологические размеры, транзисторы триггерной части программируемых ячеек конфигурационной матрицы и транзисторы ключей, составляющие значительную часть общего количества транзисторов микросхемы, что значительно повышает степень интеграции и упрощает технологическую реализацию кристаллов микросхем.

Заявляемое изобретение иллюстрируется следующими графическими материалами.

Фиг.1. Схема программируемой ячейки конфигурационной матрицы, в наиболее близкой по технической сути и достигаемому результату к заявляемой конструкции [2].

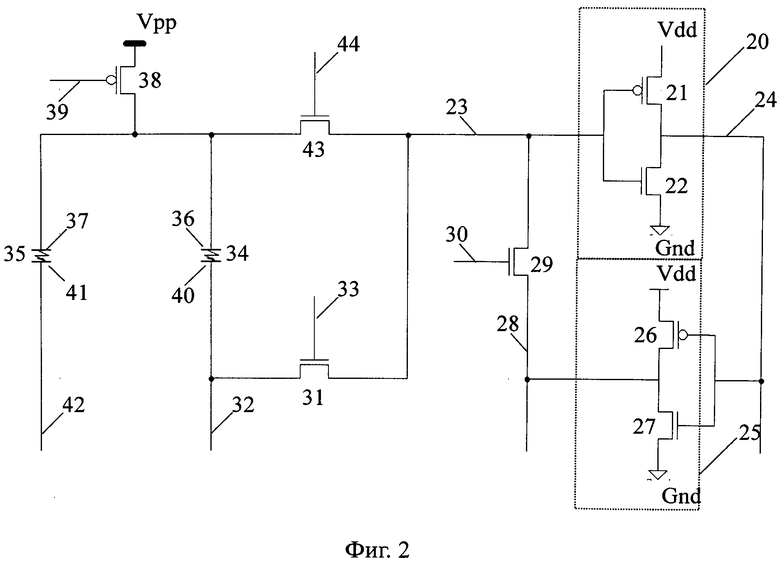

Фиг.2. Конструкция программируемой ячейки конфигурационной матрицы заявляемой радиационно-стойкой энергонезависимой программируемой логической интегральной схемы.

Заявляемое изобретение осуществляет работу следующим образом.

В радиационно-стойкой энергонезависимой программируемой логической интегральной схеме, включающей функциональные блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек, ячейки конфигурационной матрицы содержат первый инвертор 20, состоящий из подключенного истоком к шине питания Vdd p-канального транзистора 21 и подключенного истоком к шине земли Gnd n-канального транзистора 22, соединенные затворы которых являются входом 23 первого инвертора 20, соединенные стоки являются выходом 24 первого инвертора 20 и подключены к входу второго инвертора 25, состоящему из подключенного истоком к шине питания Vdd p-канального транзистора 26 и подключенного истоком к шине земли Gnd n-канального транзистора 27, затворы которых являются входом второго инвертора 25, соединенные стоки являются выходом 28 второго инвертора 25. Выход 28 инвертора 25 подключен к истоку первого n-канального транзистора 29 управления режимом работы ячейки. Затвор транзистора 29 подключен к первой шине 30 управления режимом работы ячейки, а сток ко входу 23 первого инвертора 20 и стоку n-канального адресного транзистора 31, исток которого подключен к первой разрядной шине 32, а затвор соединен с адресной шиной 33. Ячейка содержит первую 34 и вторую 35 перемычки antifuse, каждая из которых имеет по два электрода. Первый электрод 36 перемычки 34 подключен к первому электроду 37 перемычки antifuse 35 и к стоку p-канального транзистора 38 программирования перемычек antifuse. Исток транзистора 38 подключен к общей для всей матрицы шине напряжения программирования Vpp, а затвор к шине 39 управления программированием перемычек antifuse. Второй электрод 40 первой перемычки antifuse 34 подключен к первой разрядной шине 32, второй электрод 41 перемычки antifuse 35 подключен ко второй разрядной шине 42. Первые электроды 36, 37 перемычек antifuse 34, 36, соответственно, также подключены к истоку второго n-канального транзистора 43 управления режимом работы ячейки, затвор которого подключен к второй шине 44 управления режимом работы ячейки, а сток ко входу 23 инвертора 20.

Транзисторы 21, 22, 26, 27 инверторов 20, 25 являются низковольтными, транзисторы 29, 31, 38, 43 являются высоковольтными. Например, для программируемых логических интегральных схем, изготовленных в типовом КМОП технологическом процессе с 0,18 мкм проектными нормами, величина напряжения питания ядра Vdd может быть равна 1,71-1,89 В, величина напряжения питания периферийных схем (буферов) ввода-вывода микросхемы Vddo может быть равна 3,0-3,6 В. При этом номинальное напряжение питания низковольтных транзисторов может быть равно 1,8 В, номинальное напряжение питания высоковольтных транзисторов, которые также используются в периферийных схемах ввода-вывода, может быть равно 3,3 В, а предельная величина напряжения питания высоковольтных транзисторов может быть равна 7,0 В.

Инверторы 20, 25 и транзисторы 29, 31 формируют электрическую схему триггерной перезаписываемой ячейки памяти, которая используется для многократной записи данных в программируемую ячейку конфигурационной матрицы в режиме отладки проекта. Для записи данных в ячейку на первую разрядную шину 32 подается потенциал земли Gnd (для записи логического «0») или напряжение питания Vdd (для записи логической «1»), на первую шину 30 управления режимом работы программируемой ячейки подается потенциал земли Gnd, который закрывает n-канальный транзистор 29. На адресную шину 33 подается положительное смещение напряжения питания Vddo, которое открывает адресный транзистор 31 и ячейка переводится в состоянии логического «0» или «1». Для перевода ячейки в состояние хранения информации, открывается транзистор 29, а адресный транзистор 31 закрывается. При этом на выходах 24, 28 инверторов 20, 25, подключенных известным образом ко входам ключей, задающих конфигурацию межсоединений формируемой схемы, устанавливаются потенциалы земли Gnd или напряжения питания Vdd, которые определяют проводящее или не проводящее состояние ключей. При считывании записанного в ячейке логического состояния открывается адресный транзистор 31 и разрядная шина 32 заряжается до потенциала, соответствующего потенциалу на выходе 28 инвертора 25. В процессе отладки конфигурации величина напряжения питания ядра микросхемы Vdd, которое подается на карманы n-типа и стоки p-канальных транзисторов 21, 26, не превышает предельно-допустимую величину для низковольтных транзисторов технологического процесса, в котором реализуется микросхема. Например, для КМОП технологического процесса с 0,18 мкм проектными нормами с величиной напряжения питания ядра Vdd равной 1,8 В, в режиме отладки проекта величина напряжения программирования Vpp также поддерживается равной 1,8 В, что значительно меньше величины, необходимой для пробоя диэлектрика перемычек antifuse 34, 35. Второй п -канальный транзистор 43 управления режимом работы программируемой ячейки, отделяющий триггерную многократно перезаписываемую часть программируемой ячейки от части ячейки, предназначенной для однократного программирования, в режиме отладки проекта закрыт и перемычки antifuse 34, 35 не влияют на процесс записи данных и чтения данных в триггерной части ячейки.

После окончания процесса отладки конфигурации проекта проводят однократное программирование ячеек конфигурационной матрицы, программируя только одну перемычку (34 или 35) в каждой программируемой ячейке. Для пробоя диэлектрика перемычки antifuse 34 на первую разрядную шину 32 подают потенциал земли Gnd, на вторую разрядную шину 42 подают защитное напряжение, повышают напряжение Vpp до величины напряжения программирования, на шину 39 управления программированием подают потенциал земли Gnd, что бы перевести p-канальный транзистор 38 программирования перемычек в проводящее состояние. При этом на первом электроде 36 перемычки 34 устанавливается напряжение программирования Vpp, на втором электроде 40 перемычки 34 - потенциал земли Gnd. Происходит пробой диэлектрика перемычек antifuse 34 и электроды 36, 40 перемычки замыкаются. На первом электроде 37 перемычки 35 устанавливается напряжение программирования Vpp, на втором электроде 41 перемычки 34 - потенциал защитного напряжения. Такая разность потенциалов на электродах перемычки 35 недостаточна для пробоя диэлектрика и программирование перемычки 35 не происходит. Конкретная величина напряжения программирования Vpp, а также величина защитного напряжения определяется технологическим процессом изготовлением кристаллов микросхем. Например, для КМОП технологического процесса с 0,18 мкм проектными нормами, величина напряжения Vpp равна 7,0 В, что не превышает предельное напряжение питания высоковольтных транзисторов, а величина напряжения пробоя диэлектрика перемычки составляет 4,5-5,0 В. Величина защитного напряжения может быть равна величине напряжения питания периферийных схем (буферов) ввода-вывода микросхемы Vddo. Например, для КМОП технологического процесса с 0,18 мкм проектными нормами с величиной напряжения питания буферов ввода-вывода Vddo равной 3,0 - 3,6 В, величина защитного напряжения на разрядной шине 42 может быть установлена равной 3,3 В. При этом разность напряжений на обкладках 37, 41 перемычки 35 равна 3,7 В и пробоя диэлектрика перемычки не происходит.

Подобным образом, для пробоя диэлектрика перемычки antifuse 35 на вторую разрядную шину 42 подают потенциал земли Gnd, на первую разрядную шину 32 подают защитное напряжение, повышают напряжение Vpp до величины напряжения программирования, на шину 39 управления программированием подают потенциал земли Gnd, что бы перевести p-канальный транзистор 38 программирования перемычек в проводящее состояние. При этом на первом электроде 37 перемычки 35 устанавливается напряжение программирования Vpp, на втором электроде 41 перемычки 35 - потенциал земли Gnd. Происходит пробой диэлектрика перемычек antifuse 35 и электроды 37, 41 перемычки замыкаются. На первом электроде 36 перемычки 34 устанавливается напряжение программирования Vpp, на втором электроде 40 перемычки 34 - потенциал защитного напряжения. Такая разность потенциалов на электродах перемычки 34 недостаточна для пробоя диэлектрика и программирование перемычки 34 не происходит.

После однократного программирования одной из перемычек antifuse 34 или 35 микросхема переводится в рабочий режим. При этом уменьшают величину напряжения Vpp до величины, не превышающей значение предельно-допустимого напряжения питания транзисторов первого 20 и второго 25 инверторов ячейки и ключей, задающих конфигурацию межсоединений микросхемы (например, до величины напряжения питания Vdd), закрывают p-канальный транзистор 38, на первую разрядную шину 32 подают землю Gnd, на вторую разрядную шину 42 подают напряжение Vpp. Подачей на шину 30 управления режимом работы ячейки потенциала земли Gnd закрывают n-канальный транзистор 29, тем самым устраняя соединение выхода 28 второго инвертора 25 со входом 23 первого инвертора 20 и исключая защелкивание триггерной части ячейки, и закрывают адресный транзистор 31. Для подачи напряжения одной из разрядных шин 32 или 42 (в зависимости от запрограммированной перемычки 34 или 35, соответственно) на вход 23 первого инвертора 20 программируемой ячейки открывают n-канальный транзистор 43, подавая на его затвор напряжение Vddo, которое больше напряжения питания Vdd транзисторов триггерной части программируемой ячейки, для исключения снижения уровня выходного сигнала логической «1» на входе 23 инвертора 20. Если в проводящем состоянии находится перемычка 34, то на выходах 24 и 28 инверторов 20 и 25, которые управляют состоянием ключей, задающих конфигурацию межсоединений микросхемы, формируются напряжение Vdd и потенциал земли Gnd, соответственно. Если в проводящем состоянии находится перемычка 35, то на выходе 24 инвертора 20 формируется потенциал земли Gnd, а на выходе инвертора 25 напряжение питания Vdd.

Описанный выше перевод микросхемы в рабочий режим может проводиться с помощью подачи сигнала высокого или низкого уровней на внешний вывод микросхемы.

Формирование одинаковых частей программируемых ячеек всей конфигурационной матрицы под одним электрическим потенциалом, использование для проведения программирования только одного в каждой программируемой ячейке p-канального транзистора, снижение требований к пробивным напряжениям изолирующих и диффузионных слоев, исключение токов утечек р-n переходов при программировании и выполнение транзисторов триггерной части программируемых ячеек конфигурационной матрицы и транзисторов ключей низковольтными с минимальными топологическими размерами, а также исключение защелкивания триггерной части ячейки при радиационном воздействии, позволяет повысить степень интеграции и упростить техническую реализацию кристаллов микросхем.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| ИНТЕГРАЛЬНАЯ МИКРОСХЕМА РАДИОЧАСТОТНОГО ИДЕНТИФИКАТОРА | 2011 |

|

RU2465645C1 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| ЭЛЕКТРИЧЕСКИ СТИРАЕМАЯ И ПРОГРАММИРУЕМАЯ ЭНЕРГОНЕЗАВИСИМАЯ НАКОПИТЕЛЬНАЯ ЯЧЕЙКА | 1996 |

|

RU2168242C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ УРОВНЯ СИГНАЛА В СХЕМАХ С ПРОГРАММИРУЕМОЙ КОММУТАЦИЕЙ | 2011 |

|

RU2469472C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| МАТРИЦА ФЛЭШ-ПАМЯТИ С ВНУТРЕННИМ ОБНОВЛЕНИЕМ | 1999 |

|

RU2224303C2 |

Изобретение относится к области микроэлектроники. Радиационно-стойкая энергонезависимая программируемая логическая интегральная схема включает функциональные блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек. Ячейки схемы содержат первый и второй инверторы, первый n-канальный транзистор управления режимом работы программируемой ячейки, включенный между выходом второго и входом первого инверторов. Исток p-канального транзистора программирования подключен к шине напряжения питания программирования, сток к первым электродам первой и второй перемычек antifuse, вторые электроды перемычек antifuse подключены к первой и второй разрядным шинам. Второй n-канальный транзистор управления режимом работы программируемой ячейки включен между первой и второй перемычками antifuse и входом первого инвертора. Адресный транзистор подключен ко входу первого инвертора. Заявленная конструкция позволяет повысить степень интеграции и упростить техническую реализацию программируемых логических интегральных схем. 2 ил.

Радиационно-стойкая энергонезависимая программируемая логическая интегральная схема, включающая функциональные блоки, систему межсоединений и конфигурационную матрицу программируемых ячеек, ячейки которой содержат первый инвертор, состоящий из подключенного истоком к шине питания p-канального транзистора и подключенного истоком к шине земли n-канального транзистора, соединенные затворы которых являются входом первого инвертора, соединенные стоки являются выходом первого инвертора и подключены ко входу второго инвертора, состоящего из подключенного истоком к шине питания p-канального транзистора и подключенного истоком к шине земли n-канального транзистора, соединенные затворы которых являются входом второго инвертора, соединенные стоки являются выходом второго инвертора, первую и вторую перемычки antifuse, имеющие первый и второй электроды, первую и вторую разрядные шины, адресный транзистор, исток которого подключен к первой разрядной шине, сток подключен ко входу первого инвертора, а затвор соединен с адресной шиной, отличающаяся тем, что программируемые ячейки конфигурационной матрицы дополнительно содержат первый n-канальный транзистор управления режимом работы программируемой ячейки, исток которого подключен к выходу второго инвертора, сток ко входу первого инвертора, а затвор подключен к первой шине управления режимом работы программируемой ячейки, p-канальный транзистор программирования перемычек antifuse, исток которого подключен к общей для всей матрицы шине напряжения питания программирования, сток к первым электродам первой и второй перемычек antifuse, затвор к шине управления программированием перемычек antifuse, второй n-канальный транзистор управления режимом работы программируемой ячейки, исток которого подключен к стоку p-канального транзистора программирования перемычек antifuse и первым электродам первой и второй перемычек antifuse, затвор подключен ко второй шине управления режимом работы ячейки, сток ко входу первого инвертора, второй электрод первой перемычки antifuse подключен к первой разрядной шине, второй электрод второй перемычки antifuse подключен ко второй разрядной шине.

| US 5426614 A, 20.06.1995 | |||

| US 2011249487 A1, 13.10.2011 | |||

| US 6888748 B2, 03.05.2005 | |||

| US 6721197 B1, 13.04.2004 | |||

| US 5812468 A, 22.09.1998 | |||

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| RU 2010105757 A, 27.08.2011 | |||

Авторы

Даты

2015-09-20—Публикация

2014-02-04—Подача