Изобретение относится к цифровой технике и может быть использовано в микросхемах программируемой логики, динамически реконфигурируемых БИС, микропроцессорах и прочих устройствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в качестве управляющей памяти.:

В известных схемах несимметричных ячеек памяти на основе комплементарных МОП-транзисторов используется биста- биль Яая статическая ячейка и схема управ- записью в-и считыванием из-ячейки. Построение на их основе управляющего ОЗУ влечет за собой либо из- точность цепей управления выраженную в введении до- полнительных блоков, позволяющих организовать цикл записи Лог.О и Лог.1 в бистабильную ячейку памяти; что в целом снижает .)Схемы, либо. получёнйё различн ых;ур6в;ней jioг.О ходах Q и /Q, что ё услЬййях упрабляющегб

ОЗУ может привести к1 искажению сигнала управления поступайщего с Данного ОЗ У

Повышение быстродействия при записи информации в ячейкуПамяти сШпользго- . ванием минимальных схемотехнических затрат и формй ро ва ние идеНтичных зйа чё- ний выходного управляющего сй гйа ла на выходах Q и /О управляющего бЗУ является актуальной задачей, /f.-,.

Задача предполагаемого изобретения

- повышение технико-экономических характеристик цифровых микросхем (повыше- ние надежности, уменьшение габаритов и ,, стоимости изделия за счет изменения схе- Г мы элемента памяти построенной на основе ... комплементарных МОП-транзисторов).

Известна схема несимметричной КМОП ячейки памяти, состоящая из первых N- и Р-канальных МОП-транзисторов, стоки ко- .„..торых объединены и соединены с затворами .. вторых N-x и Р-канальных МОП-транзисто- .. ров, стоки котор ых, в свою очередь, объединены и соединены с затворами первых N- и ;. Р-канальных МОП-транзисторов и стоком; третьего N-канального МОП-транзистора, , Шток и атвор которого соответственно со- единены с разрядной шиной и шиной адреса, а его подложка, как и подложки первого и второго N-канальных МОП-транзисторов, так же их истоки соединены с общей шиной, шины питание, с которой соединены истоки и подложки первого и второго Р-канальных МОП-транзисторов.

Недостатком данной схемы является отличие при записи сигналов Лог.О и Лог.1 в ячейку памяти, что приводит к временным потерям в цикле записи, Так, при записи Лог.О на шину адреса подается высокий, а

на разрядную - низкий потенциалы. Первый N-канальный МОП-транзистор запирается, а первый Р-канальный МОП-транзистор открывается. При записи Лог.1 на разрядную шину подается высокий потенциал, понижается напряжение питания ячейки до некоторого промежуточного уровня и лишь после этого, по шине адреса подается импульс выборки. Первый N-канальный МОП-тран- зистор открывается, а первый Р-канальный МОП-транзистор запирается.

Известна схема ячейки памяти на комплементарных МОП-транзисторах, содержащая первый и второй нагрузочные элементы на Р-канальных МОП-транзисторах, первый и второй ключевые элементы и элемент связи на N-канальных МОП-транзисторах, причем стоки транзисторов-первых нагрузочного и ключевого элементов объединены и под- ключены к затворам МОП-транзисторов вто- рых нагрузочного и ключевого элементов и стоку транзистора элемента связи, исток и затвор которого подключены соответственно к разрядной и адресной шинам ячейки, истоки транзисторбё нагрузочных элемен- тов подключены к ;шйие питания ячейки, ис- ток гранзи стбра второго ключевого элемента подключен к шине нулевого по- тенциала ячейки, -а его сток соединен со стоком транзистора второго нагрузочного элемента и затворами транзисторов первых нагрузочного и ключевого элементов, третьего ключевого элемента на Р-канальном МОП-транзисторе затвор и исток которого подключены соответственно к разрядной шине и шине нулевого потенциала ячейки, а сток-подключен к истоку транзистора первого ключевого элемента.

Недостатком данной схемы является от- личие уровня Лог.О на выходах Q и /Q. Различие уровней Лог.О на выходах Q и /Q связано с использованием в качестве третьего ключевого элемента Р-каналь- ного МОП-транзистора. Так как Р-каналь- ный МОП-транзистор с искажением передает уровень Лог.О, то значение напряжения Лог.О на выходе Q можно определить по формуле

UflbixQ Ua - Unop.,(1)

где UBUXQ - напряжение Лог.О на выходе

ячейки памяти;

Уз. - напряжение на затворе третьего ключевого транзистора; ,

Unop. - пороговое напряжение третьего ключевого транзистора.

Если в ячейку памяти записан Лог.О, а сама ячейка находится в режиме хранения информации или управления каким-либо объектом, (третий ключевой элемент находится в открытом состоянии), как следует из формулы (1) напряжение Лог.О на выходе Q ячейки памяти будет равно Unop. третьего ключевого транзистора, что затрудняет использование данного выхода ячейки памяти дальше в схеме.

Наиболее близким по технической сущности является схема элемента памяти, содержащая два запоминающих транзистора с каналом N-типа, два нагрузочных транзистора с каналом Р-типа, транзистор связи с каналом N-типа, ключевой транзистор с каналом N-типа, исток которого соединен с истоком первого запоминающего транзистора и подключен к шине нулевого потенциала, затвор подключен к первой адресной шине, а сток соединен с истоком второго запоминающего транзистора, затвор которого соединен со стоками первого запоминающего и первого нагрузочного транзисторов и с затвором второго нагрузочного транзистора, сток которого соединен с затворами первого запоминающего и первого нагрузочного транзисторов, со стоком второго запоминающего транзистора, стоком транзистора связи, затвор которого подключен ко второй адресной шине, а исток - к разрядной шине, исток первого нагрузочного транзистора подключен к шине питания.

Недостатком данной схемы является избыточность схемы управления записью в- и считыванием из- ячейки памяти, обусловленная наличием второго элемента связи и второго ключевого элемента выполненных на Р-канальных МОП-транзисторах. Так как подвижность основных носителей у Р-каналь- ного МОП-транзистора приблизительно в два раза меньше, чем у N-канального, и для получения приблизительно одинаковых значе- .ний крутизны, Р-канальный транзистор следует изготавливать с эффективной шириной канала в два раза большей, чем N-ка- нальный, то наличие таких элементов в схеме понижает вероятность получения годного элемента памяти, так как приводит к увеличению ее эффективной площади.

Цель изобретения -упрощение элемента памяти.

Поставленная цель достигается тем, что в элемент памяти, содержащий два запрми- нающих транзистора с каналом N-типа, два нагрузочных транзистора с каналом Р-ти- rfa, транзистор связи с Каналом N-типа, ключевой транзистор с каналом N-типа, исток которого соединен с истоком первого запоминающего транзистора и подключен к шине нулевого потенциала, затвор подключен к первой адресной шине, а сток соединен с истоком второго запоминающего транзистора, затвор которого соединен со стоками первого запоминающего и первого нагрузочного транзисторов и с затвором второго нагрузочного транзистора, сток 5 которого соединен с затворами первого запоминающего и первого нагрузочного транзисторов, со стоком второго запоминающего транзистора, стоком транзистора связи, затвор которого подключён

0 ко второй адресной шине, а исток - к разрядной шине, исток первого нагрузочного транзистора подключен к шине питания, дополнительно введена связь истока второго нагрузочного транзистора с истоком перво5 го нагрузочного транзистора.

Положительный эффект (уменьшение эффективной площади кристалла путем упрощения схемы ячейки памяти) достигается тем, что в предлагаемой схеме элемента па0 мяти введение связи истока второго нагрузочного транзистора с истоком первого нагрузочного транзистора позволяет исключить второй транзистор связи с каналом Р-типа и второй ключевой элемент с кана5 лом Р-типа, при этом функциональные возможности ячейки памяти не изменяются.

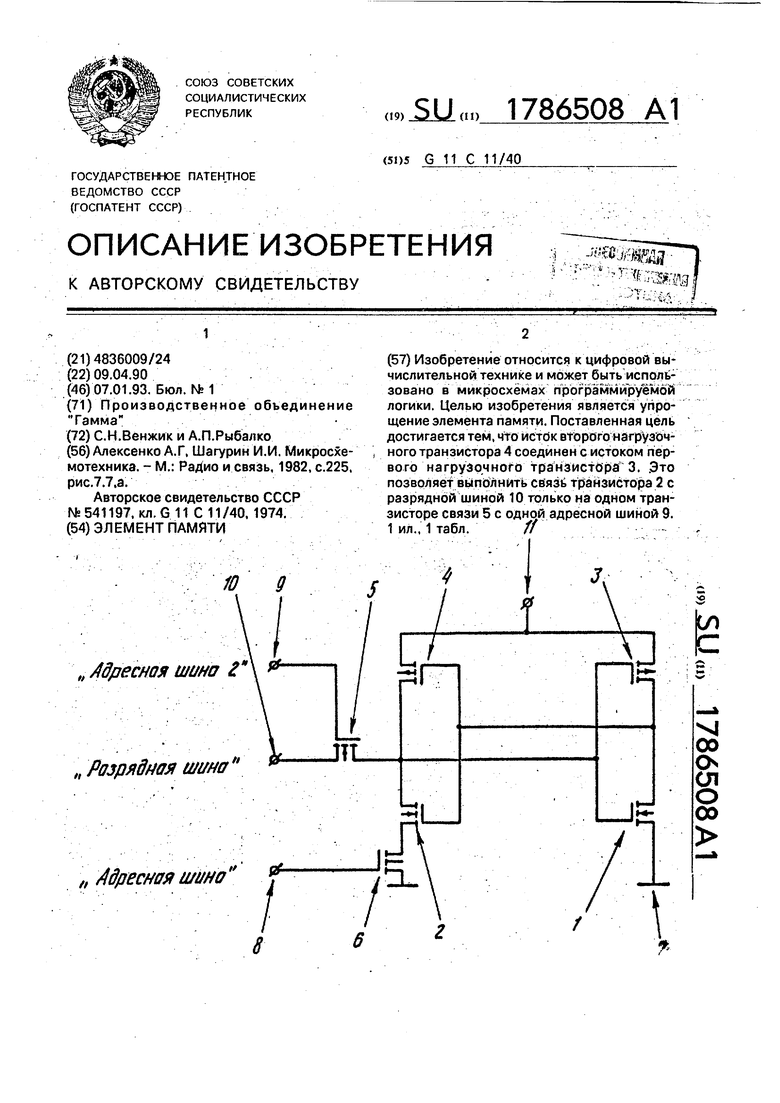

На чертеже приведена схема предлага - емого элемента памяти на основе комплементарных МОП-транзисторов.

0 Элемент памяти, содержащий два запоминающих тра нзистора с каналом N-типа 1 и 2, два нагрузочных транзистора с каналом Р-типа 3 и 4, транзистор связи 5 с каналом N-типа, ключевой транзистор 6 с

5 каналом N-типа, исток которого соединен с истоком первого запоминающего транзистора 1 и подключен к шине нулевого потенциала 7, затвор подключен к первой адресной шине 8, а сток соединен с истоком

0 второго запоминающего транзистора 2, затвор которого соединен со стоками первого запоминающего 1 и первого нагрузочного 3 транзисторов и с. затвором второго нагрузочного транзистора 4, сток которого соеди5 нен с затворами первого запоминающего 1 и первого нагрузочного 3 транзисторов, CQ стоком второго запоминающего транзистора 2, стоком транзистора связи 5, затвор которого подключен ко второй:адресной ши0 не 9, а исток - к разрядной шине 10, исток первого нагрузочного транзистора 3 подключен к шине питания 11, а исток второго нагрузочного транзистора 4 соединен с истоком первого нагрузочного транзистора 3.

5 Элемент памяти работает следующим образом.- При записи Лог.О:

На вход 10 Разрядная шина подается напряжение Лог.О, на Адресную шину 2 9 - Лог.1, а на Адресную шину 1 8 - напряжение Лог.О. По приходу Л.ог.1 и Лог.О на затворы транзистора связи 5 и ключевого транзистора 6 соответственно, транзистор связи 5 открывается, а ключевой транзистор 6 закрывается. Так как - канальный МОП- транзистор без искажения передает Лог.О, то напряжение на затворах транзисторов 3 и 1 шунтируется Лог.О, приходящим со входа 10 Разрядная шина через транзистор связи 5. Появление Лог.О на затворах транзисторов 3 и 1 приводит к включению нагрузочного транзистора 3 и выключению запоминающего транзистора 1.

Включение первого нагрузочного транзистора 3 вызывает появление Лог.1 в точке соединения стоковых областей транзисторов 3 и 1, и, следовательно, напряжения высокого уровня на затворах транзисторов 4 и 2. Появление Лог.1 на затворах транзисторов 4 и 2 приводит к выключению нагрузочного транзистора 4 и включению запьминающего транзистора 2. Вследствие этого заряд образующийся в точке соединения стоковой области транзистора 6 и исто- ковой области транзистора 2 рассасывается через транзисторы 2 и 5 на Разрядную шину 10, в напряжение в точке соединения транзисторов 6 и 2 уменьшается. По окончанию действия сигнала Лог.1, приходящего на Адресную шину 2 9 и Лог.О, приходящего на Адресную шину 1 8, транзистор связи 5 закрывается, а ключевой транзистор 6 открывается, подтверждая напряжение низкого уровня на истоке запоминающего транзистора 2,

При записе Лог.1:,

На Разрядную шину 10 подают напряжение Лог.1, а на. шины 9 и 8, как и в случае записи Лог.О соответственно Лог.1 и Лог.О. По приходу Лог.1 на затвор транзистора связи 5 он открывается, а Лог.О приходящий по Адресной шине 1 8 закрывает ключевой транзистор 6. Выключение транзистора 6 приводит к отрыву истоковой области запоминающего транзистора 2 от шины нулевого потенциала, и таким образом исключает возможность шунтирования напряжения высокого уровня приходящего с Разрядной шины 10, через транзистор связи 5, на затворы транзисторов 3 и 1. Несмотря на то, что транзистор связи 5 передает с искажением напряжение Лог.1 (Ucc-Unopjsi) это, в конечном итоге, не влияет на переключение транзисторов 3 и 1. Появление напряжения высокого уровня на затворе запоминающего транзистора 1 (большего Упоры) приводит к его включению и появлению напряжения Лог.О на затворах транзисторов 4 и 2, нагрузочный транзистор 3 при этом закрывается.

Появление Лог.О на затворах транзисторов 4 и 2 приводит к включению нагрузочного транзистора 4 и выключению (по цепи затвора) выключенного по истоковой цепи запоминающего транзистора 2. Включение нагрузочного транзистора 4 приводит к подтверждению записываемого в ячейку напряжения Лог.1. По окончанию сигнала разрешения (напряжение на входе Адрес- ная шина 2 9 меняется с Лог.1 в Лог.О, а на входе Адресная шина Г 8 с Лог.О в Лог.1) транзистор связи 5 закрывается, а ключевой транзистор 6 включается. Включение транзистора б не влияет на схему, так как запоминающий транзистор 2 заперт по цепи затвора напряжением Лог.О.

При считывании информации: Возможны два режима считывания информации записанной в предлагаемую

ячейку памяти. Режим управления объектом. Так как данная ячейка памяти предназначена для работы в качестве ячейки управляющего ОЗУ, то цепи записи и считывания

информации разграничены. При управлении объектом электронных схем (например: элементами коммутации или выступая в качестве источника опорного сигнала) выходные напряжения с Ячейки можно снимать

с точек: прямой сигнал (Вых. Q) - точка соединения стоковых областей транзисторов 4 и 2; инверсный сигнал (Вых./Q) - точка соединения стоковых областей транзисторов элементов 3 и 1.

Режим контрольного считывания информации.

При появлении Лог.1 на Адресных шинах 8 и 9 транзистор связи 5 и ключевой

транзистор 6 открываются. Ранее записанная информация (Лог.О или Лог.1) через транзистор связи 5 поступает на Разрядную шину 10, которая в данном случае является выходом Q ячейки памяти. При таком считывании Лог.О с ячейки считывается без

искажений, а Лог.1 считывается пониженной на Unop.N.; Предлагаемая ячейка памяти является статической, вследствие чего считывание можно осуществлять многократно,...

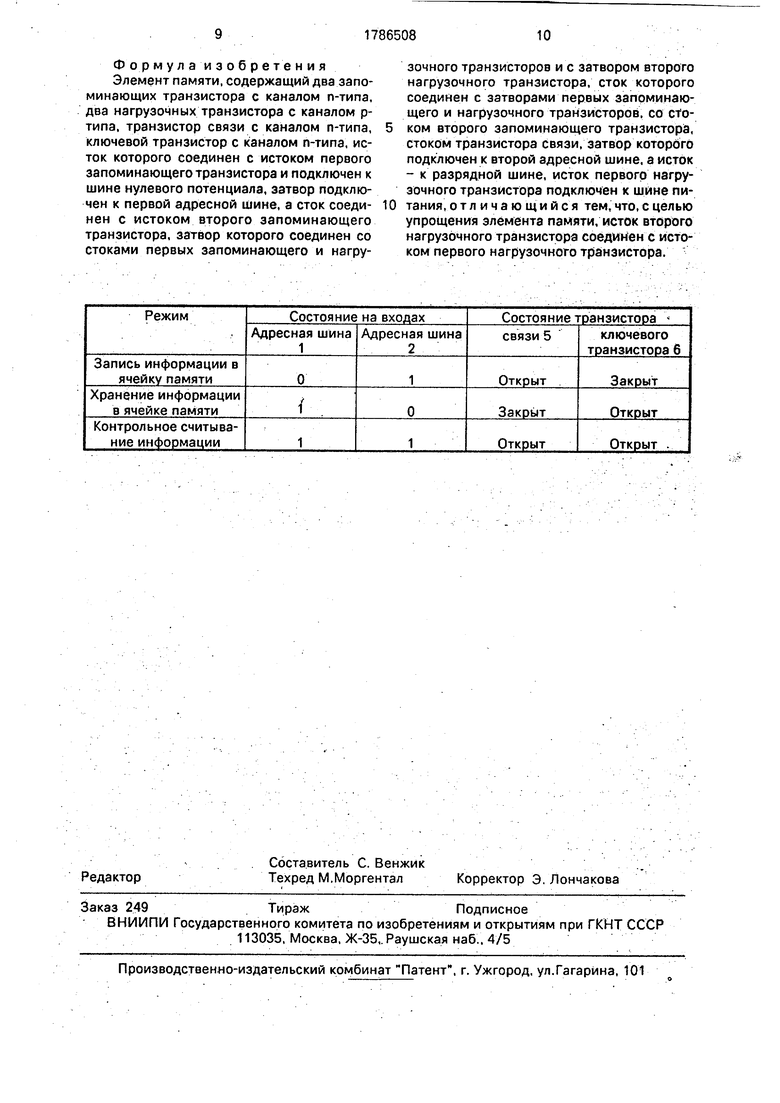

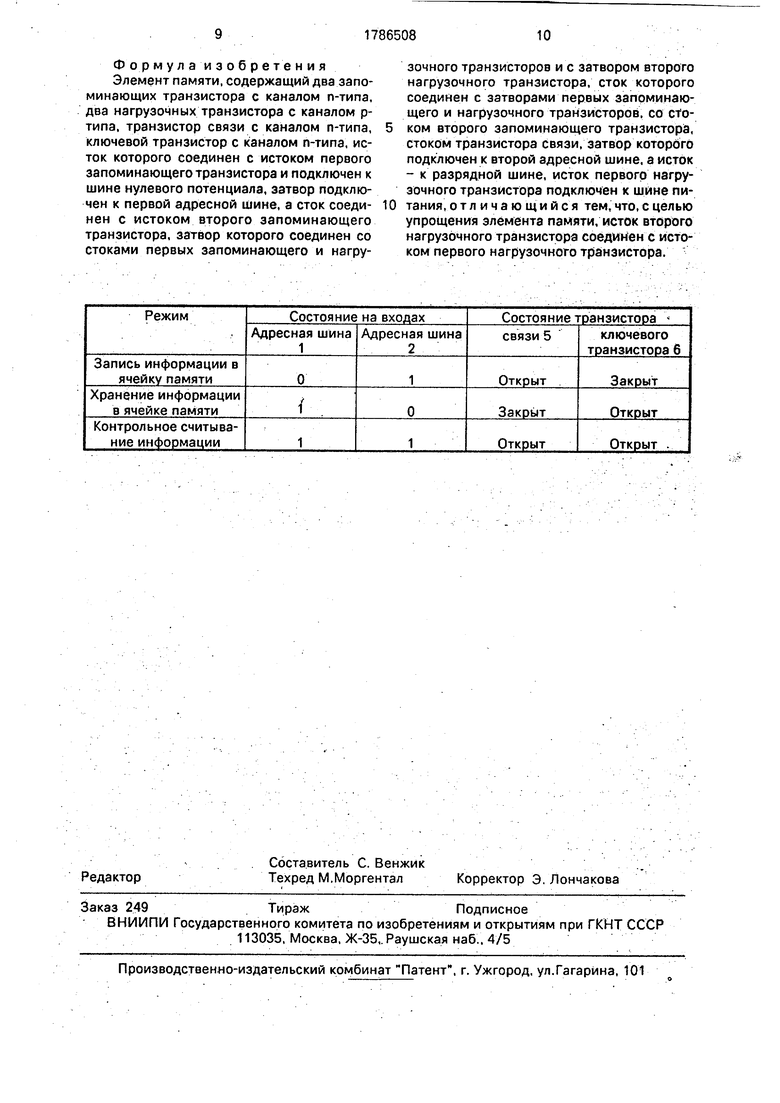

В таблице Приведены режимы функционирования заявляемой ячейки памяти.

По сравнению с наиболее близким техническим решением предлагаемое техническое решение позволяет уменьшить

эффективную площадь ячейки памяти на 25%, что в свою очередь ведет к уменьшению линейных размеров БИС в целом и положительно отразится на повышении надёжности микросхемы.

Ф о р м у л а и з о б р е т е н и я Элемент памяти, содержащий два запоминающих транзистора с каналом п-типа, два нагрузочных транзистора с каналом р- типа, транзистор связи с каналом п-типа, ключевой транзистор с каналом п-типа, исток которого соединен с истоком первого запоминающего транзистора и подключен к шине нулевого потенциала, затвор подключен к первой адресной шине, а сток соединен с истоком второго запоминающего транзистора, затвор которого соединен со стоками первых запоминающего и нагру0

зочного транзисторов и с затвором второго нагрузочного транзистора, сток которого соединен с затворами первых запоминающего и нагрузочного транзисторов, со стоком второго запоминающего транзистора, стоком транзистора связи, затвор которого подключен к второй адресной шине, а исток - к разрядной шине, исток первого нагрузочного транзистора подключен к шине питания, отличающийся тем, что, с целью упрощения элемента памяти, исток второго нагрузочного транзистора соединен с истоком первого нагрузочного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти на основе комплементарных МОП-транзисторов | 1989 |

|

SU1640738A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Усилитель парафазного сигнала | 1987 |

|

SU1564690A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в микросхемах программируемой логики. Целью изобретения является упрощение элемента памяти. Поставленная цель достигается тем, что исток второго нагрузочного транзистора 4 соединен с истоком первого нагрузочного транзистора 3. Это позволяет выполнить связь транзистора 2 с разрядной шиной 10 только на одном транзисторе связи 5 с одной адресной шиной 9. 1 ил., 1 табл.ff

| Алексеи ко А | |||

| Г, Шагурин И.И | |||

| Микросхемотехника | |||

| - М.: РаДио и связь, 1982, с.225 | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Квазистатическая ячейка памяти | 1974 |

|

SU541197A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-01-07—Публикация

1990-04-09—Подача