Изобретение относится к вычислительной технике и может быть использовано для создания виртуальной памяти компьютера и компьютерных систем.

Известен способ, согласно которому множество кэш-буферов отображений, каждый из которых ассоциирован с соответствующим ему одним из множества устройств обработки данных из состава вычислительного устройства, используются для преобразования виртуальных адресов в физические адреса и сохранения отображений, основанных на карте преобразования адресов, причем, способ включает в себя этапы, на которых поддерживают счетчик, обновляют упомянутый счетчик каждый раз, когда первый из упомянутого множества кэш-буферов отображений очищают, записывают значение упомянутого счетчика в качестве реакции на изменение в карте преобразования адресов, при этом записанное значение счетчика сохраняют, определяют на основе результата сравнения упомянутого значения счетчика с записанным значением счетчика, что первый из упомянутого множества кэш-буферов отображений не был доподлинно очищен с тех пор, когда произошло упомянутое изменение карты преобразования адресов, и очищают первый из упомянутого множества кэш-буферов отображений, при этом, политика определяет дозволенный доступ к памяти, причем, способ дополнительно включает в себя этап, на котором осуществляют управление содержимым карты преобразования адресов так, чтобы карта преобразования адресов не предоставляла объекту отображения виртуальных адресов, которые позволили бы упомянутому объекту осуществить доступ к упомянутой памяти в нарушение упомянутой политики, а упомянутое изменение содержит либо модификацию карты, которая переводит или поддерживает карту в состоянии, согласующемся с упомянутой политикой, либо модификацию карты, которая ограничивает упомянутому объекту доступ на запись к карте [RU 2371267, С2, G06F 12/08, 10.07.2009].

Недостатком способа является относительно узкая область применения.

Известен также способ организации глобально адресуемой общей памяти в многопроцессорной ЭВМ на основе многоядерно-мультитредового микропроцессора с использованием двухуровневой сегментной виртуальной памяти, с использованием сегментов двух типов - обычных сегментов и суперсегментов большого объема, с поддержкой скремблирования, то есть отображения последовательности виртуальных адресов одного сегмента, следующих с регулярным шагом, в физические адреса с псевдослучайными номерами узлов, с возможностью распределения виртуальных адресов одного сегмента по физическим адресам разных узлов, согласно которому одновременно с использованием поддержки двухуровневой сегментной виртуальной памяти используют трехуровневую сегментно-страничную организацию памяти с выполнением части этапа трансляции адреса на удаленном узле, кроме того, для поддержки работы с суперсегментами используется одна TLB, кроме того, для каждого сегмента или суперсегмента независимо от других сегментов управляют количеством узлов, по которым производится распределение сегмента одним из двух способов - блочным (когда номер узла для физического размещения данных определяется заданным количеством старших разрядов виртуального адреса) и блочно-циклическим (когда номер узла для физического размещения данных определяется заданным количеством средних разрядов виртуального адреса), а также для каждого сегмента или суперсегмента используют логическую нумерацию узлов (при этом номера узлов, на которых размещен сегмент, должны быть строго монотонны) или виртуальную нумерацию узлов (которая может отображаться на немонотонную последовательность номеров узлов), также для каждого сегмента или суперсегмената при использовании трехуровневой сегментно-страничной организации памяти указывают один из четырех возможных размеров страниц, после чего производится доступ к TLB страниц [RU 2396592, C2, G06F 12/02, 10.08.2010].

Недостатком способа также является относительно узкая область применения.

Наиболее близким по технической сущности к предложенному является способ, заключающийся в том, что используют процессор с регистром флагов процессора, кэш-память, основную память, операционную систему, разделяют буфер данных кэш-памяти на сегменты, закрепляют сегменты за задачами, предохраняют их от использования другими задачами, гарантируют сохранность содержимого в процессе работы операционной системы, при этом, в нем разделение буфера данных кэш-памяти осуществляют на две равные части, одну из которых в каждый момент назначают в качестве активной, а вторую в качестве пассивной, при смене задачи, наоборот, активную назначают пассивной, а пассивную активной, ведут кэширование в виртуальном адресном пространстве, назначают активной части буфера данных режим прямой адресации, содержимое части буфера данных старой задачи сохраняют в основную память независимо от процессора, а содержимое части буфера данных новой задачи предварительно восстанавливают из основной памяти также независимо от процессора и приводят содержащиеся в восстанавливаемой части буфера данных новой задачи глобальные данные в соответствие со значениями, которые были изменены другими задачами, с помощью блока управления глобальными данными [RU 223854, С2, G06F 12/08, 10.02.2004].

Недостатком наиболее близкого технического решения является относительно узкая область применения, поскольку оно позволяет формировать виртуальную память компьютера, но не позволяет формировать виртуальную память с повышенной оперативностью ее функционирования.

Действительно, в известном техническом решении используется кэш-память, которая обладает каталогом задач, где для каждой задачи содержится каталог страниц, который указывает на конкретные страницы внешнего накопителя, закрепленные за конкретной задачей. Поэтому в этой классической схеме построения виртуальной памяти обращение к виртуальной памяти производится в три этапа, в результате чего обращение к накопителю является медленной операцией, выполняемой специальными программами подкачки (свопирования).

Требуемый технический результат заключается в расширении области применения для формирования виртуальной памяти компьютера с повышенной оперативностью.

Требуемый технический результат достигается тем, что в способе формирования виртуальной памяти, заключающемся в формировании адресных пространств задач и их преобразовании в адресное пространство виртуальной памяти, размещенной в реальной оперативной памяти, преобразование адресных пространств задач в адресное пространство виртуальной памяти производят путем предварительного формирования виртуальной оперативной памяти, размер которой устанавливают равным размеру памяти внешнего накопителя и в которой устанавливают однозначное соответствие адресов страниц виртуальной оперативной памяти адресам страниц памяти внешнего накопителя, после чего преобразуют виртуальную оперативную память в реальную оперативную память через дополнительный этап преобразования адресов виртуальной оперативной памяти в адреса реальной оперативной памяти.

Известны также устройства, используемые для реализации виртуальной памяти.

Известно устройство, состоящее из процессора с двоичными признаками, операционной системы, кэш-памяти с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналов доступа к кэш-памяти, основной памяти, которое выполняет управление кэш-памятью, для использования в многопоточном процессоре, при этом, устройство распределяет кэш-память между потоками многопоточного процессора, когда необходимая линия в кэш-памяти не обнаружена, устройство выбирает линию замены из раздела кэш-памяти, который прикреплен к тому потоку, из которого произошло обращение, приведшее к данной ситуации, таким образом предотвращая порчу разделов, принадлежащих другим потокам [US 6381676, G06F 12/08, 07.12.2000].

Недостатком устройства являются относительно узкие функциональные возможности.

Известно также устройство, состоящее из процессора, с двоичными признаками, операционной системы, кэш-памяти с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналов доступа к кэш-памяти, основной памяти, алгоритма распределения буфера кэш-памяти и набора регистров для хранения информации об распределении, при этом, с помощью алгоритма распределения буфер кэш-памяти разбивается на сегменты, в результате чего появляется группа личных разделов и разделяемый раздел, личные сегменты закрепляются за задачами, предохраняются от использования другими задачами, гарантируется сохранность их содержимого в процессе работы операционной системы, размер каждого раздела кэш-памяти определяется в зависимости от требований, возникающих во время выполнения задач [US 5875464, G06F 12/08, 18.03.1996].

Недостатком устройства также являются относительно узкие функциональные возможности.

Наиболее близким по технической сущности к предложенному является устройство, содержащее процессор с регистром флагов, выполненный идентифицирующим текущий процесс, операционную систему, кэш-память с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналы доступа к кэш-памяти, основную память, при этом, устройство дополнительно снабжено блоком управления глобальными данными, с заложенным алгоритмом разделения данных на локальные и глобальные, соединенным с сегментированным буфером данных и каналами доступа к основной памяти, компилятором, модифицированным для учета особенностей работы кэш-памяти, а также страницей глобальных данных, используемой только блоком управления глобальными данными, буфер данных кэш-памяти выполнен разделенным на две части, таким образом, что одна из них в каждый момент назначается в качестве активной, а вторая в качестве пассивной, блок управления кэш-памятью выполнен с возможностью работать в каждый момент только с активной частью буфера данных кэш-памяти как в пространстве виртуальных адресов, так и в режиме прямой адресации, операционная система выполнена модифицированной так, чтобы поддерживать переключение страниц буфера данных и своевременную загрузку и выгрузку пассивной страницы буфера данных [RU 223854, C2, G06F 12/08, 10.02.2004].

Недостатком наиболее близкого технического решения также являются относительно узкие функциональные возможности.

Требуемый технический результат достигается тем, что, в устройство содержащее процессор, оперативную память и внешний накопитель, вход которого соединен с выходом процессора, введены первый блок переадресации, первый вход которого соединен со вторым выходом процессора, второй блок переадресации, первый вход которого соединен с выходом первого блока переадресации, первый выход - соединен с входом оперативной памяти, второй выход - соединен с входом процессора, а вход-выход - соединен с входом-выходом области оперативной памяти, выделенной для хранения таблиц переадресации второго блока переадресации, при этом, вход-выход оперативной памяти соединен с входом-выходом внешнего накопителя, а вход выход области оперативной памяти, выделенной для хранения таблиц переадресации первого блока переадресации, соединен с входом-выходом первого блока переадресации.

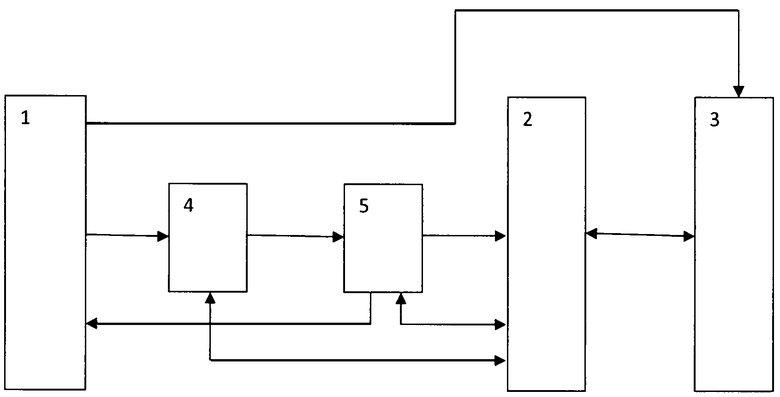

На чертеже представлена функциональная схема виртуальной памяти компьютера, реализующего предложенный способ.

Устройство содержит процессор 1, оперативную память 2 и внешний накопитель 3, вход которого соединен с выходом процессора.

Кроме того, устройство содержит первый блок 4 переадресации, первый вход которого соединен со вторым выходом процессора 1, второй блок 5 переадресации, первый вход которого соединен с выходом первого блока 4 переадресации, первый выход - соединен с входом оперативной памяти 2, второй выход - соединен с входом процессора 1, а вход-выход - соединен с входом-выходом области оперативной памяти 2, выделенной для хранения таблиц переадресации второго блока переадресации, при этом, вход-выход оперативной памяти 2 соединен с входом-выходом внешнего накопителя, а вход выход области оперативной памяти 2, выделенной для хранения таблиц переадресации первого блока переадресации, соединен с входом-выходом первого блока переадресации.

Процессор 1, оперативная память 2, внешний накопитель 3, первый 4 и второй 5 блоки переадресации являются стандартными элементами вычислительной техники.

Работает устройство, в котором реализуется предложенный способ, следующим образом.

Известно, что каждая задача (программа), выполняемая процессором компьютера (а их одновременно выполняется множество), имеет собственное адресное пространство. Это адресное пространство всегда начинается с нулевого адреса. Максимальный адрес устанавливает операционная система компьютера.

Таким образом, адресные пространства у всех задач, выполняемых процессором компьютера, формально совпадают и являются виртуальными адресами.

Для того чтобы они не пересекались в реальной оперативной памяти, их через механизм виртуальных страниц отображают на различные участки реальной оперативной памяти.

В памяти внешнего накопителя для хранения неиспользуемых в текущее время страниц имеется каталог задач, где для каждой задачи, в свою очередь, содержится каталог страниц, который указывает на конкретные страницы памяти внешнего накопителя, закрепленные за конкретной задачей. Эта структура накопителя обязательна, поскольку виртуальные адресные пространства у задач одни и те же.

Таким образом, в традиционных схемах виртуальной памяти, как и в устройстве-прототипе, адресные пространства задач отображаются на небольшое адресное пространство реальной оперативной памяти. Поэтому, если виртуальная страница задачи не используется, то она перемещается во внешний накопитель, где приходится ее размещать через двухуровневый каталог - каталог задач и для каждой задачи - каталог страниц.

В соответствии с предложенным способом формирования виртуальной памяти компьютера в предложенном устройстве для его реализации производится в два этапа с использованием первого 4 и второго 5 блоков переадресации, имеющих аппаратную реализацию.

На первом этапе адресное пространство задач преобразуется в адресное пространство создаваемой виртуальной оперативной памяти с помощью первого блока 4 переадресации. На втором, дополнительном этапе второй блок переадресации преобразует адрес виртуальной оперативной памяти в адрес реальной оперативной памяти 2.

На первом этапе никакой подкачки виртуальных страниц с внешнего накопителя 3 не происходит, так как все виртуальные страницы умещаются в адресном пространстве виртуальной оперативной памяти, объем которой устанавливается равным объему памяти внешнего накопителя 3.

Подкачка виртуальных страниц может происходить только на втором этапе. Для этого, если, например, виртуальная страница отсутствует, то второй блок 2 переадресации выдает сигнал процессору 1, для того чтобы силами специальной программы подкачки была загружена нужная виртуальная страница из внешнего накопителя 3 в реальную оперативную память 2.

Таким образом, если в традиционной схеме формирования виртуальной памяти адреса всех задач, выполняемых процессором компьютера, сразу преобразуются в адреса реальной оперативной памяти, то в предложенном способе и реализующем его устройстве адреса задач сначала преобразуются в адресное пространство внешнего накопителя и только затем преобразуются в адреса оперативной памяти 2 (реальной оперативной памяти).

Выигрыш в оперативности работы такой оперативной памяти достигается за счет упрощения доступа к памяти внешнего накопителя 3.

Вместо трех обращений к памяти внешнего накопителя 3 в традиционной схеме виртуальной памяти компьютера в предложенном техническом решении используется одно. И хотя предложенный способ и его техническая реализация формально проигрывает традиционной за счет наличия двух уровней преобразования адресов, но это незначительный по оперативности проигрыш, поскольку выполняется на аппаратных блоках переадресации, без использования программных средств и на быстродействующем оборудовании центрального процессора компьютера. При этом, замедляясь на переадресации (относительно быстрой аппаратной операции), одновременно реализуется выигрыш на доступе к памяти внешнего накопителя в три раза.

Этим самым достигается требуемый технический результат расширения области применения относительно способа и расширение функциональных возможностей относительно предложенного устройства для его реализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОРГАНИЗАЦИИ ГЛОБАЛЬНО АДРЕСУЕМОЙ ОБЩЕЙ ПАМЯТИ В МНОГОПРОЦЕССОРНОЙ ЭВМ | 2008 |

|

RU2396592C2 |

| СПОСОБ И СИСТЕМА ДЛЯ ВИРТУАЛИЗАЦИИ ГОСТЕВОГО ФИЗИЧЕСКОГО АДРЕСА В СРЕДЕ ВИРТУАЛЬНОЙ МАШИНЫ | 2006 |

|

RU2393534C2 |

| СПОСОБ ОРГАНИЗАЦИИ ПЕРСИСТЕНТНОЙ КЭШ ПАМЯТИ ДЛЯ МНОГОЗАДАЧНЫХ, В ТОМ ЧИСЛЕ СИММЕТРИЧНЫХ МНОГОПРОЦЕССОРНЫХ КОМПЬЮТЕРНЫХ СИСТЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238584C2 |

| ОТЛОЖЕННАЯ ОЧИСТКА БУФЕРОВ БЫСТРОГО ПРЕОБРАЗОВАНИЯ АДРЕСОВ | 2004 |

|

RU2361267C2 |

| УСТРОЙСТВО, СПОСОБ И СИСТЕМА УПРАВЛЕНИЯ МАТРИЦАМИ | 2010 |

|

RU2491616C2 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| УПРАВЛЕНИЕ СКОРОСТЬЮ, С КОТОРОЙ ОБРАБАТЫВАЮТСЯ ЗАПРОСЫ НА ПРЕРЫВАНИЕ, ФОРМИРУЕМЫЕ АДАПТЕРАМИ | 2010 |

|

RU2526287C2 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Связанное с выбранными архитектурными функциями администрирование обработки | 2015 |

|

RU2665243C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении оперативности работы оперативной памяти за счет упрощения доступа к памяти внешнего накопителя. Способ формирования виртуальной памяти, заключающийся в формировании адресных пространств задач и их преобразовании в адресное пространство виртуальной памяти, размещенной в реальной оперативной памяти, причем преобразование адресных пространств задач в адресное пространство виртуальной памяти производят путем предварительного формирования виртуальной оперативной памяти, размер которой устанавливают равным размеру памяти внешнего накопителя и в которой устанавливают однозначное соответствие адресов страниц виртуальной оперативной памяти адресам страниц памяти внешнего накопителя, после чего преобразуют виртуальную оперативную память в реальную оперативную память через дополнительный этап преобразования адресов виртуальной оперативной памяти в адреса реальной оперативной памяти. 2 н.п. ф-лы, 1 ил.

1. Способ формирования виртуальной памяти, заключающийся в формировании адресных пространств задач и их преобразовании в адресное пространство виртуальной памяти, размещенной в реальной оперативной памяти, отличающийся тем, что преобразование адресных пространств задач в адресное пространство виртуальной памяти производят путем предварительного формирования виртуальной оперативной памяти, размер которой устанавливают равным размеру памяти внешнего накопителя и в которой устанавливают однозначное соответствие адресов страниц виртуальной оперативной памяти адресам страниц памяти внешнего накопителя, после чего преобразуют виртуальную оперативную память в реальную оперативную память через дополнительный этап преобразования адресов виртуальной оперативной памяти в адреса реальной оперативной памяти.

2. Устройство для реализации способа по п.1, содержащее процессор, оперативную память и внешний накопитель, вход которого соединен с выходом процессора, отличающееся тем, что введены первый блок переадресации, первый вход которого соединен со вторым выходом процессора, второй блок переадресации, первый вход которого соединен с выходом первого блока переадресации, первый выход - соединен с входом оперативной памяти, второй выход - соединен с входом процессора, а вход-выход соединен с входом-выходом области оперативной памяти, выделенной для хранения таблиц переадресации второго блока переадресации, при этом вход-выход оперативной памяти соединен с входом-выходом внешнего накопителя, а вход-выход области оперативной памяти, выделенной для хранения таблиц переадресации первого блока переадресации, соединен с входом-выходом первого блока переадресации.

| СПОСОБ ОРГАНИЗАЦИИ ПЕРСИСТЕНТНОЙ КЭШ ПАМЯТИ ДЛЯ МНОГОЗАДАЧНЫХ, В ТОМ ЧИСЛЕ СИММЕТРИЧНЫХ МНОГОПРОЦЕССОРНЫХ КОМПЬЮТЕРНЫХ СИСТЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238584C2 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| СПОСОБ ОРГАНИЗАЦИИ ГЛОБАЛЬНО АДРЕСУЕМОЙ ОБЩЕЙ ПАМЯТИ В МНОГОПРОЦЕССОРНОЙ ЭВМ | 2008 |

|

RU2396592C2 |

| US 6442664 В1, 27.08.2002 | |||

| ЕР 0869437 А2, 07.10.1998. | |||

Авторы

Даты

2013-07-10—Публикация

2011-12-13—Подача