Изобретение относится к области оптимизации производительности компьютерных систем, а именно к способам и устройствам для ускорения работы подсистемы оперативной памяти и повышения ее пропускной способности.

Известен способ управления кэш-памятью в многопоточном процессоре, заключающийся в разбиении кэш-памяти на множество отдельных разделов, прикреплении отдельных подмножеств разделов к каждому из выбранных потоков многопоточного процессора, выполнении операции поиска в кэш-памяти, когда многопоточный процессор обращается к линии данных; если необходимая линия в кэш-памяти не обнаружена, то выбирается линия замены в одном из разделов кэш-памяти, который прикреплен к тому потоку, из которого произошло обращение, приведшее к замене линии, разделение кэш-памяти при этом является динамическим (патент США №6381676, МПК G 06 F 12/08, приоритет от 07.12.2000).

Недостатками известного способа являются невозможность работы в многопроцессорных системах, неэффективное использование кэширующей логики из-за распространения ее деятельности на весь буфер кэш-памяти, тогда как реально в каждый момент может использоваться лишь малая его часть, механизм динамического разбиения буфера кэш-памяти может привести к тому, что раз от раза одна и та же программа будет запускаться с разными по объему прикрепленными разделами кэш-памяти, что может сделать ее работу непрогнозируемой по скорости, отсутствие механизма сохранения и восстановления разделов кэш-памяти приведет к тому, что при большем количестве задач либо некоторым из них будет отказано в кэшировании, либо кэширование будет вестись в незначительном по объему разделе буфера, что неэффективно.

Известен также способ, выбранный в качестве прототипа, заключающийся в использовании процессора, кэш-памяти, основной памяти, разделении кэш-памяти на сегменты, закреплении сегментов за задачами, предохранении их от использования другими задачами, гарантировании сохранности содержимого в процессе работы операционной системы, определения размера каждого раздела кэш-памяти в зависимости от требований, возникающих во время выполнения задач (патент США №5875464, МПК G 06 F 12/08, приоритет от 18.03.1996).

Недостатками известного способа является то, что кэширующая логика используется неэффективно, т.к. распространяется на весь буфер кэш-памяти, тогда как реально в каждый момент может использоваться лишь малая его часть, выделение разделяемой между задачами части буфера кэш-памяти фиксированного размера не может быть эффективно на сколь-нибудь широком ряде задач, динамическое изменение разделяемой части значительно усложнит алгоритм динамического распределения буфера кэш-памяти так, что может вывести его из класса полиномиальных, механизм селекции данных по типу раздела буфера кэш-памяти, в который они должны попасть, не прописан, реализация данного механизма потребует существенных архитектурных изменений процессора, кэш-памяти и, возможно, компилятора, наличие работающей вполне традиционным образом разделяемой части буфера кэш-памяти подразумевает кэширование либо в пространстве физических адресов с отсутствием подкачки, либо в пространстве виртуальных адресов в узком классе систем с разделяемым между процессами виртуальным адресным пространством, одновременное функционирование разных частей буфера кэш-памяти и в виртуальном, и в физическом адресном пространстве приведет к очень большим архитектурным издержкам.

Известно устройство, состоящее из процессора с двоичными признаками, операционной системы, кэш-памяти с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналов доступа к кэш памяти, основной памяти, которое выполняет управление кэш-памятью, для использования в многопоточном процессоре. Устройство распределяет кэш-память между потоками многопоточного процессора. Когда необходимая линия в кэш-памяти не обнаружена, устройство выбирает линию замены из раздела кэш-памяти, который прикреплен к тому потоку, из которого произошло обращение, приведшее к данной ситуации, таким образом предотвращая порчу разделов, принадлежащих другим потокам (патент США №6381676, МПК G 06 F 12/08, приоритет от 07.12.2000).

Недостатками известного устройства являются невозможность работы в многопроцессорных системах, неэффективное использование кэширующей логики из-за распространения ее деятельности на весь буфер кэш-памяти, тогда как реально в каждый момент может использоваться лишь малая его часть, механизм динамического разбиения буфера кэш-памяти может привести к тому, что раз от раза одна и та же программа будет запускаться с разными по объему прикрепленными разделами кэш-памяти, что может сделать ее работу непрогнозируемой по скорости, отсутствие механизма сохранения и восстановления разделов кэш-памяти приведет к тому, что при большем количестве задач либо некоторым из них будет отказано в кэшировании, либо кэширование будет вестись в незначительном по объему разделе буфера, что неэффективно.

Известно также устройство, выбранное в качестве прототипа, состоящее из процессора, с двоичными признаками, операционной системы, кэш-памяти с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналов доступа к кэш-памяти, основной памяти, алгоритма распределения буфера кэш-памяти и набор регистров для хранения информации об распределении. С помощью алгоритма распределения буфер кэш-памяти разбивается на сегменты. В результате появляется группа личных разделов и разделяемый раздел, личные сегменты закрепляются за задачами, предохраняются от использования другими задачами, гарантируется сохранность их содержимого в процессе работы операционной системы, размер каждого раздела кэш-памяти определяется в зависимости от требований, возникающих во время выполнения задач (патент США №5875464, МПК G 06 F 12/08, приоритет от 18.03.1996).

Недостатками известного устройства является то, что кэширующая логика используется неэффективно, т.к. распространяется на весь буфер кэш-памяти, тогда как реально в каждый момент может использоваться лишь малая его часть, выделение разделяемой между задачами части буфера кэш-памяти фиксированного размера не может быть эффективно на сколь-нибудь широком ряде задач, динамическое изменение разделяемой части значительно усложнит алгоритм динамического распределения буфера кэш-памяти так, что может вывести его из класса полиномиальных, механизм селекции данных по типу раздела буфера кэш-памяти, в который они должны попасть, не прописан, реализация данного механизма потребует существенных архитектурных изменений процессора, кэш-памяти и, возможно, компилятора, наличие работающей вполне традиционным образом разделяемой части буфера кэш-памяти подразумевает кэширование либо в пространстве физических адресов с отсутствием подкачки, либо в пространстве виртуальных адресов в узком классе систем с разделяемым между процессами виртуальным адресным пространством, одновременное функционирование же разных частей буфера кэш-памяти и в виртуальном, и в физическом адресном пространстве приведет к очень большим архитектурным издержкам.

Перед авторами ставилась задача разработать способ и устройство для его осуществления, позволяющие оптимизировать работу подсистемы кэш-памяти в многозадачном и многопроцессорном режимах, минимизировать обмен данными, необходимый для поддержания когерентности кэш-памяти, минимизировать сложность всей подсистемы, минимизировать изменения в существующих аппаратных и программных средствах, необходимые для реализации описываемого метода.

Поставленная задача решается тем, что в способе организации персистентной кэш-памяти для многозадачных, в том числе симметричных многопроцессорных компьютерных систем, заключающийся в том, что используют процессор с регистром флагов процессора, кэш-память, основную память, операционную систему, разделяют буфер данных кэш-памяти на сегменты, закрепляют сегменты за задачами, предохраняют их от использования другими задачами, гарантируют сохранность содержимого в процессе работы операционной системы, разделение буфера данных кэш-памяти осуществляют на две равные части, одну из которых в каждый момент назначают в качестве активной, а вторую в качестве пассивной, при смене задачи наоборот, активную назначают пассивной, а пассивную - активной, ведут кэширование в виртуальном адресном пространстве, назначают активной части буфера данных режим прямой адресации, содержимое части буфера данных старой задачи сохраняют в основную память независимо от процессора, а содержимое части буфера данных новой задачи предварительно восстанавливают из основной памяти, также независимо от процессора, приводят содержащиеся в восстанавливаемой части буфера данных новой задачи глобальные данные в соответствие со значениями, которые были изменены другими задачами. Назначают часть буфера данных кэш-памяти в качестве активной или пассивной с помощью соответствующего битового флага управляющего регистра процессора. Процессы сохранения и восстановления данных осуществляют из пассивной части, используя более одного независимого канала прямого доступа к памяти, а в пассивную с возможностью их перекрытия по времени с достаточным для исключения их столкновения временным сдвигом. Кроме того, сохранение данных из пассивной части буфера данных осуществляют в структуру описания задачи в ядре операционной системы. Глобальные данные, содержащиеся в восстанавливаемой части буфера данных новой задачи, приводят в соответствие со значениями, которые были изменены другими задачами, используя алгоритм разделения данных на глобальные и локальные, размещают глобальные данные при загрузке процесса операционной системой в сегменты основной памяти, которым присваивают виртуальные адреса в соответствии с алгоритмом разделения данных на глобальные и локальные. В момент запроса процессором глобальных данных, отсутствующих в активной части буфера данных, производят их выборку из основной памяти, размещение в активной части буфера данных и регистрацию в блоке управления глобальными данными, при этом используют страницу глобальных данных, реализованную как ассоциативную память, управляемую блоком управления глобальными данными. Используют предоставляемое процессором значение, идентифицирующее процесс текущей задачи, в качестве расширения виртуального адреса глобальных данных и регистрируют глобальные данные в странице глобальных данных с использованием этого расширенного адреса. При переполнении страницы глобальных данных замещают старое глобальное значение, удаляют его из страницы глобальных данных и отменяют его регистрацию. При удалении значения из страницы глобальных данных это значение также удаляют из активной части буфера данных и из пассивной части буфера данных, если это значение было восстановлено из основной памяти для последующей задачи. В момент восстановления данных из основной памяти в пассивную часть буфера данных, данные, которые распознают как глобальные, приводят в соответствие со значениями из страницы глобальных данных. При восстановлении данных в пассивную часть буфера данных какое-либо глобальное данное не находят в странице глобальных данных, это значение игнорируют так, что оно не попадает в пассивную часть буфера данных. При изменении глобального значения в активной части буфера данных меняют соответствующее значение в странице глобальных данных и в пассивной части буфера данных, если это значение было восстановлено из основной памяти для последующей задачи. В случае многопроцессорной системы протокол поддержки распределенных транзакций для поддержания общесистемной когерентности реализуют, используя блок управления глобальными данными. Функционирование кэш-памяти приостанавливают при изменении соответствующего битового флага управляющего регистра процессора. Кэширование глобальных данных приостанавливают при изменении соответствующего битового флага управляющего регистра процессора. Активную часть буфера данных переводят в режим прямой адресации при изменении соответствующего битового флага управляющего регистра процессора. При компиляции временные значения предназначают для размещения в активной части буфера данных, находящейся в режиме прямой адресации. Размещают стек задачи в активной части буфера данных, находящейся в режиме прямой адресации. При переполнении активной части буфера данных выделяют дополнительное место в основной памяти и обеспечивают функционирование активной части буфера данных в качестве окна ускоренного доступа к содержимому стека. Присваивают глобальным данным, разделяемым между процессами, виртуальные адреса, однозначно соответствующие физическим, и обеспечивают отсутствие их подкачки. Разделяют активную часть буфера данных произвольным образом на части и обеспечивают их независимое сохранение и восстановление. Делят активную часть буфера данных на две части, одну из которых сохраняют и восстанавливают при смене задачи, а вторую при смене процесса.

А устройство для организации персистентной кэш-памяти для многозадачных, в том числе симметричных многопроцессорных компьютерных систем, включающее процессор с регистром флагов, выполненный идентифицирующим текущий процесс, операционную систему, кэш-память, с выделенным блоком управления кэш-памятью и сегментированным буфером данных, каналы доступа к кэш-памяти, основную память, дополнительно снабжено блоком управления глобальными данными, с заложенным алгоритмом разделения данных на локальные и глобальные, соединенным с сегментированным буфером данных и каналами доступа к основной памяти, компилятором, модифицированным для учета особенностей работы кэш-памяти, а также страницей глобальных данных, используемой только блоком управления глобальными данными, буфер данных кэш-памяти выполнен разделенным на две части таким образом, что одна из них в каждый момент назначается в качестве активной, а вторая в качестве пассивной, блок управления кэш-памятью выполнен с возможностью работать в каждый момент только с активной частью буфера данных кэш-памяти как в пространстве виртуальных адресов, так и в режиме прямой адресации, операционная система выполнена модифицированной так, чтобы поддерживать переключение страниц буфера данных и своевременную загрузку и выгрузку пассивной страницы буфера данных. Кроме того, буфер данных выполнен с возможностью хранения истории переходов вместе с инструкциями, кэш-память организована иерархически и выполнена работающей одновременно с данными и с инструкциями, кэш-память выполнена с возможностью приостановления при установке соответствующего значения соответствующего флага регистра управления процессором. Активный или пассивный статус части буфера кэш-памяти определяется значением соответствующего битового флага управляющего регистра процессора. Операционная система выполнена содержащей загрузчик задач, с заложенным алгоритмом, согласно которому размещают глобальные данные в сегменты основной памяти, которым присваивают виртуальные адреса в соответствии с алгоритмом разделения данных на глобальные и локальные. Блок управления глобальными данными выполнен с возможностью регистрации глобальных данных, которая реализована через использование страницы глобальных данных в качестве хранилища регистрационных данных. Страница глобальных данных реализована в виде ассоциативной памяти. Кроме того, процессор выполнен с возможностью идентификации процесса текущей задачи, страница глобальных данных выполнена с возможностью использования идентификатора процесса текущей задачи в качестве расширителя виртуального адреса при работе с глобальными данными. Блок управления глобальными данными выполнен с возможностью изменения соответствующего значения в глобальной странице, в случае изменения глобального значения в активной части буфера данных, с возможностью удаления соответствующего значения из активной и пассивной частей буфера данных в случае удаления значения из страницы глобальных данных, с возможностью сохранения содержимого пассивной части буфера данных в основную память через каналы прямого доступа к памяти, с возможностью восстановления содержимого пассивной части буфера данных из основной памяти через каналы прямого доступа к памяти, с возможностью согласования процессов сохранения и восстановления данных в пассивной части буфера данных, позволяющий им работать параллельно, с временным сдвигом, достаточным для предотвращения искажения данных, выполнен с возможностью приведения глобальных данных во время восстановления пассивной части буфера данных в соответствие с содержимым страницы глобальных данных. Операционная система выполнена содержащей в ядре, в структуре описания задачи, место, достаточное для размещения содержимого пассивной части буфера данных. В случае многопроцессорной системы блок управления глобальными данными выполнен с возможностью реализации протокола поддержки когерентности глобальных данных в масштабах всей вычислительной системы. Процессор выполнен с управляющим регистром, содержащим битовый флаг процессора, одно из значений которого означает приостановление кэширования глобальных данных, а так же с управляющим регистром, содержащим битовый флаг процессора, одно из значений которого означает, что блок управления кэш-памятью перестает кэшировать данные и делает активную часть буфера данных прямо адресуемой, при этом продолжают действовать операции сохранения и восстановления данных в пассивную часть буфера данных и переключение частей буфера данных. Компилятор, учитывающий особенности кэш-памяти, выполнен содержащим алгоритм размещения временных значений в активной части буфера данных в режиме прямой адресации. Процессор выполнен с возможностью осуществлять режим размещения верхней части стека в активной части буфера данных в режиме прямой адресации, с возможностью исключения при исчерпании и переполнении стека в случае его размещения в активной части буфера данных. Операционная система выполнена содержащей обработчик исключения, обеспечивающий дальнейшее корректное функционирование системы, кроме того, ядро операционной системы выполнено с возможностью обеспечения однозначного соответствия физических и виртуальных адресов для глобальных данных, разделяемых между процессами, и отсутствие их подкачки. Блок управления кэш-памятью выполнен с возможностью разбиения произвольным образом активную часть буфера данных на части сохранения и восстановления в них данных независимо друг от друга. Активная часть буфера данных выполнена разбитой на две части, содержимое одной из которых сохраняется и восстанавливается при смене задачи, а второй - при смене процесса.

Технический эффект заявляемого устройства заключается в возможности существенно упростить конструкцию кэш-памяти при не худшей производительности, сделать более предсказуемым поведение выполняемых программ, существенно уменьшить объем трафика, необходимого многопроцессорной системе для поддержания когерентности и тем самым увеличить верхний предел числа процессоров в такой системе, возможности реализовывать схемы компиляции с использованием личных областей сверхоперативной памяти.

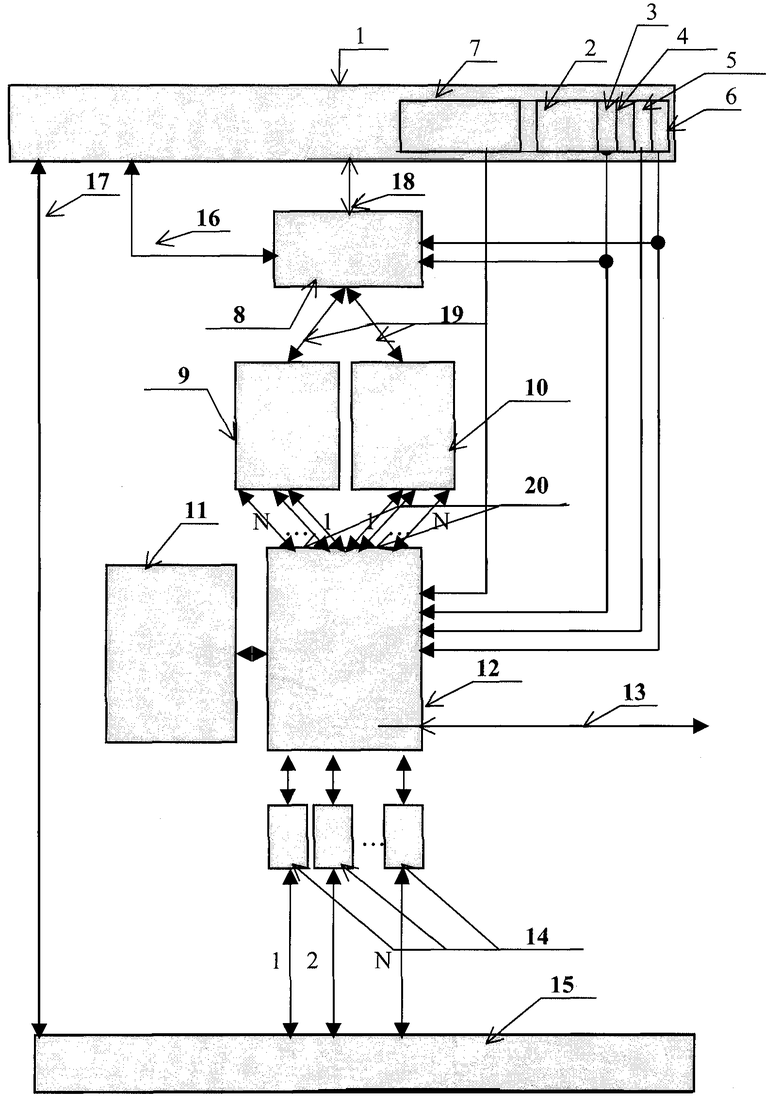

Изобретение поясняется чертежом, на котором представлена блок-схема одного из вариантов осуществления заявляемого способа.

Схема включает 1 - процессор, 2 - регистр флагов процессора, 3 - флаг, указывающий активность страницы буфера данных, 4 - флаг, запрещающий или разрешающий деятельность кэш-памяти, 5 - флаг, запрещающий или разрешающий кэширование глобальных данных, 6 - флаг, запрещающий или разрешающий прямую адресацию активной страницы буфера данных, 7 - регистр процессора, идентифицирующий процесс текущей задачи, 8 - блок управления буфером данных, 9 - первая часть буфера данных, 10 - вторая часть буфера данных, 11 - страница глобальных данных, 12 - блок управления глобальными данными, 13 - интерфейс с менеджером глобальных транзакций, 14.1 - первый канал прямого доступа к памяти (ПДП), 14.2 - второй канал ПДП,..., 14.N - N-й канал ПДП, 15 - основная память, 16 - традиционный интерфейс блока управления буфером данных к основной памяти, через который идет обмен данными при работе кэш-памяти, не связанной с переключением страниц, 17 - интерфейс между процессором и основной памятью, задействованный при отключенной кэш-памяти, 18 - интерфейс между процессором и кэш-памятью, действующий, когда кэширование разрешено, 19 - путь данных между активной страницей буфера данных и блоком управления буфером, физически его направление зависит от флага (3), 20 - путь данных, состоящий из N независимых каналов от пассивной страницы буфера данных к блоку управления глобальными данными и обратно, физически его направление зависит от флага (3).

Заявляемое изобретение работает следующим образом.

В идеале память должна обеспечивать процессор данными таким образом, чтобы избежать простоев в ожидании данных. К сожалению, не придуманы еще методы компиляции, способные обеспечить надлежащий транспорт данных. В современных вычислительных системах уменьшение времени доступа достигается введением иерархического устройства памяти, когда каждый следующий уровень памяти больше и медленнее предшествующего, при этом адресуемым является лишь самый верхний уровень, а остальные запоминают в соответствии с некоторой стратегией последние обращения к данным и способны выдавать их быстрее, чем это делают вышестоящие уровни. Размер кэш-памяти первого уровня типично равен 8К слов (у НР8500 - 1.5 мегабайта), второго и третьего (если есть) - значительно больше.

Когда инструкция в качестве операнда содержит виртуальный адрес памяти, этот адрес преобразуется в физический. По физическому адресу запрашиваются данные из памяти, если такие данные уже содержатся в кэш-памяти, процессор получает их быстрее. Зададимся вопросом, почему кэш работает с физическими адресами? Проблема в том, что адресные пространства, предоставляемые современными операционными системами задачам, могут пересекаться. Можно было бы расширить виртуальный адрес с помощью идентификатора задачи и преобразовывать адрес в физический лишь после неуспеха поиска в кэш-памяти, но это приведет к фактическому удвоению тега строк кэш-памяти и существенному усложнению устройства кэш-памяти всего лишь при небольшой экономии в преобразованиях адресов. Кроме того, преобразование адреса выполняется процессором, тогда как старшие уровни кэш-памяти обычно из процессора вынесены. Недостатки существующего подхода очевидны и большей частью заключаются в совместном использовании кэш-памяти всеми выполняющимися задачами. При любой стратегии вытеснения старых данных, после потери задачей управления и его возврате после работы десятка других задач, личное содержимое кэш-памяти можно считать потерянным, и приходится начинать собирать его заново, возникает так называемая проблема холодного старта. При нормальном числе одновременно работающих задач, измеряемом десятками или даже сотнями, для того, чтобы сохранить хоть часть личных данных, приходится делать кэш-память чудовищных размеров. Еще одна проблема связана с подкачкой. Если при преобразовании адреса оказывается, что страница с таким виртуальным адресом отсутствует в физической памяти, она будет подгружена, при этом вытеснив какую-то другую. Очевидно, все линии кэш-памяти, ссылающиеся на предыдущую страницу, должны быть аннулированы. Преимущества существующего подхода иногда оказываются спорными. Ускоряется среднее время доступа к памяти, особенно при последовательном и локализованном обращении. При любом отличном от этого поведении программа не должна рассчитывать на помощь со стороны кэш-памяти. При этом иногда такое "среднее" поведение кэш-памяти играет с программами дурную шутку, теряется смысл заботиться о "красоте" алгоритмов и пытаться оптимизировать программу вручную - кэш-память всех подстрижет под одну гребенку, и, часто, "плохо" написанный код в результате работает быстрее "хорошего", что, согласимся, не очень правильно. Попытки же использовать особенности кэш-памяти при оптимизации программ приводят к потере переносимости кода даже между версиями одного процессора. Предпринимаются попытки сделать поведение кэш-памяти более предсказуемым, например, в виде загрузки данных по предположению. Так, компилятор добавляет команды загрузки данных в кэш-память до того, как они могут реально понадобиться (SPARC V9, IBM POWER3 и HP PA-8xxx). He менее полезной является возможность принудительно инвалидировать линию кэш-памяти, если ее данные заведомо не пригодятся в ближайшем будущем. Некоторые системы (TMS320C6xxx) позволяют конфигурировать кэш-память как прямо адресуемую сверхоперативную память, но в такой ситуации возникают существенные трудности с ее совместным использованием различными задачами.

Отдельных слов заслуживает проблема поддержания идентичности (когерентности) кэш-памяти при совместном использовании памяти несколькими процессорами. Поскольку когерентность поддерживается с помощью межмодульных пересылок, а количество пересылок существенно нелинейно по отношению к числу процессоров в системе, объективно существует предел сверху числа процессоров. Отметим, что большая часть упомянутых пересылок является бесполезной, т.к. в дальнейшем не будет использована, но это издержки кэширования как такового и, частично, плата за кэширование в физических адресах, порождающее излишние зависимости между процессорными модулями. И если бы при прочих равных нам удалось избавиться от заведомо бесполезных пересылок, это позволило бы существенно поднять предел числа процессоров.

Теперь обратимся к сути данного изобретения. Основными идеями являются разделение данных на глобальные и локальные, которое может быть сделано на основании значения виртуального адреса, кэширование в виртуальном адресном пространстве, ситуация, когда каждая задача работает со своей кэш-памятью, при этом в отношении локальных данных постороннее влияние исключено, буфер данных кэш-памяти разбит на две равные страницы, при смене задач происходит переключение страниц, причем новая задача немедленно продолжает выполнение с одной страницей, а из второй страницы в фоновом режиме выгружаются старые данные и загружаются новые, глобальные данные кэшируются с тегом, расширенным идентификатором, предоставляемым операционной системой, например, номером процесса текущей задачи.

Пусть вычислительная система содержит не менее одного процессора (см.чертеж). Пусть вычислительная система предназначена для параллельного выполнения ряда процессов, каждый из которых может содержать более одной параллельно выполняющейся задачи (thread). Данные, доступ к которым имеет лишь одна задача, мы будем называть локальными, а данные, к которым имеют доступ все задачи некоторого процесса, глобальными. Разделение данных между процессами допускают, но требуют особой обработки, например, такие данные размещают в некэшируемые сегменты основной памяти, не подвергают подкачке или доступ к ним осуществляют через системные вызовы.

Выполняют загрузчик операционной системы, предназначенный для создания образа программы в основной памяти таким образом, что он размещает глобальные данные процесса в сегменты памяти с легко идентифицируемыми виртуальными адресами, например результат операции битового '&' должен быть истинным при сочетании адреса с некоторой битовой маской, которая может быть задана как аппаратно, так и программно. Ядро операционной системы, далее называемое как ядро, назначают ответственным за планирование задач по процессорам и их переключение.

Каждый процессор 1 в вычислительной системе выполняют содержащим одинаковую по размеру и одинаково устроенную локальную кэш-память и аппаратуру для работы с ней, в дальнейшем именуемую как кэш. Кэш выполняют состоящим из ряда логических блоков, как то две равные по размеру страницы данных - первую и вторую части буфера данных 9, 10, одна из которых (в каждый конкретный момент, на протяжении интервала времени обе части могут взаимоисключающе менять статус) в дальнейшем будет называться активной, другая теневой (пассивной) страницей, блок управления буфером данных 8, блок управления глобальными данными 12, страницу глобальных данных 11, не менее одного канала прямого доступа к памяти (ПДП) 14. В зависимости от реализации, кэш-памяти данных и команд могут быть расположены как на одной (как на активной, так и на теневой) странице, используя общие пути данных (каналы ПДП 14, путь данных между активной страницей буфера данных и блоком управления буфером 19, путь от пассивной страницы буфера данных к блоку управления глобальными данными и обратно 20), так и на разных, полностью или частично дублируя весь описываемый механизм кэш-памяти. Блок управления буфером данных 8 выполняют реализующим одну из известных стратегий и алгоритм кэширования, например он может быть полностью ассоциативным со сквозной буферизованной записью и LRU вытеснением. Блок управления глобальными данными 12 выполняют предназначенным для поддержания их когерентности как внутри процессорного модуля вычислительной системы, так и в масштабах всей вычислительной системы. Страницу глобальных данных 11 разделяют между всеми задачами, но эта страница не обязана совпадать по размеру с локальными страницами и используется непосредственно блоком управления глобальными данными в качестве ассоциативной памяти. Каналы прямого доступа к памяти 14 предназначают для копирования данных из кэш-памяти и обратно в кэш, причем каждый из имеющихся каналов работает независимо, в каждый конкретный момент со своей и только своей областью теневой страницы кэш-памяти.

Активную страницу кэш-памяти выделяют для использования активной в данный момент задачей, причем содержимое этой страницы является контекстом кэш-памяти этой задачи. Ядро выполняют содержащим механизм сохранения контекста кэш-памяти предыдущей задачи из теневой страницы и загрузки контекста кэш-памяти следующей задачи туда же. В момент смены активной задачи ядром производят обращение страниц кэш-памяти, т.е. активная страница становится теневой, а теневая - активной, для этого используют соответствующий флаг регистра флагов 3, инверсия значения которого приводит к соответствующему изменению работы кэш-памяти, значение этого признака может меняться как аппаратным, так и программным путем. К этому моменту теневая страница должна содержать полностью загруженный ядром контекст кэш-памяти новой активной задачи. Сразу после смены активной задачи ядром, начинают сохранять контекст кэш-памяти из новой теневой страницы. После того, как ядро выберет следующую задачу для исполнения на данном процессоре, ее начинают загружать в теневую страницу контекст кэш-памяти этой новой задачи. Загрузку и выгрузку содержимого теневой страницы имеют возможность производить одновременно со сдвигом по времени, достаточным для исключения их столкновения.

При занесении линии в страницу глобальных данных 11 в качестве тега используют виртуальный адрес, расширенный предоставляемым операционной системой идентификатором, например номером процесса текущей задачи, что делает этот виртуальный адрес уникальным в масштабах всей вычислительной системы. Идентификатор берут из механизма процессора идентифицирующий процесс текущей задачи 7, задаваемого операционной системой. В момент запроса процессором 1 глобальных данных, отсутствующих в странице глобальных данных 11, производят их выборку из основной памяти 15, размещение в активной странице и регистрацию в глобальной странице 11. В случае, когда глобальная страница 11 переполнена, действия зависят от реализации, например данному значению отказывают в кэшировании или вытесняют им другое глобальное значение одновременно из активной и глобальной страниц, важно лишь, чтобы все глобальные данные локальных страниц были синхронны со значениями из глобальной страницы. В процессе загрузки кэш-памятью данных блоком управления глобальными данными 12 пропускают без изменения локальные данные и замещают устаревшие глобальные данные актуальными значениями. В случае многопроцессорной системы блок управления глобальными данными 12 делают реализующим подходящий протокол поддержки распределенных транзакций (с помощью интерфейса с менеджером глобальных транзакций 13) для поддержания общесистемной когерентности кэш-памяти. Совпадает ли содержимое глобальных страниц кэш-памяти 11 разных процессорных модулей, зависит от реализации менеджером распределенных транзакций, доступного через интерфейс 13.

Контекст кэш-памяти каждой задачи хранят в структуре ядра, описывающей поведение данной задачи.

Функционирование кэш-памяти может быть приостанавлено изменением значения еще флага регистра флагов процессора 4. Функционирование кэш-памяти в отношении глобальных данных приостанавливают изменением значения еще одного флага регистра флагов процессора 5. При возникновении в процессоре 1 аппаратного прерывания, например в случае отсутствия нужной страницы в основной памяти 15, приостанавливают деятельность кэш-памяти вплоть до выхода этого процессора из режима прерывания.

Активную страницу выполняют дополнительно имеющей режим прямой адресации, который можно включить/выключить с помощью двоичного признака №4. Таким образом, каждой задаче при желании вместо буфера кэш-памяти (или его части) выделяют собственную область сверхоперативной памяти.

Что дает нам такая организация? Первое, сверхоперативная память может иметь либо собственное адресное пространство и собственные инструкции для доступа, либо иметь выделенную в виртуальном адресном пространстве область адресов. В любом случае, наличие такой памяти никак не учитывается в языках высокого уровня. Одним из объективных методов ее использования можно считать использование такой памяти компилятором для хранения временных переменных, возникающих при генерации кода. Увы, при генерации кода никогда не возникает потребности хранить тысячи временных переменных, поэтому необходимы области применения оставшейся сверхоперативной памяти. Существует, как минимум, три варианта. Первый - размещение в этой памяти стека. Действительно, в стеке оказываются локальные переменные (и временные в том числе), принадлежащие только данной задаче (в традиционной схеме одна задача может передать другой адрес переменной из своего стека, но подобная техника является скорее ошибкой проектирования и создает больше проблем, чем их решает), эти данные сильно локализованы, кэширование вершины стека всегда актуально, объем актуальной для кэширования вершины стека (объем локальных данных в последних 2-3 вызовах процедур) обычно не очень велик. При переполнении стека происходит исключение, операционная система выделяет дополнительный буфер для сохранения при переключении задачи и сдвигает данные так, что буфер кэш-памяти выступает в роли окна ускоренного доступа. Если происходит обращение за пределы этого окна, то при преобразовании виртуального адреса в физический выдается адрес, соответствующий нужному месту в образе стека данной задачи в основной памяти. Второй способ использования сверхоперативной памяти заключается в явном обращении за этой памятью к операционной системе и ручным управлением ее содержимым. Третий способ предполагает внесение изменений в языки высокого уровня и/или разработку новых методов компиляции с учетом особенностей архитектуры. Особенно актуально это для архитектур с явным параллелизмом уровня команд (ILP), где кэширование как таковое может оказаться недопустимым, т.к. делает поведение системы непредсказуемым.

Второе, явное разделение данных на глобальные и локальные позволяет программисту явно контролировать межпроцессорные пересылки, необходимые для поддержания когерентности системы. Возможен весь спектр, если мы запрещаем кэширование глобальных данных, синхронизация осуществляется на уровне доступа к физической памяти - не такой уж плохой вариант, если таких данных мало, а если глобальных данных вообще нет, то поддержка когерентности как таковая просто не нужна. Если же все данные глобальные, мы имеем примерно ту же ситуацию, что и в традиционной системе с кэшированием физических адресов. Здесь важно, чтобы программист всегда отдавал себе отчет, с какими именно данными он работает, и имел возможность выбора, например, в виде двух системных вызовов выделения памяти - локальной и разделяемой.

Третье, в сохраняемый контекст задачи могут быть включены и некоторые дополнительные данные как, например, таблица историй переходов и кэш физических адресов (TLB). Некоторые системы хранят таблицу историй переходов вместе с кэш-памятью инструкций, в любом случае наличие такой личной таблицы позволит без особых издержек (в MIPS R10000 такая таблица содержит 512 элементов) повысить вероятность правильного предсказания перехода для спекулятивного выполнения. Типичный размер TLB - сотни записей. Его также не составит труда разместить в сохраняемом контексте задачи с тем лишь отличием, что при подкачке страниц операционная система должна следить за тем, чтобы содержимое TLB выгруженных и неактивных в данный момент задач продолжало соответствовать действительности, впрочем, это совершенно не обременительно, т.к. даже линейный поиск в таблице из сотни пар ничто по сравнению с обращением к диску.

Преимущества заявляемого способа и устройства для его осуществления заключаются в более эффективном использовании кэширующей логики, т.к. распространяется не на весь буфер кэш-памяти, а лишь на реально используемую его часть, разделяемые данные обрабатываются аналогично личным данным задачи, и их соотношение объективно определяется поведением задачи, а не настройками операционной системы, кэширование производится в пространстве виртуальных адресов, что позволяет максимально изолировать задачи друг от друга, явное разделение данных задачи на глобальные и локальные позволяет управлять потоком межпроцессорных пересылок и создавать вычислительные системы с большей степенью параллелизма.

Изобретение относится к области оптимизации производительности компьютерных систем. Его использование позволяет получить технический результат в виде ускорения работы подсистемы оперативной памяти и повышения ее пропускной способности. Этот технический результат достигается благодаря тому, что буфер данных кэш-памяти разделяют на две равные страницы, одну из которых в каждый момент назначают в качестве активной, а вторую в качестве пассивной, а при смене задачи - наоборот, кэширование ведут в виртуальном адресном пространстве, назначают активной части буфера данных режим прямой адресации, содержимое части буфера данных старой задачи сохраняют в основную память независимо от процессора, а содержимое части буфера данных новой задачи предварительно восстанавливают независимо от процессора из основной памяти, приводят содержащиеся в восстанавливаемой части буфера данных новой задачи глобальные данные в соответствие со значениями, которые были изменены другими задачами, с помощью блока управления глобальными данными. 2 н. и 52 з.п.ф-лы, 1 ил.

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| Преобразователь перемещения в количество и ширину импульсов | 1972 |

|

SU447736A1 |

| US 6101589 A, 08.08.2000 | |||

| РЕГУЛИРУЕМАЯ ПО ВЫСОТЕ ТРОСТЬ | 1991 |

|

RU2010547C1 |

| МНОГОПРОЦЕССОРНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА С КОГЕРЕНТНОЙ КЭШ С УМЕНЬШЕННЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ | 1995 |

|

RU2171490C2 |

| СИСТЕМА И СПОСОБ ЭФФЕКТИВНОГО ИСПОЛЬЗОВАНИЯ КЭШ-ПАМЯТИ В РАСПРЕДЕЛЕННОЙ ФАЙЛОВОЙ СИСТЕМЕ | 1994 |

|

RU2170454C2 |

| ЦИРКУЛЯЦИОННЫЙ КЛАПАН | 2001 |

|

RU2206714C2 |

| US 5907678 A, 25.05.1999 | |||

| US 5875464 A, 23.02.1999. | |||

Авторы

Даты

2004-10-20—Публикация

2002-07-31—Подача