Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления и др.

Известны адресные идентификаторы (см., например, патент РФ 2143740, кл. G06G 7/25, 1999 г.), которые выполняют адресную идентификацию минимального или максимального из трех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных адресных идентификаторов, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется адресная идентификация медианного из трех входных аналоговых сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип адресный идентификатор (фиг.3 в описании изобретения к авт. св. СССР 1478233, кл. G06G 7/25, 1989 г.), который содержит три компаратора, пять переключателей и выполняет адресную идентификацию медианного из трех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется адресная идентификация минимального или максимального из трех входных аналоговых сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения выполнения адресной идентификации минимального, медианного или максимального из трех входных аналоговых сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в адресном идентификаторе, содержащем три компаратора и пять переключателей, у которых неинвертирующий, инвертирующий входы третьего компаратора и коммутационный, нормально разомкнутый контакты третьего переключателя соединены соответственно с вторым, третьим входами и выходом адресного идентификатора, коммутационным контактом второго переключателя, особенность заключается в том, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем объединенные вторые входы второго, четвертого и объединенные вторые входы первого, третьего, пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым настроечными входами адресного идентификатора, первый вход и выход i-го

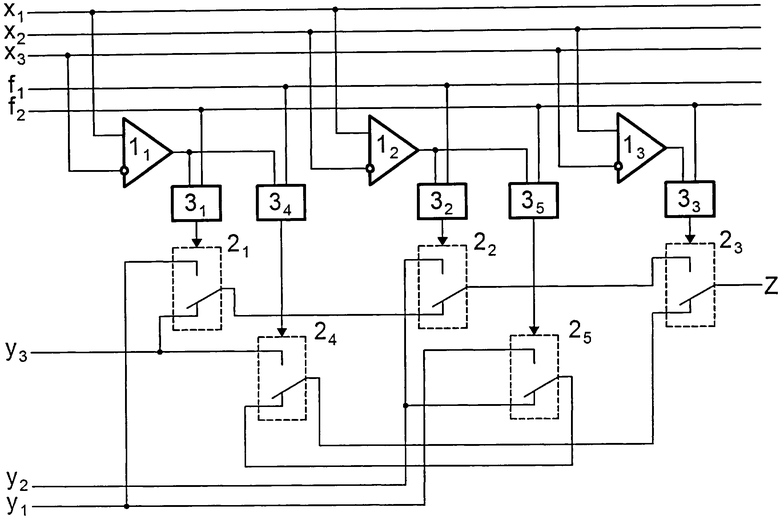

На фиг. представлена схема предлагаемого адресного идентификатора.

Адресный идентификатор содержит компараторы 11,…,13, переключатели 21,…,25 и элементы исключающее или 31,…,35, причем неинвертирующий, инвертирующий входы компаратора 13 и коммутационный, нормально разомкнутый контакты переключателя 23 соединены соответственно с вторым, третьим входами и выходом адресного идентификатора, коммутационным контактом переключателя 22, объединенные вторые входы элементов 33, 34 и объединенные вторые входы элементов 31, 33, 35 соединены соответственно с первым и вторым настроечными входами адресного идентификатора, первый вход и выход элемента 3i

Работа предлагаемого адресного идентификатора осуществляется следующим образом. На его первый, второй, третий входы и первый, второй, третий идентифицирующие входы подаются соответственно аналоговые сигналы (напряжения) x1, x2, x3 и y1, y2, y3; на его первом, втором настроечных входах фиксируются соответственно необходимые управляющие сигналы f1f2∈{0,1}. Если на управляющем входе переключателя 2k

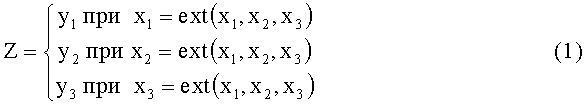

где ext=min при f1=0 и f2=1, ext=med при f1=f2=0, ext=max при f1=1 и f2=0. Согласно (1), номер i ∈{1, 2, 3} сигнала yi, прошедшего на выход предлагаемого идентификатора, соответствует адресу экстремального сигнала в кортеже (x1, x2, x3).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый адресный идентификатор обладает более широкими по сравнению с прототипом функциональными возможностями, так как выполняет адресную идентификацию минимального, медианного или максимального из трех входных аналоговых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 2015 |

|

RU2580802C1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ, СЕЛЕКЦИИ И РАНЖИРОВАНИЯ ТРЕХ АНАЛОГОВЫХ СИГНАЛОВ | 1999 |

|

RU2149450C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2013 |

|

RU2518664C1 |

| РЕЛЯТОРНЫЙ КОММУТАТОР АНАЛОГОВЫХ СИГНАЛОВ С АДРЕСНЫМ УПРАВЛЕНИЕМ | 2004 |

|

RU2256220C1 |

| РЕЛЯТОРНЫЙ КОММУТАТОР | 1996 |

|

RU2103735C1 |

| ИНТЕРВАЛЬНЫЙ ИДЕНТИФИКАТОР | 2009 |

|

RU2417434C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2143740C1 |

| АНАЛОГОВЫЙ СЕЛЕКТОР | 2013 |

|

RU2514786C1 |

| РАНГОВЫЙ ФИЛЬТР | 2013 |

|

RU2518642C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2143735C1 |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано в системах аналоговой вычислительной техники как средство предварительной обработки информации. Техническим результатом является расширение функциональных возможностей адресного идентификатора за счет обеспечения выполнения адресной идентификации минимального, медианного или максимального из трех входных аналоговых сигналов. Устройство содержит три компаратора, пять переключателей, пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. 1 ил., 1 табл.

Адресный идентификатор, содержащий три компаратора и пять переключателей, у которых неинвертирующий, инвертирующий входы третьего компаратора и коммутационный, нормально разомкнутый контакты третьего переключателя соединены соответственно с вторым, третьим входами и выходом адресного идентификатора, коммутационным контактом второго переключателя, отличающийся тем, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем объединенные вторые входы второго, четвертого и объединенные вторые входы первого, третьего, пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым настроечными входами адресного идентификатора, первый вход и выход i-го

| РАНГОВЫЙ КОММУТАТОР | 2001 |

|

RU2195700C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2143740C1 |

| Аналоговый мультиплексор-демультиплексор | 1987 |

|

SU1478233A1 |

| US 6188251 B1, 13.02.2001 | |||

| JP 7160793 A, 23.06.1995. | |||

Авторы

Даты

2013-08-27—Публикация

2012-07-03—Подача