Изобретение относится к аналоговой вычислительной технике и автоматике и может быть использовано в аналоговых вычислительных машинах и устройствах автоматики и управления для адресно-ранговой идентификации, селекции и ранжирования трех аналоговых сигналов, для допускового контроля параметров, представленных аналоговыми сигналами, в качестве медицинского фильтра и др.

Известны устройства для ранжирования трех аналоговых сигналов, построенные на трех минимаксных реляторах (см., например, авт. св. 1365099, G 06 G 7/12, фиг. 2). Известные устройства обладают ограниченными функциональными возможностями, так как не воспроизводят адресную идентификацию информационных входов, на которых воздействуют ранжированные сигналы.

Наиболее близким к предлагаемому схемному решению является устройство для ранжирования трех аналоговых сигналов, построенное на трех четырехканальных и трех трехканальных реляторах (авт.св. 1541636, 5 G 06 G 7/25, фиг. 1). Указанный прототип обладает теми же функциональными возможностями, но имеет аппаратурную избыточность.

Цель изобретения - уменьшение аппаратурных затрат при сохранении всех функций, воспроизводимых прототипом.

Указанный технический результат при осуществлении изобретения достигается тем, что в известном устройстве используются три четырехканальных и три трехканальных релятора, каждый из которых состоит из компаратора, который управляет состоянием размыкающего и замыкающего ключей в переключательных каналах релятора, а неинвертирующие и инвертирующие входы компараторов реляторов в различных попарных сочетаниях, присоединяются к каналам информационной шины, на входы которых подаются идентифицируемые аналоговые сигналы x1, x2 и x3.

Особенность предложенного схемного решения заключается в том, что инвертирующие и неинвертирующие входы компараторов первого, второго и третьего реляторов соединены соответственно со вторым и первым, с третьим и первым, с третьим и вторым каналами информационной шины, первый, второй и третий реляторы содержат соответственно по два, три и четыре переключательных канала, входные выводы ключей в каждом канале всех реляторов соединены и образуют переключательные входы реляторов, второй и третий выходы второго, второй и третий, шестой и седьмой выходы третьего реляторов попарно объединены. При работе в режиме адресно-ранговой идентификации первый, второй и третий каналы идентифицирующей шины соединены соответственно с первым и вторым переключательными входами первого и третьим переключательным входом второго реляторов, первый и второй, третий и четвертый выходы первого релятора соединены соответственно с первым и вторым переключательными входами второго релятора и с четвертым и третьим переключательными входами третьего релятора, пятый и шестой выходы второго релятора соединены соответственно со вторым и первым входами третьего релятора, первый, объединенные второй и третий, четвертый выходы второго релятора соединены соответственно с третьим, вторым и первым каналами первой адресной шины Z1, пятый, объединенные шестой и седьмой, восьмой выходы третьего релятора соединены соответственно с третьим, вторым и первым каналами второй адресной шины Z2, а первый, объединенные второй и третий, четвертый выходы третьего релятора соединены соответственно с третьим, вторым и первым каналами третьей адресной шины Z3, в режиме адресно-ранговой селекции идентифицируемых сигналов первый, второй и третий каналы информационной шины соединены соответственно с первым, вторым и третьим каналами идентифицирующей шины, при этом в режиме ранжирования первые каналы первой, второй и третьей адресных шин присоединены к первому каналу ранжирующей шины, вторые каналы первой, второй и третьей адресных шин присоединены ко второму каналу ранжирующей шины, а третьи каналы адресных шин присоединены к третьему каналу ранжирующей шины, причем при работе в режиме адресно-ранговой селекции соединение информационной и идентифицирующей шин осуществляется на входном наборном поле X•Y, а соединение группы адресных шин Z1, Z2, Z3 и ранжирующей шины Z осуществляется на выходных наборных полях Z1•Z,Z2•Z,Z3•Z.

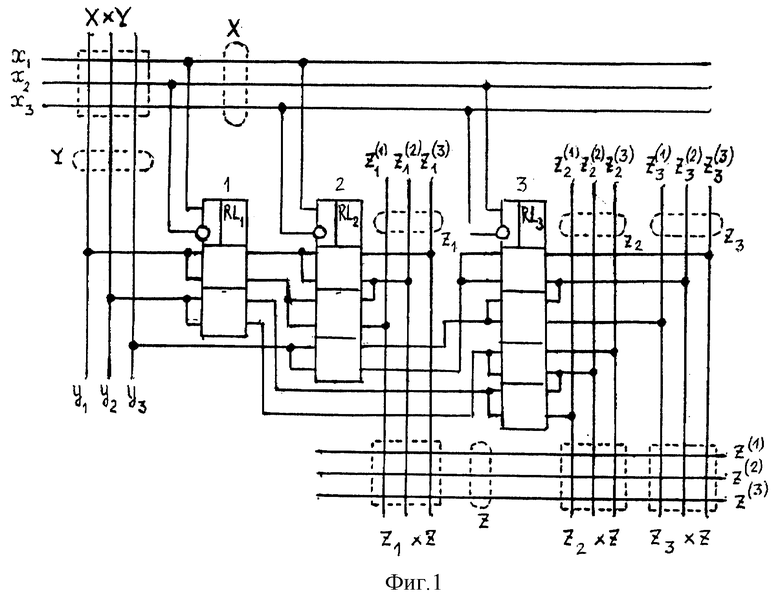

На фиг. 1 представлена базовая схема реляторного процессора, построенного на реляторах 1, 2, 3 в режиме адресно-ранговой идентификации;

на фиг. 2 схема двухканального релятора 1, содержащего компаратор K, замыкающие S1, S2 и размыкающие  ключи;

ключи;

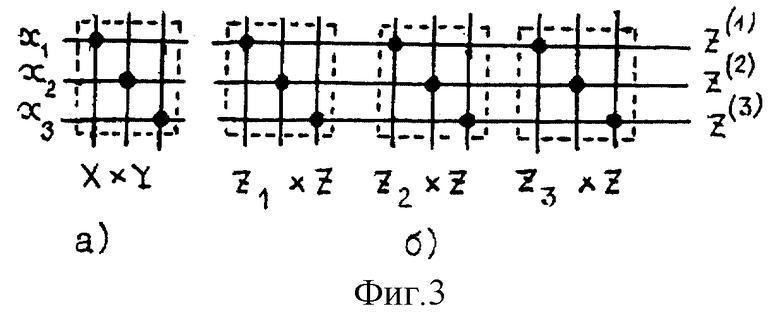

на фиг. 3а изображена коммутационная схема входного наборного поля X•Y при работе реляторного процессора в режиме селекции аналоговых сигналов x2, x2, x3 с их адресно-ранговой идентификацией;

на фиг. 3б показаны коммутационные схемы выходных наборных полей Z1•Z, Z2•Z,Z3•Z при работе реляторного процессора в режиме ранжирования аналоговых сигналов x2, x3, x3.

Реляторный процессор (фиг. 1) построен на двухканальном 1, трехканальном 2 и четырехканальном 3 реляторах RL1, RL2 и RL3.

Каждый релятор 1, 2, 3 содержит дифференциальный компаратор K с не инвертирующим и инвертирующим компараторными входами (на фиг. 1 инвертирующие входы отмечены не зачерненным кружком).

Первый 1, второй 2 и третий 3 реляторы содержат соответственно по два, три и четыре переключательных канала. Каждый переключательный канал состоит из замыкающего Si и размыкающего  ключей, управляемых выходным напряжением компаратора. В схеме реляторного процессора входные выводы ключей каждого переключательного канала реляторов 1, 2, 3 попарно соединены и образуют переключательные входы реляторов, и выходные выводы ключей являются их выходами.

ключей, управляемых выходным напряжением компаратора. В схеме реляторного процессора входные выводы ключей каждого переключательного канала реляторов 1, 2, 3 попарно соединены и образуют переключательные входы реляторов, и выходные выводы ключей являются их выходами.

Электрическая схема двухканального релятора 1 изображена на фиг. 2 (положение ключей  соответствует ситуации, когда x2>x1). Для второго 2 и третьего 3 реляторов переключательные каналы построены по одинаковым с фиг. 2 схемам.

соответствует ситуации, когда x2>x1). Для второго 2 и третьего 3 реляторов переключательные каналы построены по одинаковым с фиг. 2 схемам.

Реляторный процессор содержит информационную X=(x1,x2,x3) шину, на первый, второй и третий входы которой подаются соответственно первый x1, второй x2 и третий x3 аналоговые сигналы (напряжения), идентифицирующую шину Y=(y1, y2, y3), на входы которой при работе в режиме адресно-ранговой идентификации подаются идентифицирующие сигналы y1, y2, y3 и соответствующее им входное наборное поле X•Y, первую Z1=(z1 (1),z1 (2),z1 (3)), вторую Z2=(z2 (1),z2 (2), z2 (3)) и третью Z3= (z3 (1),z3 (2),z3 (3) адресные шины, ранжирующую шину Z= (z(1),z(2),z(3) и три выходных наборных адресных поля Z1•Z,Z2•Z,Z3•Z.

При работе в режиме идентификации идентифицируемых сигналов x1, x2, x3 используются межсоединения базовой схемы, изображенной на фиг. 1 (на входы шин X и Y подаются соответственно идентифицируемые x1, x2, x3 и идентифицирующие y1, y2, y3 сигналы).

Инвертирующие и неинвертирующие компараторные входы первого 1, второго 2 и третьего реляторов 3 соединены соответственно со вторым и первым, третьим и первым, третьим и вторым каналами информационной шины X, а первый, второй и третий каналы идентифицирующей шины Y соединены соответственно с первым и вторым переключательными входами первого релятора 1 и с третьим переключательным входом второго релятора 2.

Первый и второй выходы первого релятора 1 соединены соответственно с первым и вторым переключательными входами второго релятора 2, а третий и четвертый выходы первого релятора 1 соединены соответственно с четвертым и третьим переключательными входами третьего релятора 3. Пятый и шестой выходы второго релятора 2 соединены соответственно со вторым и первым переключательными входами третьего релятора 3. Первый, объединенные второй и третий выходы второго релятора 2 соединены соответственно с третьим, вторым и первым каналами первой Z1(z1 (1),z1 (2),z1 (3)) адресной шины. Пятый, объединенные шестой и седьмой, восьмой выходы третьего релятора 3 соединены соответственно с третьим, вторым и первым каналами второй Z2=(z2 (1),z2 (2),z2 (3)) адресной шины. Первый, объединенные второй и третий, четвертый выходы третьего релятора 3 соединены соответственно с третьим, вторым и первым каналами третьей Z3=(z3 (1),z3 (2),z3 (3)) адресной шины.

При работе в режиме адресно-ранговой селекции идентифицируемых сигналов x1, x2,x3 первый, второй и третий каналы информационной шины X соединены соответственно с первым, вторым и третьим каналами идентифицирующей шины y (без подачи идентифицирующих сигналов y1,y2,y3), как это показано на фиг. 3а.

При работе в режиме ранжирования сигналов x1,x2,x3 межсоединение шин X и Y соответствует и осуществляется на входном наборном поле X•Y (фиг. 3а), а соединение группы адресных шин Z1, Z2, Z3 и ранжирующей шины Z осуществляется на выходных наборных полях Z1•Z,Z2•Z,Z3•Z (фиг. 3б).

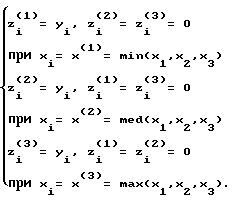

Работа реляторного процессора осуществляется следующим образом. При работе в режиме адресно-ранговой идентификации (фиг. 1) по выходам первой (i= 1), второй (i= 1) и третьей (i=3) адресных шин Z1 воспроизводятся функции идентификации

В частном случае y1=y2=3=y.

Здесь x(1)= min(x1, x2, x3), x(2)=med(x1,x2,x3, x(3)=max(x1,x2,x3) есть соответственно минимальный, медианный и максимальный сигналы из множества X идентифицируемых сигналов x1, x2, x3 (сигналы первого r=1, второго r=2 или третьего r=3 рангов).

Отсюда следует, что каждая i-я адресная шина Z1=(zi (1),zi (2),zi (3)) идентифицирует адрес i сигнала r-го ранга (i=1,2,3). При этом номер i возбужденного выхода zi (r)= yi≠0 в i-ой адресной шине указывает номер канала (адрес) в информационной шине, через который проводится сигнал xi=x(r) r-го ранга, где xi∈ {x1,x2,x3}.

Следовательно, при работе в режиме адресно-ранговой идентификации сигнала xi=x(r) осуществляется идентификация адреса (номера) i-й компоненты xi вектора X=(1,x2,x3) и ее ранга r.

При работе реляторного процессора в режиме адресно-ранговой селекции (фиг. 1 и 3а) в вышеприведенных выражениях величины y1,y2,y3 необходимо заменить на идентифицируемые сигналы x1, x2, x3, т. е. по адресным выходам (каналам) zi (1),zi (2),zi (3) каждой адресной шины Zi воспроизводится операция селекции (выделения) сигналов x1=x (r1) , x2=x (r2) , x3=x(r3) с индентификацией их ранга ri и номера входа (канала) i, на который воздействует сигнал xi ранга ri∈ {1,2,3}.

При работе процессора в режиме ранжирования (фиг. 1 и 3а,б) воспроизводится операция ранжирования (упорядочивания) сигналов {x1,x2,x3} → (x(1),x(2),x(3)) без их адресной идентификации.

В прототипе воспроизводится только режим адресно-ранговой идентификации.

При работе в режиме ранжирования и при снятии выходного сигнала только с одного канала z(r) ранжирующей шины воспроизводится операция ранговой фильтрации только минимального (r=1), медианного (r+2) или максимального (r+3) сигнала x(r)∈ {x1,x2,x3} их трех входных сигналов. При снятии сигналов между двумя выходами z3 и z1 воспроизводится операция селекции минимаксного интервала z(3)-z(1)= δ31, что расширяет функциональные возможности предложенного схемного решения.

В прототипе используются шесть реляторов, т.е. шесть компараторов и 42 управляемых ими однополюсных аналоговых ключа. В предлагаемом схемном решении использовано три релятора, т.е. три компартора и 18 однополюсных аналоговых ключей. Следовательно, выигрыш в аппаратурных затратах составляет три компаратора и 24 ключа.

Изобретение относится к аналоговой вычислительной технике и автоматике и может быть использовано в аналоговых вычислительных машинах и устройствах автоматики и управления для адресно-ранговой идентификации, селекции и ранжирования трех аналоговых сигналов для допускового контроля параметров, представленных аналоговыми сигналами. Техническим результатом является уменьшение аппаратурных затрат. Для этого изобретение содержит реляторы, информационные шины, идентифицирующие шины, выходные адресные шины и выходные ранжирующие шины, входное наборное поле и выходные наборные адресные поля. 3 ил.

Реляторный процессор для адресно-ранговой идентификации, селекции и ранжирования трех аналоговых сигналов, состоящий из информационной шины Х, идентифицирующей шины Y, первой Z1, второй Z2 и третьей Z3 адресных шин, ранжирующей шины Z, входного наборного поля Х и Y, трех выходных наборных адресных полей Z1 x Z, Z2 x Z, Z3 x Z и трех многоканальных реляторов, при этом каждая из упомянутых шин содержит первый, второй и третий входы по числу идентифицирующих сигналов, первый, второй и третий входы информационной шины Х предназначены для подачи соответственно первого, второго и третьего аналоговых сигналов, каждый из многоканальных реляторов содержит компаратор, управляющий состоянием замыкающих и размыкающих ключей каждого канала упомянутого релятора, входные выводы упомянутых ключей в каждом канале многоканальных реляторов соединены и образуют переключательные входы многоканальных реляторов, выходные выводы замыкающих и размыкающих ключей в каждом канале упомянутых реляторов образуют их выходы, инвертирующие и неинвертирующие входы компараторов первого, второго и третьего многоканальных реляторов соединены соответственно со вторым и первым, с третьим и первым, с третьим и вторым входами информационной шины Х, отличающийся тем, что первый, второй и третий многоканальные реляторы содержат соответственно по два, три и четыре канала, второй и третий выходы второго, второй и третий, шестой и седьмой выходы третьего упомянутых реляторов попарно объединены, первый, второй и третий входы идентифицирующей шины Y соединены соответственно с первым и вторым переключательными входами первого и с третьим переключательным входом второго многоканальных реляторов, первый и второй, третий и четвертый выходы первого многоканального релятора соединены соответственно с первым и вторым переключательными входами второго многоканального релятора, с четвертым и третьим переключательными входами третьего многоканального релятора, пятый и шестой выходы второго многоканального релятора соединены соответственно со вторым и первым переключательными входами третьего многоканального релятора, первый, объединенные второй и третий, четвертый выходы второго многоканального релятора соединены соответственно с третьим, вторым и первым входами первой адресной шины Z1, пятый, объединенные шестой и седьмой, восьмой выходы третьего многоканального релятора соединены соответственно с третьим, вторым и первым входами второй адресной шины Z2, а первый, объединенные второй и третий, четвертый выходы третьего многоканального релятора соединены соответственно с третьим, вторым и первым входами третьей адресной шины Z3, первый, второй и третий входы информационной шины Х соединены соответственно во входном наборном поле Х х Y с первым, вторым и третьим входами идентифицирующей шины Y, первые входы первой Z1, второй Z2 и третьей Z3 адресных шин присоединены в выходном наборном поле Z1 х Z к первому входу ранжирующей шины Z, вторые входы первой Z1, второй Z2 и третьей Z3 адресных шин присоединены в выходном наборном поле Z2 x Z ко второму входу ранжирующей шины Z, а третьи входы первой Z1, второй Z2 и третьей Z3 адресных шин присоединены в выходном наборном поле Z3 x Z к третьему входу ранжирующей шины Z.

| Устройство для ранжирования аналоговых сигналов | 1988 |

|

SU1541636A1 |

| Вопросы проектирования радиоэлектронной аппаратуры | |||

| Опыт, результаты, проблемы | |||

| Таллин, ЭстНИИНТИ, 1989, с.87-90, рис.6б | |||

| Устройство для коммутации аналоговых сигналов | 1986 |

|

SU1365099A1 |

| US 3979580 A, 07.09.1976. | |||

Авторы

Даты

2000-05-20—Публикация

1999-02-16—Подача