Изобретение относится к аналоговой вычислительной технике, автоматике систем управления и коммутирования и может быть использовано для преобразования структуры данных, представленных в виде кортежей аналоговых сигналов, для реализаций различных перегруппировок информации, для построения коммутационных процессоров и др.

Известны цифровые процессоры и коммутаторы кортежей (x1,... , хn), компонентами которых являются двоичные числа хk∈{0,1}, k=1, 2,... , n (см., например, Koutz W.H., Levitt K.N. IEEE Trans., 1968. Vol.C-17, N5, p.443-451).

Указанные устройства не могут быть использованы в аналоговой области, так как их система управления предназначена для обработки только двоичных сигналов.

Известны реляторные аналоговые коммутаторы размерности 3× 3, построенные на трех реляторах, в которых переадресация иденфицирующих переменных y1, y2, y3 на соответствующий выход z1, z2, z3 осуществляется по адресу экстремальной (минимальной или максимальной) предикатной переменной (см. Волгин Л.И. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллин: Валгус, 1989, рис.139-142; а.с. СССР 1622888, кл. G 06 G 7/25).

Здесь недостатком является ограниченное число переменных (n=3) и ограниченные функциональные возможности.

Наиболее близким к предлагаемому схемному решению по совокупности существенных признаков и назначению является процессор размерности n× n для адресно-ранговой селекции аналоговых сигналов, содержащий последовательно соединенные ранговый квантователь (патент РФ 2060550, кл. 6 G 06 G 7/25) и амплитудно-диапазонный идентификатор, воспроизводящий операцию отображения (x1,... ,xn)→ (y1,... ,yn) по ранговому признаку предикатных переменных, что ограничивает функциональные возможности прототипа (см. Волгин Л.И. Реляторные нейропроцессоры и коммутационно-логические преобразователи с кодированием номером канала. - Ульяновск, УлГТУ, 1996, рис.8,9, рис.13з, рис.15) и содержащий 0,5n(n-1) реляторов сгруппированных в n-1 вертикальных групп, n входов n проводной входной шины реляторного коммутатора, на которые подается набор аналоговых сигналов x1,... ,xn, n выходов n проводной выходной шины реляторного коммутатора, каждый релятор состоит из компаратора, выход которого соединен с управляющими входами первого, второго замыкающих и первого, второго размыкающих ключей, входные выводы первых замыкающего и размыкающего ключей соединены и образуют первый переключательный вход релятора, входные выводы вторых замыкающего и размыкающего ключей соединены и образуют второй переключательный вход релятора, выходные выводы первого замыкающего, второго размыкающего ключей соединены и образуют первый переключательный выход релятора, выходные выводы второго замыкающего и первого размыкающего ключей соединены и образуют второй переключательный выход релятора, а входные выводы компаратора образуют первый и второй компараторные входы релятора, на которые подаются напряжения, управляющие состоянием ключей реляторов, первая, вторая,... , (n-2)-я, (n-1)-я группы реляторов содержат соответственно один, два,... n-2 и n-1 реляторов, первый и второй входы входной шины соединены соответственно с первым и вторым переключательными входами первого релятора первой группы.

В прототипе снимаются ограничения на размерность процессора, но переадресация предикатных переменных (рис.13з) осуществляется по их ранговому признаку, что ограничивает функциональные возможности.

Проведенный анализ уровня техники и выявление источников, содержащих сведения об аналогах, позволили установить, что заявитель не обнаружил аналогов с признаками, тождественными всем существенным признакам заявляемого изобретения.

Технический результат изобретения заключается в расширении функциональных возможностей за счет реализации полного набора всех n!=1· 2· 3· ... · n переадресаций (перестановок) на выходные шины компонент x1, х2,... , xn входного кортежа реляторного коммутатора.

Поставленная задача решена заявляемым изобретением.

Технический результат расширения функциональных возможностей достигается тем, что предлагается реляторный коммутатор аналоговых сигналов с адресным управлением, содержащий 0,5n(n-1) реляторов, сгруппированных в n-1 вертикальных групп, n входов n проводной входной шины реляторного коммутатора, на которые подается набор аналоговых сигналов x1,... , xn, n выходов n проводной выходной шины реляторного коммутатора, каждый релятор состоит из компаратора, выход которого соединен с управляющими входами первого, второго замыкающих и первого, второго размыкающих ключей, входные выводы первых замыкающего и размыкающего ключей соединены и образуют первый переключательный вход релятора, входные выводы вторых замыкающего и размыкающего ключей соединены и образуют второй переключательный вход релятора, выходные выводы первого замыкающего, второго размыкающего ключей соединены и образуют первый переключательный выход релятора, выходные выводы второго замыкающего и первого размыкающего ключей соединены и образуют второй переключательный выход релятора, а входные выводы компаратора образуют первый и второй компараторные входы релятора, на которые подаются напряжения, управляющие состоянием ключей реляторов, первая, вторая,... , (n-2)-я, (n-1)-я группы реляторов содержат соответственно один, два, ... n-2 и n-1 реляторов, первый и второй входы входной шины соединены соответственно с первым и вторым переключательными входами первого релятора первой группы. В отличие от прототипа первый и второй переключательный выходы релятора первой группы соединены соответственно с первым переключательным входом первого релятора второй группы и с первым переключательным входом второго релятора второй группы, в каждом i-й (i=2,3,... ,n-2) группе первый переключательный выход j-го по вертикали релятора соединен с первым переключательный входом последующего по горизонтали j-го релятора (i+1)-й группы, второй переключательный выход j-го по вертикали релятора i-ой группы при (i=2,3,... ,n-1) при j≤ i-1 соединен со вторым переключательным входом (j+1)-го по вертикали релятора этой же группы, второй переключательный выход j=i по вертикали релятора i-й группы соединен с первым переключательным входом (j+1)-го по вертикали релятора i+1 группы при (i=2,3,... ,n-2), первый и второй переключательные выходы (n-1)-го релятора (n-1) группы и первые переключательные выходы (n-2)-го, (n-3)-го,... , второго и первого реляторов этой же группы соединены соответственно с n-й, (n-1)-й,... , второй и первой выходными шинами реляторного коммутатора, в каждой i-й группе реляторов (i=2,3,... ,n-1) вторые переключательные входы первых реляторов (j=1) соединены соответственно с третьим, четвертым,... , (n-1), n-м входами входной шины хi(i=3,4,... ,n), при этом полный набор n!=1· 2· 3· ... · n перестановок компонент xk(k=1,2,... ,n) входного кортежа (x1,... ,xn) осуществляется через соответствующие изменения полярности подаваемых на компараторные входы реляторов напряжений Uij.

На фиг.1 представлена схема коммутационного инвертирующего релятора, используемого в реляторном коммутаторе аналоговых сигналов с адресным управлением, изображенного на фиг.2, 3.

На фиг.2 представлена схема реляторного коммутатора аналоговых сигналов с адресным управлением при n=3.

На фиг.3 представлена схема реляторного коммутатора аналоговых сигналов с адресным управлением при n=4.

В схемах реляторного коммутатора аналоговых сигналов с адресным управлением используются коммутационные реляторы, схема которых изображена на фиг.1

Каждый релятор содержит первый S1-1 и второй S2-2 замыкающие и первый  и второй

и второй  размыкающие аналоговые ключи, входные выводы первых замыкающего и размыкающего ключей соединены и образуют первый переключательный вход релятора 5, выходные выводы вторых замыкающего и размыкающего ключей соединены и образуют второй переключательный вход релятора 6. Выходные выводы первого замыкающего, второго размыкающего ключей объединены и образуют первый переключательный выход релятора 7, выходные выводы второго замыкающего, первого размыкающего ключей объединены и образуют второй переключательный выход релятора 8. Входные выводы компаратора являются первым 10 (неинвертирующим) и вторым 11 (инвертирующим) компараторными входами релятора. Состояние ключей (замкнут, разомкнут) задается полярностью управляющих напряжений Uij=U1-U2, подаваемых на компараторные входы релятора С, где U1 и U2 есть напряжения соответственно на первом 10 и втором 11 входах компаратора С 9 релятора. При Uij=U1-U2>0 ключи релятора находятся в положениях, указанных на фиг.1. При Uij=U1-U2<0 имеем обратную картину (замыкающие ключи разомкнуты, размыкающие замкнуты).

размыкающие аналоговые ключи, входные выводы первых замыкающего и размыкающего ключей соединены и образуют первый переключательный вход релятора 5, выходные выводы вторых замыкающего и размыкающего ключей соединены и образуют второй переключательный вход релятора 6. Выходные выводы первого замыкающего, второго размыкающего ключей объединены и образуют первый переключательный выход релятора 7, выходные выводы второго замыкающего, первого размыкающего ключей объединены и образуют второй переключательный выход релятора 8. Входные выводы компаратора являются первым 10 (неинвертирующим) и вторым 11 (инвертирующим) компараторными входами релятора. Состояние ключей (замкнут, разомкнут) задается полярностью управляющих напряжений Uij=U1-U2, подаваемых на компараторные входы релятора С, где U1 и U2 есть напряжения соответственно на первом 10 и втором 11 входах компаратора С 9 релятора. При Uij=U1-U2>0 ключи релятора находятся в положениях, указанных на фиг.1. При Uij=U1-U2<0 имеем обратную картину (замыкающие ключи разомкнуты, размыкающие замкнуты).

На фиг.2 представлена схема реляторного коммутатора аналоговых сигналов с адресным управлением при n=3.

Реляторный коммутатор аналоговых сигналов с адресным управлением при n=3 содержит 3 входа 12, 13, 14 3-проводной входной шины 15 реляторного коммутатора, на которые подается набор аналоговых сигналов х1, x2, x3 соответственно, 3 выхода 16, 17, 18 3-проводной выходной шины 19 реляторного коммутатора с выходными сигналами y1, y2, y3, три коммутационных релятора 20 RLij, сгруппированных в 2 вертикальные группы (i=1,2) 21, 22 соответственно. Здесь i - номер вертикальной группы, j - номер релятора по вертикали в вертикальной группе.

В каждом реляторе на первый 10 и второй 11 компараторные входы поданы напряжения Uij, первый и второй переключательные выходы релятора первой группы соединены соответственно с первым переключательным входом первого релятора второй группы и с первым переключательным входом второго релятора второй группы, второй переключательный выход 1-го по вертикали релятора 20 RL21 2-й группы соединен со вторым переключательным входом 2-го по вертикали релятора этой же группы 20 RL22, первый и второй переключательные выходы релятора 20 RL22 и первый переключательный выход релятора 20 RL21 этой же группы соединены соответственно с 3-им 18, вторым 17 и первым 16 выходами выходной шины реляторного коммутатора, второй переключательный вход первого релятора второй группы 20 RL21 соединен с третьим 14 входом входной шины, при этом полный набор n!=1· 2· 3· ... · n перестановок компонент xk(k=1,2,... ,n) входного кортежа (x1,... ,xn) осуществляется через соответствующие изменения полярности подаваемых на компараторные входы реляторов напряжений Uij.

На фиг.3 изображена схема реляторного коммутатора аналоговых сигналов с адресным управлением при n=4.

Реляторный коммутатор с адресной идентификацией набора входных аналоговых сигналов содержит 4 входа 23, 24, 25, 26 4-проводной входной шины 27 реляторного коммутатора, на которые подается набор аналоговых сигналов x1, x2, x3, x4 соответственно, 4 выхода 28, 29, 30, 31 4-проводной выходной шины 32 ранжирующего процессора.

Все 0,5n(n-1) реляторов RL 20 реляторного коммутатора сгруппированы в n-1 вертикальных групп 1, 2,... , n-1 (при n=4 - это 1-33, 2-34 и 3-35 группы, как это показано на фиг.3). Двойная индексация ij реляторов RL в схеме реляторного коммутатора образует прямоугольную матрицу, в которой горизонтальные строки i при j=1 являются порядковым номером (слева направо) горизонтальных групп (i=1,2,... ,n-1), a j является порядковым номером по вертикали (сверху вниз) реляторов внутри каждой вертикальной группы (j=1,2,... ,n-1), т.е. при n=4 первая, вторая и третья группы содержат соответственно один, два и три релятора, такое же число реляторов содержится по горизонтали.

В каждом реляторе на первый 10 и второй 11 компараторные входы поданы напряжения Uij, первый 5 и второй 6 переключательные входы релятора первой группы 20 RL11 соединены соответственно с первым 23 и вторым 24 входами входной шины 27, первый 7 и второй 8 переключательные выходы релятора первой группы 20 RL11 соединены соответственно с первым 5 переключательным входом первого релятора второй группы 20 RL21 и с первым переключательным входом 5 второго релятора второй группы 20 RL22, в каждой i-й (1=2,3,... ,n-2) группе первый переключательный выход 7 j-го по вертикали релятора 20 RLij соединен с первым переключательным входом 5 последующего по горизонтали j-го по вертикали релятора (i+1)-й группы 20 RL(i+1)j, второй переключательный выход 8 j-го по вертикали релятора i-й группы 20 RLij при (i=2,3,... ,n-1) j≤ i-1 соединен со вторым переключательным входом 6 (j+1)-го по вертикали релятора этой же группы 20 RLi(j+1), второй переключательный выход j=i по вертикали релятора i-й группы соединен с первым переключательным входом (j+1)-го по вертикали релятора i+1 группы при (i=2,3,... ,n-2), первый и второй переключательные выходы (n-1)-го релятора (n-1) группы и первые переключательные выходы (n-2)-го, (n-3)-го,... , второго и первого реляторов этой же группы соединены соответственно с n-й, (n-1)-й,... , вторым и первым выходами выходной шины ранжирующего процессора, в каждой i-й группе реляторов (i=2,3,... , n-1) вторые переключательные входы первых реляторов (j=1) соединены соответственно с третьим, четвертым,... , (n-1), n-м входами входной шины 27 xk(k=3,4,... ,n), при этом полный набор n!=1· 2· 3· ... · n перестановок компонент xk(k=1,2,... ,n) входного кортежа (x1,... ,xn) осуществляется через соответствующие изменения полярности подаваемых на компараторные входы реляторов напряжений Uij.

Устройство работает следующим образом.

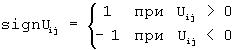

При Uij>0 ключи всех реляторов рангового коммутатора находятся в положении, указанном на фиг.1, ключи S1, S2, и  находятся соответственно в замкнутом и разомкнутом состоянии. При Uij<0 имеем обратную картину (замыкающие ключи разомкнуты, размыкающие замкнуты). Соответственно имеем прямое и перекрестное соединения входных переключательных входов и выходов реляторов. Заданные переадресации (перегруппировки) компонент хk входного кортежа (х1,x2,... ,xn) устанавливается настройкой полярности sign Uij компараторных напряжений, где

находятся соответственно в замкнутом и разомкнутом состоянии. При Uij<0 имеем обратную картину (замыкающие ключи разомкнуты, размыкающие замкнуты). Соответственно имеем прямое и перекрестное соединения входных переключательных входов и выходов реляторов. Заданные переадресации (перегруппировки) компонент хk входного кортежа (х1,x2,... ,xn) устанавливается настройкой полярности sign Uij компараторных напряжений, где

есть сигма-функция.

В таблице приведен полный набор функций переадресации

(x1,x2,... ,xn)→ (xk1,xk2,... ,xkn),

воспроизводимых трехкомпонентным реляторным коммутатором, представленным на фиг.3

Здесь первый, второй и третий разряды кода указывают на состояние реляторов в первой, второй,... , (n-1)-й горизонтальных (вертикальных группах): 0 - прямое соединение переключательных входов и выходов, I - перекрестное соединение.

Перестановки в таблице строк N1 и N6 являются соответственно тождественной (повторение) и покомпонентной инверсией.

При n=2 реляторным коммутатором является сам коммутационный инвертирующий релятор (фиг.2).

В реляторных коммутаторах (фиг.1, 2, 3) управление является потенциально-кодовым, а рассмотренные схемы являются однородными комбинационными автоматами (аналоговыми процессорами).

При использовании в рассмотренных устройствах стробируемых компараторов (например, компараторы с триггером-защелкой) приходим к реляторам с импульсно-кодовым управлением и однобитовой памятью.

Реляторные коммутаторы (фиг.1, 2, 3) являются обратимыми, т.е. в качестве входных и выходных шин могут быть использованы соответственно шины 2 и 1, что также расширяет области их применения.

Устройство прошло лабораторные испытания. Опытные данные показывают достижение цели.

Таким образом, предлагаемое устройство имеет более широкие функциональные возможности по сравнению с прототипом и может выпускаться промышленностью как на дискретных элементах, так и в виде микросхемы.

Изобретение относится к аналоговой вычислительной технике, автоматике систем управления и коммутирования и может быть использовано для преобразования структуры данных, представленных в виде кортежей аналоговых сигналов, для реализаций различных перегруппировок информации, для построения коммутационных процессоров. Техническим результатом является расширение функциональных возможностей за счет реализации полного набора всех переадресаций (перестановок) на выходные шины компонент x1, x2,... xn входного кортежа. Аналоговый коммутатор содержит n-1 вертикальных групп коммутационных реляторов, первая, вторая,..., (n-2)-я, (n-1) группы которого содержат соответственно один, два,..., n-2, n-1 реляторов с двумя компараторными входами, с первым и вторым переключательными входами и выходами, в каждом реляторе на первый и второй компараторные входы поданы напряжения Uij, входную и выходную n проводные шины. При этом полный набор n!=1·2·3·...·n перестановок компонент xk(k=1,2,...,n) входного кортежа (х1,...,xn) осуществляется через соответствующие изменения полярности подаваемых на компараторные входы реляторов напряжений Uij. 3 ил., 1 табл.

Реляторный коммутатор аналоговых сигналов с адресным управлением, содержащий 0,5n(n-1) реляторов сгруппированных в n-1 вертикальных групп, n входов n проводной входной шины реляторного коммутатора, на которые подается набор аналоговых сигналов x1,..., хn, n выходов n проводной выходной шины реляторного коммутатора, каждый релятор состоит из компаратора, выход которого соединен с управляющими входами первого, второго замыкающих и первого, второго размыкающих ключей, входные выводы первых замыкающего и размыкающего ключей соединены и образуют первый переключательный вход релятора, входные выводы вторых замыкающего и размыкающего ключей соединены и образуют второй переключательный вход релятора, выходные выводы первого замыкающего, второго размыкающего ключей соединены и образуют первый переключательный выход релятора, выходные выводы второго замыкающего и первого размыкающего ключей соединены и образуют второй переключательный выход релятора, а входные выводы компаратора образуют первый и второй компараторные входы релятора, на которые подаются напряжения, управляющие состоянием ключей реляторов, первая, вторая,...,(n-2)-я, (n-1)-я группы реляторов содержат соответственно один, два,... n-2 и n-1 реляторов, первый и второй входы входной шины соединены соответственно с первым и вторым переключательными входами первого релятора первой группы, отличающийся тем, что первый и второй переключательные выходы релятора первой группы соединены соответственно с первым переключательным входом первого релятора второй группы и с первым переключательным входом второго релятора второй группы, в каждом i-й (i=2,3,...,n-2) группе первый переключательный выход j-го по вертикали релятора соединен с первым переключательным входом последующего по горизонтали j-го релятора (i+1)-й группы, второй переключательный выход j-го по вертикали релятора i-й группы при (i=2,3,...,n-1), при j≤i-1 соединен со вторым переключательным входом (j+1)-го по вертикали релятора этой же группы, второй переключательный выход j=i по вертикали релятора i-й группы соединен с первым переключательным входом (j+1)-гo по вертикали релятора i+1 группы при (i=2,3,...,n-2), первый и второй переключательный выходы (n-1)-гo релятора (n-1) группы и первые переключательные выходы (n-2)-го, (n-3)-го,..., второго и первого реляторов этой же группы соединены соответственно с n-й, (n-1)-й,..., второй и первой выходными шинами реляторного коммутатора, в каждой i-й группе реляторов (i=2,3,...,n-1) вторые переключательные входы первых реляторов (j=1) соединены соответственно с третьим, четвертым,..., (n-1), n-м входами входной шины xk(k=3,4,...,n), при этом полный набор n!=1·2·3·...·n перестановок компонент xk(k=1,2,...,n) входного кортежа (x1,...,xn) осуществляется через соответствующие изменения полярности подаваемых на компараторные входы реляторов напряжений Uij.

| РАНГОВЫЙ КВАНТОВАТЕЛЬ | 1993 |

|

RU2060550C1 |

| КОММУТАЦИОННЫЙ РЕЛЯТОР ДЛЯ ВОСПРОИЗВЕДЕНИЯ БАЗОВЫХ ОПЕРАЦИЙ КОМПЛЕМЕНТАРНОЙ АЛГЕБРЫ | 2000 |

|

RU2170456C1 |

| РАНГОВЫЙ КОММУТАТОР | 2001 |

|

RU2195700C1 |

| Коммутатор- распределитель экстремального сигнала | 1989 |

|

SU1622888A1 |

| US 5905387 А, 18.05.1999. | |||

Авторы

Даты

2005-07-10—Публикация

2004-02-18—Подача