Устройство относится к области вычислительной техники и может использоваться в системах автоматизации для прямого и обратного преобразования аналогового сигнала в цифровой код.

Известен аналого-цифровой преобразователь (АЦП) по методу двухтактного интегрирования, содержащий интегратор, ключевые элементы, генераторы импульсов, счетчик, регистр памяти, элемент задержки (Волович, Г.И. Схемотехника аналоговых и аналогово-цифровых электронных устройств / Г.И.Волович. - М.: Издательский дом «Додэка-XXI», 2005. - С.446 с).

Известное устройство имеет недостаточно высокую точность, что является следствием разомкнутого характера его структуры.

Известно устройство аналого-цифровой преобразователь с последовательными во времени действиями поразрядного уравновешивания от старшего разряда к младшему и схемы его реализации в виде множества АЦП с общепринятым термином «поразрядного уравновешивания». При всем разнообразии таких АЦП они содержат источник входного сигнала, устройство его сравнения (первый сумматор) с сигналом выхода цифро-аналогово преобразователя (ЦАП), кодовые входы которого одновременно являются кодом выхода всего АЦП и управляются кольцевым распределителем, который сам потактово управляется выходом устройства сравнения. Правильный код формируется и периодически фиксируется в конце каждого цикла тактов работы кольцевого распределителя (Темников Ф.Е. Теоретические основы информационной техники / Темников Ф.Е., Афонин В.А., Дмитриев В.И. - М: Энергия, 1979. - 512 с. См. стр.118, 119, рис.3-20, 3-21.).

Недостатком устройства является его повышенная сложность, пониженное быстродействие из-за задержки на время цикла работы кольцевого распределителя, циклический характер выдачи результатов преобразования.

Наиболее близким к предлагаемому устройству является многозонный развертывающий преобразователь, содержащий последовательно включенные источник входного сигнала, первый сумматор и интегратор, выход которого подключен к входам группы из нечетного числа релейных элементов, выходы которых соединены с входами второго сумматора, выход которого соединен с выходом устройства и со вторым входом первого сумматора (А.С. СССР №1183988 от 27 апреля 1984 г., опубл. 07.10.85, Бюл. №37).

Устройство служит для преобразования аналогового сигнала в многозонный сигнал с частотно-широтно-импульсной модуляцией (ЧШИМ).

В своем первоначальном виде устройство-прототип не может работать в режиме преобразования аналогового сигнала в цифру с последующим обратным цифро-аналоговым преобразованием (ЦАП).

Для преобразования в код выходного сигнала устройства-прототипа требуется включение на его выходе сглаживающего фильтра и непосредственно АЦП того или иного принципа действия.

Такая структура будет иметь низкую точность работы и пониженное быстродействие, так как при ЧШИМ практически невозможно согласовать амплитудное значение пульсаций на выходе сглаживающего фильтра, которое потом может быть учтено как постоянное значение погрешности преобразования, с тактовой частотой АЦП.

Кроме того, недостатком известного технического решения является наличие мгновенной динамической ошибки преобразования, обусловленной конечным значением длительности фронтов выходных импульсов релейных элементов.

Таким образом, известное техническое решение в случае применения релейных элементов с недостаточно высоким быстродействием (длительность фронтов на уровне единиц микросекунд) характеризуется низкой точностью.

Таким образом, известное техническое решение при построении на его основе АЦП будет характеризоваться низким быстродействием и невысокой точностью.

В тоже время, известное техническое решение относится к замкнутым системам регулирования, что позволяет при соответствующих схемотехнических дополнениях организовать на его основе высокоточный интегрирующий преобразователь «Аналог - Цифра - Аналог».

Технической задачей изобретения является повышение быстродействия и точности работы АЦП-ЦАП на базе известного интегрирующего многозонного частотно-широтно-импульсного развертывающего преобразователя.

Указанная техническая задача решается тем, что скоростной преобразователь «Аналог - Цифра - Аналог» с бестактовым поразрядным уравновешиванием, содержащий источник входного сигнала и n-ое число релейных элементов, причем n=1, 2, 3… целое число, выходной сумматор, выход которого подключен к аналоговому выходу устройства, и согласно изобретению в скоростной преобразователь дополнительно введены буферный усилитель, n-ое число пропорциональных звеньев, n-1 число дополнительных сумматоров, n-ое число ключевых элементов, n-1 число динамических D-триггеров, устройство сравнения кодов, одновибратор, источник опорного цифрового кода и устройство вычитания кодов, причем выход каждого из n-го числа релейных элементов соединен с входом соответствующего ключевого элемента, а также через соответствующее из n-го числа пропорциональное звено подключен к соответствующему входу выходного сумматора, первый вход первого дополнительного сумматора соединен с выходом буферного усилителя, вход которого подключен к источнику входного сигнала, также выход буферного усилителя подключен к входу первого релейного элемента, первый вход каждого из последующих дополнительных сумматоров, начиная со второго, подключен к выходу предыдущего дополнительного сумматора, второй вход каждого из дополнительных сумматоров подключен к выходу соответствующего пропорционального звена, при этом выход каждого из дополнительных сумматоров подключен к входу соответствующего релейного элемента, начиная со второго, D-входы триггеров и первая группа входов устройства сравнения кодов соединены с выходами соответствующих из n-1 ключевых элементов, кроме последнего ключевого элемента, выходы D-триггеров подключены ко второй группе соответствующих входов устройства сравнения кодов и также к первой группе соответствующих входов устройства вычитания кодов, выход устройства сравнения кодов соединен с входом одновибратора, выход которого подключен к С-входам динамических D-триггеров, выход n-го ключевого элемента соединен с соответствующим входом первой группы входов устройства вычитания кодов, вторая группа входов устройства вычитания кодов соединена с соответствующими выходами источника опорного цифрового кода, выходы устройства вычитания кодов подключены к соответствующим цифровым выходам скоростного преобразователя «Аналог - Цифра - Аналог» с бестактовым поразрядным уравновешиванием.

Техническим результатом предлагаемого устройства является его повышенная точность работы и быстродействие за счет того, что при изменении кодового состояния ключевых элементов создается команда запрета считывания с них цифровых данных на время переключения релейных элементов.

Изобретение поясняется чертежами, где на:

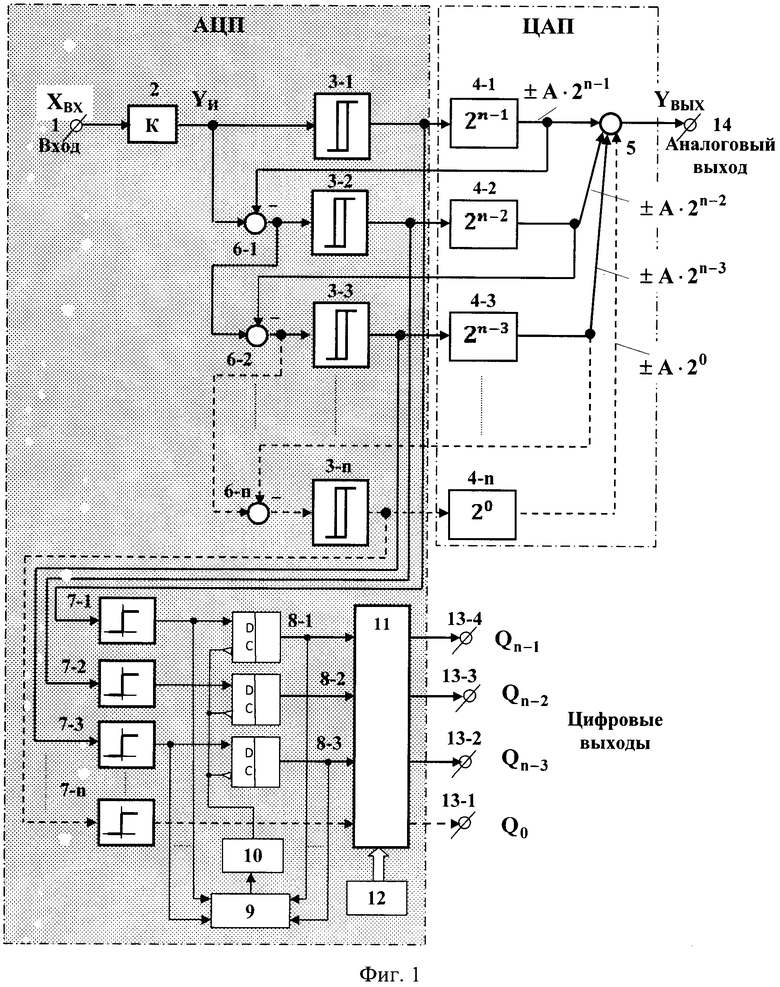

Фиг.1 - дана функциональная схема предлагаемого устройства;

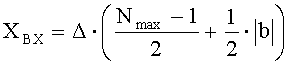

Фиг.2-5 - приведены временные диаграммы сигналов скоростного преобразователя «Аналог - Цифра - Аналог».

В состав преобразователя «Аналог - Цифра - Аналог» (фиг.1) входят последовательно включенные входная клемма 1, буферный усилитель 2, первый релейный элемент 3-1, первое пропорциональное звено 4-1 с коэффициентом усиления 2n-1 и выходной сумматор 5, последовательно включенные третий сумматор 6-1, второй релейный элемент 3-2 и второе пропорциональное звено 4-2 с коэффициентом усиления 2n-2, последовательно включенные четвертый сумматор 6-2, третий релейный элемент 3-3 и третье пропорциональное звено 4-3 с коэффициентом усиления 2n-3, последовательно включенные n-й сумматор 6-и, n-й релейный элемент 3-n и n-е пропорциональное звено 4-и с коэффициентом усиления 20, а также в состав устройства входят ключи 7-1, 7-2,…, 7-n, входы которых подключены к соответствующим выходам релейных элементов 3-1, 3-2, …, 3-n, а выходы всех ключевых элементов кроме последнего 7-1,…, 7-(n-1) соединены с D-входами динамических D-триггеров 8-1…8-3 и с первой группой входов устройства сравнения кодов 9, вторая группа входов которых подключена к выходам триггеров 8-1…8-3, одновибратор 10, устройство вычитания кодов 11, выход n-го ключевого элемента 7-n соединен с соответствующим входом первой группы входов устройства вычитания кодов 11, источник опорного цифрового кода 12, цифровые выходы 13-1…13-4, аналоговый выход 14.

Звенья скоростного преобразователя «Аналог - Цифра - Аналог» (фиг.1) имеют следующие характеристики.

Сумматоры 6-1, 6-2,…, 6-n содержат два входа с единичным коэффициентом передачи по каждому из них и выполняют операцию вычитания сигналов.

Буферный усилитель 2 имеет, например, единичный коэффициент передачи и предназначен для повышения входного сопротивления АЦП-ЦАП.

Релейные элементы 3-1, 3-2, …, 3-n выполнены с симметричной относительно «нуля» петлей гистерезиса. Их выходной сигнал меняется дискретно в пределах ±А.

Пропорциональные звенья 4-1, 4-2, …, 4-n реализованы с коэффициентами усиления, которые изменяются в соответствии с весом разряда преобразуемого кода с произвольным основанием, но чаще с двоичным кодом, пропорциональным 2n-1, 2n-2, …, 20. Здесь n - количество разрядов двоичного кода. Наибольший коэффициент пропорционального звена 2n-1 соответствует весу старшего разряда двоичного кода, а наименьший 20 - весу младшего разряда.

Сумматор 5 имеет n-е количество входов с единичным коэффициентом передачи по каждому из них и выполняет операцию суммирования сигналов. Количество входов сумматора 5 выбирается равным числу разрядов n преобразователя АЦП-ЦАП.

Ключи 7-1, 7-2, …, 7-n преобразуют биполярные выходные импульсы релейных элементов 3-1, 3-2, …, 3-n в однополярные для последующего согласования выходов релейных элементов 3-1, 3-2, …, 3-n с входами последующих цифровых элементов. Каждый ключ имеет нулевое значение порогов включения/выключения и неинвертирующую характеристику «вход-выход».

Динамические D-триггеры 8-1…8-3 переключаются по заднему фронту импульса на С-входе в состояние, которое имеет D-вход.

Устройство сравнения кодов 9 (цифровой компаратор) переключается в «1» при неравенстве кодов на первой и второй группе его входов.

Одновибратор 10 запускается передним фронтом сигнала «1» с выхода устройства сравнения кодов 9.

Принцип работы скоростного преобразователя «Аналог - Цифра - Аналог» с бестактовым поразрядным уравновешиванием следующий.

При рассмотрении работы АЦП-ЦАП ограничимся четырьмя разрядами «n» двоичного кода.

Буферный усилитель 2, релейные элементы 3-1…3-n, сумматоры 6-1…6-n, ключи 7-1…7-n, динамические D-триггеры 8-1…8-3, устройства сравнения кодов 9, одновибратор 10, устройство вычитания кодов 11 и источник опорного цифрового кода 12 в совокупности образуют АЦП.

Функции ЦАП выполняют пропорциональные звенья 4-1…4-n и сумматор 5. Сумматоры 6-1…6-n имеют единичный коэффициент передачи по каждому из входов и производят вычитание входных сигналов. Релейные элементы 3-1…3-n в общем случае имеют симметричную относительно «нуля» петлю гистерезиса, а их выходной сигнал меняется дискретно в пределах ±А.

Величина ±b порогов переключения релейных элементов 3-1…3-n выбирается из условия |b|<|A|.

Сумматор 5 имеет «n»-е количество входов с единичным коэффициентом передачи по каждому из них и выполняет операцию суммирования сигналов.

Ключи 7-1…7-n являются вспомогательными элементами, которые преобразуют биполярные выходные импульсы релейных элементов 3-1…3-n в однополярные для последующего согласования выходов релейных элементов 3-1…3-n с входами последующих цифровых элементов. Каждый из ключей 7-1…7-n имеет нулевое значение порогов «включения/выключения» и неинвертирующую характеристику «вход-выход».

Устройство вычитания кодов 11 производит операцию поразрядного вычитания из кода N1, формируемого на выходе ключей 7-1…7-3 и ключа 7-n, кода N2, задаваемого источником опорного цифрового кода 12, и может выполняться как на основе стандартных микросхем, так и на базе программируемых контроллеров.

Пропорциональные звенья П1…Пn реализованы с коэффициентами передачи, которые изменяются в соответствии с весом разряда преобразуемого кода в общем случае с произвольным основанием, но чаще, как принято здесь, с двоичным кодом, пропорциональным ряду 2n-1 2n-2, …, 20.

Наибольший коэффициент пропорционального звена 2n-1 соответствует весу старшего разряда двоичного кода, а наименьший 20 - весу младшего разряда.

Далее в тексте приняты следующие обозначения: ХBX - входной сигнал; YВЫХ - выходной сигнал сумматора 5; ±А·2n-1, ±А·2n-2, ±А·2 n-3, …, ±А·20 - максимальные уровни сигналов на выходе пропорциональных звеньев 4-1…4-n соответственно; ±b - пороги переключения релейных элементов 3-1…3-n; ±А - амплитуда выходных импульсов релейных элементов 3-1…3-n; Qn-1, Qn-2, Qn-3, …, Q0 - разряды цифрового кода на цифровых выходах 13-1…13-4; N1 - цифровой код на выходе ключей 7-1…7-n, N2 - цифровой код, задаваемый источником опорного цифрового кода 12; N3 - цифровой код на цифровых выходах 13-1…13-4 АЦП.

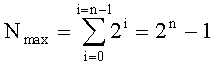

Для АЦП-ЦАП входной сигнал можно представить в виде выражения ХBX=±Δ(k+0,5·|b|), где Δ=2Amax/Nmax=2A - вес единицы младшего разряда преобразуемого кода в аналоговой форме;

Рассмотрим работу устройства при k=0 и ХBX=(0,5·Δ·|b|)>0, считая, что пороги переключения релейных элементов 3-1…3-n равны ±b.

В этом случае релейный элемент 3-1, формирующий старший разряд преобразуемого кода, переключается в «положительное» состояние, а все остальные 3-2…3-n в системе вынуждены переключиться в «отрицательное» положение, когда суммарный сигнал на аналоговом выходе 14 равен YВЫХ=A(2n-1-2n-2-2n-3-20)=A. Условие равенства ХBX=YВЫХ=А может быть выполнено только при условии |b|=|A|, когда в схеме достигается максимальная степень помехоустойчивости к сигналам внешних и внутренних помех.

Положительному уровню сигнала на выходе релейных элементов 3-1…3-n соответствует сигнал логической «1» на выходе ключей 7-1…7-n, а отрицательному уровню - сигнал логического «0». В результате при ХBX=(0,5·Δ·|b|) на выходе ключей 7-1…7-n формируется смещенный двоичный код N1 равный (Nmax+1)/2.

Считаем, что выходы ключей 7-1…7-n подключены непосредственно к входам устройства вычитания кодов 11.

Для устранения «смещенности» двоичного кода с помощью устройства вычитания кодов 11 и источником опорного цифрового кода 12 реализуется операция поразрядного вычитания из кода N1 кода N2 так, чтобы цифровой код N3=N1-N2 соответствовал бы стандартному двоичному коду. В дальнейшем принимаем N2=(Nmax+1)/2. Тогда при ХBX=0,5·Δ·|b| выходной код преобразователя N3 в десятичной форме будет равен нулю.

При значениях k=0 и ХBX=-(0,5·Δ·|b|)<0 АЦП - ЦАП работает аналогичным образом. При этом релейный элемент 3-1 переключается в состояние «-A», а остальные релейные элементы 3-2…3-n - в положении «+А». Цифровой код N1 на выходе ключей 7-1…7-n становится равным (Nmax-1)/2, а код на цифровых выходах 13-1…13-4 АЦП N3=N1-N2 равным минус единице (в десятичной форме).

Таким образом, интервал -b<XBX<b формирует в преобразователе зону нечувствительности, когда на границах данного интервала состояние кода N на цифровых выходах 13-1…13-4 АЦП меняется, составляя в десятичной системе счисления «0» или «-1», что соответствует статической ошибке, равной единице младшего разряда кода N3. При большом количестве разрядов АЦП-ЦАП (n≥8) данная ошибка практически не оказывает заметного влияния на точность его работы и ею можно пренебречь.

Аналогичным образом АЦП-ЦАП работает при других значениях k. Например, максимально возможному значению k=(Nmax-1)/2 будет соответствовать максимальный уровень входного сигнала

когда релейные элементы 3-1…3-n переключаются в «положительное» состояние, а суммарный сигнал на аналоговом выходе 14 равен YВЫХ=A(2n-1+2n-2+2n-3+,…,+20)=A·Nmax. Все ключи 7-1…7-n находятся в состоянии логической «1», что соответствует максимальному значению кода N1=Nmax. При вычитании из кода N1 кода N2=(Nmax+1)/2 на цифровых выходах 13-1…13-4 преобразователя получаем код N3=(Nmax-1) 2.

При

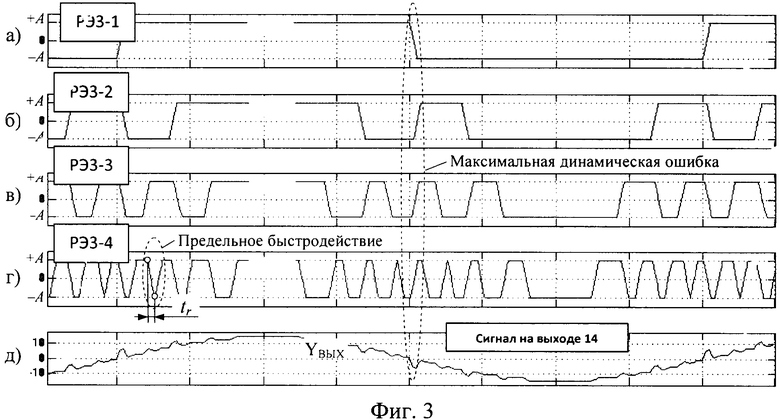

С теоретических позиций при идеализации динамических характеристик релейных элементов 3-1…3-n полоса пропускания АЦП-ЦАП неограничена. Диаграммы сигналов «вход - аналоговый выход» АЦП-ЦАП при нулевом значении времени переключения релейных элементов 3-1…3-n (n=4) приведены на фиг.3.

Однако на практике, учитывая, что схема включения релейных элементов 3-1…3-n по сути дела является последовательной асинхронной структурой, время их переключения (длительность фронтов) может вызвать существенную погрешность работы устройства.

Так на приведенных диаграммах сигналов АЦП-ЦАП (фиг.3) видно, что максимальную частоту переключений имеет релейный элемент младшего разряда (РЭ3-4), и быстродействие АЦП-ЦАП ограничивается длительностью tг фронта импульса релейного элемента 3-n, при которой прямоугольный импульсный сигнал вырождается в импульс треугольной формы.

Как уже отмечалось, рассмотренный АЦП-ЦАП относится к последовательной асинхронной структуре, где при переходе от одного числа к другому может наблюдаться мгновенная динамическая ошибка преобразования. Так при переходе от числа 1000 к числу 0111 (фиг.3а-г), когда меняются все разряды двоичного числа, наблюдается максимальная динамическая ошибка, как в коде, так и в аналоговом сигнале на выходе ЦАП (фиг.3д). Одновременно, если меняется значение только младшего разряда, то динамическая ошибка отсутствует.

Для исключения подобной динамической ошибки необходимо на время переходного процесса в АЦП блокировать считывание данных с его цифровых выходов. С этой целью в АЦП-ЦАП введены динамические D-триггеры 8-1…8-3, устройство сравнения кодов 9 и одновибратор 10.

При изменении кода на выходе ключей 7-1……7-3 устройство сравнения кодов 9 переходит в состояние «1», под действием которой запускается одновибратор 10. В течение длительности его импульса D-триггеры 8-1…8-3 сохраняют свое предыдущее состояние. Длительность импульса с выхода одновибратора 9 должна превышать время неопределенности состояния релейных элементов 3-1…3-n АЦП при их переключении в 1,3…1,5 раза.

При возврате одновибратора 9 в исходное нулевое состояние D-триггеры 8-1…8-3 синхронно переключаются, формируя на своих выходах кодовое состояние ключей 7-1……7-3, а устройство сравнения кодов 9 переходит в «0», так как кодовое состояние его первой и второй групп входов равны между собой.

Далее из кодовой последовательности D-триггеров 8-1…8-3 и ключа 7-n вычитается опорный код, формируемый источником опорного цифрового кода 12.

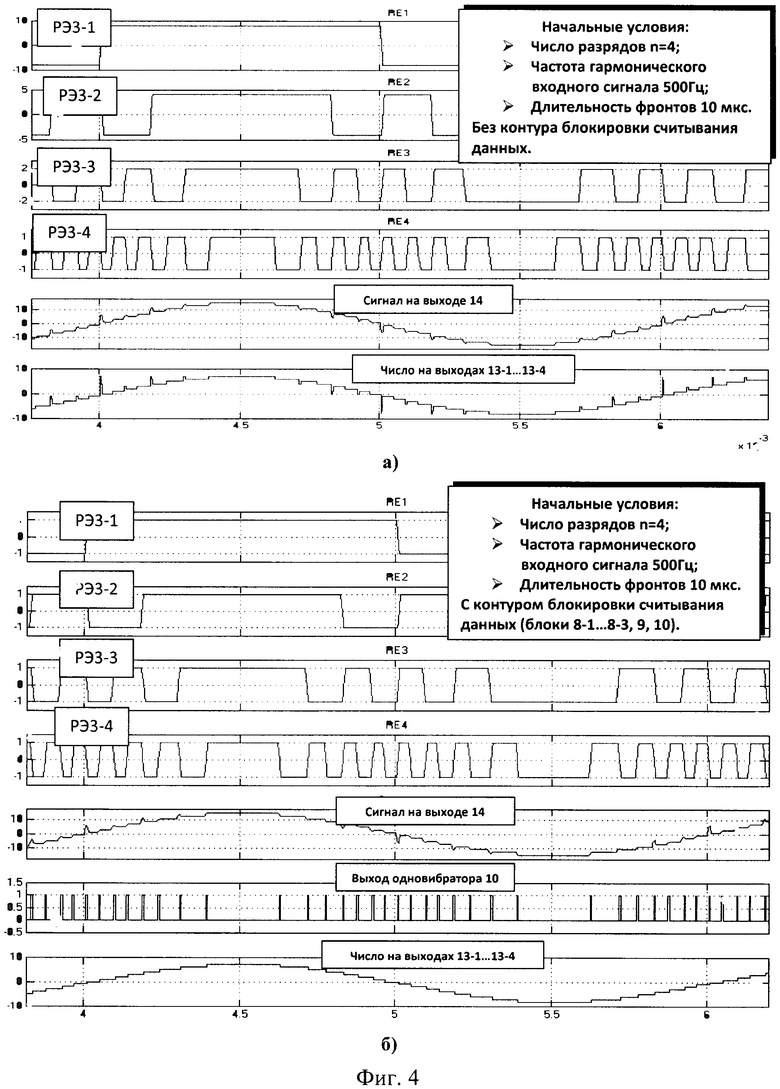

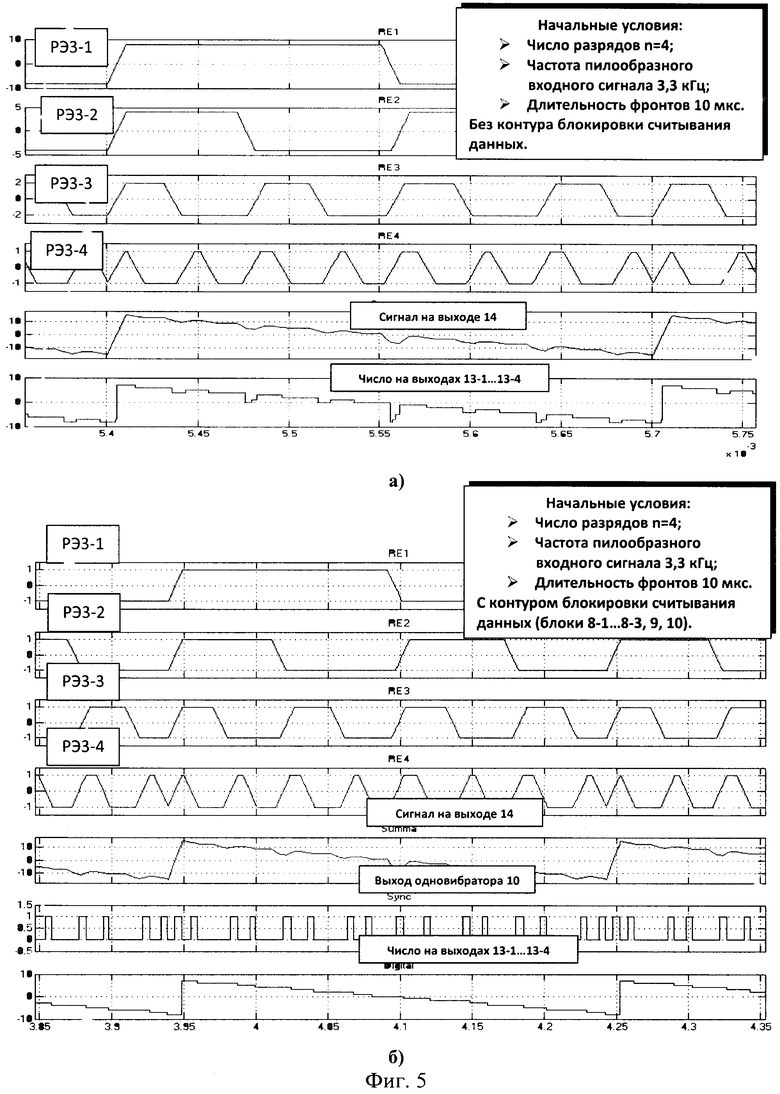

На фиг.4, и фиг.5 приведены результаты моделирования АЦП-ЦАП в пакете Matlab + Simulink при воздействии на вход гармонического сигнала (фиг.4) и пилообразного (фиг.5) с линейно спадающим и дискретно возрастающим фронтами (фиг.5).

При отсутствии контура блокировки считывания данных (D-триггеры 8-1…8-3, устройство сравнения кодов 9 и одновибратор 10) (фиг.4, а, фиг.5, а) на аналоговом и цифровых выходах устройства присутствует мгновенная динамическая ошибка, уровень которой определяется текущим числом АЦП.

После введения D-триггеров 8-1…8-3, устройства сравнения кодов 9 и одновибратора 10 (фиг.4б, фиг.5б) на цифровых выходах 13-1…13-4 данная ошибка полностью подавляется. Что касается выходного аналогового сигнала ЦАП (выход 14), то здесь ошибка преобразования легко может быть подавлена сглаживающим фильтром, например, апериодическим первого порядка с малым значением постоянной времени.

Таким образом, введение D-триггеров 8-1…8-3, устройства сравнения кодов 9 и одновибратора 10 приводит к ликвидации динамической ошибки устройства, что повышает точность его работы.

Рассмотренный преобразователь предполагается предложить фирмам-изготовителям интегральных микросхем для его серийного производства на интегральной основе.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ "АНАЛОГ-ЦИФРА-АНАЛОГ" | 2011 |

|

RU2460210C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2011 |

|

RU2449470C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

Изобретение относится к области вычислительной техники и может использоваться в системах автоматизации для прямого и обратного преобразования аналогового сигнала в цифровой код. Техническим результатом является повышение быстродействия и точности преобразования. Устройство содержит источник входного сигнала, сумматоры, буферный усилитель, релейные элементы, n пропорциональных звеньев, n ключевых элементов, источник опорного цифрового кода, устройство вычитания кодов, n-1 динамических D-триггеров, одновибратор, устройство сравнения кодов. 5 ил.

Скоростной преобразователь «Аналог - Цифра - Аналог» с бестактовым поразрядным уравновешиванием, содержащий источник входного сигнала и n релейных элементов, причем n=1, 2, 3… - целое число, выходной сумматор, выход которого подключен к аналоговому выходу устройства, отличающийся тем, что в него введены буферный усилитель, n пропорциональных звеньев, n-1 дополнительных сумматоров, n ключевых элементов, n-1 динамических D-триггеров, устройство сравнения кодов, одновибратор, источник опорного цифрового кода и устройство вычитания кодов, причем выход каждого из n релейных элементов соединен с входом соответствующего ключевого элемента, а также через соответствующее звено из n пропорциональных звеньев подключен к соответствующему входу выходного сумматора, первый вход первого дополнительного сумматора соединен с выходом буферного усилителя, вход которого подключен к источнику входного сигнала, также выход буферного усилителя подключен к входу первого релейного элемента, первый вход каждого из последующих дополнительных сумматоров, начиная со второго, подключен к выходу предыдущего дополнительного сумматора, второй вход каждого из дополнительных сумматоров подключен к выходу соответствующего пропорционального звена, при этом выход каждого из дополнительных сумматоров подключен к входу соответствующего релейного элемента, начиная со второго, D-входы триггеров и первая группа входов устройства сравнения кодов соединены с выходами соответствующих из n-1 ключевых элементов, кроме последнего ключевого элемента, выходы D-триггеров подключены ко второй группе соответствующих входов устройства сравнения кодов и также к первой группе соответствующих входов устройства вычитания кодов, выход устройства сравнения кодов соединен с входом одновибратора, выход которого подключен к С-входам динамических D-триггеров, выход n-го ключевого элемента соединен с соответствующим входом первой группы входов устройства вычитания кодов, вторая группа входов устройства вычитания кодов соединена с соответствующими выходами источника опорного цифрового кода, выходы устройства вычитания кодов подключены к соответствующим цифровым выходам скоростного преобразователя «Аналог - Цифра - Аналог» с бестактовым поразрядным уравновешиванием.

| Развертывающий усилитель | 1984 |

|

SU1183988A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| US 2009309778 A1, 17.12.2009 | |||

| JP 6164399 A, 10.06.1994. | |||

Авторы

Даты

2013-08-27—Публикация

2012-06-20—Подача