Изобретение относится к области измерительной и вычислительной техники и может быть использовано для быстрого преобразования аналоговых электрических сигналов в цифровой код в системах, функционирующих в модулярной системе счисления.

Известно устройство (аналог) (авт. св. СССР №1368989, МКИ Н03М 1/28, БИ №3, 1988 г.), содержащее блок определения остатка по наибольшему основанию СОК, аналогово-цифровые преобразователи, сумматоры, шифраторы, блоки коррекции, коммутаторы, одновибратор, регистр, аналоговую входную шину, шину коррекции, шину управления, выходную шину «ядро числа» и выходные шины остатков по соответствующим основаниям СОК. Недостаток - большие аппаратные затраты устройства.

Известно устройство (аналог) (авт. св. СССР №1181141, МКИ Н03М 1/28, БИ №35, 1985 г.), содержащее блок определения остатка по наибольшему основанию СОК, аналогово-цифровые преобразователи, блоки коррекции, входную шину, шину коррекции, выходные шины кодов по основаниям СОК, сумматоры, шифраторы, шины кодов оснований СОК. Недостаток - большие аппаратные затраты устройства.

Известно также устройство (прототип) (патент РФ 2433527, МПК7 Н03М 1/28, заявл. 12.04.2010; опубл. 10.11.2011) содержащее блоки слежения-хранения, аналогово-цифровые преобразователи, цифроаналоговые преобразователи, блоки вычитания, выходные шины кодов остатков в СОК, вход.

Недостаток прототипа - применение большого количества параллельных аналого-цифровых преобразователей, что с увеличением их разрядности приводит к несоизмеримому росту дороговизны устройства. К тому же логика работы прототипа обеспечивается таким же количеством других блоков, перечисленных выше, что также влияет на сложность и цену устройства.

Задача, на решение которой направлено заявляемое устройство, состоит в снижении аппаратных издержек при производстве аналого-цифровых преобразователей, функционирующих в системе остаточных классов.

Технический результат выражается в возможности сокращения в n раз, где n - число оснований системы остаточных классов, количества элементарных аналого-цифровых преобразователей, цифроаналоговых преобразователей и блоков вычитания, входящих в аналого-цифровой преобразователь, функционирующий в системе остаточных классов.

Технический результат достигается тем, что в аналого-цифровой преобразователь в системе остаточных классов, содержащий вход, n выходных шин кодов остатков в системе остаточных классов, где n - число оснований системы остаточных классов, первый блок слежения-хранения, аналогово-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, при этом выход первого блока слежения-хранения подключен к первому входу блока вычитания и к первому входу аналого-цифрового преобразователя, а выход цифроаналогового преобразователя соединен со вторым входом блока вычитания, введены источник напряжения смещения, второй блок слежения-хранения, n регистров-защелок, при этом вход устройства объединен с входом второго блока слежения-хранения, выход которого подключен ко второму входу первого блока слежения-хранения, при этом выход блока вычитания подключен к первому входу первого блока слежения-хранения, выход источника напряжения смещения подключен ко второму входу аналого-цифрового преобразователя, выход которого подключен к цифроаналоговому преобразователю и входам n регистров-защелок, при этом выход i-гo

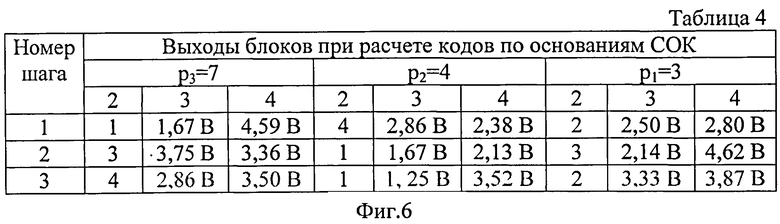

На фиг.1 представлена структурная схема АЦП в СОК.

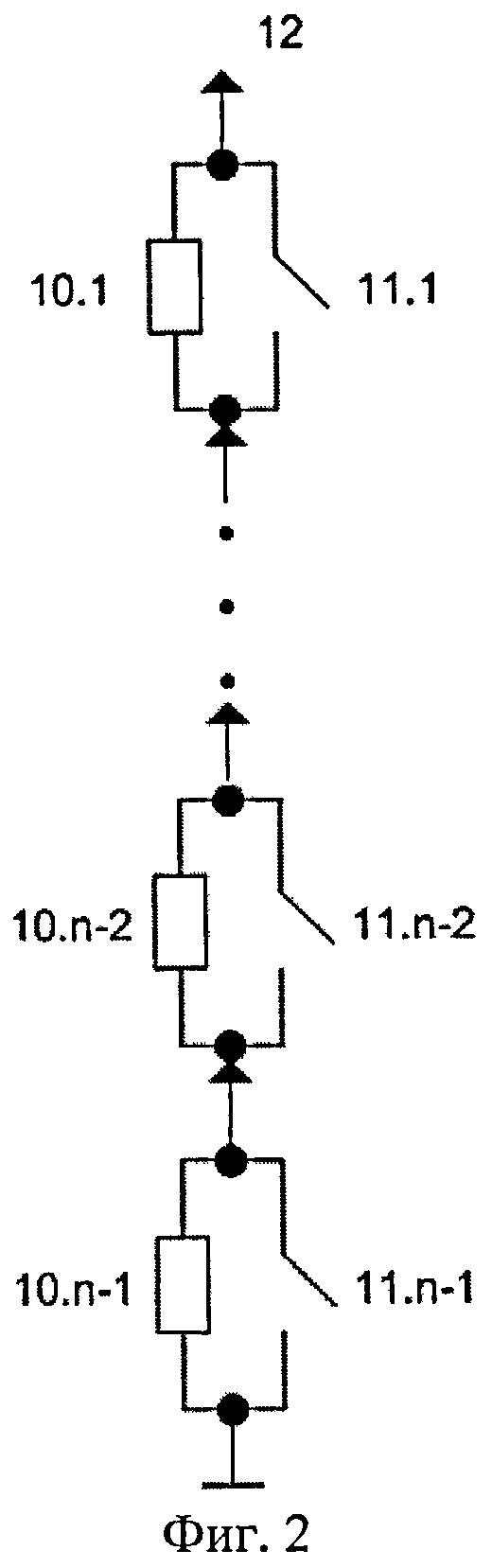

На фиг.2 приведена схема источника напряжения смещения.

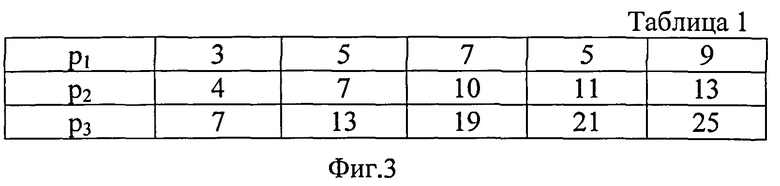

На фиг.3 приведена таблица 1 сочетаний трех оснований СОК.

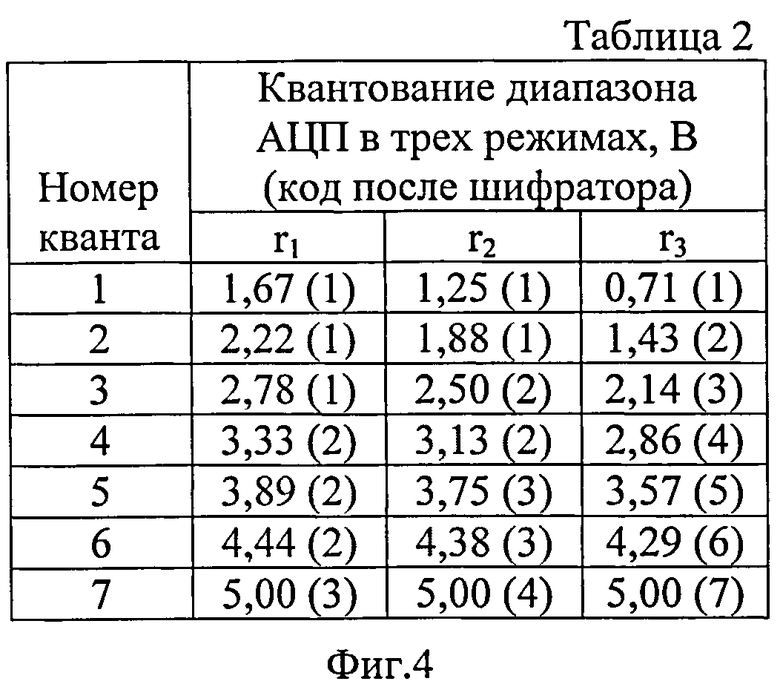

На фиг.4 приведена таблица 2 значений напряжений, полученные при квантовании диапазона АЦП в трех режимах в устройстве по трем основаниям СОК p1=3, p2=4, р3=7.

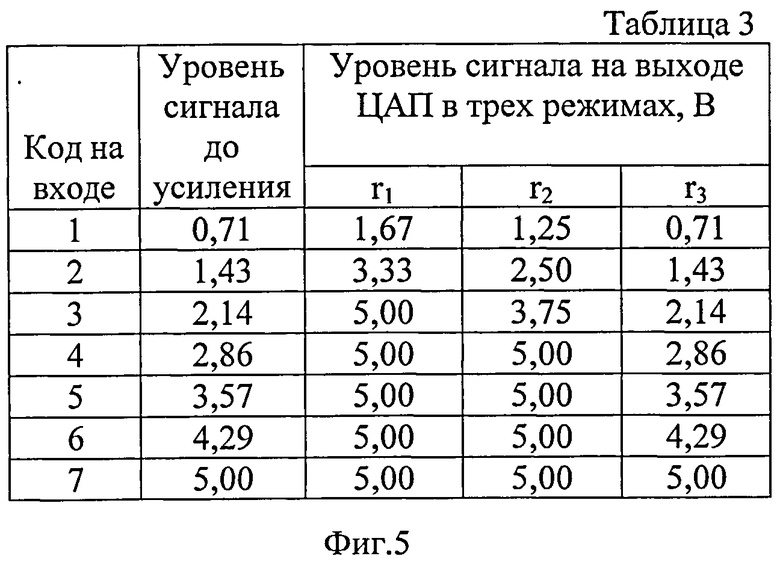

На фиг.5 приведена таблица 3 значений напряжений на выходе ЦАП при различных уровнях сигнала до усиления.

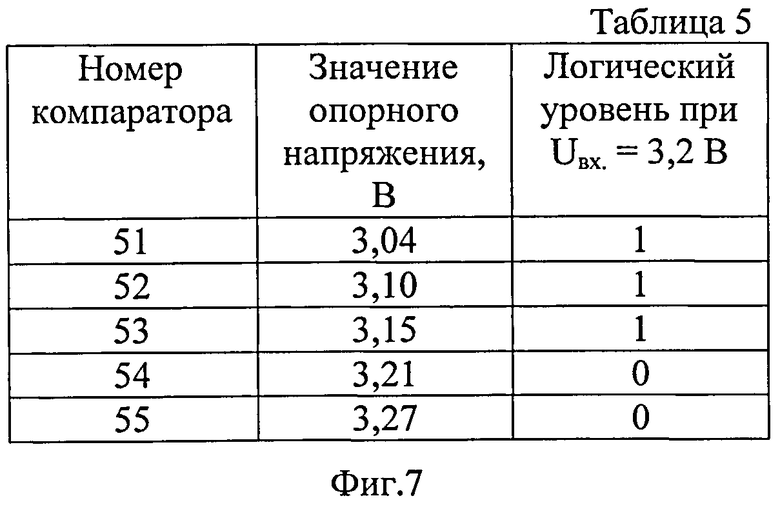

На фиг.6 приведена таблица 4 значений кодов и уровней сигналов на выходе блоков устройства, полученные в процессе вычисления остатков по основаниям р3, р2 и p1.

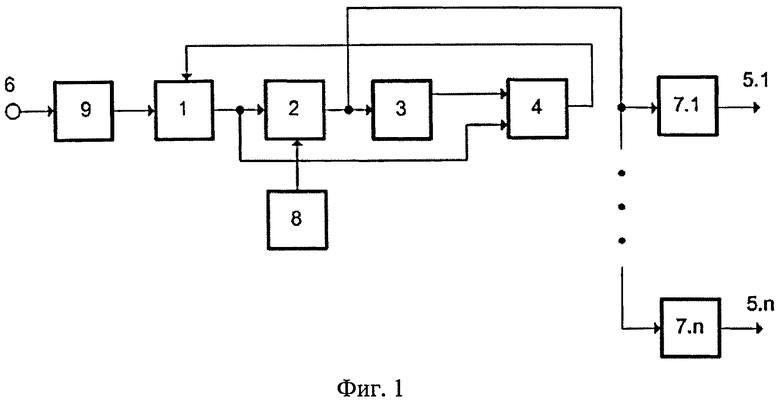

На фиг.7 приведена таблица 5 опорных напряжений.

Сущность изобретения заключается в объединении функций идентичных блоков в одном АЦП, одном ЦАП и одном блоке вычитания, за счет чего и происходит сокращение аппаратных издержек по сравнению с прототипом. Каждое i-e элементарное параллельное АЦП прототипа

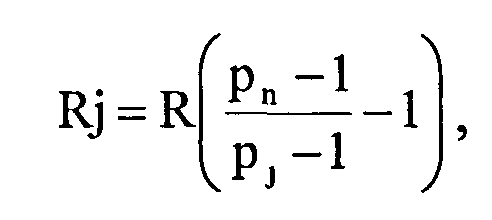

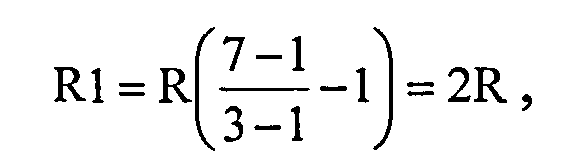

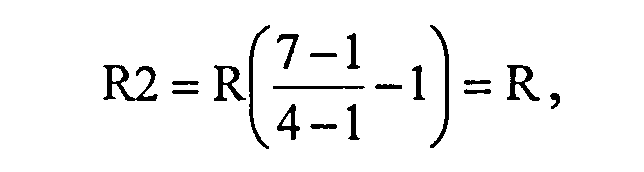

Источник напряжения смещения содержит n-1 сопротивлений, и для резистора Rj

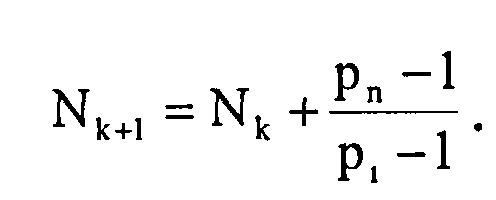

где R - номинал элементарного сопротивления из линейки резисторов, формирующих опорные напряжения в параллельном АЦП. Подключая посредством аналоговых ключей то или иное сопротивление Rj к делителю опорных напряжений АЦП, получаем j-e элементарное параллельное АЦП прототипа. Если все ключи замкнуты, то на делитель подается нулевой потенциал и получается n-е элементарное АЦП прототипа. Шифратор АЦП в зависимости от режима работы источника напряжения смещения будет принимать для дальнейшего преобразования значения компараторов, порядковые номера которых можно получить из рекуррентной формулы при

Объединение функций идентичных блоков в одном ЦАП и одном блоке вычитания дает возможность переключения коэффициента усиления сигнала на выходе. Поскольку схема ЦАП и блока вычитания основана на операционном усилителе (ОУ) (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., ил.), то переключаемый коэффициент может быть организован посредством аналоговых ключей и резисторов необходимого номинала в цепи обратной связи ОУ.

Показанный на фиг.1 АЦП в СОК содержит первый блок слежения-хранения 1, аналого-цифровой преобразователь 2, цифроаналоговый преобразователь 3, блок вычитания 4, выходные шины кодов остатков в СОК 5.1-5.n, вход 6, регистры-защелки 7.1-7.n, источник напряжения смещения 8, второй блок слежения-хранения 9.

Выход первого блока слежения-хранения 1 подключен к первому входу блока вычитания 4 и к первому входу аналого-цифрового преобразователя 2, а выход цифроаналогового преобразователя 3 соединен со вторым входом блока вычитания 4, вход устройства 6 объединен с входом второго блока слежения-хранения 9, выход которого подключен ко второму входу первого блока слежения-хранения 1, при этом выход блока вычитания 4 подключен к первому входу первого блока слежения-хранения 1, выход источника напряжения смещения 8 подключен ко второму входу аналого-цифрового преобразователя. 2, выход которого подключен к цифроаналоговому преобразователю 3 и входам регистров-защелок 7.1-7.n, при этом выход 7.i-го

Представленный на фиг.2 источник напряжения смещения содержит резисторы 10.1-10.n-1, аналоговые ключи 11.1-11.n-1 и выхода источника 12.

Выходы аналоговых ключей 11.i и резисторов 10.i

Работа АЦП в СОК осуществляется в течение n шагов для каждого i-го основания

Полный цикл преобразования начинается с того, что преобразуемое напряжение через вход 6 поступает на вход второго блока слежения-хранения 9 и запоминается.

Для вычисления остатка по основанию ps

Пример.

Рассмотрим устройство по трем основаниям СОК p1=3, p2=4, р3=7. Оно будет состоять из первого и второго блоков слежения-хранения, АЦП, источника напряжения смещения, ЦАП, блока вычитания и трех регистров-защелок. Поскольку оснований три, то количество режимов работы АЦП, источника напряжения смещения, ЦАП и блока вычитания будет три; обозначим эти режимы r1, r2 и r3. Значение остатка по каждому из оснований будет рассчитываться в течение трех шагов. Коэффициенты усиления ЦАП равны в зависимости от режима 7/3, 7/4 и 1 соответственно. Коэффициенты усиления блока вычитания равны в зависимости от режима 3, 4 и 7 соответственно. Источник напряжения смещения будет состоять из двух сопротивлений R1(10.1) и R2(10.2) и двух аналоговых ключей 11.1 и 11.2. Номиналы сопротивлений соответственно равны:

где R - номинал элементарного сопротивления из линейки резисторов, формирующих опорные напряжения в параллельном АЦП 2. Режиму r1 будет соответствовать ситуация когда ключ 11.1 разомкнут, 11.2 - замкнут, режиму r2: ключ 11.1 замкнут, 11.2 - разомкнут, и r3 - оба ключа замкнуты. Количество уровней квантования АЦП равно 7. Пусть диапазон преобразуемых АЦП напряжений - от 0 до 5 В, т.е. Е=5 В. В этом случае квантование диапазона АЦП (без смещения нуля на 1/2 младшего разряда) в зависимости от режима даст следующие значения напряжений (таблица 2).

При этом шифратор параллельного АЦП будет принимать для дальнейшего преобразования значения следующих компараторов: r1 - №№ 1, 4, 7, r2 - №№ 1, 3, 5, 7, и для r3 - №№ 1-7. Пусть преобразуемое входное напряжение Uвх.=3,2 В.

Полный цикл преобразования начинается с того, что преобразуемое напряжение через вход 6 поступает на вход второго блока слежения-хранения 9 и запоминается. Рассмотрим преобразование аналогового сигнала в код СОК в обратном порядке оснований (р3, р2 и p1).

Для вычисления остатка по основанию р3 аналоговый сигнал со второго блока слежения-хранения 9 поступает на второй вход первого блока слежения-хранения 1 и запоминается.

Первый шаг. Устройство устанавливается в режим r1. Аналоговый сигнал с первого блока слежения-хранения 1 поступает на АЦП 2, где преобразуется (согласно таблице 2 на фиг.4) в код 1. Этот код поступают на ЦАП 3. ЦАП преобразуют код в аналоговый сигнал и усиливает его согласно режима (таблица 3 на фиг.5) до 1,67 В. Полученная аналоговая величина вычитается блоком 4 из уровня сигнала на выходе первого блока слежения-хранения 1 и умножаются на коэффициент 3. В результате на выходе блока 4 образуется уровень сигнала: (3,20-1,67)·3=4,59 В, который запоминаются первым блоком слежения-хранения 1.

Следующие два шага аналогичны за исключением того, что для второго шага устанавливается режим r2, а для третьего - r3. На третьем шаге код с АЦП 2 защелкивается регистром 7.3.

Для вычисления остатка по основанию р2 аналоговый сигнал со второго блока слежения-хранения 9 поступает на второй вход первого блока слежения-хранения 1 и запоминается. После чего проводятся три шага преобразования за исключением того, что в шагах меняется порядок режимов работы устройства: первый шаг - режим r3, второй шаг - r1 и третий шаг - r2. На третьем шаге код с АЦП 2 защелкивается регистром 7.2.

Для вычисления остатка по основанию p1 повторяем процедуру за исключением того, что в шагах меняется порядок режимов работы устройства: первый шаг - режим r2, второй шаг - r3 и третий шаг - r1. На третьем шаге код с АЦП 2 защелкивается регистром 7.1.

Коды и уровни сигналов на выходе блоков устройства, полученные в процессе вычисления остатков по основаниям р3, р2 и p1, представлены в таблице 4 (фиг.6). Таким образом, код в СОК по основаниям p1=3, p2=4, р3=7 равен 2, 1, 4.

Проверим полученный результат. Рассмотрим параллельный АЦП (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., ил., рис.9.49) (без смещения нуля на 1/2 младшего разряда), состоящий из делителя опорных напряжений, компараторов, количество которых Р=3·4·7=84, и шифратора. Измеряемое напряжение равно 3,2 В. Получив таблицу опорных напряжений (таблица 5 на фиг.7), кратных Е/84, где Е=5В, обнаруживаем, что компараторы с 1-го по 53-й установятся в «1», а все остальные в «0». Следовательно, на выходе шифратора установится код, десятичное представление которого равно 53. Целые остатки от деления числа 53 на 3, 4 и 7 соответственно равны 2, 1 и 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2010 |

|

RU2433527C1 |

| АЛИАСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2589388C1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1531006A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПО МОДУЛЮ m | 2020 |

|

RU2747568C1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Устройство для поверки цифроаналоговых преобразователей | 1987 |

|

SU1578809A1 |

Изобретение относится к области измерительной и вычислительной техники и может быть использовано для быстрого преобразования аналоговых электрических сигналов в цифровой код в системах, функционирующих в системе остаточных классов (СОК). Технический результат - упрощение конструкции. Аналого-цифровой преобразователь в код СОК содержит вход, первый и второй блоки слежения-хранения, аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, источник напряжения смещения, регистры-защелки, выходные шины кодов остатков в СОК. Сущность изобретения заключается в объединении функций идентичных блоков в одном АЦП, одном ЦДЛ и одном блоке вычитания. 7 ил.

Аналого-цифровой преобразователь в системе остаточных классов, содержащий вход, n выходных шин кодов остатков в системе остаточных классов, где n - число оснований системы остаточных классов, первый блок слежения-хранения, аналогово-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, при этом выход первого блока слежения-хранения подключен к первому входу блока вычитания и к первому входу аналого-цифрового преобразователя, а выход цифроаналогового преобразователя соединен со вторым входом блока вычитания, отличающийся тем, что введены источник напряжения смещения, второй блок слежения-хранения, n регистров-защелок, при этом вход устройства объединен с входом второго блока слежения-хранения, выход которого подключен ко второму входу первого блока слежения-хранения, при этом выход блока вычитания подключен к первому входу первого блока слежения-хранения, выход источника напряжения смещения подключен ко второму входу аналого-цифрового преобразователя, выход которого подключен к цифроаналоговому преобразователю и входам n регистров-защелок, при этом выход i-го  регистра-защелки объединен с i-й выходной шиной кода остатков.

регистра-защелки объединен с i-й выходной шиной кода остатков.

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2010 |

|

RU2433527C1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| JP 60021580 A, 20.09.1985 | |||

Авторы

Даты

2015-04-10—Публикация

2014-01-09—Подача