ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к сдвиговому регистру для использования в вентиль-формирователе дисплейной панели и т.д.

УРОВЕНЬ ТЕХНИКИ

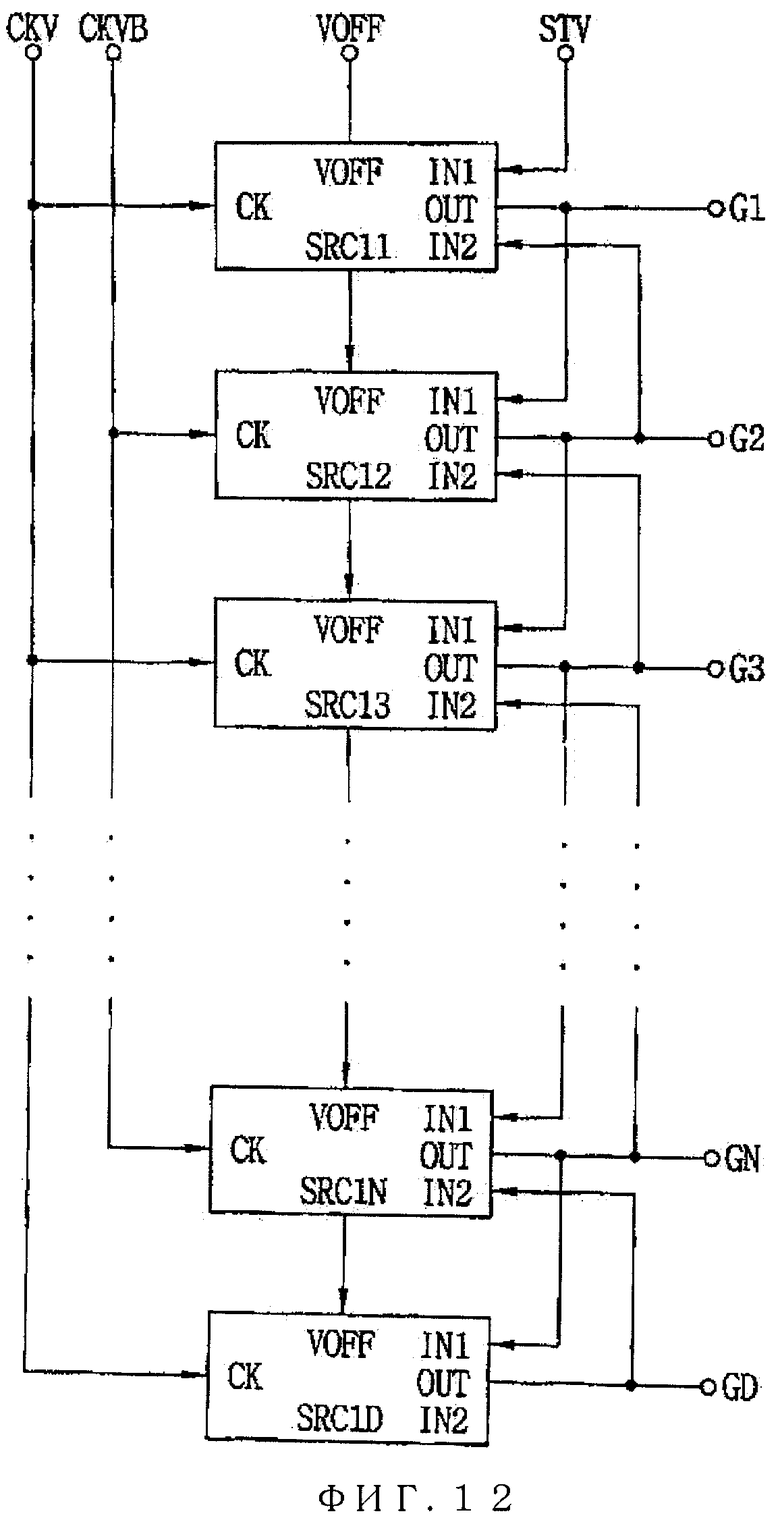

В последние годы, с целью снижения стоимости развивалось производство интегрального вентиль-формирователя. Интегральным вентиль-формирователем называется вентиль-формирователь, который сформирован из аморфного кремния на жидкокристаллической панели. Термин "интегральный вентиль-формирователь" также соответствует таким терминам, как "вентиль без формирователя", "встроенный в панель вентиль-формирователь" и "вентиль в панели". На Фиг.12 приведена структура такого вентиль-формирователя (схема управления разверткой), описанного в Патентном источнике 1. Вентиль-формирователь устроен таким образом, что единичные разряды SRC11, SRC12, … SRC1N и SRC1D располагаются каскадом друг за другом. К тактовому выводу СК каждого нечетного единичного разряда подключается первый тактовый генератор CKV, а к тактовому выводу СК каждого четного единичного разряда подключается второй тактовый генератор CKVB. Первый тактовый генератор CKV и второй тактовый генератор CKVB находятся в противофазе. С выходного вывода OUT отпирающий сигнал (G1, G2, … GN,GD) подается на линию шины вентиля.

На первый входной вывод IN1 первого единичного разряда SRC11 подается сигнал STV запуска развертки, а к соответствующим входным выводам IN1 последующих единичных разрядов (SRC12, SRC13, … SRC1N, и SRC1D) подаются отпирающие сигналы с предшествующих им единичных разрядов. На соответствующие вторые входные выводы IN2 единичных разрядов SRC11, SRC12, … и SRC1N подаются отпирающие сигналы со следующих после них единичных разрядов. Каждый из единичных разрядов имеет первый вывод напряжения VOFF.

Список упомянутых материалов:

Патентный источник 1

Заявка на патент Японии Tokukai, No.2005-50502 А (Дата публикации 24 февраля 2005 г.).

Патентный источник 2

Заявка на патент Японии Tokukai, No.2000-155550 А (Дата публикации 6 июня 2000 г.).

Патентный источник 3

Заявка на патент Японии Tokukai, No.2003-016794 А (Дата публикации 17 января 2003 г.).

Патентный источник 4

Заявка на патент Японии Tokukaihei, No.6-216753 А (Дата публикации 5 августа 1994 г.).

Патентный источник 5

Заявка на патент Японии Tokukai, No.2003-346492 А (Дата публикации 5 декабря 2003 г.)

Патентный источник 6

Перевод приложения РСТ, Tokuhyo, No.2008-508654 А (Дата публикации 21 марта 2008 г.)

Сущность изобретения

Техническая проблема

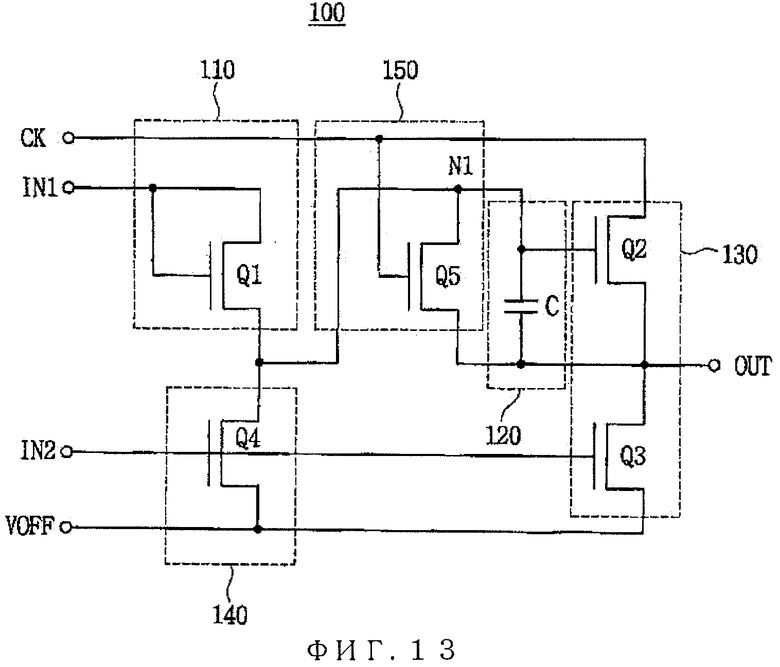

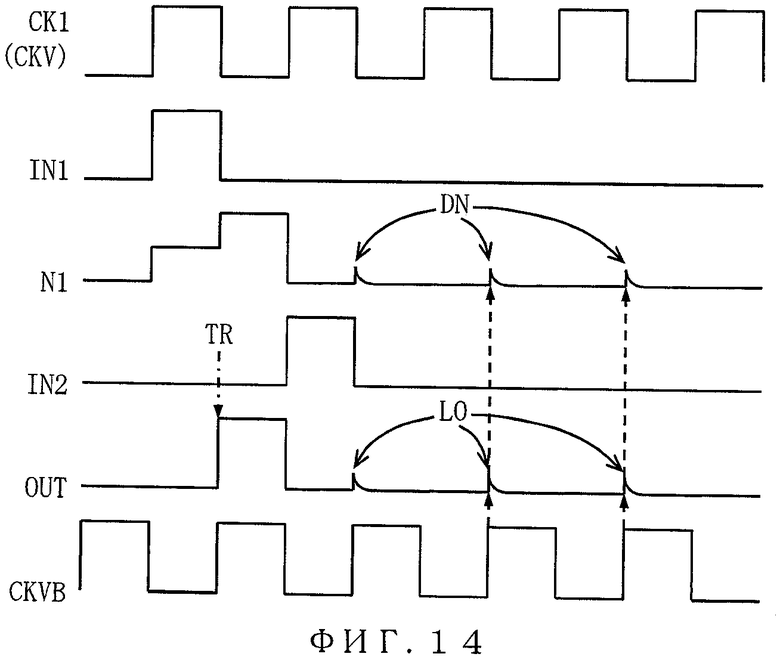

Патентный источник 1 раскрывает схемотехническую структуру единичного разряда 100 (см. Фиг. 13), как каждого из единичных разрядов SRC11, SRC12, … SRC1N, и SRC1D. Единичный разряд 100 содержит буферную секцию 110, секцию 120 загрузки, секцию 130 управления, секцию 140 выгрузки и секцию 150 задержки. Ниже описывается функционирование данной схемы, основываясь на предположении, что первый тактовый генератор CKV или второй тактовый генератор CKVB по Фиг.14, установленный заявителем настоящей заявки, подключается к единичному разряду 100. В частности, когда единичный разряд 100 является нечетным, первый тактовый генератор по Фиг.14 подключается к тактовому выводу СК, тогда как в случае, если единичный разряд 100 является четным, к тактовому выводу подключается второй тактовый генератор CKVB по Фиг.14. Первый генератор CKV и второй тактовый генератор CKVB находятся в противофазе.

Дальнейшее описание приводится исходя из примера, в котором единичный разряд 100 является четным.

Как показано на Фиг.14, когда отпирающий сигнал подается с предыдущего единичного разряда 100 на первый входной вывод IN1, т.е. на затвор и сток транзистора Q1 буферной секции 110, транзистор Q1 отпирается, что заряжает конденсатор С секции 120 загрузки. Это приводит к тому, что транзистор Q2 секции 130 управления отпирается. Затем отпирающий сигнал, подаваемый с предыдущего единичного разряда 100 на первый входной вывод IN1, переходит в состояние с низким потенциалом, что приводит к закрытию транзистора Q1. Впоследствии, когда прикладывается электрический потенциал высокого уровня со второго тактового генератора CKVB к стоку транзистора Q2, электрический потенциал узла N1 повышается благодаря эффекту вольтодобавки конденсатора С. Это в достаточной мере снижает сопротивление канала транзистора Q2. В результате чего на вывод OUT приходит отпирающий сигнал, имеющий почти такую же амплитуду, как и тактовый импульс.

Отпирающий сигнал, подаваемый таким образом из единичного разряда 100 следующего разряда, приходит на второй входной вывод IN2 единичного разряда 100 настоящего разряда. Это приводит к тому, что транзистор Q3 секции 130 управления и транзистор Q4 секции 140 выгрузки отпираются. В результате выходной вывод OUT, линия шины вентиля и узел N1 подключаются к первому выводу напряжения VOFF и переходят в состояние с низким потенциалом.

Во время функционирования других единичных разрядов 100 транзистор Q5 секции 150 задержки отпирается каждый раз, когда второй тактовый генератор CKBV переходит в состояние с высоким потенциалом, так что узел N1 периодически подключается к выходному выводу OUT.

Нечетный единичный разряд 100 функционирует таким же образом в промежутках времени, отличающихся от указанных на Фиг.14 на 1 тактовый импульс.

В соответствии с данной схемотехнической структурой с интегральными вентилями, даже если используются только n-канальные пленочные транзисторы, сопротивление канала выходного транзистора, такого как транзистор Q2, может быть значительно уменьшено благодаря эффекту вольтодобавки, что таким образом увеличит нагрузочную способность. Это дает следующие преимущества. В частности, даже в случае когда вентиль-формирователь создается из такого вещества, как аморфный кремний, из которого можно создавать только тонкопленочные n-канальные транзисторы и который интегрально встроен в панель, то можно в значительной степени преодолеть неблагоприятные свойства тонкопленочных транзисторов на аморфном кремнии, такие как высокое пороговое напряжение и низкая подвижность электронов и для удовлетворения требования уменьшения напряжения панели. Тем не менее, обычная схема с интегральными вентилями имеет следующий недостаток. Он заключается в том, что так как выходной транзистор, представленный транзистором Q2 на Фиг.13 имеет паразитную емкость между затвором и стоком (здесь и далее называемую паразитной емкостью стока) и паразитную емкость между затвором и истоком (здесь и далее называемую паразитной емкостью истока), то в выходном сигнале с затвора появляются искажения.

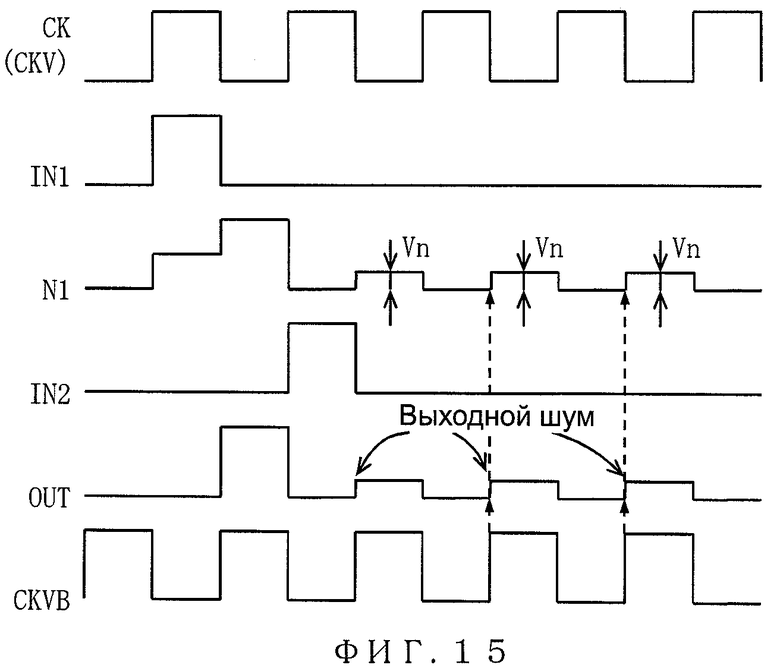

К стоку затвора Q2 постоянно приложено напряжение тактового генератора с тактового вывода СК. Соответственно, даже на протяжении периода, когда транзистор Q2 должен быть закрыт, колебания DN электрического потенциала узла N1 появляются через паразитную емкость стока из-за так называемого явления сквозного пропускания каждый раз при возникновении тактового импульса, как показано на Фиг.4. Это приводит к утечкам на транзисторе Q2. В случае если на транзисторе Q2 происходит утечка, с выходного вывода OUT подается сигнал утечки LO на протяжении периода, в течение которого вывод затвора должен быть в закрытом состоянии, как показано на Фиг.14. Кроме того, когда колебание DN электрического потенциала проявляется через паразитную емкость стока из-за так называемого явления сквозного пропускания до такой степени, что электрические потенциал узла N1 превышает пороговый электрический потенциал транзистора Q2, транзистор Q2 отпирается. Соответственно, происходит утечка с тактового генератора на исток транзистора Q2, и вывод истока повышает электрический потенциал узла N1 через конденсатор С. Следовательно, электрический потенциал узла N1 увеличивается на Vn в период тактового импульса, а импульс OUTnoise, который возникает с шириной импульса, равной периоду тактового импульса, подается на выходной вывод OUT.

На протяжении периода, в который отпирающий импульс должен подаваться на выходной вывод OUT, колебание DN электрического потенциала узла N1, которое появляется через паразитную емкость стока, проявляется в увеличении пропускной способности транзистора Q2. Это происходит по причине того, что колебание DN электрического потенциала узла N1 уменьшает сопротивление канала транзистора Q2 и увеличивает электрический ток. Однако, так как отпирающий импульс должен подаваться на выходной вывод OUT только один раз в одном кадре, колебание DN электрического потенциала узла N1 становится шумом на протяжении периода, отличного от периода подачи отпирающего импульса. Например, в панели разрешения WXGA, которая имеет 768 линий шины вентиля, повышение электрического потенциала узла N1 становится шумом на протяжении периодов (i), относящихся к 767 тактовым импульсам, иным, нежели период, в который каждый разряд подает отпирающий импульс на соответствующую линию шины вентиля и (ii) время гашения обратного хода, предоставляемое на границе между кадрами, которая определяется по сигналу вертикальной синхронизации VSync.

Благодаря паразитной емкости истока на узле N1 повышается электрический потенциал во время подачи отпирающего импульса и таким образом она повышает пропускную способность транзистора Q2. Хотя этот эффект может быть получен до известной степени только благодаря паразитной емкость истока, он усилен на Фиг.13, по которой конденсатор вольтодобавки, представляемый конденсатором С транзистора Q2, параллельно соединяется с паразитной емкостью истока. Однако в случае когда работает этот метод, не наблюдается эффект загрузки до тех пор, пока электрический потенциал выходного вывода OUT не поднимется окончательно. То есть этот метод имеет тот недостаток, что возникновение TR отпирающего импульса задерживается. Задержка возникновения TR приводит к искажению формы сигнала отпирающего импульса.

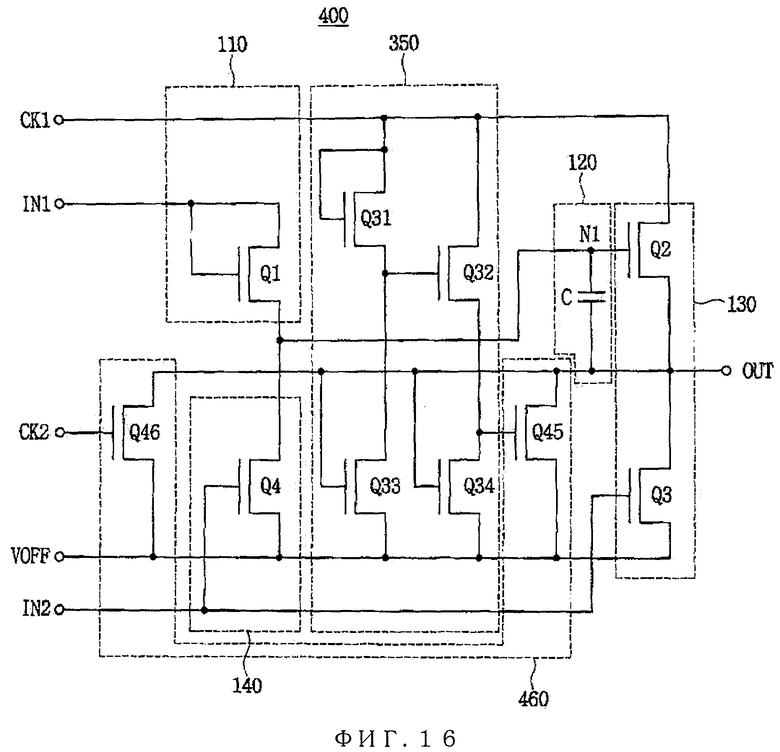

Как описано выше, устройство разряда по Фиг.13 имеет недостаток в том, что на выходе разряда появляется шум. Кроме того, поскольку выход каждого разряда подключен к последующему разряду, шум цепной реакцией распространяется по последующим разрядам, что может привести к неправильному срабатыванию сдвигового регистра. В связи с этим в Патентном источнике 1 раскрывается другое устройство регистра (см. Фиг.16) для предотвращения накопления и распространения выходного шума регистра путем добавления цепей. По Фиг.16 привносятся транзисторы Q45 и Q46 таким образом, что выходной вывод OUT и линия шины вентиля подключаются к первому выводу напряжения VOFF каждый раз, когда возникает тактовый импульс в периоды, отличные от периода отпирающего импульса. Таким образом на выходном выводе OUT и линии шины вентиля устанавливается низкий потенциал. В этом случае предлагается управляющая схема, состоящая из транзисторов от Q31 до Q34, действующая таким же образом, как транзистор Q45. Кроме того, единичный разряд 400 имеет два тактовых вывода, то есть первый тактовый выход CK1 и второй тактовый выход CK2 для того, чтобы продлить период подключения первого вывода напряжения VOFF. К первому тактовому выводу CK1 и второму тактовому выводу CK2 подключаются соответствующие тактовые генераторы, имеющие противоположные фазы, таким образом, что транзистор Q45 и транзистор Q46 включаются поочередно.

Тем не менее, конфигурация по Фиг.16 требует добавления цепи, как описано выше. Это ведет к увеличению числа элементов схемы и площади, занимаемой схемой, и, следовательно, не является предпочтительным вариантом.

Настоящее изобретение было получено с учетом вышеописанных оговоренных проблем, и целью настоящего изобретения является создание сдвигового регистра и дисплейного устройства, каждое из которых может хорошо подавить шумы каждого вывода разряда без увеличения размера схемы.

Решение проблемы

Для достижения указанной цели сдвиговый регистр содержит одну или более схем каскадного соединения, в каждой из которых разряды соединены каскадом таким образом, что имеется возможность передачи импульса сдвига, причем

по меньшей мере одна из указанных одной или более схем каскадного соединения содержит в числе своих разрядов группу последовательных разрядов, а

каждый разряд из указанной группы последовательных разрядов содержит:

первый выходной транзистор, имеющий сток, на который подается первое постоянное напряжение, и исток, служащий первым выходным выводом, который является выходным выводом указанного каждого разряда;

второй выходной транзистор, имеющий (i) сток, на который подается первый тактовый сигнал, соответствующий указанному каждому разряду, первый тактовый сигнал, имеющий период активного тактового импульса, который не перекрывается с периодом импульса сдвига указанного каждого разряда, и (ii) исток, служащий вторым выходным выводом, который является выходным выводом указанного каждого разряда и который отличен от первого выходного вывода;

первый конденсатор, один вывод которого подключен к затвору первого выходного транзистора и затвору второго выходного транзистора; второй конденсатор, один вывод которого подключен к одному выводу первого конденсатора, а второй вывод подключен ко второму выходному выводу;

входной вентиль, на который подается импульс сдвига указанного каждого разряда и через который на один вывод первого конденсатора подается электрический потенциал на протяжении периода импульса сдвига указанного каждого разряда;

первый переключающий элемент, который имеет один вывод, подключенный к другому выводу первого конденсатора, второй вывод, на который прикладывается первое постоянное напряжение, и вывод управления проводимостью и/или запиранием, на который подается первый тактовый сигнал;

второй переключающий элемент, который имеет один вывод, подключенный к другому выводу первого конденсатора, второй вывод, на который прикладывается второе постоянное напряжение, более низкое, чем первое постоянное напряжение, и вывод управления проводимостью и/или запиранием, на который подается импульс сдвига указанного каждого разряда;

третий переключающий элемент, имеющий один вывод, подключенный к одному выводу первого конденсатора, другой вывод, на который прикладывается второе постоянное напряжение, и вывод управления проводимостью и/или запиранием, на который подается импульс сдвига, который имеет задержку по фазе относительно импульса сдвига, подаваемого со второго выходного вывода указанного каждого разряда;

четвертый переключающий элемент, имеющий один вывод, подключенный к первому выходному выводу, другой вывод, на который прикладывается второе постоянное напряжение, и вывод управления проводимостью и/или запиранием (i), на который в случае, если указанный каждый разряд не является последним разрядом в группе последовательных разрядов, подается импульс сдвига со второго выходного вывода следующего разряда, и (ii) на который в случае, если указанный каждый разряд является последним разрядом в группе последовательных разрядов, подается импульсный сигнал, фаза которого имеет задержку относительно импульса сдвига, подаваемого со второго выходного вывода последнего разряда; и

пятый переключающий элемент, имеющий один вывод, подключенный ко второму выходному выводу, второй вывод, на который подается второе постоянное напряжение, и вывод управления проводимостью и/или запиранием, соединенный с выводом управления проводимостью и/или запиранием четвертого переключающего элемента.

В соответствии с изобретением, первое постоянное напряжение подается на сток первого выходного транзистора и происходит процесс переключения конденсатора с помощью первого переключающего элемента, второго переключающего элемента и первого конденсатора. Это позволяет предотвратить явление сквозного пропускания, проявляющееся через паразитную емкость стока и паразитную емкость истока первого выходного транзистора. Таким образом можно предотвратить (i) колебания выходного напряжения, которые появляются в случае, если тактовый сигнал подается на сток первого выходного транзистора, и (ii) утечку заряда с электрода элемента изображения, которая происходит по причине колебания выходного напряжения. Это избавляет от необходимости в дополнительной цепи для частого подключения первого выходного вывода разряда к источнику с низким потенциалом.

В результате возможно обеспечить сдвиговый регистр, который способен хорошо подавлять шумы каждого вывода разряда без увеличения размера схемы.

Кроме того, можно предотвратить ситуацию, в которой электрический потенциал одного вывода первого конденсатора увеличивается из-за емкостной связи таким образом, что выходной сигнал второго выходного вывода возникает в нежелательный момент, таким образом предотвратив сбой в работе сдвигового регистра. Кроме того, возможно уменьшить число необходимых внешних входных сигналов, подаваемых на сдвиговый регистр.

Так как второй выходной транзистор используется для подачи импульса сдвига, передаваемого через разряды, размер второго выходного транзистора может быть гораздо меньше размера первого выходного транзистора, который используется для передачи за пределы сдвигового регистра. Соответственно, паразитная емкость стока второго выходного транзистора достаточно мала по сравнению с паразитной емкостью стока и паразитной емкостью истока первого выходного транзистора и с первым конденсатором. Соответственно, даже если первый тактовый сигнал подается на сток второго выходного транзистора, влияние увеличения электрического потенциала одного вывода первого конденсатора через емкостную связь можно не принимать во внимание. Кроме того, поскольку нагрузка на втором выходном выводе значительно меньше нагрузки на первом выходном выводе, то изменение нагрузки на внешней схеме сдвига уровня, которая подает управляющий сигнал для сдвигового регистра, можно не принимать во внимание. Кроме того, так как и нагрузка, подключенная к первому выходному выводу, и нагрузка, подключенная ко второму выходному выводу, возбуждаются для повышения напряжения на них через первый конденсатор и второй конденсатор, который расположен между одним выводом первого конденсатора и вторым выходным выводом, суммарное значение емкости первого конденсатора и второго конденсатора может быть равно или меньше емкости первого конденсатора в случае, когда второй конденсатор отсутствует, а размеры входного вентиля, первого переключающего элемента, второго переключающего элемента и третьего переключающего элемента могут быть уменьшены в сравнении со случаем, когда второй конденсатор отсутствует. Соответственно, можно уменьшить общую площадь схемы, использующей сдвиговый регистр в сравнении со случаем, когда второй конденсатор отсутствует. Кроме того, можно уменьшить относительное число транзисторов, особенно тонкопленочных транзисторов сдвигового регистра. Кроме того, поскольку площадь схемы, использующей сдвиговый регистр, уменьшается, то можно уменьшить размер и стоимость дисплейной панели, использующей схему в качестве формирователя. Уменьшение значения емкости и размеров элементов, таких как транзисторы, приводит к менее значительному уменьшению выхода годных изделий, обусловленному дефектами, способствуя тем самым увеличению выхода годных дисплейных панелей и снижению стоимости дисплейной панели. Кроме того, поскольку постоянное напряжение прикладывается на сток первого выходного транзистора, линия шины вентиля может управляться постоянным напряжением питания. Это позволяет значительно снизить нагрузку на внешнюю схему сдвига уровня, которая формирует управляющий сигнал для сдвигового регистра в сравнении со случаем, когда тактовый сигнал подается на сток первого выходного транзистора, так что линия шины вентиля управляется тактовым сигналом.

Кроме того, поскольку постоянное напряжение прикладывается на сток первого выходного транзистора, период времени, в который между затвором и стоком первого выходного транзистора прикладывается отрицательное смещение, продлевается. Это позволяет уменьшить рост порогового напряжения, тем самым предотвращая снижение производительности сдвигового регистра.

Для достижения указанной цели сдвиговый регистр по настоящему изобретению содержит:

одну или более схем каскадного соединения, в каждой из которых разряды соединены друг с другом каскадом таким образом, что имеется возможность передачи импульса сдвига, причем

по меньшей мере одна из указанных одной или более схем каскадного соединения содержит в числе своих разрядов группу последовательных разрядов, а

каждый разряд из указанной группы последовательных разрядов содержит:

первый выходной транзистор, имеющий сток, к которому прикладывается первое постоянное напряжение и исток, служащий первым выходным выводом, который является выходным выводом указанного каждого разряда;

второй выходной транзистор, имеющий (i) сток, на который подается первый тактовый сигнал, относящийся к указанному каждому разряду, первый тактовый сигнал, имеющий период активного тактового импульса, который не перекрывается с периодом импульса сдвига указанного каждого разряда, и (ii) исток, служащий вторым выходным выводом, который является выходным выводом указанного каждого разряда и отличен от первого выходного вывода;

третий выходной транзистор, имеющий сток, на который подается первый тактовый сигнал, и исток, служащий третьим выходным выводом, который является выходным выводом указанного каждого разряда и

который отличен от первого выходного вывода и второго выходного вывода;

первый конденсатор, один вывод которого подключен к затвору первого выходного транзистора, затвору второго выходного транзистора и третьего выходного транзистора;

второй конденсатор, один вывод которого подключен к одному выводу первого конденсатора, а другой вывод подключен ко второму выходному выводу;

второй конденсатор, один вывод которого подключен к одному выводу первого конденсатора, а другой вывод подключен к третьему выходному выводу;

входной вентиль, на который подается импульс сдвига указанного каждого разряда и через который электрический потенциал прикладывается к одному выводу первого конденсатора на протяжении длительности импульса сдвига указанного каждого разряда; первый переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на другой вывод прикладывается первое постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается первый тактовый сигнал, второй переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на второй вывод подается второе постоянное напряжение, более низкое, чем первое постоянное, а на вывод управления проводимостью и/или запиранием подается импульс сдвига указанного каждого разряда;

третий переключающий элемент, один вывод которого подключен к одному выводу первого конденсатора, а на второй вывод подается второе постоянное, а на вывод управления проводимостью и/или запиранием подается первый импульсный сигнал, отстающий по фазе от импульса сдвига, подаваемого со второго выходного вывода указанного каждого разряда;

четвертый переключающий элемент, один вывод которого подключен к первому выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается, отстающий по фазе от импульса сдвига, подаваемого со второго выходного вывода указанного каждого разряда;

и

пятый переключающий элемент, один вывод которого подключен ко второму выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а вывод управления проводимостью и/или запиранием подключен к выводу управления проводимостью и/или запиранием четвертого переключающего элемента;

сигнал, подаваемый со второго выходного вывода каждого из разрядов группы последовательных разрядов, за исключением первого разряда используется как импульс сдвига и первый импульсный сигнал для предыдущего разряда, и

сигнал, подаваемый с третьего выходного вывода каждого из разрядов группы последовательных разрядов, за исключением первого разряда используется как второй импульсный сигнал для предыдущего разряда. В соответствии с изобретением, первое постоянное напряжение прикладывается к стоку первого выходного транзистора и происходит процесс переключения конденсатора с помощью первого переключающего элемента, второго переключающего элемента и первого конденсатора. Это позволяет предотвратить явление сквозного пропускания, проявляющееся через паразитную емкость стока и паразитную емкость истока первого выходного транзистора. Таким образом можно предотвратить (i) колебания выходного напряжения, которые появляются в случае, если тактовый сигнал подается на сток первого выходного транзистора, и (ii) утечку заряда с электрода элемента изображения, которая происходит по причине колебания выходного напряжения. Это избавляет от необходимости в дополнительной цепи для частого подключения первого выходного вывода разряда к источнику с низким потенциалом. В результате возможно обеспечить сдвиговый регистр, который способен хорошо подавлять шумы каждого вывода разряда без увеличения размера схемы.

Кроме того, можно предотвратить ситуацию, в которой электрический потенциал одного вывода первого конденсатора увеличивается из-за емкостной связи таким образом, что выходной сигнал второго выходного вывода возникает в нежелательный момент, таким образом предотвратив сбой в работе сдвигового регистра. Кроме того, возможно уменьшить число необходимых внешних входных сигналов, подаваемых на сдвиговый регистр.

Так как второй выходной транзистор используется для подачи импульса сдвига, передаваемого через разряды, размер второго выходного транзистора может быть гораздо меньше размера первого выходного транзистора, который используется для передачи за пределы сдвигового регистра. Соответственно, паразитная емкость стока второго выходного транзистора достаточно мала по сравнению с паразитной емкостью стока и паразитной емкостью истока первого выходного транзистора и с первым конденсатором. Соответственно, даже если первый тактовый сигнал подается на сток второго выходного транзистора, влияние увеличения электрического потенциала одного вывода первого конденсатора через емкостную связь можно не принимать во внимание.

Кроме того, поскольку нагрузка на втором выходном выводе значительно меньше нагрузки на первом выходном выводе, то изменение нагрузки на внешней схеме сдвига уровня, которая подает управляющий сигнал для сдвигового регистра, можно не принимать во внимание. Кроме того, секция, с которой подается импульс сдвига, подаваемый на другой разряд, и сигнал сброса на один вывод первого конденсатора со второго выходного транзистора через второй выходной вывод, и секция, с которой подается сигнал сброса на выходной вывод другого разряда с третьего выходного транзистора через третий выходной вывод, располагаются отдельно друг от друга, чтобы возбуждать различные нагрузки. Это позволяет предотвратить помехи между (i) импульсом сдвига, подаваемым на другой разряд, и сигналом сброса для одного вывода первого конденсатора и (ii) сигналом сброса для выходного вывода другого разряда.

Кроме того, так как все нагрузки, подключенные к первому выходному выводу, второму выходному выводу и третьему выходному выводу, возбуждаются для повышения напряжения на них через первый конденсатор и второй конденсатор, который расположен между одним выводом первого конденсатора и вторым выходным выводом, и третий конденсатор, расположенный между одним выводом первого конденсатора и третьим выходным выводом, суммарное значение емкости первого конденсатора, второго конденсатора и третьего конденсатора может быть равно или меньше емкости первого конденсатора в случае, когда второй конденсатор и третий конденсатор отсутствуют, или может быть равно или меньше суммарной емкости первого конденсатора и второго конденсатора в случае, когда третий конденсатор отсутствует. Соответственно, размеры входного вентиля, первого переключающего элемента, второго переключающего элемента и третьего переключающего элемента могут быть уменьшены в сравнении со случаем, когда второй конденсатор и третий конденсатор отсутствуют, и в сравнении со случаем, когда третий конденсатор отсутствует. Соответственно, можно уменьшить общую площадь схемы, использующей сдвиговый регистр, в сравнении со случаем, когда второй конденсатор и третий конденсатор отсутствуют, и в сравнении со случаем, когда третий конденсатор отсутствует. Кроме того, можно уменьшить относительное число транзисторов, особенно тонкопленочных транзисторов сдвигового регистра.

Кроме того, поскольку площадь схемы, использующей сдвиговый регистр, уменьшается, то можно уменьшить размер и стоимость дисплейной панели, использующей схему в качестве формирователя. Уменьшение значения емкости и размеров элементов, таких как транзисторы, приводит к менее значительному уменьшению выхода годных изделий, обусловленному дефектами, способствуя тем самым увеличению выхода годных дисплейных панелей и снижению стоимости дисплейной панели. Кроме того, поскольку постоянное напряжение прикладывается на сток первого выходного транзистора, линия шины вентиля может управляться постоянным напряжением питания. Это позволяет значительно снизить нагрузку на внешнюю схему сдвига уровня, которая формирует управляющий сигнал для сдвигового регистра в сравнении со случаем, когда тактовый сигнал подается на сток первого выходного транзистора, так что линия шины вентиля управляется тактовым сигналом. Кроме того, поскольку постоянное напряжение прикладывается на сток первого выходного транзистора, период времени, в который между затвором и стоком первого выходного транзистора прикладывается отрицательное смещение, продлевается. Это позволяет уменьшить рост порогового напряжения, тем самым предотвращая снижение производительности сдвигового регистра.

Преимущества изобретения

Как описано выше, сдвиговый регистр по настоящему изобретению содержит

одну или более схем каскадного соединения, в каждой из которых разряды соединены друг с другом каскадом таким образом, что имеется возможность передачи импульса сдвига, причем

по меньшей мере одна из одной или более схем каскадного соединения содержит в числе своих разрядов группу последовательных разрядов, а каждый разряд группы последовательных разрядов содержит:

первый выходной транзистор, имеющий сток, к которому прикладывается первое постоянное напряжение, и исток, служащий первым выходным выводом, который является выходным выводом указанного каждого разряда;

второй выходной транзистор, имеющий (i) сток, на который подается первый тактовый сигнал, относящийся к указанному каждому разряду, первый тактовый сигнал, имеющий период активного тактового импульса, который не перекрывает период импульса сдвига указанного каждого разряда, и (ii) исток, служащий вторым выходным выводом, который является выходным выводом указанного каждого разряда и отличен от первого выходного вывода;

первый конденсатор, один вывод которого подключен к затвору первого выходного транзистора и затвору второго выходного транзистора; второй конденсатор, один вывод которого подключен к одному выводу первого конденсатора, а другой вывод подключен ко второму выходному выводу;

входной вентиль, на который подается импульс сдвига указанного каждого разряда и через который электрический потенциал прикладывается к одному выводу первого конденсатора на протяжении длительности импульса сдвига указанного каждого разряда;

первый переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на другой вывод прикладывается первое постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается первый тактовый сигнал;

второй переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на второй вывод подается второе постоянное напряжение, более низкое, чем первое постоянное, а на вывод управления проводимостью и/или запиранием подается импульс сдвига указанного каждого разряда;

третий переключающий элемент, один вывод которого подключен к одному выводу первого конденсатора, а на второй вывод подается второе постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается импульсный сигнал, отстающий по фазе от импульса сдвига, подаваемого со второго выходного вывода указанного каждого разряда;

четвертый переключающий элемент, один вывод которого подключен к первому выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а на вывод управления проводимостью и/или запиранием (i) в случае, когда указанный каждый разряд не является последним разрядом группы последовательных разрядов, подается импульс сдвига со второго выходного вывода следующего разряда, и (ii) в случае, если указанный каждый разряд является последним разрядом группы последовательных разрядов, подается импульсный сигнал, фаза которого отстает от фазы импульса сдвига, подаваемого со второго выходного вывода последнего разряда; и

пятый переключающий элемент, один вывод которого подключен ко второму выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а вывод управления проводимостью и/или запиранием подключен к выводу управления проводимостью и/или запиранием четвертого переключающего элемента.

Таким образом, возможно обеспечить сдвиговый регистр, который способен хорошо подавлять шумы каждого вывода разряда без увеличения размера схемы. Кроме того, можно уменьшить общую площадь схемы, использующей сдвиговый регистр, в сравнении со случаем, когда второй конденсатор отсутствует. Кроме того, можно уменьшить относительное число транзисторов, особенно тонкопленочных транзисторов сдвигового регистра.

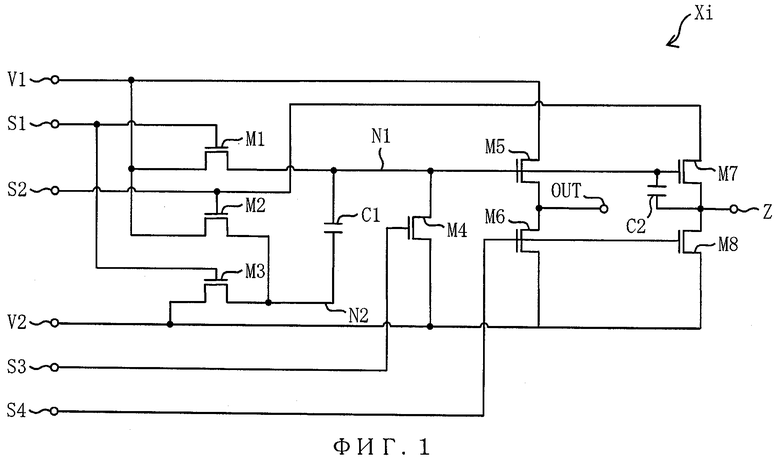

Краткое описание чертежей Фиг.1

На Фиг.1 представляет вариант реализации настоящего изобретения в виде принципиальной схемы, показывающей структуру разряда сдвигового регистра по Примеру 1.

Фиг.2

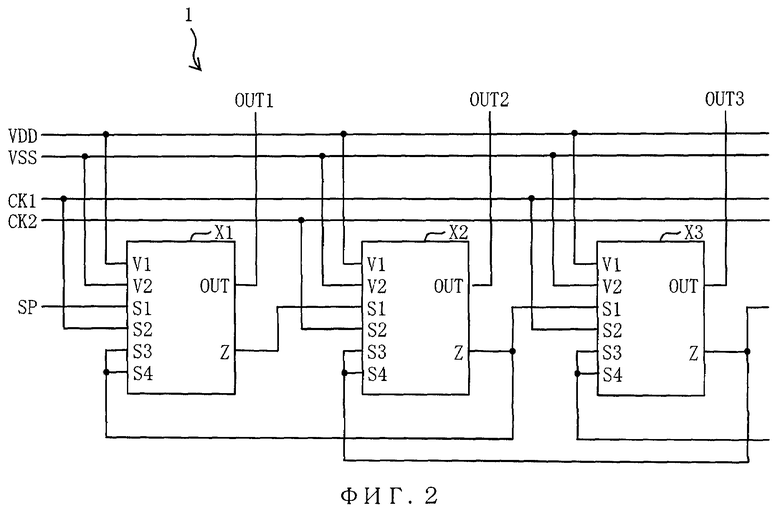

На Фиг.2 представлена блок схема, показывающая структуру сдвигового регистра по Примеру 1.

Фиг.3

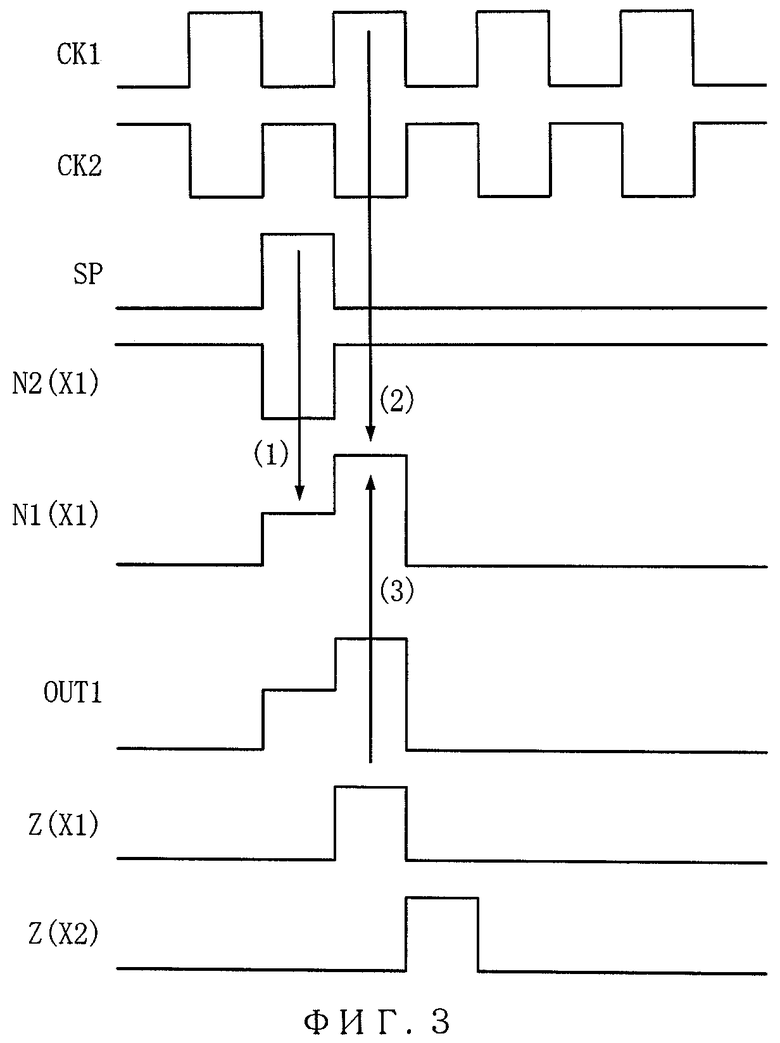

На Фиг.3 представлена временная диаграмма сигналов, показывающая действие сдвигового регистра по Примеру 1.

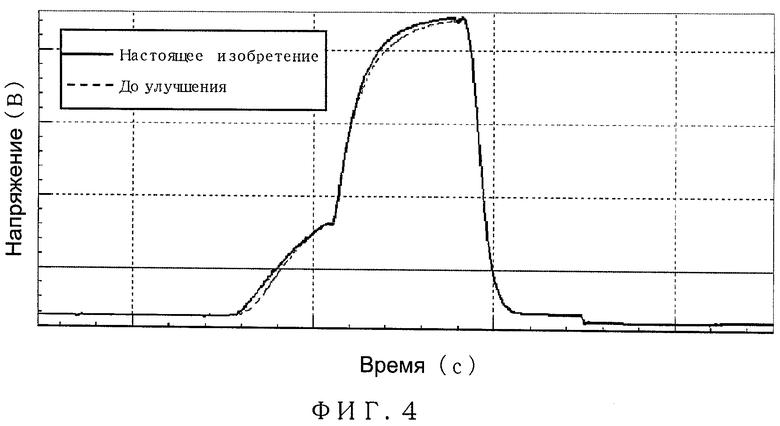

Фиг.4

На Фиг.4 представлена временная диаграмма сигналов, на которой сравниваются кривая выходного электрического потенциала сдвигового регистра по Примеру 1 и кривая, полученная до улучшения.

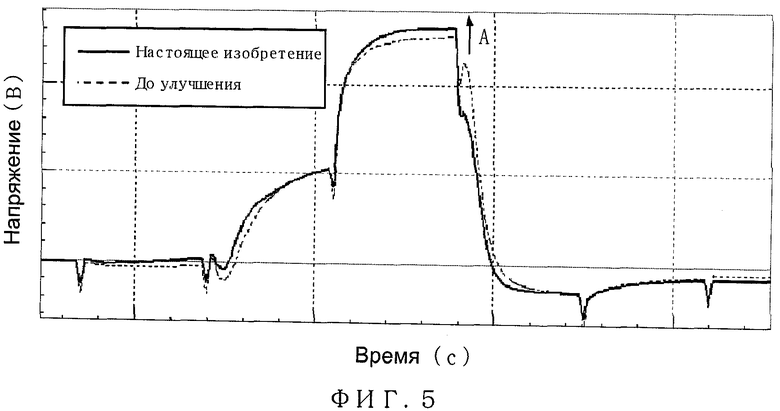

Фиг.5

На Фиг.5 представлена временная диаграмма сигналов, на которой сравниваются кривая электрического потенциала на одном выводе первого конденсатора сдвигового регистра по Примеру 1 и кривая, полученная до улучшения.

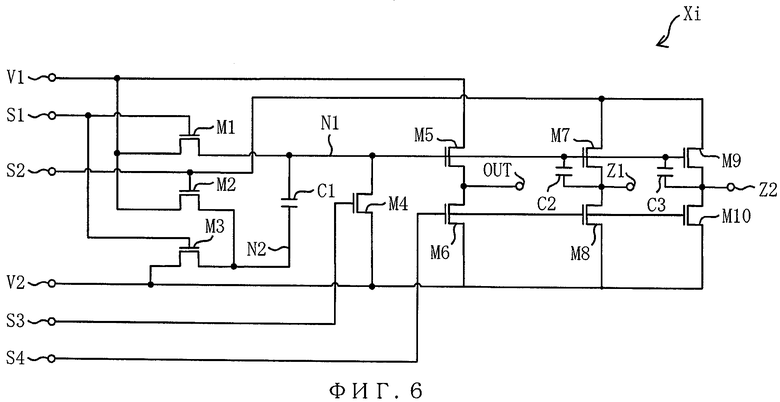

Фиг.6

На Фиг.6 представлен вариант реализации настоящего изобретения в виде блок-схемы, показывающей структуру сдвигового регистра по примеру 2.

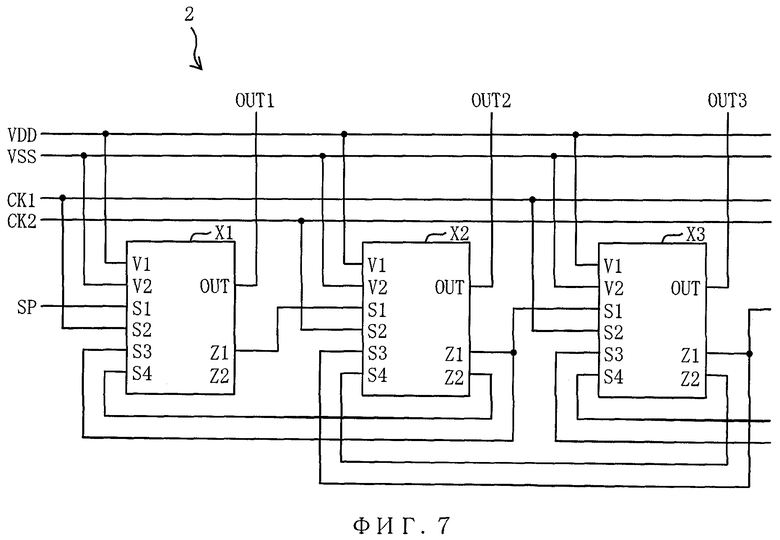

Фиг.7

На Фиг.7 представлена блок схема, показывающая структуру сдвигового регистра по Примеру 2.

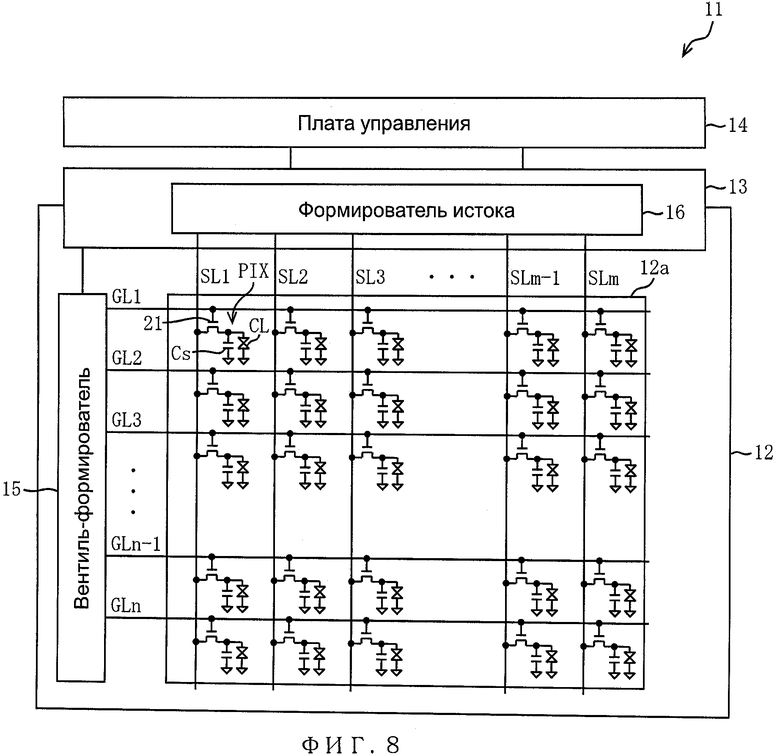

Фиг.8

На Фиг.8 представлен вариант реализации настоящего изобретения в виде блок-схемы, показывающей структуру дисплейного устройства.

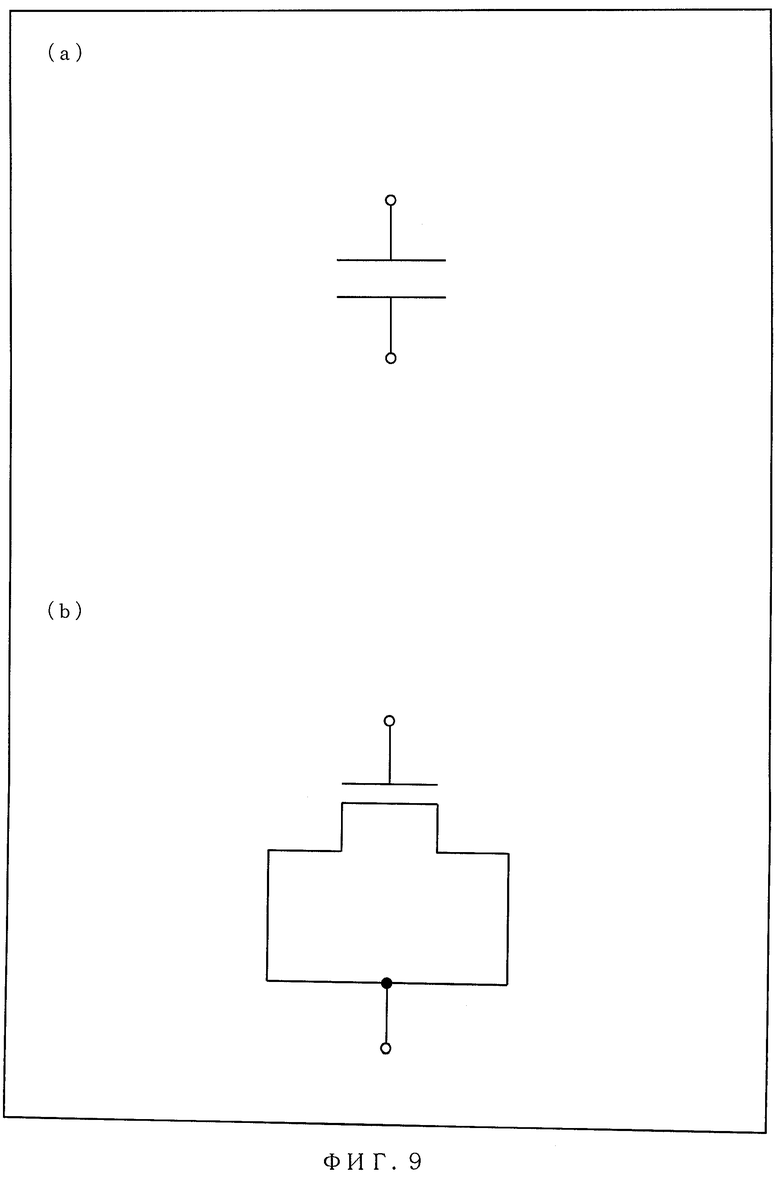

Фиг.9

На Фиг.9 представлен вариант реализации настоящего изобретения в виде принципиальной схемы, показывающей форму конденсатора, на Фиг.9 (а) представлена принципиальная схема, показывающая первую форму конденсатора, а на Фиг.9 (b) представлена принципиальная схема, показывающая вторую форму конденсатора.

Фиг.10

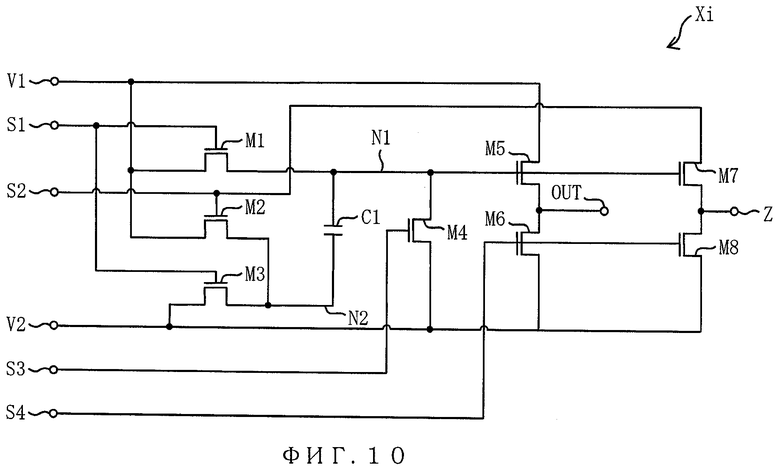

на Фиг.10 приведена принципиальная схема, показывающая структуру разряда сдвигового регистра, имеющего структуру, по Сравнительному Примеру варианта реализации настоящего изобретения.

Фиг.11

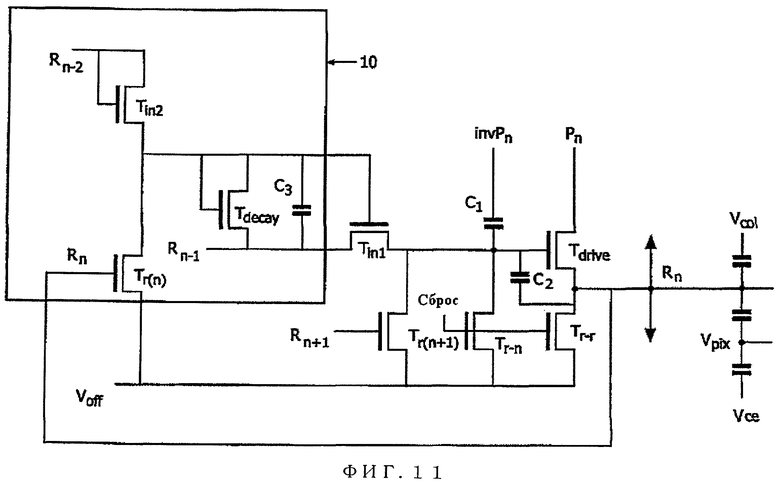

На Фиг.11 приведена отражающая текущий уровень техники принципиальная схема, показывающая типовую структуру разряда первого сдвигового регистра.

Фиг.12

На Фиг.12 приведена отражающая текущий уровень техники блок схема, показывающая структуру второго сдвигового регистра.

Фиг.13

На Фиг.13 приведена отражающая текущий уровень техники принципиальная схема, показывающая первую типовую структуру разряда второго сдвигового регистра.

Фиг.14

На Фиг.14 представлена первая временная диаграмма сигналов, на которой объясняются недостатки обычного сдвигового регистра.

Фиг.15

На Фиг.15 представлена вторая временная диаграмма сигналов, на которой объясняются недостатки обычного сдвигового регистра.

Фиг.16

На Фиг.16 приведена отражающая текущий уровень техники принципиальная схема, показывающая вторую типовую структуру разряда второго сдвигового регистра.

Описание вариантов реализации изобретения

Вариант реализации настоящего изобретения описан ниже, ссылаясь на фиг. с 1 по 11.

Фиг.8 показывает структуру жидкокристаллического дисплейного устройства 11, которое является дисплейным устройством настоящего изобретения.

Жидкокристаллическое дисплейное устройство 11 содержит дисплейную панель 12, гибкую печатную плату 13 и плату управления 14. Дисплейная панель 12 является дисплейной панелью с активной матрицей, устроенной таким образом, что использует аморфный кремний, отображающая область 12а, линии шины вентилей (линии сигналов развертки) GL, линии шины истока (линии сигналов данных) SL, и вентиль-формирователь (схема управления линиями сигналов развертки) 15 встроены на стеклянную подложку. Дисплейная панель 12 может быть произведена с использованием поликристаллического кремния, микрокристаллического кремния или подобного вида кремния. Отображающая область 12а - это область, в которой пиксели PIX расположы в виде матрицы. Каждый из пикселей PIX содержит тонкопленочный транзистор 21, который является переключающим элементом пикселя, жидкокристаллический конденсатор CL и вспомогательный конденсатор Cs. Затвор тонкопленочного транзистора 21 подключен к линии GL шины вентиля, а исток тонкопленочного транзистора 21 подключен к линии SL шины истока. Жидкокристаллический конденсатор CL и вспомогательный конденсатор Cs подключены к стоку тонкопленочного транзистора 21. Линии GL шины вентиля состоят из линий GL1, GL2, GL3, … и GLn шин вентиля и подключены к соответствующим выводам вентиль-формирователя (схема управления линией сигналов развертки) 15. Линии SL шины истока состоят из линий SL1, SL2, SL3, … SLm шины истока, которые подключены к соответствующим выводам формирователя 16 истока, который будет описан позже. Хотя это не показано, образуется линия вспомогательного конденсатора для приложения напряжения вспомогательного конденсатора к каждому вспомогательному конденсатору Cs пикселей PIX.

Вентиль-формирователь 15 размещается в одной из двух областей, прилегающих к отображающей области 12а дисплейной панели 12 в направлении, в котором идут линии GL шины вентиля и последовательно распространяется отпирающий импульс (импульс развертки) на каждую из линий GL шины вентиля. Другой вентиль-формирователь может быть размещен в другой области, прилегающей к отображающей области 12а дисплейной панели 12, в направлении, в котором идут линии GL шины вентиля, и сканировать другую группу линий GL шины вентиля, отличную от группы, сканируемой вентиль-формирователем 15. Кроме того, вентиль-формирователь, который размещен в одной из двух областей, прилегающих к отображающей области 12а дисплейной панели 12 в направлении, в котором идут линии GL шины вентиля и вентиль-формирователь, размещенный в другой из двух областей, прилегающих к отображающей области 12а дисплейной панели 12, могут сканировать одни и те же линии GL шины вентиля. Данные вентиль-формирователи встроены в дисплейную панель 12 для того, чтобы изготавливаться монолитно с отображающей областью 12а.

Примеры вентиль-формирователей могут включать все вентиль-формирователи, обозначенные такими терминами, как"монолитный вентиль-формирователь" "вентиль без формирователя", "встроенный в панель вентиль-формирователь" и "вентиль в панели". Гибкая печатная плата 13 содержит формирователь16 истока. Формирователь истока 16 подает сигнал данных на каждую из линий SL шины истока. Формирователь 16 истока может быть встроен в дисплейную панель 12 для того, чтобы изготавливаться монолитно с отображающей областью 12а. Плата управления 14 подключается к гибкой печатной плате 13 и подает необходимые сигналы и питание на вентиль-формирователь 15 и формирователь 16 истока. Сигналы и питание, которые подаются на вентиль-формирователь 15 с платы управления 14, проходят через гибкую печатную плату 13 и затем приходят на вентиль-формирователь 15 на дисплейной панели 12. Далее, со ссылками на Примеры описывается структура сдвигового регистра, предоставляемого в вентиль-формирователе 15.

[Пример 1]

Ниже описывается Пример 1 сдвигового регистра со ссылками на фиг. с 1 по 3, 10 и 11.

На Фиг.2 представлена структура сдвигового регистра 1 настоящего изобретения.

Сдвиговый регистр 1 устроен таким образом, что разряды Xi (где i - это натуральное число) соединены каскадом друг с другом. Сдвиговый регистр 1 содержит число разрядов Xi, равное числу линий шины вентиля. В настоящем Примере и последующих Примерах схема, в которой разряды Xi соединены каскадом друг с другом, будет называться схемой каскадного соединения. Каждый из разрядов Xi содержит выводы V1, V2, S1, S2, S3, S4, OUT и Z.

В каждом нечетном разряде Xi (i=1, 3, 5, …) напряжение питания (первое постоянное напряжение) VDD, которое является высоким потенциалом (т.е. потенциалом отпирающего импульса) напряжения управления вентилем, подается на вывод V1, напряжение питания (второе постоянное напряжение) VSS, которое является низким потенциалом напряжения управления вентилем, подается на вывод V2, выходной сигнал с вывода Z предыдущего разряда Xi-1 подается на вывод S1, тактовый сигнал (первый тактовый сигнал) CK1 подается на вывод S2, выходной сигнал с выхода Z последующего разряда Xi+1 подается на выводы S3 и S4, а выходной сигнал OUTi разряда Xi подается с вывода OUT. Однако следует отметить, что вместо выходного сигнала OUTi-1 на вывод S1 разряда X1 подается стартовый отпирающий импульс SP.

В каждом четном разряде Xi (i=2, 4, 6,...) напряжение питания (первое постоянное напряжение) VDD, которое является высоким потенциалом (т.е. потенциалом отпирающего импульса) напряжения управления вентилем, подается на вывод V1, напряжение питания (второе постоянное напряжение) VSS, которое является низким потенциалом напряжения управления вентилем, подается на вывод V2, выходной сигнал с вывода Z предыдущего разряда Xi-1 подается на вывод S1, тактовый сигнал (первый тактовый сигнал) CK2 подается на вывод S2, выходной сигнал с выхода Z последующего разряда Xi+1 подается на выводы S3 и S4, а выходной сигнал OUTi разряда Xi подается с вывода OUT.

Следует отметить, что второе постоянное напряжение ниже, чем первое постоянное напряжение.

На вывод S3 последнего разряда Xn подается с другого разряда выходной импульсный сигнал, фаза которого отстает на 1 импульс, выходной сигнал OUTi-1 разряда Xi схемы каскадного соединения. Примером такого выходного импульсного сигнала является выходной импульсный сигнал с выходного вывода пустого разряда, который следует за последним разрядом Xn. Пустой разряд имеет аналогичную разряду Xi структуру и не подает импульсов на линию GL шины вентиля. Выходной импульс пустого разряда называется завершающим отпирающим импульсом ЕР. Завершающий отпирающий импульс ЕР имеет аналогичную форму с импульсами выходного сигнала OUTi и отличается от импульса выходного сигнала OUTi только по фазе. То есть необходимо только, чтобы на вывод S3 каждого разряда Xi с выходного вывода другого предопределенного разряда схемы каскадного соединения подавался выходной импульсный сигнал, фаза которого отстает (в данном случае на 1 импульс) от фазы выходного сигнала OUTi разряда Xi. Кроме того, также возможно, что (i) предоставляется пустой разряд, следующий за первым разрядом Х1 и имеющий аналогичную первому разряду X1 структуру, (ii) стартовый отпирающий импульс подается на пустой разряд, и (iii) выходной импульсный сигнал пустого разряда подается на разряд X1. Эти пустые разряды предоставляются для того, чтобы первый разряд X1 и последний разряд Xn функционировали при тех же условиях, что и другие разряды Xi. То же действительно и для других Примеров.

Далее, на Фиг.1 представлена структура каждого разряда Xi сдвигового регистра 1.

Разряд Xi содержит транзисторы M1, М2, М3, М4, М5, М6, М7 и М8 и конденсаторы С1 и С2. В настоящем примере транзисторы с M1 по М8 - это n-канальные тонкопленочные транзисторы, но могут быть и р-канальными тонкопленочными транзисторами. То же действительно для всех транзисторах во всех примерах, включая транзистор М10, который описан ниже. Следует отметить, что затвор каждого переключающего элемента, описанного ниже, является выводом управления проводимостью и/или запиранием в переключающем элементе.

Затвор транзистора (входной затвор, седьмой переключающий элемент) M1 подключен к выводу S1, сток транзистора M1 подключен к выводу V1, а исток транзистора M1 подключен к узлу N1, подключенному к затвору транзистора М5. Один вывод конденсатора (первого конденсатора) С1 подключен к узлу N1.

Затвор транзистора (первый переключающий элемент) М2 подключен к выводу S2, сток транзистора М2 подключен к выводу V1, а исток транзистора М2 подключен к другому выводу конденсатора С1, который противоположен выводу, подключенному к узлу N1. Другой вывод конденсатора С1 подключен к узлу N2.

Затвор транзистора (второй переключающий элемент) М3 подключен к выводу S1, сток транзистора М3 подключен к узлу N2, а исток транзистора МЗ подключен к выводу V2.

Затвор транзистора (третий переключающий элемент) М4 подключен к выводу S3, сток транзистора М4 подключен к узлу N1, а исток транзистора М4 подключен к выводу V2.

Сток транзистора (первый выходной транзистор) М5 подключен к выводу V1, а исток транзистора М5 подключен к выводу OUT. То есть к стоку транзистора М5 прикладывается постоянное напряжение питания VDD, а исток транзистора М5 действует как первый выходной вывод, который является выходным выводом разряда Xi.

Затвор транзистора (четвертый переключающий элемент) М6 подключен к выводу S4, сток транзистора подключен к выводу OUT, а исток транзистора М6 подключен к выводу V2.

Затвор транзистора (второй выходной транзистор) М7 подключен к узлу N1, сток транзистора М7 подключен к выводу S2, а исток транзистора М7 подключен к выводу (второй выходной вывод) Z. То есть на сток транзистора М7 подается первый тактовый сигнал и исток транзистора М7 действует как второй выходной вывод, который является выходным выводом разряда Xi, отличным от первого выходного вывода. Затвор транзистора (пятый переключающий элемент) М8 подключен к выводу S4 и таким образом подключен к затвору транзистора М6, сток транзистора М8 подключен к выводу Z и исток транзистора М8 подключен к выводу V2.

Вывод Z подключен к выводу S1 другого разряда Xi, на который приходит импульс сдвига с разряда Xi настоящего разряда, импульс сдвига подается с транзистора М7. Транзистор М8 сбрасывает вывод Z в состояние с низким потенциалом.

Как описано выше, сдвиговый регистр 1 организован таим образом, что секция, с которой подается отпирающий импульс, отделена от секции, с которой подается управляющий сигнал установки/сброса, такой как сигнал установки (импульс сдвига) и сигнал сброса для другого разряда Xi.

Один вывод конденсатора (второй конденсатор) С2 подключен к затвору транзистора М7, а другой вывод конденсатора С2 подключен к выводу Z. Далее действие сдвигового регистра 1 описывается со ссылкой на Фиг.3.

Тактовый сигнал CK1 и тактовый сигнал CK2 согласованы таким образом, что их активные периоды не перекрывают друг друга. В настоящем примере тактовый сигнал CK1 и тактовый сигнал CK2 находятся в противофазе. В настоящем примере состояние с высоким потенциалом у тактовых сигналов CK1 и CK2 установлено на VDD, а состояние с низким потенциалом у тактовых сигналов CK1 и CK2 установлено на VSS. Однако необходимо только, чтобы состояние с высоким потенциалом тактовых сигналов CK1 и CK2 было равно или выше VDD, а состояние с низким потенциалом тактовых сигналов CK1 и CK2 было равно или ниже VSS. Кроме того, каждый из тактовых сигналов CK1 и CK2 и стартовый отпирающий импульс SP имели ширину импульса, соответствующую 1 горизонтальному периоду (1Н). Стартовый отпирающий импульс SP является, например, (i) импульсом, который возникает с цикличностью одного вертикального периода и который не совпадает по фазе на половину периода тактового сигнала CK1 с активным тактовым импульсом тактового сигнала CK1, или (ii) импульсом, который возникает с цикличностью одного вертикального периода и который не совпадает по фазе на половину периода тактового сигнала CK2 с активным тактовым импульсом тактового сигнала CK2. В настоящем Примере тактовый сигнал, подаваемый на вывод S2, является первым тактовым сигналом. В нечетном разряде Xi тактовый сигнал CK1 соответствует первому тактовому сигналу, а в четном разряде Xi тактовый сигнал CK2 соответствует первому тактовому сигналу. Импульс сдвига, подаваемый на разряд Xi, и первый тактовый сигнал согласованы таким образом, что их активные периоды тактовых импульсов (здесь - периоды с высоким потенциалом) не перекрывают друг друга.

Во-первых, когда стартовый отпирающий импульс SP подается как импульс сдвига на вывод S1 разряда X1, транзисторы M1 и М3 открываются. Таким образом начинает работать разряд X1. Затем последовательно подаются выходные сигналы OUTi с выводов OUT соответствующих разрядов Xi. В нижеследующем описании узел N1 разряда Xi называется "узел N1 X(i)", а узел N2 разряда Xi называется "узел N2 XQ)", а выходной сигнал с вывода Z разряда Xi называется "Z (Xi)".

Предполагается, что стартовый импульс SP подается на разряд X1, как показано на Фиг.3. В разряде X1 это приводит к тому, что напряжение прикладывается с вывода V1 к узлу N1 (X1) через транзистор M1 и приводит к тому, что напряжение питания VSS прикладывается с вывода V2 к узлу N2 (X1) через транзистор МЗ. Когда конденсатор заряжается до тех пор, пока электрический потенциал узла N1 (X1) не достигнет (напряжение питания VDD) - (пороговое напряжение Vth транзистора М1) (см. (1) по Фиг.3), транзистор M1 закрывается. В результате разность потенциалов (напряжение питания VDD) - (пороговое напряжение Vth транзистора M1) - (напряжение питания VSS) возникает между двумя выводами конденсатора С1. Это повышает электрический потенциал узла N1 (X1) и это состояние сохраняется. Следует отметить, что значение напряжения питания VDD устанавливается таким образом, чтобы напряжение (напряжение вывода Z), подаваемое на вывод S1 следующего разряда Xi+1, которое определяется электрическим потенциалом узла N1 (Xi), полученное в данный момент, было равно или меньше порогового напряжения Vth транзистора M1 следующего разряда Xi+1. В таком случае транзистор M1 действует как входной вентиль, на который подается импульс сдвига для разряда Xi и который пропускает напряжение, которое должно быть приложено к узлу N1 на протяжении периода импульса сдвига. Для разряда X1 стартовый отпирающий импульс SP служит импульсом сдвига, а для других разрядов Xi импульсом сдвига служит отпирающий импульс, содержащийся в выходном сигнале OUTi-1 предыдущего разряда Xi-1. Далее, в разряде X1 импульс сдвига (здесь - стартовый отпирающий импульс SP (выходной сигнал Z (Xi-1) предыдущего разряда в случае, если i≥2)) прерывается, что приводит к закрытию транзистора М3. Далее, тактовый сигнал CK1, который служит первым тактовым сигналом, подаваемым с вывода S2, переходит в состояние с высоким потенциалом, так что транзистор М2 открывается. Затем в результате приложения напряжения с вывода V1 электрический потенциал узла N2 (X1) становится равен (напряжение питания VDD) - (пороговое напряжение Vth). Это повышает электрический потенциал узла N1 (X1) через конденсатора С1 (см. (2) по Фиг.3), что приводит к открытию транзистора М5. В этот момент разность потенциалов VDD-Vth-VSS сохраняется между двумя выводами конденсатора С1. Соответственно, электрический потенциал V (N1) узла N1 (X1) выражается следующим уравнением:

V (N1)=(VDD-Vth-VSS)+(VDD-Vth)

=2×VDD-(VSS+2×Vth).

Соответственно, на затворе транзистора М5 имеется достаточно высокий электрический потенциал V (N1) в сравнении с VDD и транзистор М5 открыт, из-за чего имеет достаточно малое сопротивление канала. Следовательно, напряжение питания VDD подается как выходной сигнал OUT1 с вывода V1 на вывод OUT через транзистор М5. Выходной сигнал OUT (N-1) с вывода OUT становится отпирающим импульсом, амплитуда которого равна VDD-VSS. Кроме того, в этот момент также открыт транзистор М7, и высокий потенциал (активный уровень) тактового сигнала CK1 подается с вывода S2 на вывод Z. Это зависит от увеличения потенциала на затворе транзистора М7 через конденсатор С2. Это говорит о том, что конденсатор С2 также способствует повышению электрического потенциала узла N1 (X1) (см. (3) по Фиг.3). Затем импульс выходного сигнала Z (Х1) подается на вывод S1 следующего разряда Х2, который заряжает конденсатор С1 разряда Х2. Затем поскольку высокий потенциал тактового сигнала CK2, являющегося первым тактовым сигналом, подается на вывод S2, электрический потенциал узла N1 (Х2) повышается. Это приводит к тому, что транзистор М5 открывается. Следовательно, напряжение питания подается как выходной сигнал OUT2 с вывода OUT через транзистор М и затем становится отпирающим импульсом. Кроме того, высокий потенциал (активный уровень) тактового сигнала CK2 подается как выходной сигнал Z (Х2) на вывод Z через транзистор М7. Импульс выходного сигнала Z (Х2) подается на выводы S3 и S4 разряда X1. Это приводит к тому, что транзисторы М4, М6 и М8 разряда X1 открываются.

Соответственно, электрический потенциал узла N1 (X1) падает до напряжения питания VSS. Следовательно, отпирающий импульс как выходной сигнал OUT (N) и импульс сдвига как выходной сигнал Z (X1) прерываются. Таким образом, разряд X1 сбрасывается.

Таким образом, отпирающие импульсы выходных сигналов OUTi последовательно подаются на соответствующие линии GL шины вентилей.

Как описано выше, в соответствии со сдвиговым регистром 1, напряжение питания VDD, которое служит первым постоянным напряжением, прикладывается к стоку (вывод, противоположный выходной стороне вентиль-формирователя) транзистора М5, который подает отпирающий импульс, и происходит процесс переключения конденсатора с использованием транзисторов М2 и М3 и конденсатора С1. Это позволяет предотвратить (i) колебания выходного напряжения, которые появляются в случае, когда тактовый сигнал подается на сток транзистора М5, и (ii) утечку заряда с электрода жидкокристаллического элемента изображения, которая появляется в результате колебаний выходного напряжения.

Кроме того, поскольку постоянное напряжение прикладывается к стоку транзистора М5, линия шины вентиля может управляться постоянным напряжением питания. Благодаря этому можно достичь значительного снижения нагрузки на внешнюю схему сдвига уровня, которая подает управляющий сигнал для сдвигового регистра, в сравнении со случаем, когда на сток транзистора М5 подается тактовый сигнал и линия шины вентиля управляется тактовым сигналом.

Поскольку постоянное напряжение прикладывается к стоку транзистора М5, то период времени, на протяжении которого отрицательное смещение прикладывается между затором и стоком транзистора М5, становится длиннее. Это может уменьшить рост порогового напряжения. Поскольку линия шины вентиля не управляется тактовым сигналом, тактовый сигнал может иметь любую амплитуду. В частности, состояние с низким потенциалом может быть установлено на VSS или ниже, а состояние с высоким потенциалом может быть установлен на VDD или выше. В случае когда состояние с высоким потенциалом имеет уровень выше, чем VDD, то ток открытого транзистора, на затвор которого подается сигнал с высоким потенциалом, позволяет тем самым улучшить скорость работы. В случае когда состояние с низким потенциалом имеет уровень ниже, чем VSS, то ток закрытого транзистора, на затвор которого подается сигнал с низким потенциалом, падает, что позволяет предотвратить неправильное срабатывание схемы сдвига уровня из-за тока утечки.

Кроме того, в случае когда состояние с низким потенциалом устанавливается на уровень ниже, чем VSS, потенциал затвора может быть уменьшен по сравнению с потенциалом истока и потенциалом стока. Это дает возможность уменьшить изменение во времени порогового напряжения Vth, которое возникает из-за составляющей постоянного напряжения, прикладываемой к затвору, благодаря чему предотвращается снижение производительности регистра.

Согласно топологии схемы, раскрытой в Патентном источнике 1, тактовый сигнал подается на сток выходного транзистора Q2 (см. Фиг.13 и 16). Соответственно, появляются выходные колебания на каждом тактовом генераторе по причине сквозного пропускания тактового генератора. Для того чтобы подавить выходные колебания, управляющий сигнал транзистора Q3 должен быть тактовым сигналом. При этом в соответствии со сдвиговым регистром 1 постоянное напряжение подается на сток транзистора М5 и, следовательно, на выводе OUT для каждого тактового генератора не появляется никакого шума. Соответственно, можно произвести действие, во время которого выходной импульс следующего разряда подается в качестве управляющего импульса на затвор транзистора М6 только один раз, так что вывод OUT поддерживает состояние с низким потенциалом до сигнала с вентиль-формирователя в следующем кадре.

Поскольку выход следующего разряда таким образом подключен к затвору транзистора М6, то там не возникает сквозного пропускания тактового генератора, которое появляется из-за прихода тактового сигнала на затвор, а также не возникает явления изменения порогового напряжения. Это хорошо позволяет предотвратить колебания электрического потенциала на выводе OUT до выхода на следующий разряд с вывода OUT.

Секция, в которой последовательные разряды Xi (см. Фиг.1) соединены друг с другом каскадом, называется группой последовательных разрядов, схема каскадного соединения в примере 2, показанном на Фиг.2, является группой последовательных разрядов. Однако настоящее изобретение не ограничивается этим. Схема каскадного соединения может отчасти содержать группу последовательных разрядов (например, может содержать группу последовательных разрядов и пустые разряды). Следует отметить, что когда пустой разряд имеет структуру, аналогичную заявленному разряду Xi, то группа, в которой пустые разряды и разряды Xi соединены каскадом друг с другом, может считаться группой последовательных разрядов. Кроме того, схема каскадного соединения может содержать группы последовательных разрядов, которые отделены одним или более разрядом, отличающимся от разряда Xi. Например, такая схема каскадного соединения предпочтительно используется в случае, когда каждая из групп последовательных разрядов управляет соответствующей группой линий GL шины вентиля. То же верно и для других Примеров.

В каждом из Примеров предоставлен только один вентиль-формирователь, но на дисплейной панели может быть предоставлена одна или более схем каскадного соединения. Это очевидно, исходя из того факта, что бывают случаи, когда вентиль-формирователь состоит из нескольких интегральных микросхем, и случаи, когда предоставляется несколько вентиль-формирователей, между которыми заключается отображающая область 12а.

В сдвиговом регистре 1 необходимо только, чтобы импульсный сигнал, фаза которого отстает от фазы импульса сдвига (здесь - выходной сигнал OUTi), подаваемого с вывода OUT разряда Xi, подавался на вывод управления проводимостью и/или запиранием третьего переключающего элемента (здесь - транзистор М4). В настоящем Примере на каждый из разрядов Xi, за исключением последнего разряда, подается выходной сигнал OUTi следующего разряда Xi+1. На последний разряд Xi может подаваться выходной сигнал с определенного разряда (например, с пустого разряда) в цепи каскадного соединения.

Кроме того, в сдвиговом регистре 1, в случае каждого разряда Xi группы последовательных разрядов, кроме последнего разряда, на вывод управления проводимостью и/или запиранием четвертого переключающего элемента (здесь - транзистор М6) приходит импульс сдвига (здесь - выходной сигнал OUTi), подаваемый с вывода OUT следующего разряда Xi+1. В случае последнего разряда на вывод управления проводимостью и/или запиранием четвертого переключающего элемента (здесь - транзистор М6) приходит импульсный сигнал, фаза которого отстает от фазы импульса сдвига, подаваемого с вывода OUTi последнего разряда Xi. На последний разряд Xi может подаваться выходной сигнал определенного разряда (например, пустого разряда) схемы каскадного соединения.

Кроме того, на затвор транзистора M1 может прикладываться третье постоянное напряжение, которое отлично от первого постоянного напряжения. Таким образом, потенциал заряда узла N1 не ограничивается напряжением питания VDD.

Далее описываются эффекты, создаваемые конденсатором С2, предоставляемом в каждом разряде Xi.

На Фиг.10 представлен разряд Xi, получаемый при удалении конденсатора С2 из разряда Xi по Фиг.1.

Согласно схеме, узел N1, потенциал на котором повышается через конденсатор С1, должен давать мощность, достаточную для подачи выходного сигнала на обе нагрузки, подключенные к выводам OUT и Z для передачи на выходные транзисторы (транзисторы М5 и М7), которые потребляют большую мощность. Соответственно, емкость конденсатора С1 должна быть увеличена для того, чтобы на процесс переключения конденсатора подавалась большая энергия для поднятия потенциала. Следовательно, размер конденсатора С1 и размеры тонкопленочных транзисторов M1, М2, М3 и М4, которые связаны с процессом заряда/разряда конденсатора С1, увеличиваются. Это увеличение размеров приводит к увеличению площади вентиль-формирователя на панели, что таким образом приводит к увеличению частоты возникновения дефектов. В результате снижается выработка годных изделий. Кроме того, увеличение размера конденсатора и транзисторов (в особенности тонкопленочных транзисторов) приводит к увеличению нагрузки на действующую цепь схемы формирователя, что невыгодно для высокоскоростного для работы на высокой скорости. В то же время, в соответствии со сдвиговым регистром 1 настоящего Примера, обе нагрузки, подключенные к выводам OUT и Z, возбуждаются для повышения напряжения через конденсатор С1 и конденсатор С2, который расположен между узлом Т1 и выводом Z. Это дает следующие преимущества.

Так как конденсатор С2 расположен между узлом Т1 и выводом Z, чтобы повышать напряжение отпирающего сигнала транзистора М7, подключенного к выводу Z, с которого подается импульс сдвига, можно обеспечить более подходящее повышение напряжения вдобавок к повышению напряжения паразитным конденсатором затвор-сток, предоставляемому в транзисторе М7. Конденсатор С2 предпочтительно располагается в непосредственной близости от транзистора М7. Значение емкости конденсатора С2 не ограничено, в частности, при условии, что паразитная емкость транзистора М7 компенсируется и обеспечивается повышение напряжения. Соответственно, значение емкости и размер конденсатора С2 не должны быть слишком большими.

(2) Поскольку добавляется конденсатор, значение емкости конденсатора С1 может быть любым при условии, что может обеспечить достаточное увеличение напряжения, главным образом, отпирающего сигнала транзистора М5, и поэтому может быть меньшим, чем в схеме, в которой напряжение на обоих транзисторах М5 и М7 повышается через конденсатор С1. (3) Поскольку конденсатор С1 имеет меньшее значение емкости, каждый из транзисторов M1, М2, М3 и М4, которые связаны с процессом заряда/разряда конденсатора С1, могут иметь меньший размер.

По причине (1) и (2) общее значение емкости конденсаторов С1 и С2 может быть равным или меньшим, чем значение емкости конденсатора С1, достигнутое до улучшения, а по причине (3) размеры транзисторов M1, М2, М3 и М4 могут быть уменьшены в сравнении с размерами до улучшения. Это позволяет уменьшить общую площадь вентиль-формирователя в сравнении с той, что была до улучшения. Кроме того, можно уменьшить относительное число транзисторов, особенно тонкопленочных транзисторов в вентиль-формирователе. Поскольку может быть уменьшена площадь формирователя, можно ожидать уменьшения размера и стоимости дисплейной панели. Кроме того, уменьшение значения емкости, а также размеров приводит к менее значительному уменьшению выхода годных изделий, способствую тем самым улучшению выхода годных изделий и снижению стоимости дисплейной панели.

На Фиг.4 представлен результат моделирования колебаний электрического потенциала, который представляет выходной сигнал с вывода OUT в случае, когда предоставляется конденсатор С2, и в случае, когда не предоставляется конденсатор С2. На Фиг.5 представлен результат моделирования колебаний электрического потенциала на узле N1 в случае когда предоставляется конденсатор С2, и в случае когда не предоставляется конденсатор С2. Моделирование проводилось при условии, что пороговое значение каждого тонкопленочного транзистора изменялось с увеличением времени работы тонкопленочного транзистора, и поэтому снижалась нагрузочная способность. Сплошной линией обозначается сигнал сдвигового регистра по настоящему изобретению, который содержит конденсатор С2, а пунктирной линией обозначается сигнал сдвигового регистра без улучшения, т.е. сдвигового регистра, полученного до улучшения, который не содержит конденсатора С2.

В настоящем изобретении значение емкости конденсатора С1 составляет 1/2 от емкости конденсатора С1 сдвигового регистра, полученного до улучшения, а значение емкости конденсатора С2 составляет 1/4 от емкости конденсатора С1 сдвигового регистра, полученного до улучшения. Кроме того, в настоящем изобретении размер каждого из транзисторов M1, М2, М3 и М4 составляет 1/2 от размера в сдвиговом регистра, полученном до.

Как ясно из Фиг.4, M1, М2, М3 и М4, пропускная способность большая или равная пропускной способности сдвигового регистра, полученного до улучшения, может быть получена даже в случае когда общая емкость, а также размеры транзисторов M1, М2, М3 и М4 уменьшены. Кроме того, как видно по Фиг.5, повышение электрического потенциала на узле N1 улучшено (см. изменение А) благодаря эффекту загрузки конденсатора С1 и конденсатора С2 в сравнении со сравнительным примером.

Как описано выше, даже в случае когда общая емкость и размер тонкопленочных транзисторов уменьшаются, режим работы схемы, который в достаточной мере может выдерживать потребление на нагрузках, может быть достигнут путем повышения электрического потенциала узла N1, который становится отпирающим сигналом выходного транзистора при использовании не только конденсатора С1, но и конденсатора С2.

Ниже описывается структура, раскрываемая в Патентном источнике 6.

На Фиг.11 представлена структура сдвигового регистра, раскрытая в патентном источнике 6.

В соответствии со структурой, конденсатор С2 подключен к транзистору Tdrive, исток которого подключен к выводу сигнала СК (соединение аналогично транзистору М7 настоящего изобретения) для того, чтобы повысить напряжение на транзисторе Tdrive и конденсаторе С3, который повышает напряжение на затворе конденсатора Tin1, с которого подается отпирающий сигнал транзистора Tdrive, подключен к транзистору Tin1. То есть используются 2 загрузочных конденсатора. Однако, так как используются 2 загрузочных конденсатора, т.е. конденсаторы С2 и С3 используются для увеличения напряжения отпирающего сигнала транзистора Tdrive, необходимо добавить в операцию сдвига ввод Rn-2 для того, чтобы конденсатор СЗ повышал напряжение на затворе транзистора Tin1. Это приводит к увеличению числа сигналов и соединений для работы сдвигового регистра. Так как число проводящих слоев в ЖК-панели, на которой создается схема, как правило, ограничено, то увеличение числа соединительных сигналов не желательно.

Таких трудностей не возникает в сдвиговом регистре 1 настоящего изобретения.

[Пример 2]

Пример 2 сдвигового регистра описан ниже со ссылками на Фиг.6 и 7. На Фиг.7 представлена структура сдвигового регистра 2 настоящего Примера.

Сдвиговый регистр 2 устроен таким образом, что разряды Xi (где i - натуральное число) соединены каскадом друг с другом. Сдвиговый регистр 1 содержит число разрядов Xi, равное числу линий шины вентиля. Каждый из разрядов Xi содержит выводы V1, V2, S1, S2, S3, S4, OUT, Z1 и Z2.

В каждом нечетном разряде Xi (i=1, 3, 5, …) напряжение питания (первое постоянное напряжение) VDD, которое является высоким потенциалом (т.е. потенциалом отпирающего импульса) напряжения управления вентилем, подается на вывод V1, напряжение питания (второе постоянное напряжение) VSS, которое является низким потенциалом напряжения управления вентилем, подается на вывод V2, выходной сигнал с вывода Z предыдущего разряда Xi-1 подается на вывод S1, тактовый сигнал (первый тактовый сигнал) CK1 подается на вывод S2. На вывод S3 подается выходной сигнал с вывода Z1 следующего разряда Xi+1, а на вывод S4 подается выходной сигнал с вывода Z2 следующего разряда Xi+1. С вывода OUT подается выходной сигнал OUTi разряда Xi. Однако следует отметить, что вместо выходного сигнала OUTi-1 на вывод S1 разряда X1 подается стартовый отпирающий импульс.

В каждом четном разряде Xi (i=2, 4, 6, …) напряжение питания (первое постоянное напряжение) VDD, которое является высоким потенциалом (т.е. потенциалом отпирающего импульса) напряжения управления вентилем, подается на вывод V1, напряжение питания (второе постоянное напряжение) VSS, которое является низким потенциалом напряжения управления вентилем, подается на вывод V2, выходной сигнал с вывода Z предыдущего разряда Xi-1 подается на вывод S1, а тактовый сигнал (первый тактовый сигнал) CK2 подается на вывод S2. На вывод S3 подается выходной сигнал с вывода Z1 следующего разряда Xi+1, а на вывод S4 подается выходной сигнал с вывода Z2 следующего разряда Xi+1. С вывода OUT подается выходной сигнал OUTi разряда Xi. В предыдущем Примере сигнал, поступающий на вывод S3, назывался первым импульсным сигналом, а сигнал, поступавший на вывод S4, назывался вторым импульсным сигналом. Первый импульсный сигнал и второй импульсный сигнал, подаваемые на каждый разряд Xi - это импульсные сигналы, фазы которых отстают от фазы импульса сдвига, подаваемого с вывода Z1 разряда Xi.

Следует отметить, что второе постоянное напряжение ниже, чем первое постоянное напряжение.

Далее, на Фиг.6 показана структура каждого разряда Xi сдвигового регистра 2.

Сдвиговый регистр 2 получается путем добавления транзисторов М9 и М10 и конденсатора С3 к разряду Xi сдвигового регистра 1 по Фиг.1. Вывод Z разряда Xi сдвигового регистра 1 называется выводом Z1. Затвор транзистора (третий выходной транзистор) М9 подключен к узлу N1, сток транзистора М9 подключен к выводу S2, а исток транзистора М9 подключен к выводу (третий выходной вывод) Z2. То есть на сток транзистора М9 подается первый тактовый сигнал, а исток транзистора М9 работает как третий выходной вывод, который является выходным выводом разряда Xi, отличным от первого выходного вывода и второго выходного вывода.

Затвор транзистора (шестой переключающий элемент) М10 подключен к выводу S4 и таким образом подключен к затвору транзистора Мб, а сток транзистора М10 подключен к выводу Z2, а исток транзистора М10 подключен к выводу V2.

Импульс, подаваемый с вывода Z1, приходит в качестве импульса сдвига на вывод S1 следующего разряда Xi+1 и на выход S3 предыдущего разряда Xi-1, так чтобы сбросить узел N1 разряда Xi-1 в состояние с низким потенциалом.

Импульс, подаваемый с вывода Z2, приходит на вывод S4 предыдущего разряда Xi-1, чтобы сбросить выводы OUT, Z1 и Z2 разряда Xi-1 в состояние с низким потенциалом.

Как описано выше, сдвиговый регистр 1, секция, с которой подается сигнал установки (импульс сдвига) для другого разряда Xi и сигнал сброса (первый импульсный сигнал) для узла N1, и секция, с которой подается сигнал сброса (второй импульсный сигнал) для выходных выводов другого разряда Xi, отделены друг от друга так, чтобы возбуждать соответствующие нагрузки. Это позволяет предотвратить помехи между (i) сигналом установки (импульсом сдвига) для другого разряда Xi и сигналом сброса (первый импульсный сигнал) для узла N1 и (ii) сигналом сброса (второй импульсный сигнал) для выходных выводов другого разряда Xi.

Один вывод конденсатора (третий конденсатор) С3 подключен к затвору транзистора М9, а другой вывод конденсатора С3 подключен к выводу Z2.

Сигнал, подаваемый с вывода Z1 каждого из разрядов Xi группы последовательных разрядов, за исключением первого разряда, используется как импульс сдвига и сигнал сброса для узла N1 предыдущего разряда Xi-1, а сигнал, подаваемый с вывода Z2 каждого из разрядов Xi группы последовательных разрядов, за исключением первого разряда, используется как импульс сдвига и сигнал сброса для выходных выводов предыдущего разряда Xi-1. В качестве сигнала сброса для последнего разряда группы последовательных разрядов и сигнала сброса для выходных выводов последнего разряда, например, могут использоваться выходные сигналы с пустого разряда. В соответствии со сдвиговым регистром 2 настоящего изобретения, конденсаторы С2 и С3 предоставляются в дальней выходной секции. Соответственно, общая емкость конденсаторов C1, С2 и С3 и размеры транзисторов M1, М2, М3 и М4 могут быть уменьшены в сравнении со случаем, когда конденсаторы С2 и С3 отсутствуют и в сравнении со случаем, когда отсутствует конденсатор С3, как в Примере 1. Кроме того, даже если общая емкость и размеры транзисторов уменьшаются, таким образом, может быть достигнут режим работы схемы, который в достаточной мере может выдерживать потребление на нагрузках. Примеры были описаны.

В Примерах каждый из конденсаторов C1, С2 и С3 может быть, например, плоским конденсатором, состоящим из двух проводящих пластин, расположенных друг напротив друга, и изолятора, заключенного между этими пластинами, как показано на Фиг.9 (а), или МОП-конденсатором, в котором сток и исток МОП-транзистора закорочены, как показано на Фиг.9 (b).

Для того чтобы достичь указанной цели, сдвиговый регистр по настоящему изобретению содержит:

одну или более схем каскадного соединения, в каждой из которых разряды соединены друг с другом каскадом таким образом, что имеется возможность передачи импульса сдвига,

по меньшей мере одну из одной или более схем каскадного соединения, содержащую в числе своих разрядов группу последовательных разрядов, а каждый разряд группы последовательных разрядов содержит:

первый выходной транзистор, имеющий сток, к которому прикладывается первое постоянное напряжение, и исток, служащий первым выходным выводом, который является выходным выводом указанного каждого разряда;

второй выходной транзистор, имеющий (i) сток, на который подается первый тактовый сигнал, относящийся к указанному каждому разряду, первый тактовый сигнал, имеющий период активного тактового импульса, который не перекрывается с периодом импульса сдвига указанного каждого разряда, и (ii) исток, служащий вторым выходным выводом, который является выходным выводом указанного каждого разряда и отличен от первого выходного вывода;

первый конденсатор, один вывод которого подключен к затвору первого выходного транзистора и затвору второго выходного транзистора; второй конденсатор, один вывод которого подключен к одному выводу первого конденсатора, а другой вывод подключен ко второму выходному выводу;

входной вентиль, на который подается импульс сдвига указанного каждого разряда и через который электрический потенциал прикладывается к одному выводу первого конденсатора на протяжении длительности импульса сдвига указанного каждого разряда;

первый переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на другой вывод прикладывается первое постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается первый тактовый сигнал, второй переключающий элемент, один вывод которого подключен к другому выводу первого конденсатора, а на второй вывод подается второе постоянное напряжение, более низкое, чем первое постоянное, а на вывод управления проводимостью и/или запиранием подается импульс сдвига указанного каждого разряда;

третий переключающий элемент, один вывод которого подключен к одному выводу первого конденсатора, а на второй вывод подается второе постоянное напряжение, а на вывод управления проводимостью и/или запиранием подается импульсный сигнал, отстающий по фазе от импульса сдвига, подаваемого со второго выходного вывода указанного каждого разряда;

четвертый переключающий элемент, один вывод которого подключен к первому выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а на управляющий вывод проводимости/запирания (i), в случае когда указанный каждый разряд не является последним разрядом группы последовательных разрядов, подается импульс сдвига со второго выходного вывода следующего разряда, и (ii) в случае если указанный каждый разряд является последним разрядом группы последовательных разрядов, подается импульсный сигнал, фаза которого отстает от фазы импульса сдвига, подаваемого со второго выходного вывода последнего разряда; и

пятый переключающий элемент, один вывод которого подключен ко второму выходному выводу, а к другому выводу прикладывается второе постоянное напряжение, а вывод управления проводимостью и/или запиранием подключен к выводу управления проводимостью и/или запиранием четвертого переключающего элемента.

В соответствии с изобретением, первое постоянное напряжение подается на сток первого выходного транзистора и происходит процесс переключения конденсатора с помощью первого переключающего элемента, второго переключающего элемента и первого конденсатора. Это позволяет предотвратить явление сквозного пропускания, проявляющееся через паразитную емкость стока и паразитную емкость истока первого выходного транзистора. Таким образом можно предотвратить (i) колебания выходного напряжения, которые появляются в случае, если тактовый сигнал подается на сток первого выходного транзистора, и (ii) утечку заряда с электрода элемента изображения, которая происходит по причине колебания выходного напряжения. Это избавляет от необходимости в дополнительной цепи для частого подключения первого выходного вывода разряда к источнику с низким потенциалом.

В результате возможно обеспечить сдвиговый регистр, который способен хорошо подавлять шумы каждого вывода разряда без увеличения размера схемы.

Кроме того, можно предотвратить ситуацию, в которой электрический потенциал одного вывода первого конденсатора увеличивается из-за емкостной связи таким образом, что выходной сигнал второго выходного вывода возникает в нежелательный момент, таким образом предотвратив сбой в работе сдвигового регистра. Кроме того, возможно уменьшить число необходимых внешних входных сигналов, подаваемых на сдвиговый регистр.