Область техники, к которой относится изобретение

Настоящее изобретение относится к сдвиговому регистру, который предоставляется в возбуждающей схеме устройства отображения с активной матрицей, а более конкретно - к сдвиговому регистру, допускающему двунаправленный сдвиг входного сигнала.

Уровень техники

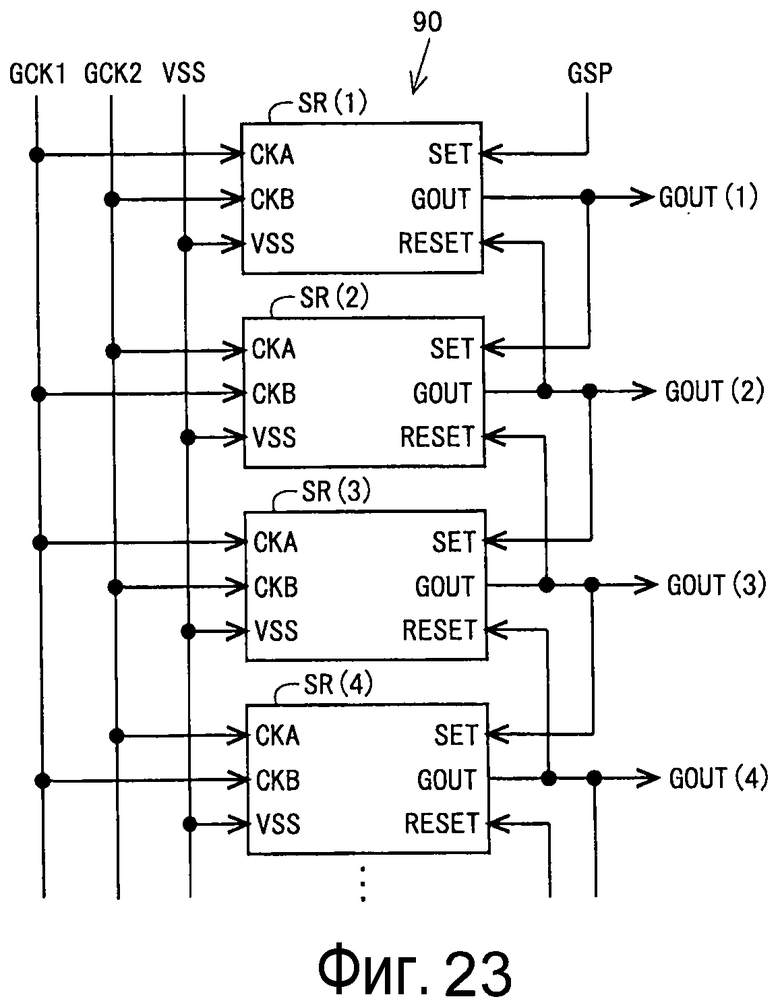

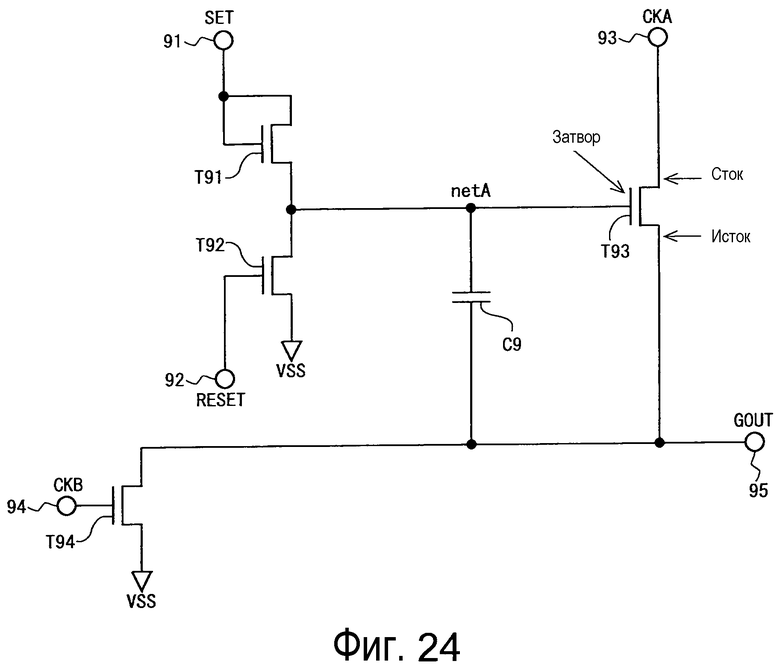

В последние годы, с целью уменьшить размер устройства отображения и сократить затраты, проводятся активные разработки устройств отображения, в которых как модуль отображения, включающий в себя пиксельную схему, так и формирователь сигналов управления затворами для возбуждения линии шины затворов (линии сигналов сканирования) формируются на одной подложке. Фиг. 23 является блок-схемой, показывающей пример конфигурации формирователя сигналов управления затворами такого традиционного устройства отображения. Помимо этого, фиг. 24 является принципиальной схемой, показывающей пример конфигурации одного каскада сдвигового регистра, который составляет формирователь сигналов управления затворами.

Как показано на фиг. 23, формирователь сигналов управления затворами включает в себя сдвиговый регистр 90 из нескольких каскадов (число каскадов, идентичное числу каскадов линий шины затворов). Каждый каскад сдвигового регистра 90 является бистабильной схемой, которая находится в любом из двух состояний (первого состояния и второго состояния) в каждый момент времени, и выводит сигнал, указывающий это состояние, в качестве сигнала сканирования. Таким образом, сдвиговый регистр 90 включает в себя несколько бистабильных схем SR. Каждая бистабильная схема SR содержит входные контактные выводы для приема двухфазных синхросигналов CKA (в дальнейшем в этом документе называемых "первым тактовым сигналом") и CKB (в дальнейшем в этом документе называемых "вторым тактовым сигналом") соответственно, входной контактный вывод для приема напряжения VSS питания с низким уровнем мощности, входной контактный вывод для приема сигнала SET задания, входной контактный вывод для приема сигнала RESET сброса и выходной контактный вывод для вывода сигнала GOUT сканирования. Сигнал GOUT сканирования, выводимый из каждого каскада (бистабильной схемы), предоставляется в следующий каскад в качестве сигнала задания, а также предоставляется в предыдущий каскад в качестве сигнала сброса.

Как показано на фиг. 24, бистабильная схема включает в себя четыре тонкопленочных транзистора T91, T92, T93 и T94 и конденсатор C9. Бистабильная схема также включает в себя четыре входных контактных вывода 91-94 и выходной контактный вывод 95 в дополнение к входному контактному выводу для напряжения VSS питания с низким уровнем мощности. Контактный вывод истока тонкопленочного транзистора T91, контактный вывод стока тонкопленочного транзистора T92 и контактный вывод затвора тонкопленочного транзистора T93 подключаются друг к другу. Следует отметить, что область (межсоединение), в которой эти контактные выводы подключаются друг к другу, называется "netA" для удобства.

В тонкопленочном транзисторе T91 контактный вывод затвора и контактный вывод стока подключаются к входному контактному выводу 91 (т.е. в диодном включении), и контактный вывод истока подключается к netA. В тонкопленочном транзисторе T92 контактный вывод затвора подключается к входному контактному выводу 92, контактный вывод стока подключается к netA, и контактный вывод истока подключается к напряжению VSS питания. В тонкопленочном транзисторе T93 контактный вывод затвора подключается к netA, контактный вывод стока подключается к входному контактному выводу 93, и контактный вывод истока подключается к выходному контактному выводу 95. В тонкопленочном транзисторе T94 контактный вывод затвора подключается к входному контактному выводу 94, контактный вывод стока подключается к выходному контактному выводу 95, и контактный вывод истока подключается к напряжению VSS питания. В конденсаторе C9 один конец подключается к netA, а другой конец подключается к выходному контактному выводу 95.

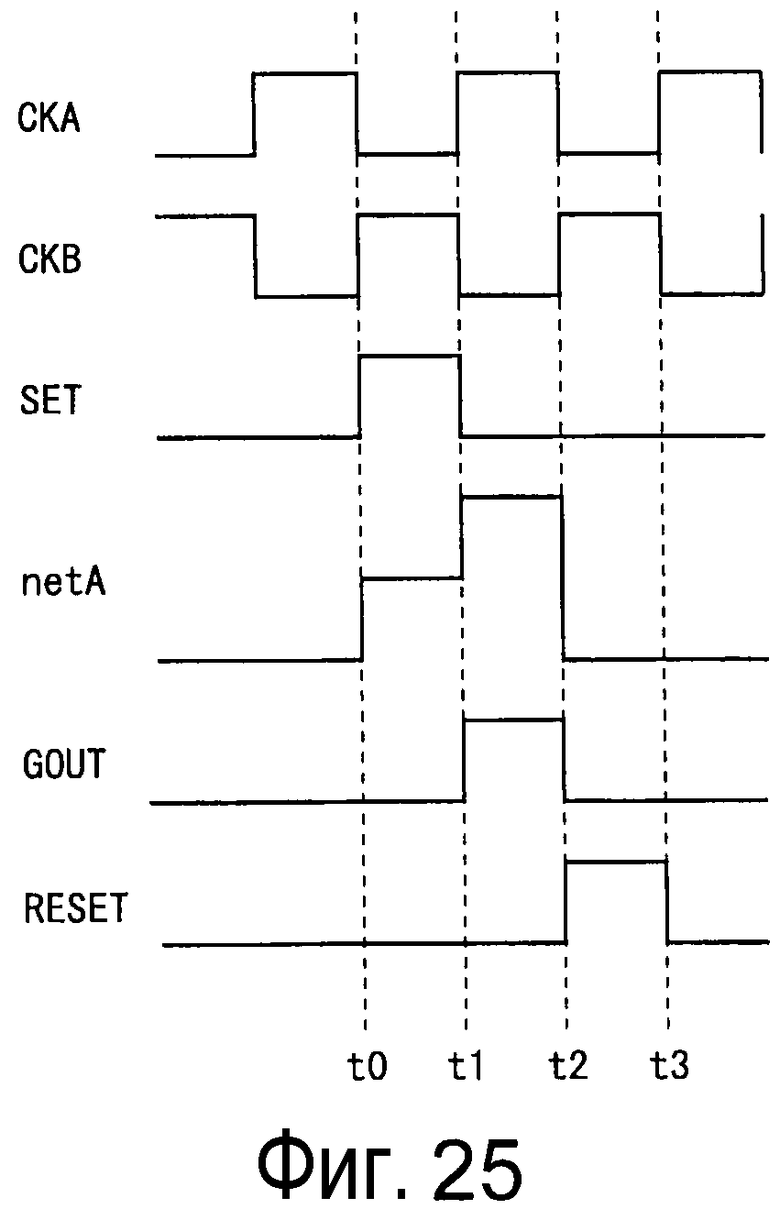

В конфигурации, как описано выше, каждый каскад (бистабильная схема) сдвигового регистра 90 работает следующим образом. Следует отметить, что фиг. 25 является временной диаграммой для описания работы каждого каскада сдвигового регистра 90. Первый тактовый сигнал CKA, который переходит к высокому уровню в каждом другом периоде горизонтального сканирования, предоставляется на входной контактный вывод 93. Второй тактовый сигнал CKB, фаза которого сдвигается на 180 градусов от фазы первого тактового сигнала CKA, предоставляется на входной контактный вывод 94. В течение периода перед моментом t0 времени потенциал netA и потенциал сигнала GOUT сканирования (потенциал выходного контактного вывода 95) имеют низкий уровень.

При достижении момента t0 времени импульс сигнала SET задания предоставляется на входной контактный вывод 91. Поскольку тонкопленочный транзистор T91 находится в диодном включении, как показано на фиг. 24, тонкопленочный транзистор T91 переходит во включенное состояние посредством импульса этого сигнала SET задания, и конденсатор C9 заряжается. Как результат, потенциал netA изменяется от низкого уровня к высокому уровню, и тонкопленочный транзистор T93 переходит во включенное состояние. В этом случае первый тактовый сигнал CKA имеет низкий уровень в период от момента t0 времени до момента t1 времени. Следовательно, в течение этого периода сигнал GOUT сканирования поддерживается на низком уровне. Кроме того, в течение этого периода, поскольку сигнал RESET сброса имеет низкий уровень, тонкопленочный транзистор T92 поддерживается в отключенном состоянии. Следовательно, потенциал netA не снижается в течение этого периода.

При достижении момента t1 времени первый тактовый сигнал CKA изменяется от низкого уровня к высокому уровню. В этом случае, поскольку тонкопленочный транзистор T93 находится во включенном состоянии, потенциал входного контактного вывода 93 увеличивается, и потенциал выходного контактного вывода 95 также увеличивается. Здесь, как показано на фиг. 24, поскольку конденсатор C9 предоставляется между netA и выходным контактным выводом 95, потенциал netA также увеличивается (netA использует компенсационную обратную связь) с увеличением потенциала выходного контактного вывода 95. Как результат, большое напряжение прикладывается к тонкопленочному транзистору T93, и потенциал сигнала GOUT сканирования увеличивается до потенциала высокого уровня первого тактового сигнала CKA. Следовательно, линия шины затворов, подключенная к выходному контактному выводу 95 бистабильной схемы, переходит в выбранное состояние. Следует отметить, что в период от момента t1 времени до момента t2 времени второй тактовый сигнал CKB имеет низкий уровень. Следовательно, поскольку тонкопленочный транзистор T94 поддерживается в отключенном состоянии, потенциал сигнала GOUT сканирования не снижается в течение этого периода.

При достижении момента t2 времени первый тактовый сигнал CKA изменяется от высокого уровня к низкому уровню. Соответственно потенциал выходного контактного вывода 95 снижается со снижением потенциала входного контактного вывода 93, и потенциал netA также снижается через конденсатор C9. Кроме того, в момент t2 времени импульс сигнала RESET сброса предоставляется на входной контактный вывод 92. Соответственно тонкопленочный транзистор T92 переходит во включенное состояние. Как результат, потенциал netA изменяется от высокого уровня к низкому уровню. Кроме того, в момент t2 времени второй тактовый сигнал CKB изменяется от низкого уровня к высокому уровню. Соответственно тонкопленочный транзистор T94 переходит во включенное состояние. Как результат, потенциал выходного контактного вывода 95, т.е. потенциал сигнала GOUT сканирования переходит к низкому уровню.

Как описано выше, сигнал GOUT сканирования, выводимый из каждого каскада (бистабильной схемы), предоставляется в следующий каскад в качестве сигнала SET задания, как показано на фиг. 23. Таким образом, несколько линий шины затворов, предоставляемых в устройстве отображения, последовательно переходят в выбранное состояние в каждом периоде горизонтального сканирования, и запись выполняется для пиксельной емкости в пиксельной схеме для каждой строки.

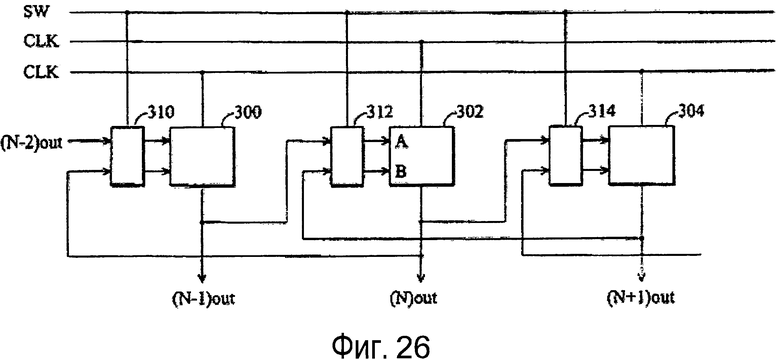

Касательно устройства отображения, как описано выше, предлагается конфигурация, которая позволяет переключаться между порядками сканирования (направлениями сканирования) линий шины затворов. Фиг. 26 является блок-схемой, показывающей конфигурацию сдвигового регистра, раскрытого в патенте (США) № 6778626. В этом сдвиговом регистре предоставляются схемы (схемы для ввода сигнала SW выбора в качестве сигнала, соответствующего порядку сканирования) 310, 312 и 314 для переключения между порядками сканирования в каждом каскаде. Порядки сканирования переключаются посредством сигнала SW выбора, который предоставляется в эти схемы 310, 312 и 314.

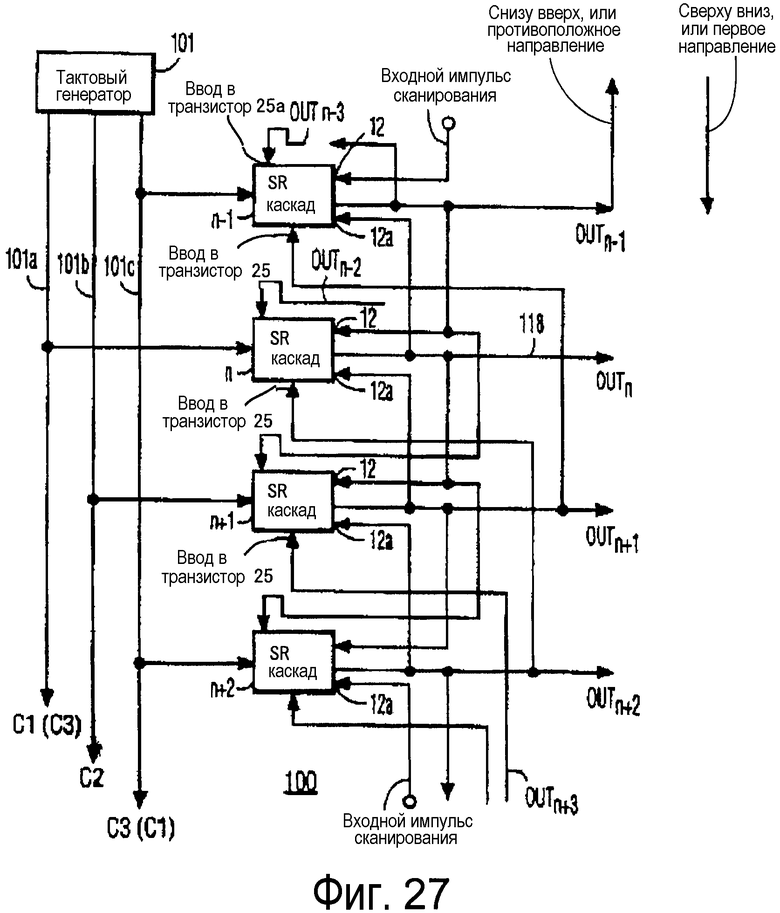

Фиг. 27 является блок-схемой, показывающей конфигурацию сдвигового регистра, раскрытого в публикации не прошедшей экспертизу заявки на патент (Япония) № 2001-506044. В этом сдвиговом регистре сигнал задания из предыдущего каскада или из следующего каскада предоставляется в каждый каскад, и сигнал сброса из второго предыдущего каскада или из второго следующего каскада предоставляется в каждый каскад. Посредством предоставления конфигурации, как описано выше, можно переключаться между порядками сканирования линий шины затворов без использования сигнала выбора для переключения между порядками сканирования.

Цель предоставления возможности переключаться между порядками сканирования линий шины затворов заключается в следующем. Когда пользователь встраивает жидкокристаллический модуль отображения в телевизионный приемник в месте назначения доставки, например, направление встраивания иногда отличается в зависимости от места назначения доставки (например, направления вверх и вниз становятся противоположными). В этом случае, когда порядки сканирования могут быть переключены в месте назначения доставки, отображение изображений, требуемое пользователем, может быть выполнено. Также предлагается телевизионный приемник, который позволяет просматривать изображение, отражаемое от зеркала. В этом случае, когда порядки сканирования могут быть переключены, пользователь может просматривать изображение в обычном состоянии, даже когда изображение на экране является изображением, отражаемым от зеркала.

Документы предшествующего уровня техники

Патентные документы

Патентный документ 1. Патент (США) № 6778626

Патентный документ 2. Публикация не прошедшей экспертизу заявки на патент (Япония) номер 2001-506044

Сущность изобретения

Задачи, которые должны быть решены изобретением

Тем не менее, согласно конфигурации, описанной в патенте (США) № 6778626, как описано выше, схемы 310, 312 и 314 для переключения между порядками сканирования необходимы в каждом каскаде сдвигового регистра. Следовательно, это приводит к увеличению площади схемы и увеличению потребления тока, а также к увеличению затрат. Дополнительно, схемы 310, 312 и 314 для переключения между порядками сканирования выполнены с возможностью переключать переключатель посредством сигнала SW выбора. Согласно этой конфигурации, транзисторы, которые составляют переключатели, поддерживаются во включенном состоянии в ходе работы устройства отображения. Следовательно, когда тонкопленочный транзистор и т.п., который использует аморфный кремний, применяется в качестве переключателей, возникает сдвиг порогового напряжения транзисторов во время высокотемпературного старения, и он иногда приводит к анормальной работе. Соответственно высокая надежность не обеспечивается.

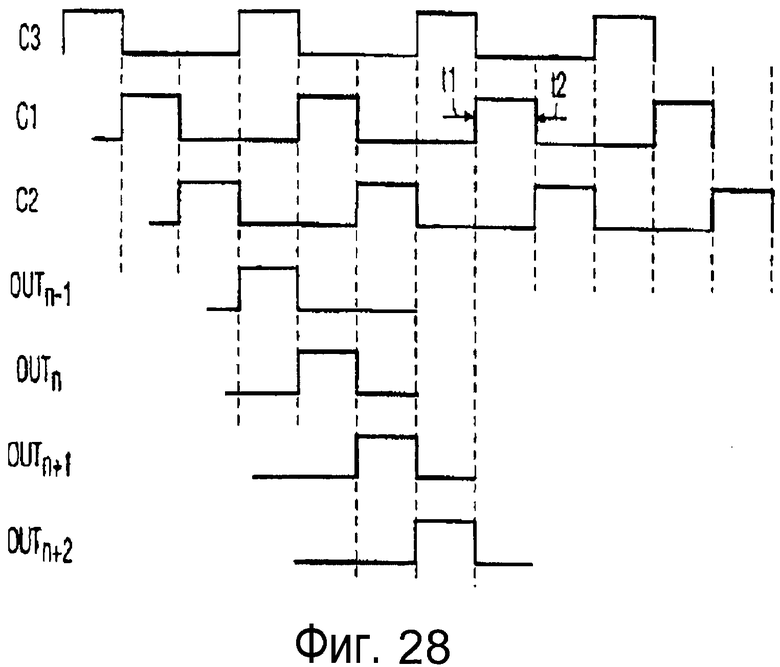

В последние годы, кроме того, постоянно увеличивается размер панели и увеличивается высокое разрешение, и становится важным предотвращать недостаток заряда для пиксельной емкости. Относительно этого аспекта, согласно сдвиговому регистру, раскрытому в публикации не прошедшей экспертизу заявки на патент (Япония) № 2001-506044, отсутствует период, в который несколько линий шины затворов одновременно выбираются (см. фиг. 28). Следовательно, во время прямого сканирования, например, невозможно выполнять предварительный заряд (предзаряд) для (k+1)-й строки в течение периода, когда заряд выполняется для k-й линии. Чтобы давать возможность выполнять предварительный заряд в этом сдвиговом регистре, сдвиговый регистр должен быть выполнен с возможностью использовать шесть или более синхросигналов.

Цель настоящего изобретения заключается в том, чтобы реализовывать сдвиговый регистр, который может переключаться между порядками сканирования линий сигналов сканирования при подавлении увеличения площади схемы, увеличения потребления тока и недостатка заряда для пиксельной емкости.

Средство для решения задач

Первый аспект настоящего изобретения направлен на сдвиговый регистр, содержащий множество бистабильных схем, каждая из которых имеет первое состояние и второе состояние и соединенных последовательно друг с другом, при этом множество бистабильных схем последовательно переходит в первое состояние на основе, по меньшей мере, четырехфазных синхросигналов, включающих в себя двухфазные синхросигналы, которые предоставляются в качестве первого синхросигнала и второго синхросигнала в бистабильные схемы каскада нечетного порядка из множества бистабильных схем, и двухфазные синхросигналы, которые предоставляются в качестве первого синхросигнала и второго синхросигнала в бистабильные схемы каскада четного порядка из множества бистабильных схем, при этом:

- каждая бистабильная схема включает в себя:

- выходной узел, который выводит сигнал состояния, указывающий любое из первого состояния и второго состояния;

- элемент переключения управления выводом, в котором первый синхросигнал предоставляется во второй электрод и третий электрод подключается к выходному узлу;

- первый модуль заряда первого узла для заряда первого узла, подключенного к первому электроду элемента переключения управления выводом, на основе сигнала состояния, выводимого из бистабильной схемы из предыдущего каскада каждой соответствующей бистабильной схемы;

- второй модуль заряда первого узла для заряда первого узла на основе сигнала состояния, выводимого из бистабильной схемы следующего каскада каждой соответствующей бистабильной схемы;

- первый модуль разряда первого узла для разряда первого узла на основе сигнала состояния, выводимого из бистабильной схемы третьего каскада после каждой соответствующей бистабильной схемы, и

- второй модуль разряда первого узла для разряда первого узла на основе сигнала состояния, выводимого из бистабильной схемы третьего каскада перед каждой соответствующей бистабильной схемой.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- фаза первого синхросигнала и фаза второго синхросигнала сдвигаются на 180 градусов друг от друга.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- фаза двухфазных синхросигналов, предоставляемых в бистабильные схемы каскада нечетного порядка, и фаза двухфазных синхросигналов, предоставляемых в бистабильные схемы каскада четного порядка, сдвигаются на 90 градусов друг от друга.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- тактирование, в которое первый синхросигнал изменяется от высокого уровня к низкому уровню, является идентичным тактированию, в которое второй синхросигнал изменяется от низкого уровня к высокому уровню, а также тактирование, в которое первый синхросигнал изменяется от низкого уровня к высокому уровню, является идентичным тактированию, в которое второй синхросигнал изменяется от высокого уровня к низкому уровню.

Согласно пятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- рабочая нагрузка каждого из четырехфазных синхросигналов составляет 50%.

Согласно шестому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- в каждой бистабильной схеме

- первый модуль заряда первого узла включает в себя первый переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы из предыдущего каскада каждой соответствующей бистабильной схемы, предоставляется в первый электрод и второй электрод, и третий электрод подключается к первому узлу,

- второй модуль заряда первого узла включает в себя второй переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы следующего каскада каждой соответствующей бистабильной схемы, предоставляется в первый электрод и второй электрод, и третий электрод подключается к первому узлу,

- первый модуль разряда первого узла включает в себя третий переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы третьего каскада после каждой соответствующей бистабильной схемы, предоставляется в первый электрод, второй электрод подключается к первому узлу, и потенциал низкого уровня предоставляется в третий электрод, и

- второй модуль разряда первого узла включает в себя четвертый переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы третьего каскада перед каждой соответствующей бистабильной схемой, предоставляется в первый электрод, второй электрод подключается к первому узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- каждая бистабильная схема дополнительно включает в себя:

- пятый переключающий элемент, в котором второй электрод подключается к первому узлу, и потенциал низкого уровня предоставляется в третий электрод; и

- модуль управления второго узла, который управляет потенциалом второго узла, подключенного к первому электроду пятого переключающего элемента, на основе второго синхросигнала и потенциала первого узла.

Согласно восьмому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения

- модуль управления второго узла включает в себя:

- шестой переключающий элемент, в котором второй синхросигнал предоставляется в первый электрод и второй электрод, и третий электрод подключается ко второму узлу; и

- седьмой переключающий элемент, в котором первый электрод подключается к первому узлу, второй электрод подключается ко второму узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно девятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- бистабильные схемы каскада нечетного порядка принимают двухфазные синхросигналы, которые предоставляются в бистабильные схемы каскада четного порядка, в качестве третьего синхросигнала и четвертого синхросигнала соответственно,

- бистабильные схемы каскада четного порядка принимают двухфазные синхросигналы, которые предоставляются в бистабильные схемы каскада нечетного порядка, в качестве третьего синхросигнала и четвертого синхросигнала соответственно и

- каждая бистабильная схема дополнительно включает в себя:

- восьмой переключающий элемент, в котором второй электрод подключается к первому узлу, и потенциал низкого уровня предоставляется в третий электрод;

- модуль управления третьего узла, который управляет потенциалом третьего узла, подключенного к первому электроду восьмого переключающего элемента, на основе третьего синхросигнала и потенциала первого узла;

- одиннадцатый переключающий элемент, в котором второй электрод подключается к первому узлу, и потенциал низкого уровня предоставляется в третий электрод; и

- модуль управления четвертого узла, который управляет потенциалом четвертого узла, подключенного к первому электроду одиннадцатого переключающего элемента, на основе четвертого синхросигнала и потенциала первого узла.

Согласно десятому аспекту настоящего изобретения, в девятом аспекте настоящего изобретения

- модуль управления третьего узла включает в себя:

- девятый переключающий элемент, в котором третий синхросигнал предоставляется в первый электрод и второй электрод, и третий электрод подключается к третьему узлу, и

- десятый переключающий элемент, в котором первый электрод подключается к первому узлу, второй электрод подключается к третьему узлу, и потенциал низкого уровня предоставляется в третий электрод, и

- модуль управления четвертого узла включает в себя:

- двенадцатый переключающий элемент, в котором четвертый синхросигнал предоставляется в первый электрод и второй электрод, и третий электрод подключается к четвертому узлу, и

- тринадцатый переключающий элемент, в котором первый электрод подключается к первому узлу, второй электрод подключается к четвертому узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно одиннадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- три сигнала управления на стороне первого каскада для разряда первого узла, включенного в каждую из бистабильных схем первого каскада, второго каскада и третьего каскада из множества бистабильных схем, посредством второго модуля разряда первого узла соответственно предоставляются снаружи, и

- три сигнала управления на стороне последнего каскада для разряда первого узла, включенного в каждую из бистабильных схем последнего каскада, каскада перед последним каскадом и второго каскада перед последним каскадом из множества бистабильных схем, посредством первого модуля разряда первого узла соответственно предоставляются снаружи.

Согласно двенадцатому аспекту настоящего изобретения, в одиннадцатом аспекте настоящего изобретения

- два сигнала управления на стороне первого каскада из трех сигналов управления на стороне первого каскада реализуются посредством одного сигнала, и

- два сигнала управления на стороне последнего каскада из трех сигналов управления на стороне последнего каскада реализуются посредством одного сигнала.

Согласно тринадцатому аспекту настоящего изобретения, в двенадцатом аспекте настоящего изобретения

- в каждой из бистабильных схем первого каскада, второго каскада и третьего каскада из множества бистабильных схем изменение первого синхросигнала от низкого уровня к высокому уровню подавляется в течение периода до тех пор, пока первый узел не разряжается посредством второго модуля разряда первого узла после того, как первый узел заряжается посредством второго модуля заряда первого узла, и

- в каждой из бистабильных схем последнего каскада, каскада перед последним каскадом и второго каскада перед последним каскадом из множества бистабильных схем изменение первого синхросигнала от низкого уровня к высокому уровню подавляется в течение периода до тех пор, пока первый узел не разряжается посредством первого модуля разряда первого узла после того, как первый узел заряжается посредством первого модуля заряда первого узла.

Согласно четырнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- любая из бистабильных схем первого каскада, второго каскада и третьего каскада из множества бистабильных схем включает в себя пятнадцатый переключающий элемент, в котором сигнал управления на стороне первого каскада предоставляется в первый электрод, второй электрод подключается к выходному узлу, и потенциал низкого уровня предоставляется в третий электрод, и

- любая из бистабильных схем последнего каскада, каскада перед последним каскадом и второго каскада перед последним каскадом из множества бистабильных схем включает в себя шестнадцатый переключающий элемент, в котором сигнал управления на стороне последнего каскада предоставляется в первый электрод, второй электрод подключается к выходному узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно пятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- каждая бистабильная схема дополнительно включает в себя четырнадцатый переключающий элемент, в котором второй синхросигнал предоставляется в первый электрод, второй электрод подключается к выходному узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно шестнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- каждая бистабильная схема дополнительно включает в себя конденсатор, в котором один конец подключается к первому узлу, а другой конец подключается к выходному узлу.

Согласно семнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- каждая бистабильная схема дополнительно включает в себя семнадцатый переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы второго каскада или третьего каскада после каждой соответствующей бистабильной схемы, предоставляется в первый электрод, второй электрод подключается к выходному узлу, и потенциал низкого уровня предоставляется в третий электрод, и восемнадцатый переключающий элемент, в котором сигнал состояния, выводимый из бистабильной схемы второго каскада или третьего каскада перед каждой соответствующей бистабильной схемой, предоставляется в первый электрод, второй электрод подключается к выходному узлу, и потенциал низкого уровня предоставляется в третий электрод.

Согласно восемнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- сдвиговый регистр формируется за счет использования аморфного кремния.

Согласно девятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- сдвиговый регистр формируется за счет использования микрокристаллического кремния.

Согласно двадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- сдвиговый регистр формируется посредством использования поликристаллического кремния.

Согласно двадцать первому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

- сдвиговый регистр формируется посредством использования оксидного полупроводника.

Двадцать второй аспект настоящего изобретения направлен на возбуждающую схему линии сигналов сканирования устройства отображения для возбуждения множества линий сигналов сканирования, которые предоставляются в модуле отображения, содержащую:

- сдвиговый регистр, согласно первому аспекту настоящего изобретения, в котором:

- множество бистабильных схем предоставляются так, что они имеют соответствие "один-к-одному" с множеством линий сигналов сканирования, и

- каждая бистабильная схема предоставляет сигнал состояния, выводимый из выходного узла, в линию сигналов сканирования, соответствующую каждой соответствующей бистабильной схеме, в качестве сигнала сканирования.

Двадцать третий аспект настоящего изобретения направлен на устройство отображения, содержащее возбуждающую схему линии сигналов сканирования согласно двадцать второму аспекту настоящего изобретения, включающую в себя модуль отображения.

Согласно двадцать четвертому аспекту настоящего изобретения, в двадцать третьем аспекте настоящего изобретения

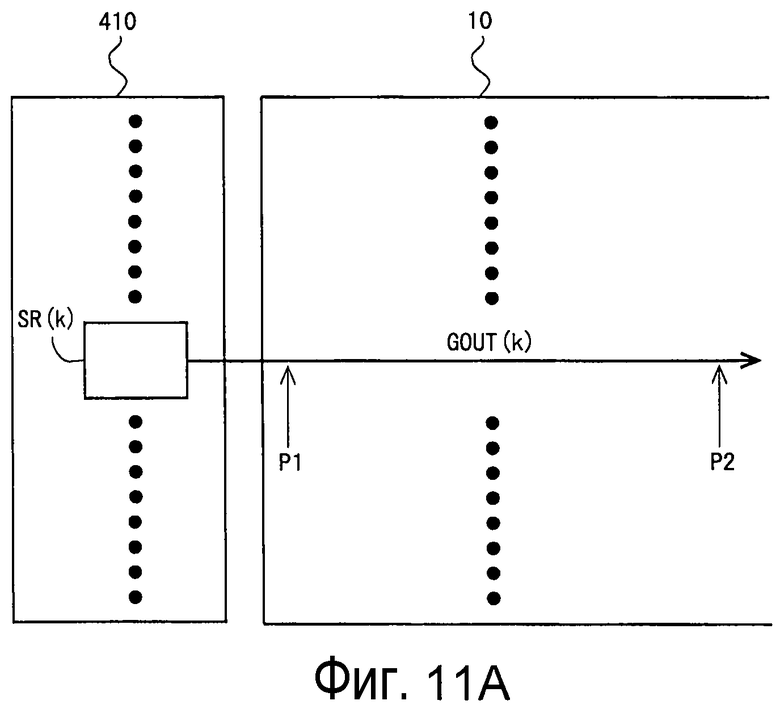

- сдвиговый регистр, включающий в себя множество бистабильных схем, предоставляется как на одной стороне, так и на другой стороне модуля отображения, соответственно.

Согласно двадцать пятому аспекту настоящего изобретения, в двадцать третьем аспекте настоящего изобретения

- бистабильные схемы каскада нечетного порядка предоставляются на одной стороне модуля отображения, а бистабильные схемы каскада четного порядка предоставляются на другой стороне модуля отображения.

Преимущества изобретения

Согласно первому аспекту настоящего изобретения, в каждый каскад (бистабильную схему) сдвигового регистра сигнал состояния, выводимый из предыдущего каскада, и сигнал состояния, выводимый из следующего каскада, предоставляются в качестве сигналов для того, чтобы заряжать первый узел, подключенный к первому электроду (типично электроду затвора) элемента переключения управления выводом для управления потенциалом (потенциалом сигнала состояния, выводимого из каждого каскада) выходного узла, и сигнал состояния, выводимый из третьего каскада перед соответствующим каскадом, и сигнал состояния, выводимый из третьего каскада после соответствующего каскада, предоставляются в качестве сигналов для того, чтобы разряжать первый узел. Т.е. сигнал состояния, выводимый из каждого каскада сдвигового регистра, имеет функцию, чтобы заряжать первые узлы предыдущего каскада и следующего каскада, а также имеет функцию, чтобы разряжать первые узлы третьего каскада до и третьего каскада после соответствующего каскада. Дополнительно, первый синхросигнал, который циклически повторяет потенциал высокого уровня и потенциал низкого уровня, предоставляется во второй электрод (типично электрод стока) элемента переключения управления выводом. Следовательно, когда первый узел заряжается в первом каскаде сдвигового регистра вначале, сигнал состояния, выводимый из каждого каскада сдвигового регистра, переходит в первое состояние в порядке прямого направления (в порядке "от первого каскада к последнему каскаду"). С другой стороны, когда первый узел заряжается в последнем каскаде сдвигового регистра вначале, сигнал состояния, выводимый из каждого каскада сдвигового регистра, переходит в первое состояние в порядке обратного направления (в порядке "от последнего каскада к первому каскаду"). Таким образом, сдвиговый регистр, допускающий переключение направлений сдвига, может быть реализован без включения конфигураций ("конфигурации для переключения переключателя посредством сигнала выбора", "возбуждающей схемы и сигнального межсоединения для сигнала выбора"), которые традиционно необходимы для того, чтобы изменять направление сдвига. Следовательно, когда устройство отображения имеет конфигурацию, допускающую переключение между порядками сканирования линий сигналов сканирования, например, увеличение площади схемы, увеличение потребления тока и увеличение затрат могут подавляться. Дополнительно, поскольку переключатель для переключения порядков сканирования (направлений сдвига) становится необязательным, возникновение ошибочной операции, обусловленной сдвигом порогового напряжения переключателя (транзистора) во время высокотемпературного старения, подавляется.

Согласно второму аспекту настоящего изобретения, получается преимущество, аналогичное преимуществу первого аспекта.

Согласно третьему аспекту настоящего изобретения, фазы двухфазных синхросигналов, которые предоставляются в каскады нечетного порядка, и двухфазных синхросигналов, которые предоставляются в каскады четного порядка, сдвигаются на 90 градусов друг от друга. Следовательно, время заряда для пиксельной емкости униформизируется, и возникновение сбоя в работе дисплея, обусловленного разностью заряда, подавляется.

Согласно четвертому аспекту настоящего изобретения, поскольку тактирование изменения первого синхросигнала и тактирование изменения второго синхросигнала становится идентичным, уменьшается шум сигнала состояния, выводимого из бистабильной схемы. Дополнительно, поскольку время заряда для пиксельной емкости становится длительным, возникновение сбоя в работе дисплея, обусловленного недостатком заряда, эффективно подавляется.

Согласно пятому аспекту настоящего изобретения, рабочая нагрузка каждого синхросигнала составляет 50%. Следовательно, можно предоставлять период, когда несколько линий сигналов сканирования одновременно выбираются. В этом случае предварительный заряд (предзаряд) выполняется для пиксельной емкости в течение первого полупериода из периода, когда каждая линия сигналов сканирования выбирается, и основной заряд выполняется для пиксельной емкости в течение второго полупериода. Следовательно, достаточное время заряда обеспечивается, и понижение качества отображения, обусловленное недостатком заряда для пиксельной емкости, подавляется.

Согласно шестому аспекту настоящего изобретения, преимущество, аналогичное преимуществу первого аспекта настоящего изобретения, получается в конфигурации, в которой переключающие элементы включаются в первый модуль заряда первого узла, второй модуль заряда первого узла, первый модуль разряда первого узла и второй модуль разряда первого узла.

Согласно седьмому аспекту настоящего изобретения, в течение периода, когда потенциал первого узла имеет низкий уровень, потенциал второго узла для управления потенциалом первого узла может задаваться равным высокому уровню в каждый предварительно определенный период. Следовательно, в течение периода, когда потенциал первого узла имеет низкий уровень, пятый переключающий элемент переходит во включенное состояние в каждый предварительно определенный период, и потенциал первого узла извлекается до более низкого потенциала. Следовательно, даже когда сдвиг порогового напряжения элемента переключения управления выводом возникает вследствие высокотемпературного старения, а также когда ток утечки в переключающем элементе становится большим, например, потенциал первого узла может быть надежно задан равным низкому уровню в каждый предварительно определенный период, и вывод анормального импульса из выходного узла может подавляться.

Согласно восьмому аспекту настоящего изобретения, преимущество, аналогичное преимуществу седьмого аспекта настоящего изобретения, получается в конфигурации, в которой переключающий элемент включается в модуль управления второго узла.

Согласно девятому аспекту настоящего изобретения, в течение периода, когда потенциал первого узла имеет низкий уровень, потенциалы третьего узла и четвертого узла для управления потенциалом первого узла могут задаваться равными высокому уровню в каждый предварительно определенный период. В этом случае потенциал третьего узла и потенциал четвертого узла управляются на основе различных синхросигналов. Соответственно потенциал первого узла может извлекаться до более низкого потенциала в течение большей части, например, периода, когда потенциал первого узла имеет низкий уровень. Следовательно, даже когда сдвиг порогового напряжения элемента переключения управления выводом возникает вследствие высокотемпературного старения, а также когда ток утечки в переключающем элементе становится большим, например, потенциал первого узла может задаваться равным низкому уровню, и вывод анормального импульса из выходного узла может эффективно подавляться.

Согласно десятому аспекту настоящего изобретения, преимущество, аналогичное преимуществу девятого аспекта настоящего изобретения, получается в конфигурации, в которой переключающие элементы включаются в модуль управления третьего узла и модуль управления четвертого узла.

Согласно одиннадцатому аспекту настоящего изобретения, первые узлы первого каскада, второго каскада, третьего каскада, второго каскада перед последним каскадом, каскада перед последним каскадом и последнего состояния разряжаются посредством сигнала управления, предоставляемого снаружи.

Согласно двенадцатому аспекту настоящего изобретения, когда операция сдвига выполняется в порядке прямого направления, первые узлы двух каскадов из последнего каскада, каскада перед последним каскадом и второго каскада перед последним каскадом разряжаются на основе идентичного сигнала. Когда операция сдвига выполняется в порядке обратного направления, первые узлы двух каскадов из первого каскада, второго каскада и третьего каскада разряжаются на основе идентичного сигнала. Следовательно, сигнальные межсоединения, которые необходимы для того, чтобы разряжать первые узлы, снижаются, и преимущество уменьшения площади схемы, уменьшения потребления тока и снижения затрат достигается в большей степени.

Согласно тринадцатому аспекту настоящего изобретения, необязательное увеличение потенциалов первых узлов подавляется, и понижение качества отображения подавляется в первом каскаде, втором каскаде, третьем каскаде, втором каскаде перед последним каскадом, каскаде перед последним каскадом и последнем каскаде.

Согласно четырнадцатому аспекту настоящего изобретения, потенциалы сигнала состояния могут задаваться равными низкому уровню на основе сигнала управления, предоставляемого снаружи, в первом каскаде, втором каскаде, третьем каскаде, втором каскаде перед последним каскадом, каскаде перед последним каскадом и последнем каскаде.

Согласно пятнадцатому аспекту настоящего изобретения, даже когда утечка наружу возникает в элементе переключения управления выводом, поскольку потенциал выходного узла переходит к низкому уровню на основе второго синхросигнала, вывод анормального импульса из выходного узла может эффективно подавляться.

Согласно шестнадцатому аспекту настоящего изобретения, когда потенциал выходного узла увеличивается, потенциал первого узла увеличивается через конденсатор (первый узел использует компенсационную обратную связь). Следовательно, в течение периода, когда бистабильная схема должна поддерживаться в первом состоянии, уменьшение потенциала первого узла подавляется, и большое напряжение предоставляется в первый электрод элемента переключения управления выводом. Соответственно форма сигнала состояния, выводимого из выходного узла, стабилизируется.

Согласно семнадцатому аспекту настоящего изобретения, когда операция сдвига выполняется в порядке прямого направления, потенциал выходного узла задается равным низкому уровню на основе сигнала состояния, выводимого из второго каскада после каждого каскада или из третьего каскада после каждого каскада, а когда операция сдвига выполняется в порядке обратного направления, потенциал выходного узла задается равным низкому уровню на основе сигнала состояния, выводимого из второго каскада перед каждым каскадом или из третьего каскада перед каждым каскадом. Соответственно потенциал сигнала состояния может более надежно снижаться до низкого уровня.

Согласно восемнадцатому аспекту настоящего изобретения, преимущество, аналогичное преимуществу первого аспекта настоящего изобретения, получается в сдвиговом регистре, сформированном за счет использования аморфного кремния.

Согласно девятнадцатому аспекту настоящего изобретения, преимущество, аналогичное преимуществу первого аспекта настоящего изобретения, получается в сдвиговом регистре, сформированном за счет использования микрокристаллического кремния.

Согласно двадцатому аспекту настоящего изобретения, преимущество, аналогичное преимуществу первого аспекта настоящего изобретения, получается в сдвиговом регистре, сформированном посредством использования поликристаллического кремния.

Согласно двадцать первому аспекту настоящего изобретения, преимущество, аналогичное преимуществу первого аспекта настоящего изобретения, получается в сдвиговом регистре, сформированном посредством использования оксидного полупроводника.

Согласно двадцать второму аспекту настоящего изобретения, реализуется возбуждающая схема линии сигналов сканирования, включающая в себя сдвиговый регистр, допускающий получение преимущества, аналогичного преимуществу первого аспекта настоящего изобретения.

Согласно двадцать третьему аспекту настоящего изобретения, реализуется устройство отображения, включающее в себя возбуждающую схему линии сигналов сканирования, допускающую получение преимущества, аналогичного преимуществу двадцать второго аспекта настоящего изобретения.

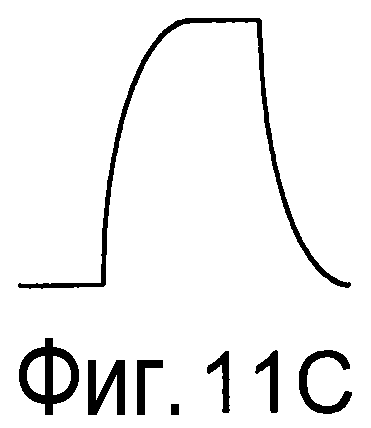

Согласно двадцать четвертому аспекту настоящего изобретения, заряд выполняется для одной линии сигналов сканирования с обеих сторон модуля отображения. Следовательно, понижение качества отображения, обусловленное недостатком заряда, подавляется.

Согласно двадцать пятому аспекту настоящего изобретения, размер в расчете на один каскад сдвигового регистра может задаваться равным фактически половине размера по сравнению с размером в конфигурации, в которой бистабильная схема, составляющая сдвиговый регистр, предоставляется только на одной стороне модуля отображения. Соответственно область, которая необходима в качестве кадрирующей рамки панели, может быть уменьшена, и уменьшение размеров различных изделий может быть реализовано.

Краткое описание чертежей

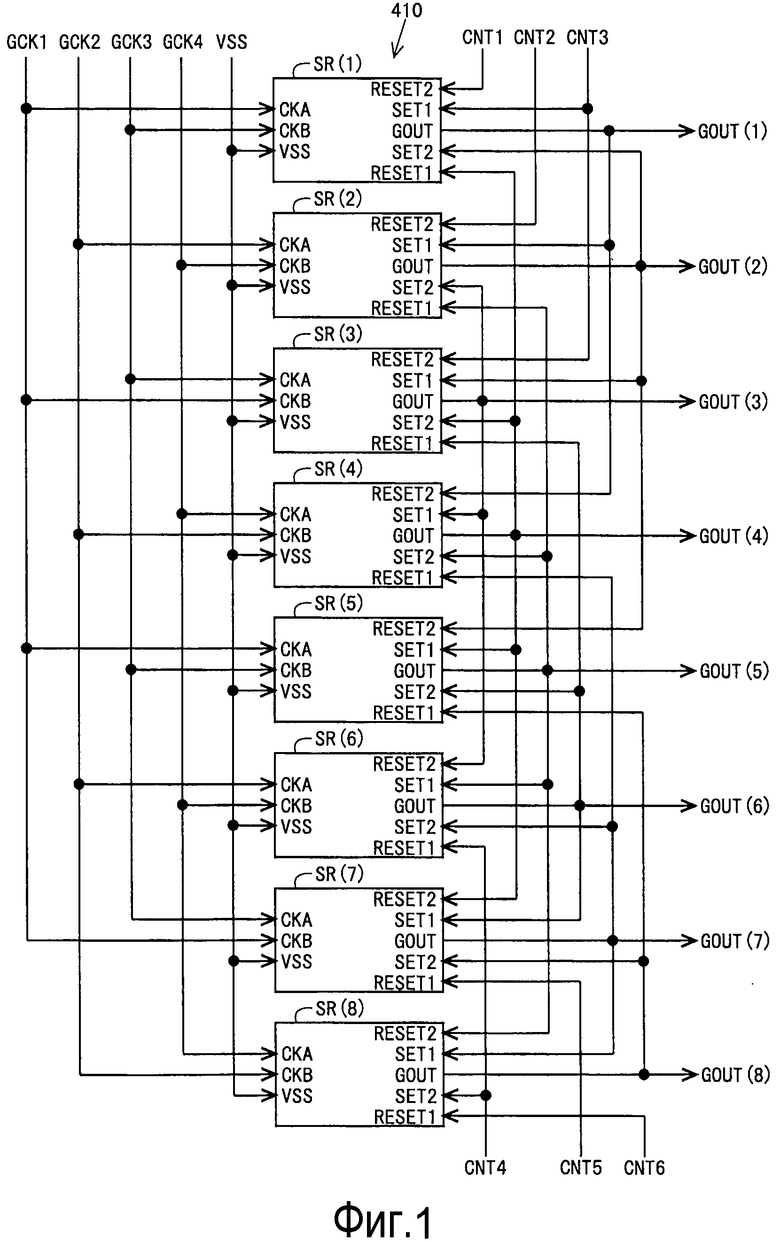

Фиг. 1 является блок-схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затворами жидкокристаллического устройства отображения с активной матрицей согласно первому варианту осуществления настоящего изобретения.

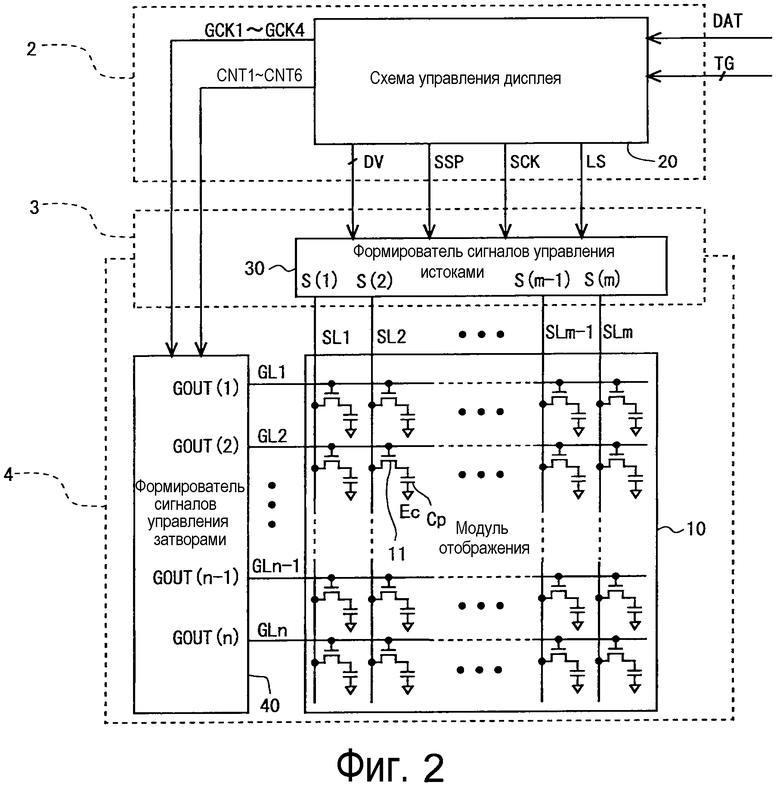

Фиг. 2 является блок-схемой, показывающей общую конфигурацию жидкокристаллического устройства отображения в первом варианте осуществления.

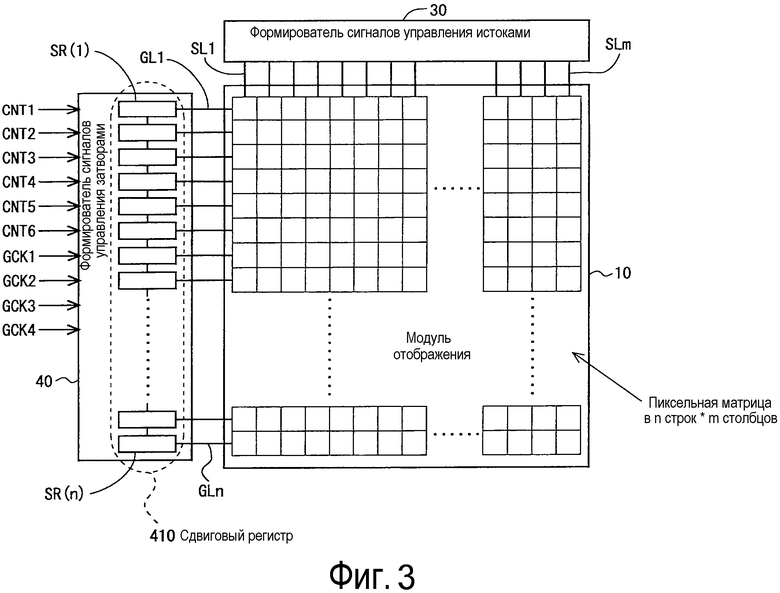

Фиг. 3 является блок-схемой для описания конфигурации формирователя сигналов управления затворами в первом варианте осуществления.

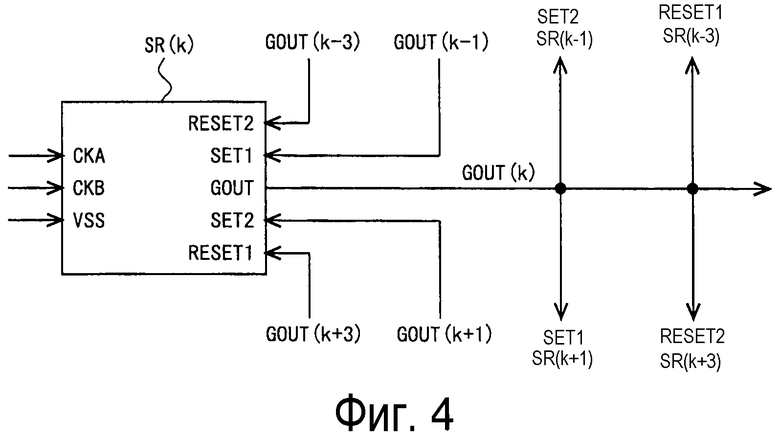

Фиг. 4 является схемой для описания входных/выходных сигналов k-й бистабильной схемы сдвигового регистра в первом варианте осуществления.

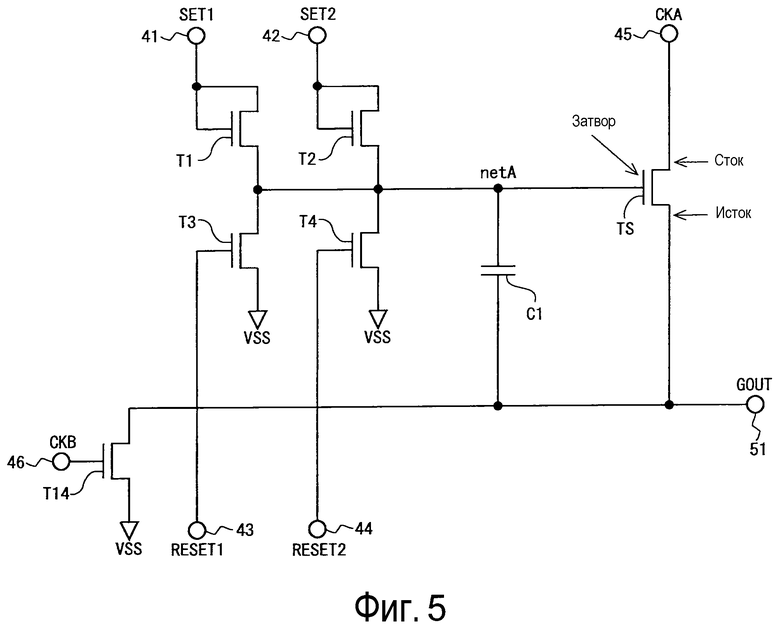

Фиг. 5 является принципиальной схемой, показывающей конфигурацию бистабильной схемы, включенной в сдвиговый регистр в первом варианте осуществления.

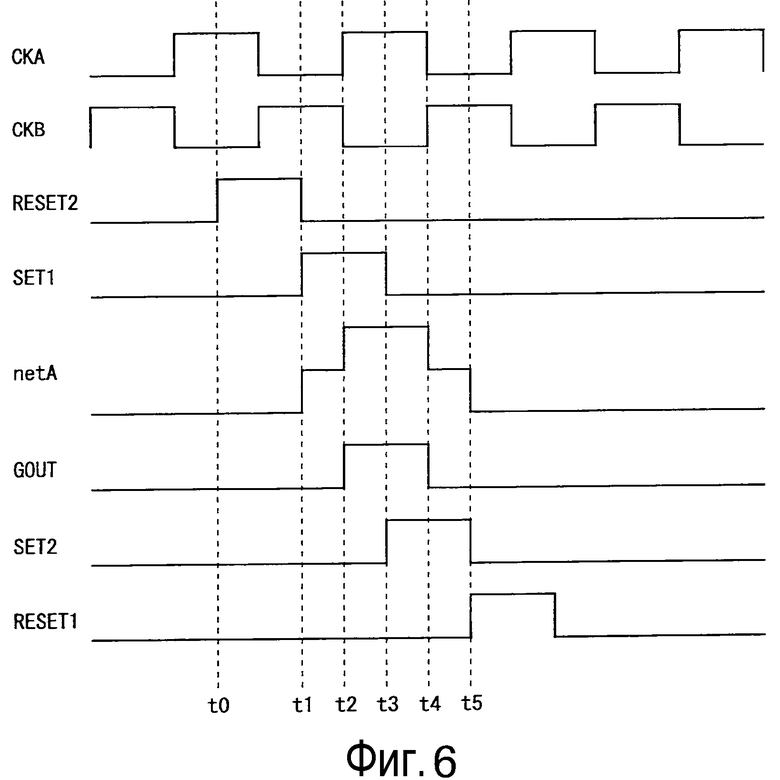

Фиг. 6 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда прямое сканирование выполняется в первом варианте осуществления.

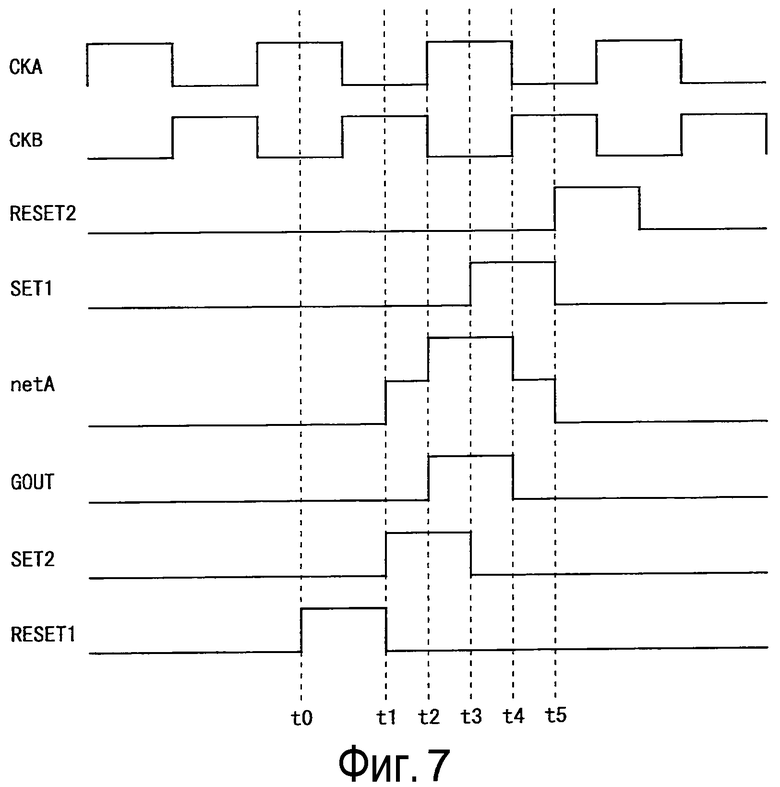

Фиг. 7 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда обратное сканирование выполняется в первом варианте осуществления.

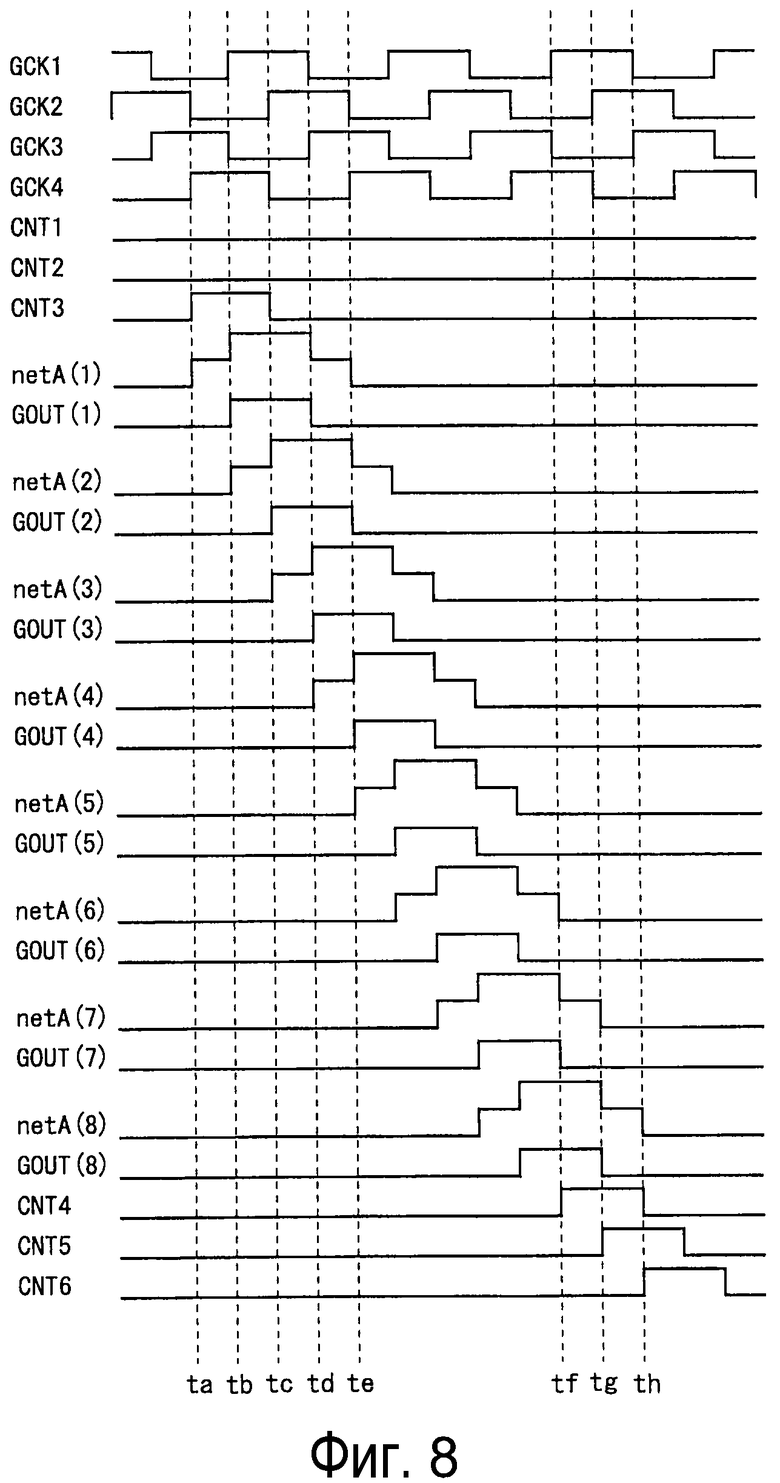

Фиг. 8 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда прямое сканирование выполняется в первом варианте осуществления.

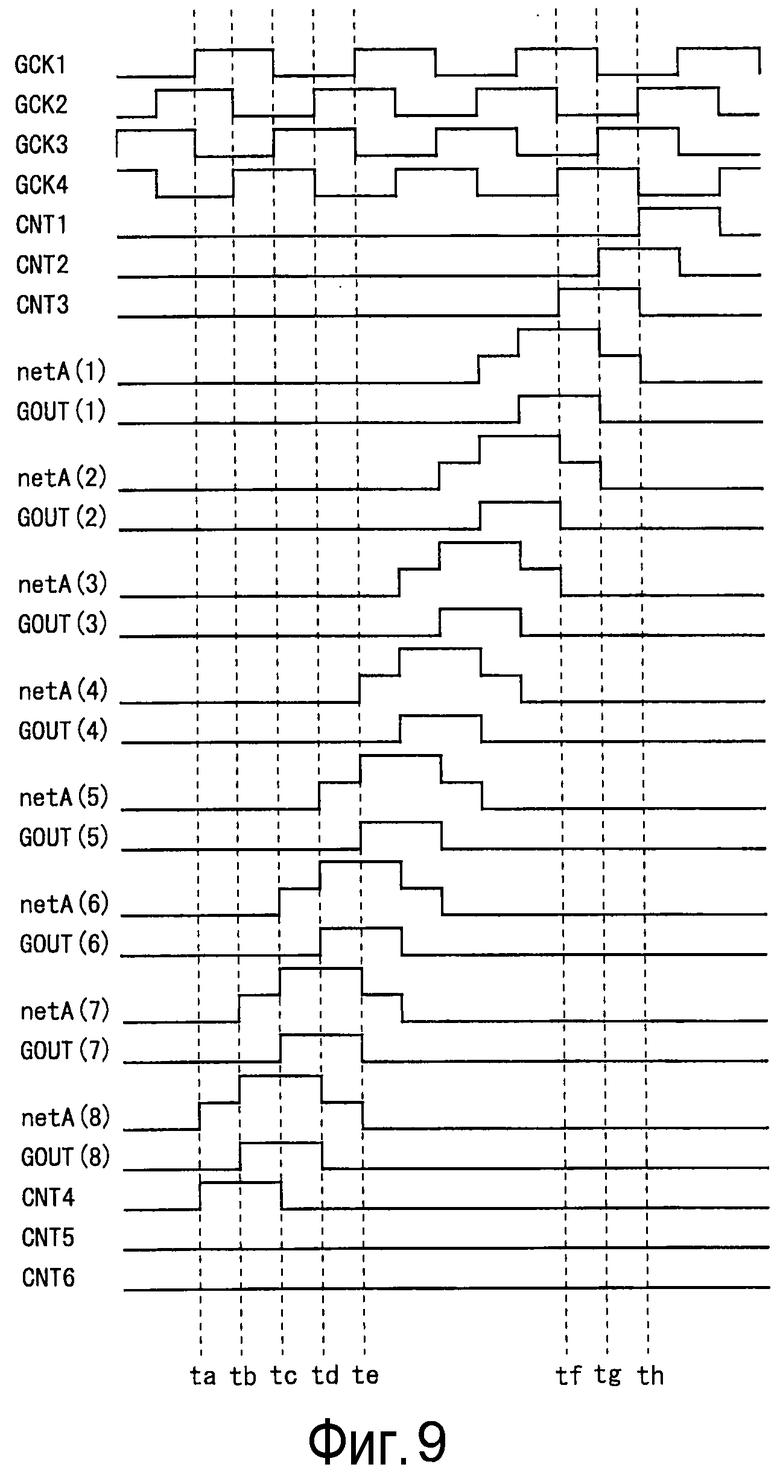

Фиг. 9 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда прямое сканирование выполняется в первом варианте осуществления.

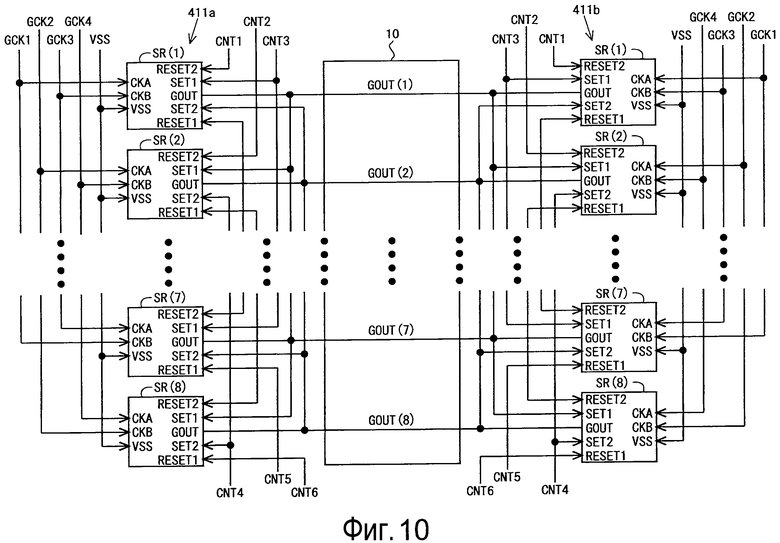

Фиг. 10 является блок-схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затворами во втором варианте осуществления настоящего изобретения.

Фиг. 11A-11C являются схемами для описания преимущества второго варианта осуществления.

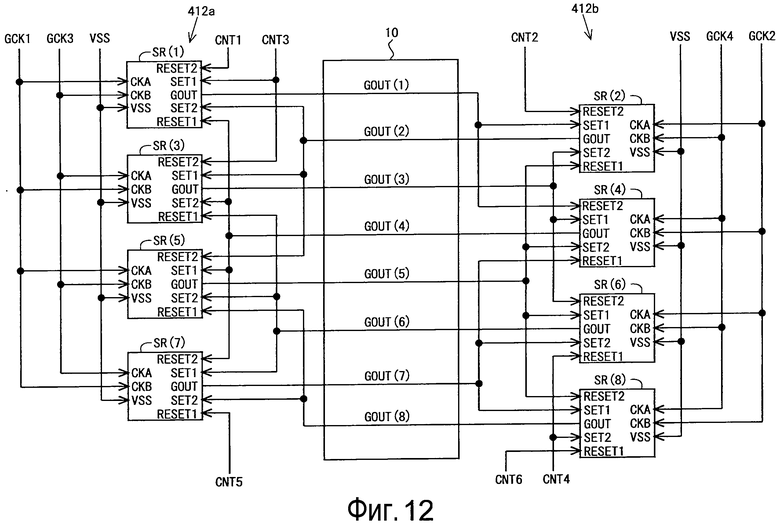

Фиг. 12 является блок-схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затворами в третьем варианте осуществления настоящего изобретения.

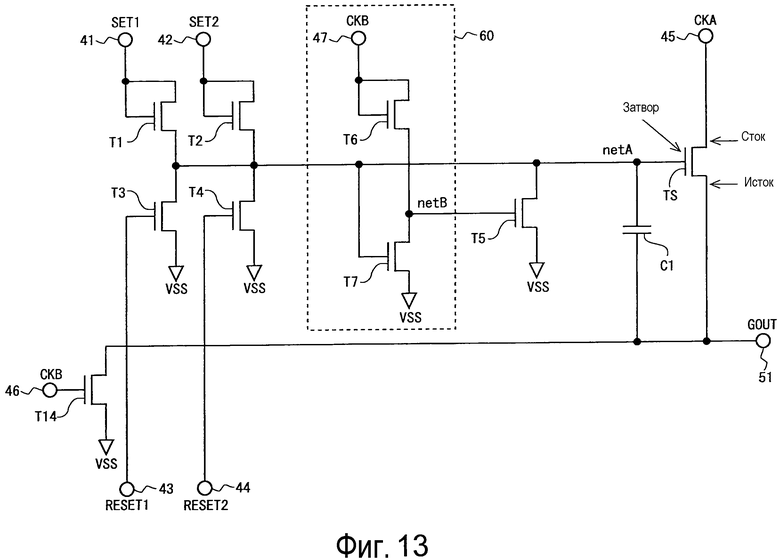

Фиг. 13 является принципиальной схемой, показывающей конфигурацию бистабильной схемы, включенной в сдвиговый регистр в четвертом варианте осуществления настоящего изобретения.

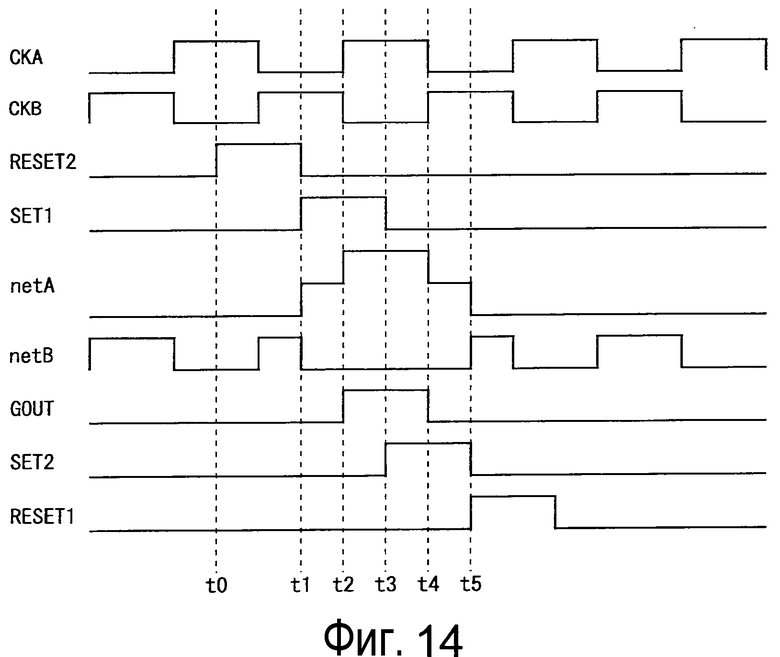

Фиг. 14 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда прямое сканирование выполняется в четвертом варианте осуществления.

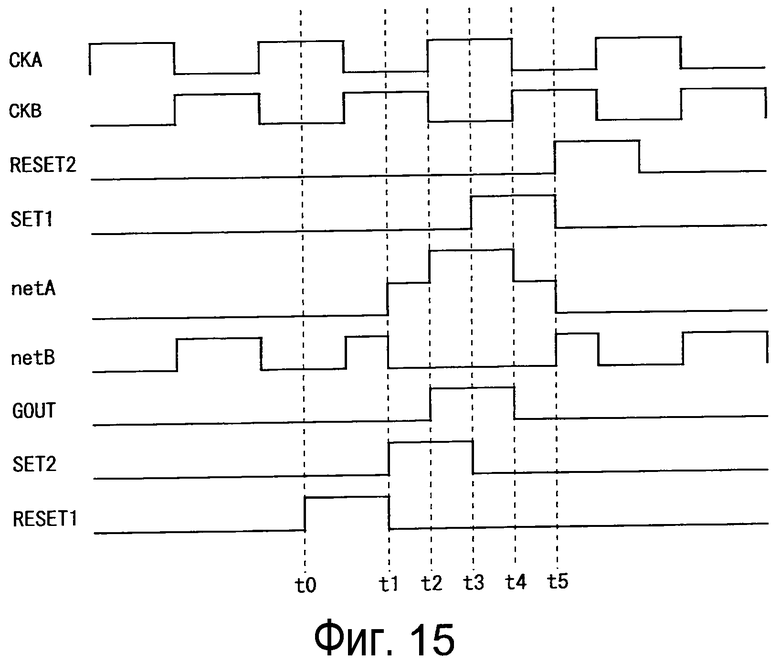

Фиг. 15 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда обратное сканирование выполняется в четвертом варианте осуществления.

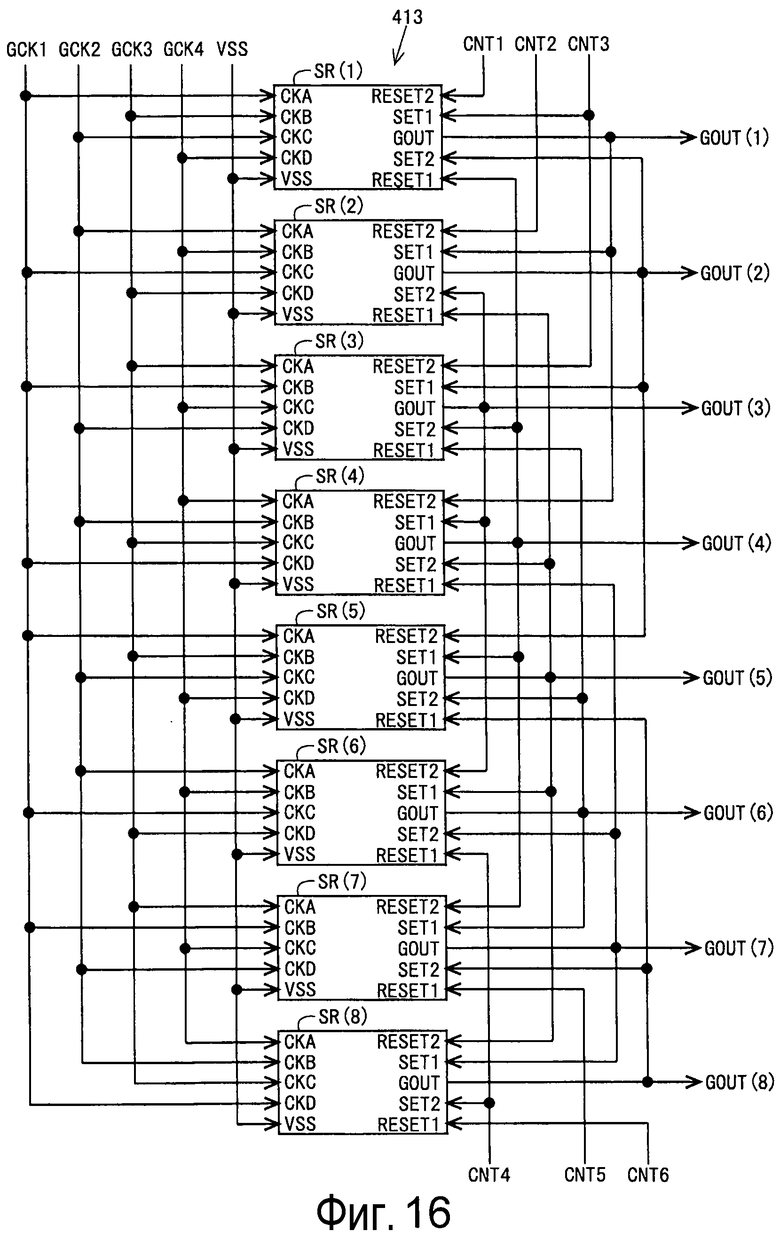

Фиг. 16 является блок-схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затворами в пятом варианте осуществления настоящего изобретения.

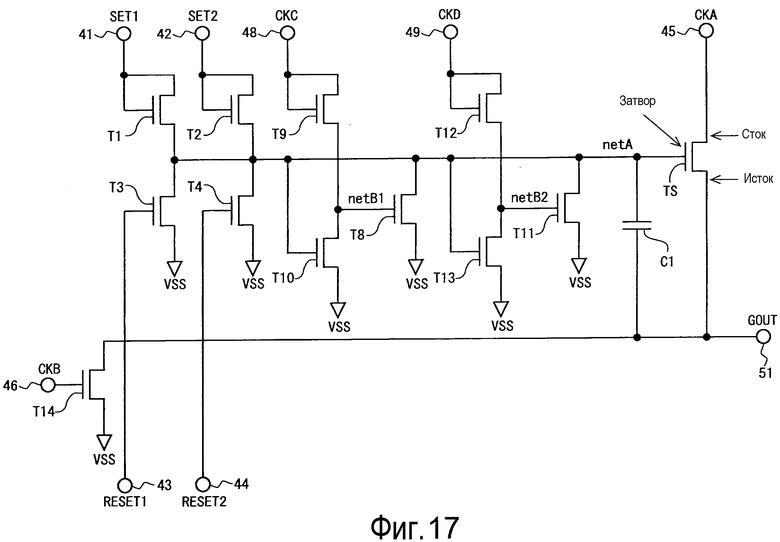

Фиг. 17 является принципиальной схемой, показывающей конфигурацию бистабильной схемы, включенной в сдвиговый регистр в пятом варианте осуществления.

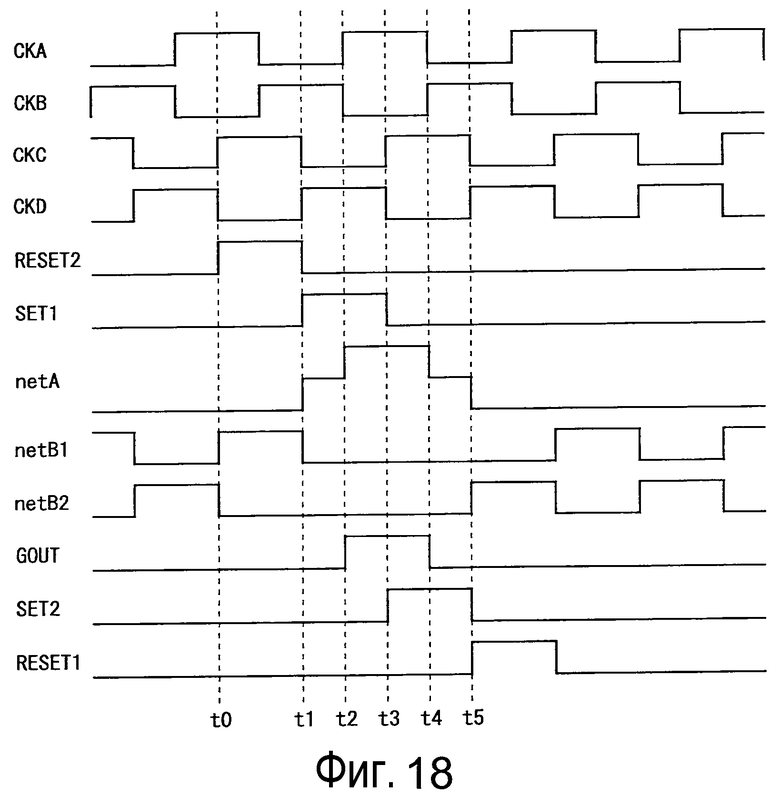

Фиг. 18 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда прямое сканирование выполняется в пятом варианте осуществления.

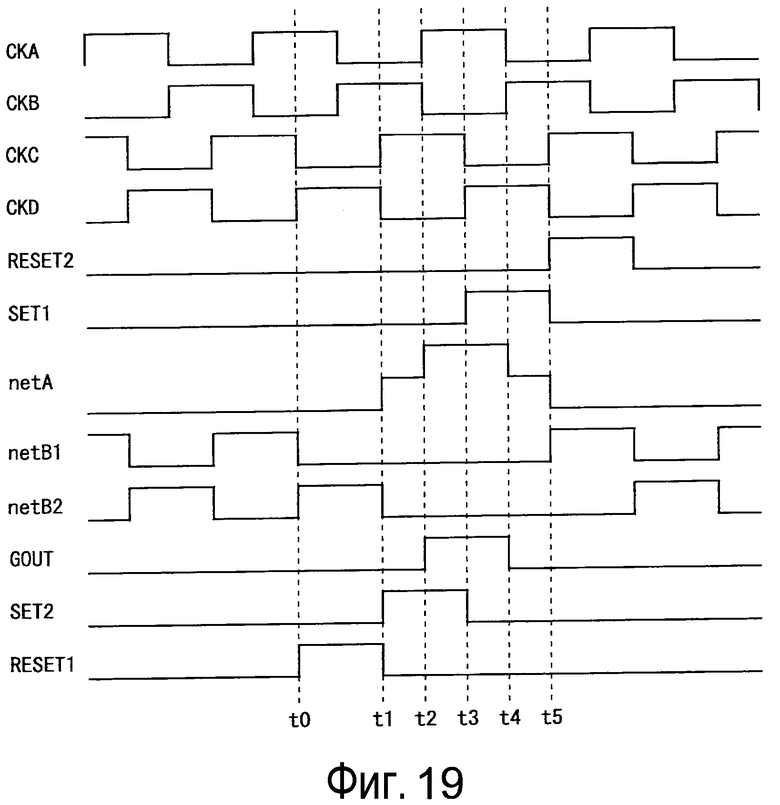

Фиг. 19 является временной диаграммой для описания работы каждого каскада сдвигового регистра, когда обратное сканирование выполняется в пятом варианте осуществления.

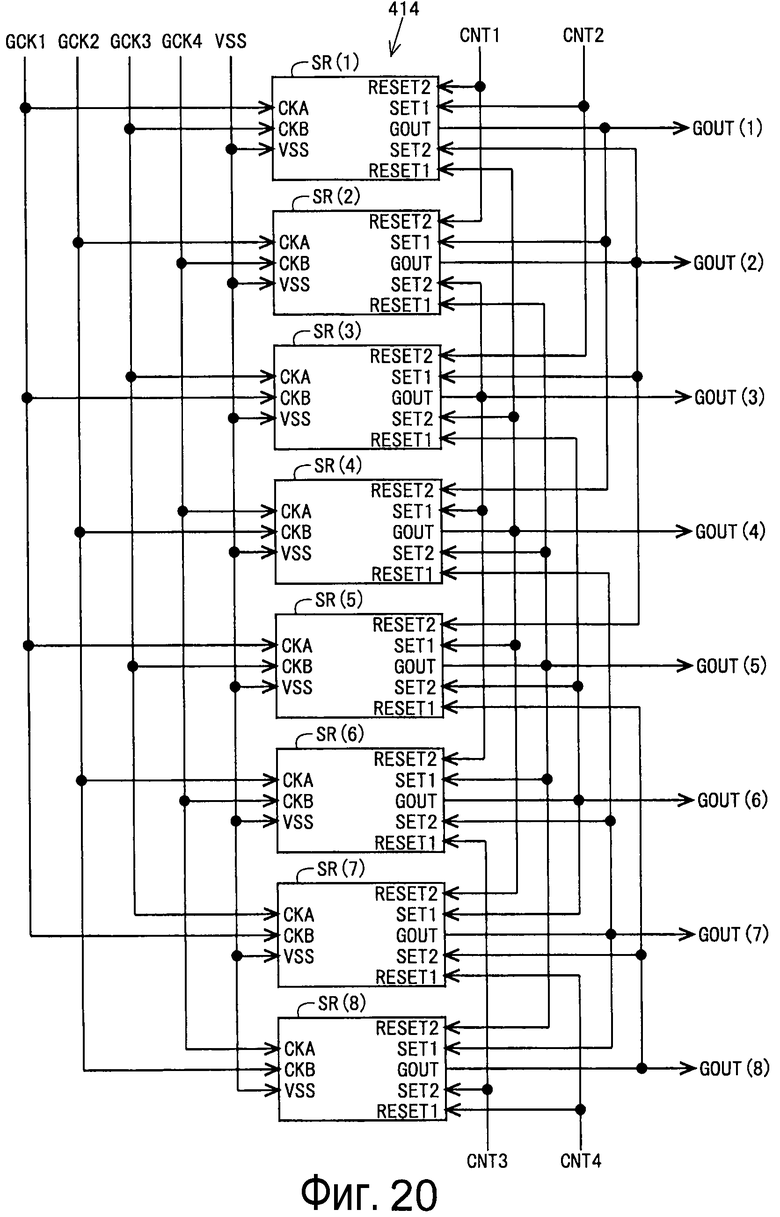

Фиг. 20 является блок-схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затворами в шестом варианте осуществления настоящего изобретения.

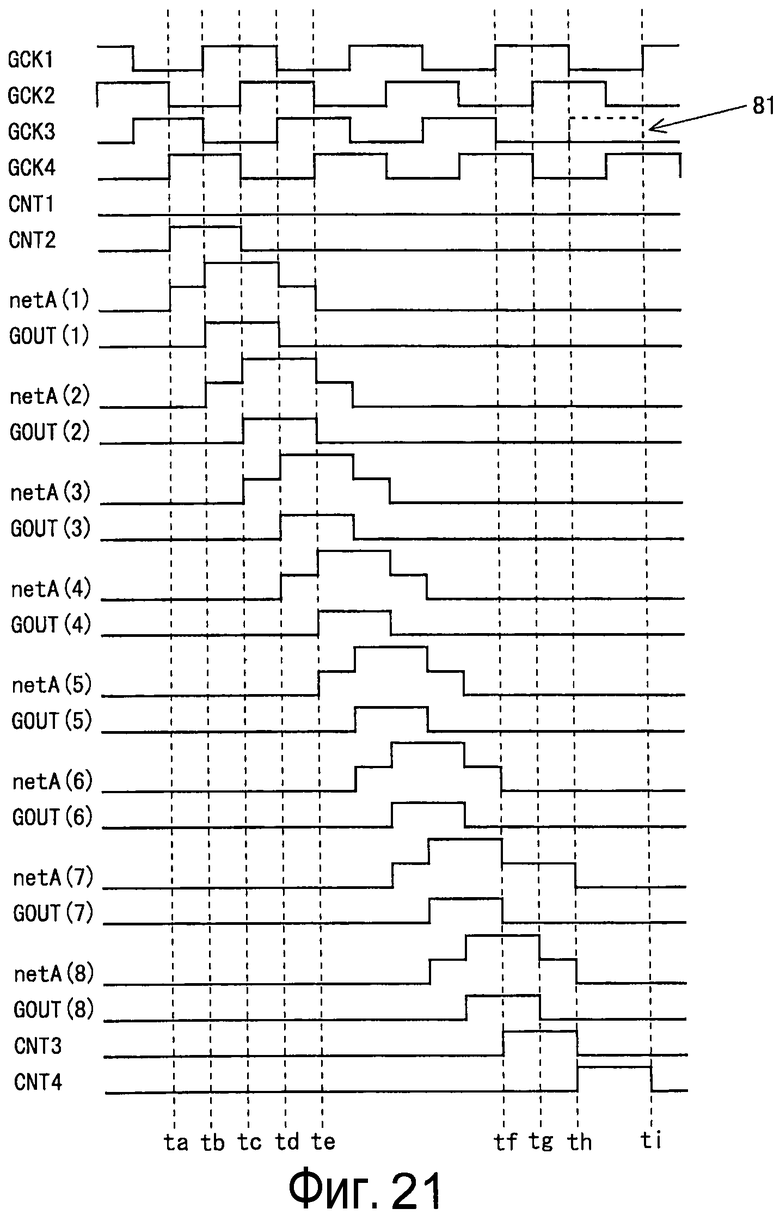

Фиг. 21 является временной диаграммой для описания общей работы сдвигового регистра, когда прямое сканирование выполняется в шестом варианте осуществления.

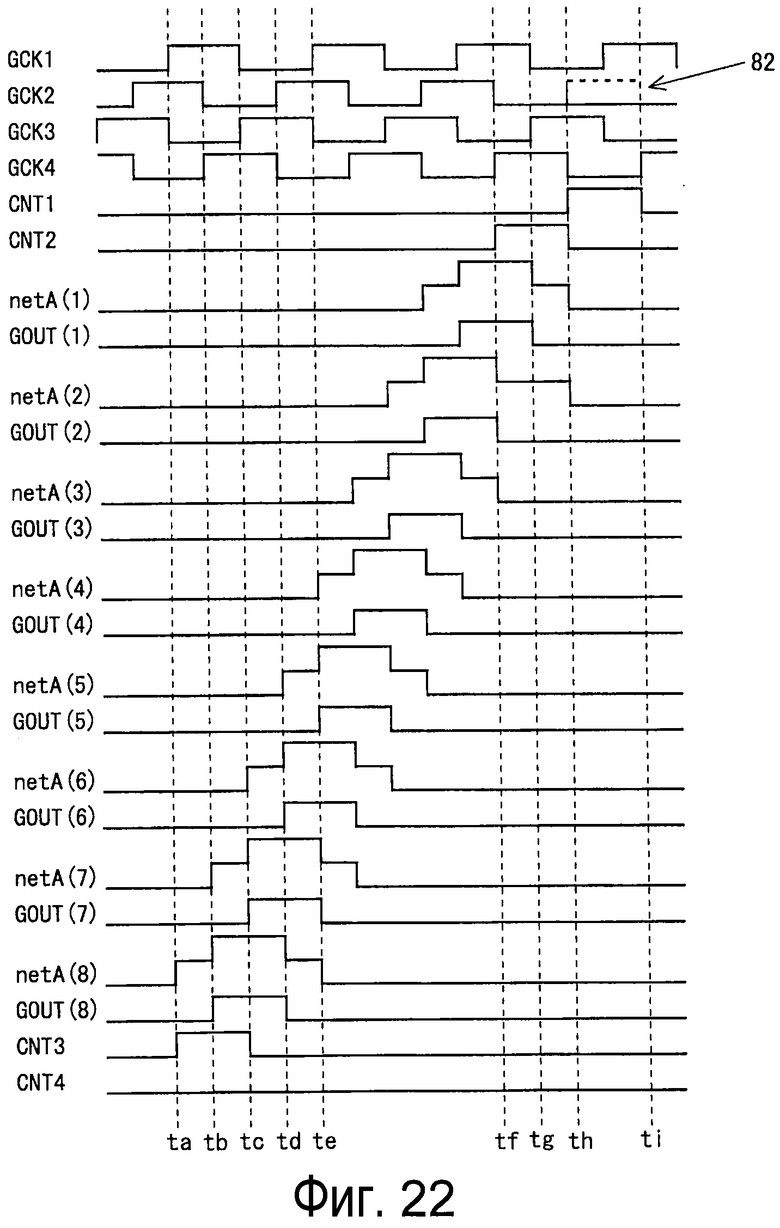

Фиг. 22 является временной диаграммой для описания общей работы сдвигового регистра, когда обратное сканирование выполняется в шестом варианте осуществления.

Фиг. 23 является блок-схемой, показывающей пример конфигурации формирователя сигналов управления затворами в первом устройстве отображения.

Фиг. 24 является принципиальной схемой, показывающей пример конфигурации одного каскада сдвигового регистра, который составляет формирователь сигналов управления затворами в традиционном примере.

Фиг. 25 является временной диаграммой для описания работы каждого каскада сдвигового регистра в традиционном примере.

Фиг. 26 является блок-схемой, показывающей конфигурацию сдвигового регистра, раскрытого в патенте (США) № 6778626.

Фиг. 27 является блок-схемой, показывающей конфигурацию сдвигового регистра, раскрытого в публикации не прошедшей экспертизу заявки на патент (Япония) № 2001-506044.

Фиг. 28 является временной диаграммой для описания работы сдвигового регистра, раскрытого в публикации не прошедшей экспертизу заявки на патент (Япония) № 2001-506044.

Режим осуществления изобретения

Далее описываются примерные варианты осуществления настоящего изобретения со ссылками на прилагаемые чертежи. В последующем описании контактный вывод затвора (электрод затвора) тонкопленочного транзистора соответствует первому электроду, контактный вывод стока (электрод стока) соответствует второму электроду, а контактный вывод истока (электрод истока) соответствует третьему электроду.

1. Первый вариант осуществления

1.1. Общая конфигурация и работа

Фиг. 2 является блок-схемой, показывающей общую конфигурацию жидкокристаллического устройства отображения с активной матрицей, согласно первому варианту осуществления настоящего изобретения. Как показано на фиг. 2, это жидкокристаллическое устройство отображения включает в себя модуль 10 отображения, схему 20 управления дисплея, формирователь 30 сигналов управления истоками (возбуждающую схему линии видеосигналов) и формирователь 40 сигналов управления затворами (возбуждающую схему линии сигналов сканирования). Схема 20 управления дисплея формируется на управляющей подложке 2. Формирователь 30 сигналов управления истоками формируется на гибкой подложке 3. Формирователь 40 сигналов управления затворами формируется на панели 4 отображения, которая включает в себя модуль 10 отображения, за счет использования аморфного кремния, поликристаллического кремния, микрокристаллического кремния, оксидного полупроводника (например, IGZO) и т.п. Другими словами, в настоящем варианте осуществления, формирователь 40 сигналов управления затворами конфигурируется монолитно.

Модуль 10 отображения включает в себя несколько (m) линий SL1-SLm шины истоков (линий видеосигналов), несколько (n) линий GL1-GLn шины затворов (линий сигналов сканирования) и несколько (n*m) частей формирования пикселов, которые предоставляются, согласно пересечениям между линиями SL1-SLm шины истоков и линиями GL1-GLn шины затворов, соответственно.

Несколько частей формирования пикселов размещаются в матричной форме и составляют пиксельную матрицу. Каждая часть формирования пикселов включает в себя тонкопленочный транзистор (TFT) 11, который является переключающим элементом, в котором контактный вывод затвора подключается к линии шины затворов, которая проходит соответствующее пересечение, и контактный вывод истока подключается к линии шины истоков, которая проходит соответствующее пересечение, пиксельный электрод, подключенный к контактному выводу стока тонкопленочного транзистора 11, общий электрод Ec, который является противоэлектродом, предоставляемым так, что он совместно используется посредством нескольких частей формирования пикселов, и жидкокристаллический слой, который предоставляется так, что он совместно используется посредством нескольких частей формирования пикселов, и который размещается между пиксельным электродом и общим электродом Ec. Пиксельная емкость Cp конфигурируется посредством емкости жидкого кристалла, сформированной посредством пиксельного электрода и общего электрода Ec. Следует отметить, что обычно вспомогательные емкости предоставляются параллельно с емкостью жидкого кристалла, чтобы надежно удерживать напряжение в пиксельной емкости Cp. Тем не менее, поскольку вспомогательные емкости не связаны непосредственно с настоящим изобретением, их описание и иллюстрация опускаются.

Схема 20 управления дисплея принимает группу TG синхронизирующих сигналов, к примеру, сигнал горизонтальной синхронизации и сигнал вертикальной синхронизации, а также сигнал DAT изображения, которые передаются снаружи, и выводит цифровой видеосигнал DV и сигнал SSP пускового импульса истока, синхросигнал SCK истока, защелкивающий стробирующий сигнал LS, первый-шестой сигналы CNT1-CNT6 управления сканированием и первый-четвертый стробирующие синхросигналы GCK1-GCK4 для управления отображением изображений в модуле 10 отображения.

Формирователь 30 сигналов управления истоками принимает цифровой видеосигнал DV, сигнал SSP пускового импульса истока, синхросигнал SCK истока и защелкивающий стробирующий сигнал LS, которые выводятся из схемы 20 управления дисплея, и применяет видеосигналы S(1)-S(m) возбуждения к линиям SL1-SLm шины истоков, соответственно.

Формирователь 40 сигналов управления затворами повторяет применение активных сигналов GOUT(1)-GOUT(n) сканирования к линиям GL1-GLn шины затворов в циклах одного периода вертикального сканирования в качестве цикла на основе первого-шестого сигналов CNT1-CNT6 управления сканированием и первого-четвертого стробирующих синхросигналов GCK1-GCK4, которые выводятся из схемы 20 управления дисплея. В настоящем варианте осуществления прямое сканирование (сканирование в порядке "GL1, GL2, ..., GLn-1, GLn") и обратное сканирование (сканирование в порядке "GLn, GLn-1, ..., GL2, GL1") переключаются на основе тактирования возникновения импульсов первого-шестого сигналов CNT1-CNT6 управления сканированием. Следует отметить, что формирователь 40 сигналов управления затворами подробно описывается ниже.

Таким образом, как описано выше, видеосигналы S(1)-S(m) возбуждения применяются к линиям SL1-SLm шины истоков, соответственно и сигналы GOUT(1)-GOUT(n) сканирования применяются к линиям GL1-GLn шины затворов соответственно, так что изображение на основе сигнала DAT изображения, переданного снаружи, отображается на модуле 10 отображения.

1.2. Конфигурация формирователя сигналов управления затворами

Конфигурация формирователя 40 сигналов управления затворами, согласно настоящему варианту осуществления, описывается ниже со ссылкой на фиг. 1, 3 и 4. Как показано на фиг. 3, формирователь 40 сигналов управления затворами конфигурируется посредством сдвигового регистра 410, имеющего n каскадов. Пиксельная матрица в n строк * m столбцов формируется в модуле 10 отображения, и каскады сдвигового регистра 410 предоставляются так, что они имеют соответствие "один-к-одному" со строками пиксельной матрицы. Помимо этого, каждый каскад сдвигового регистра 410 является бистабильной схемой, которая находится в любом из двух состояний (первого состояния и второго состояния) в каждый момент времени и которая выводит сигнал (сигнал состояния), указывающий это состояние, в качестве сигнала сканирования. Таким образом, сдвиговый регистр 410 конфигурируется посредством n бистабильных схем SR(1)-SR(n). Следует отметить, что в настоящем варианте осуществления, когда бистабильная схема находится в первом состоянии, бистабильная схема выводит сигнал состояния высокого уровня (H-уровня) в качестве сигнала сканирования, а когда бистабильная схема находится во втором состоянии, бистабильная схема выводит сигнал состояния низкого уровня (L-уровня) в качестве сигнала сканирования. Последующее описание приводится при допущении, что сдвиговый регистр 410 конфигурируется посредством восьми бистабильных схем SR(1)-SR(8).

Фиг. 1 является блок-схемой, показывающей конфигурацию сдвигового регистра 410 в формирователе 40 сигналов управления затворами. Кроме того, фиг. 4 является схемой для описания входных/выходных сигналов k-й бистабильной схемы SR(k) сдвигового регистра 410. Как показано на фиг. 1, сдвиговый регистр 410 конфигурируется посредством восьми бистабильных схем SR(1)-SR(8). Каждая бистабильная схема содержит входные контактные выводы для приема двухфазных синхросигналов CKA (в дальнейшем в этом документе называемых "первым тактовым сигналом") и CKB (в дальнейшем в этом документе называемых "вторым тактовым сигналом") соответственно, входной контактный вывод для приема напряжения VSS питания с низким уровнем мощности, входной контактный вывод для приема первого сигнала SET1 задания в качестве сигнала начала сканирования, когда прямое сканирование выполняется, входной контактный вывод для приема второго сигнала SET2 задания в качестве сигнала начала сканирования, когда обратное сканирование выполняется, входной контактный вывод для приема первого сигнала RESET1 сброса в качестве сигнала завершения сканирования, когда прямое сканирование выполняется, входной контактный вывод для приема второго сигнала RESET2 сброса в качестве сигнала завершения сканирования, когда обратное сканирование выполняется, и выходной контактный вывод для вывода сигнала GOUT сканирования.

Сигналы, предоставленные на входные контактные выводы каждого каскада (каждой бистабильной схемы), описываются ниже. Следует отметить, что, как показано на фиг. 1, напряжение VSS питания с низким уровнем мощности обычно предоставляется во все каскады SR(1)-SR(8).

Первый тактовый сигнал CKA и второй тактовый сигнал CKB предоставляются следующим образом (см. фиг. 1). В первом каскаде SR(1) первый стробирующий синхросигнал GCK1 предоставляется в качестве первого тактового сигнала CKA, а третий стробирующий синхросигнал GCK3 предоставляется в качестве второго тактового сигнала CKB. Во втором каскаде SR(2) второй стробирующий синхросигнал GCK2 предоставляется в качестве первого тактового сигнала CKA, а четвертый стробирующий синхросигнал GCK4 предоставляется в качестве второго тактового сигнала CKB. В третьем каскаде SR(3) третий стробирующий синхросигнал GCK3 предоставляется в качестве первого тактового сигнала CKA, а первый стробирующий синхросигнал GCK1 предоставляется в качестве второго тактового сигнала CKB. В четвертом каскаде SR(4) четвертый стробирующий синхросигнал GCK4 предоставляется в качестве первого тактового сигнала CKA, а второй стробирующий синхросигнал GCK2 предоставляется в качестве второго тактового сигнала CKB. Пятый-восьмой каскады SR(5)-SR(8) имеют конфигурации, которые являются аналогичными конфигурациям первого-четвертого каскадов SR(1)-R(4), описанным выше.

Первый сигнал SET1 задания и второй сигнал SET2 задания предоставляются следующим образом. Фокусируясь на k-м каскаде SR(k), сигнал GOUT(k-1) сканирования предыдущего каскада предоставляется в качестве первого сигнала SET1 задания, и сигнал GOUT(k+1) сканирования следующего каскада предоставляется в качестве второго сигнала SET2 задания (см. фиг. 4). Тем не менее, в первом каскаде SR(1) третий сигнал CNT3 управления сканированием предоставляется в качестве первого сигнала SET1 задания, а в восьмом каскаде (последнем каскаде) SR(8) четвертый сигнал CNT4 управления сканированием предоставляется в качестве второго сигнала SET2 задания (см. фиг. 1).

Первый сигнал RESET1 сброса и второй сигнал RESET2 сброса предоставляются следующим образом. Фокусируясь на k-м каскаде SR(k), сигнал GOUT(k+3) сканирования (k+3)-го каскада предоставляется в качестве первого сигнала RESET1 сброса, и сигнал GOUT(k-3) сканирования (k-3)-го каскада предоставляется в качестве второго сигнала RESET2 сброса (см. фиг. 4). Тем не менее, в первом каскаде SR(1) первый сигнал CNT1 управления сканированием предоставляется в качестве второго сигнала RESET2 сброса, во втором каскаде SR(2) второй сигнал CNT2 управления сканированием предоставляется в качестве второго сигнала RESET2 сброса, а в третьем каскаде SR(3) третий сигнал CNT3 управления сканированием предоставляется в качестве второго сигнала RESET2 сброса. В шестом каскаде SR(6) четвертый сигнал CNT4 управления сканированием предоставляется в качестве первого сигнала RESET1 сброса, в седьмом каскаде SR(7) пятый сигнал CNT5 управления сканированием предоставляется в качестве первого сигнала RESET1 сброса, а в восьмом каскаде SR(8) шестой сигнал CNT6 управления сканированием предоставляется в качестве первого сигнала RESET1 сброса (см. фиг. 1).

Сигнал, выводимый из выходного контактного вывода каждого каскада (каждой бистабильной схемы), описывается ниже. Из выходного контактного вывода k-го каскада SR(k) выводится сигнал GOUT(k) сканирования для задания k-й линии GLk шины затворов в выбранное состояние. Сигнал GOUT(k) сканирования предоставляется в (k-3)-й каскад в качестве первого сигнала RESET1 сброса, предоставляется в (k-1)-й каскад в качестве второго сигнала SET2 задания, предоставляется в (k+1)-й каскад в качестве первого сигнала SET1 задания и предоставляется в (k+3)-й каскад в качестве второго сигнала RESET2 сброса (см. фиг. 4).

Сигнал управления на стороне первого каскада реализуется посредством первого сигнала CNT1 управления сканированием, второго сигнала CNT2 управления сканированием и третьего сигнала CNT3 управления сканированием. Сигнал управления на стороне последнего каскада реализуется посредством четвертого сигнала CNT4 управления сканированием, пятого сигнала CNT5 управления сканированием и шестого сигнала CNT6 управления сканированием.

1.3. Конфигурация бистабильной схемы

Фиг. 5 является принципиальной схемой, показывающей конфигурацию бистабильной схемы (конфигурацию одного каскада сдвигового регистра 410), включенной в сдвиговый регистр 410, описанный выше. Как показано на фиг. 5, эта бистабильная схема включает в себя шесть тонкопленочных транзисторов TS (элемент переключения управления выводом), T1 (первый переключающий элемент), T2 (второй переключающий элемент), T3 (третий переключающий элемент), T4 (четвертый переключающий элемент) и T14 (четырнадцатый переключающий элемент) и конденсатор C1. Дополнительно, эта бистабильная схема включает в себя шесть входных контактных выводов 41-46 и один выходной контактный вывод (выходной узел) 51 в дополнение к входному контактному выводу для напряжения VSS питания с низким уровнем мощности. Следует отметить, что ссылка с номером 41 присоединена к входному контактному выводу, который принимает первый сигнал SET1 задания, ссылка с номером 42 присоединена к входному контактному выводу, который принимает второй сигнал SET2 задания, ссылка с номером 43 присоединена к входному контактному выводу, который принимает первый сигнал RESET1 сброса, ссылка с номером 44 присоединена к входному контактному выводу, который принимает второй сигнал RESET2 сброса, ссылка с номером 45 присоединена к входному контактному выводу, который принимает первый тактовый сигнал CKA, и ссылка с номером 46 присоединена к входному контактному выводу, который принимает второй тактовый сигнал CKB. Взаимосвязи соединений между составляющими элементами в этой бистабильной схеме описываются ниже.

Контактный вывод истока тонкопленочного транзистора T1, контактный вывод истока тонкопленочного транзистора T2, контактный вывод стока тонкопленочного транзистора T3, контактный вывод стока тонкопленочного транзистора T4 и контактный вывод затвора тонкопленочного транзистора TS подключаются друг к другу. Следует отметить, что область (межсоединение), в которой эти контактные выводы подключаются друг к другу, называется "netA" (первым узлом) для удобства.

В тонкопленочном транзисторе T1 контактный вывод затвора и контактный вывод стока подключаются к входному контактному выводу 41 (т.е. в диодном включении), и контактный вывод истока подключается к netA. В тонкопленочном транзисторе T2 контактный вывод затвора и контактный вывод стока подключаются к входному контактному выводу 42 (т.е. в диодном включении), и контактный вывод истока подключается к netA. В тонкопленочном транзисторе T3 контактный вывод затвора подключается к входному контактному выводу 43, контактный вывод стока подключается к netA, и контактный вывод истока подключается к напряжению VSS питания. В тонкопленочном транзисторе T4 контактный вывод затвора подключается к входному контактному выводу 44, контактный вывод стока подключается к netA, и контактный вывод истока подключается к напряжению VSS питания. В тонкопленочном транзисторе TS контактный вывод затвора подключается к netA, контактный вывод стока подключается к входному контактному выводу 45, и контактный вывод истока подключается к выходному контактному выводу 51. В тонкопленочном транзисторе T14 контактный вывод затвора подключается к входному контактному выводу 46, контактный вывод стока подключается к выходному контактному выводу 51, и контактный вывод истока подключается к напряжению VSS питания. В конденсаторе C1 один конец подключается к netA, а другой конец подключается к выходному контактному выводу 51.

Функции составляющих элементов в этой бистабильной схеме описываются ниже. Тонкопленочный транзистор T1 задает потенциал netA равным высокому уровню, когда первый сигнал SET1 задания имеет высокий уровень. Тонкопленочный транзистор T2 задает потенциал netA равным высокому уровню, когда второй сигнал SET2 задания имеет высокий уровень. Тонкопленочный транзистор T3 задает потенциал netA равным низкому уровню, когда первый сигнал RESET1 сброса имеет высокий уровень. Тонкопленочный транзистор T4 задает потенциал netA равным низкому уровню, когда второй сигнал RESET2 сброса имеет высокий уровень. Тонкопленочный транзистор TS предоставляет потенциал первого тактового сигнала CKA на выходной контактный вывод 51, когда потенциал netA имеет высокий уровень. Тонкопленочный транзистор T14 задает потенциал сигнала GOUT сканирования (потенциал выходного контактного вывода 51) равным низкому уровню, когда второй тактовый сигнал CKB имеет высокий уровень. Конденсатор C1 выступает в качестве емкости компенсации для поддержания потенциала netA на высоком уровне в течение периода, когда линия шины затворов, подключенная к этой бистабильной схеме, находится в выбранном состоянии.

Следует отметить, что в настоящем варианте осуществления первый модуль заряда первого узла реализуется посредством тонкопленочного транзистора T1, и второй модуль заряда первого узла реализуется посредством тонкопленочного транзистора T2. Дополнительно, первый модуль разряда первого узла реализуется посредством тонкопленочного транзистора T3, и второй модуль разряда второго узла реализуется посредством тонкопленочного транзистора T4.

1.4. Работа сдвигового регистра

Работа сдвигового регистра 410 согласно настоящему варианту осуществления описывается ниже. Следует отметить, что работа отличается в зависимости от прямого сканирования и обратного сканирования на основе тактирования возникновения импульсов первого-шестого сигналов CNT1-CNT6 управления сканированием, которые предоставляются из схемы 20 управления дисплея.

1.4.1. Работа каждого каскада (бистабильной схемы)

Работа каждого каскада (бистабильной схемы) сдвигового регистра 410 описывается со ссылкой на фиг. 5-7. Следует отметить, что фиг. 6 является временной диаграммой, когда прямое сканирование выполняется, а фиг. 7 является временной диаграммой, когда обратное сканирование выполняется. В последующем описании предполагается, что период от момента t2 времени до момента t4 времени на фиг. 6 и 7 является периодом (выбранным периодом), в течение которого линия шины затворов, подключенная к выходному контактному выводу 51 бистабильной схемы, должна быть переведена в выбранное состояние. Следует отметить, что период от момента t2 времени до момента t3 времени является периодом для предварительного заряда (предзаряда) для пиксельной емкости, а период от момента t3 времени до момента t4 времени является периодом для первичного заряда (основного заряда) для пиксельной емкости.

1.4.1.1. Работа, когда прямое сканирование выполняется

Работа бистабильной схемы при выполнении прямого сканирования описывается далее. Как показано на фиг. 6, в ходе работы жидкокристаллического устройства отображения первый тактовый сигнал CKA предоставляется на входной контактный вывод 45, и второй тактовый сигнал CKB предоставляется на входной контактный вывод 46. Таким образом, в настоящем варианте осуществления двухфазные синхросигналы, фазы которых сдвигаются на 180 градусов друг от друга, предоставляются в бистабильную схему.

В течение периода перед моментом t0 времени потенциал netA и потенциал сигнала GOUT сканирования (потенциал выходного контактного вывода 51) имеют низкий уровень. При достижении момента t0 времени импульс второго сигнала RESET2 сброса предоставляется на входной контактный вывод 44. Соответственно тонкопленочный транзистор T4 переходит во включенное состояние, и потенциал netA поддерживается на низком уровне. При достижении момента t1 времени импульс первого сигнала SET1 задания предоставляется на входной контактный вывод 41. Поскольку тонкопленочный транзистор T1 находится в диодном включении, как показано на фиг. 5, тонкопленочный транзистор T1 переходит во включенное состояние посредством импульса первого сигнала SET1 задания, и конденсатор C1 заряжается. Соответственно потенциал netA изменяется от низкого уровня к высокому уровню, и тонкопленочный транзистор TS переходит во включенное состояние. В период от момента t1 времени до момента t2 времени первый тактовый сигнал CKA имеет низкий уровень. Следовательно, в течение этого периода сигнал GOUT сканирования поддерживается на низком уровне.

При достижении момента t2 времени первый тактовый сигнал CKA изменяется от низкого уровня к высокому уровню. В это время, поскольку тонкопленочный транзистор TS находится во включенном состоянии, потенциал выходного контактного вывода 51 увеличивается с увеличением потенциала входного контактного вывода 45. В этом случае, поскольку конденсатор C1 предоставляется между netA и выходным контактным выводом 51, как показано на фиг. 5, потенциал netA также увеличивается (netA использует компенсационную обратную связь) с увеличением потенциала выходного контактного вывода 51. Как результат, большое напряжение прикладывается к тонкопленочному транзистору TS, и потенциал сигнала GOUT сканирования увеличивается до потенциала высокого уровня первого тактового сигнала CKA. Следовательно, линия шины затворов, подключенная к выходному контактному выводу 51 этой бистабильной схемы, переходит в выбранное состояние.

При достижении момента t3 времени импульс второго сигнала SET2 задания предоставляется на входной контактный вывод 42. Поскольку тонкопленочный транзистор T2 находится в диодном включении, как показано на фиг. 5, тонкопленочный транзистор T2 переходит во включенное состояние посредством импульса второго сигнала SET2 задания. Тем не менее, поскольку потенциал netA уже является высоким вследствие использования компенсационной обратной связи, потенциал netA не варьируется вследствие перехода во включенное состояние тонкопленочного транзистора T2. Помимо этого, поскольку потенциал первого тактового сигнала CKA и потенциал второго тактового сигнала CKB не изменяются в момент t3 времени, netA и сигнал GOUT сканирования поддерживают потенциалы от момента t2 времени до момента t3 времени.

При достижении момента t4 времени первый тактовый сигнал CKA изменяется от высокого уровня к низкому уровню. Соответственно потенциал выходного контактного вывода 51 снижается со снижением потенциала входного контактного вывода 45, и потенциал netA также снижается через конденсатор C1. Следует отметить, что поскольку потенциал netA снижается только посредством приблизительно снижения потенциала выходного контактного вывода 51, потенциал netA не снижается до низкого уровня и поддерживается на высоком уровне. Дополнительно, в момент t4 времени, второй тактовый сигнал CKB изменяется от низкого уровня к высокому уровню. Соответственно тонкопленочный транзистор T14 переходит во включенное состояние, и потенциал выходного контактного вывода 51, т.е. потенциал сигнала GOUT сканирования, переходит к низкому уровню.

При достижении момента t5 времени импульс первого сигнала RESET1 сброса предоставляется на входной контактный вывод 43. Соответственно тонкопленочный транзистор T3 переходит во включенное состояние, и потенциал netA изменяется от высокого уровня к низкому уровню.

В период от момента t1 времени до момента t5 времени, поскольку первый сигнал RESET1 сброса и второй сигнал RESET2 сброса имеют низкий уровень, тонкопленочные транзисторы T3 и T4 поддерживаются в отключенном состоянии. Следовательно, потенциал netA не снижается до низкого уровня в течение этого периода. В период от момента t2 времени до момента t4 времени, поскольку второй тактовый сигнал CKB имеет низкий уровень, тонкопленочные транзисторы T14 поддерживаются в отключенном состоянии. Следовательно, потенциал сигнала GOUT сканирования не снижается до низкого уровня в течение этого периода.

Как описано выше, когда прямое сканирование выполняется, первый сигнал SET1 задания выступает в качестве сигнала для увеличения потенциала netA от низкого уровня к высокому уровню, чтобы формировать активный сигнал GOUT сканирования, и первый сигнал RESET1 сброса выступает в качестве сигнала для снижения потенциала высокого уровня netA до низкого уровня. Посредством перехода первого тактового сигнала CKA к высокому уровню в течение периода, когда потенциал netA имеет высокий уровень, активный сигнал GOUT сканирования выводится из бистабильной схемы.

1.4.1.2. Работа, когда обратное сканирование выполняется

Работа бистабильной схемы при выполнении обратного сканирования описывается. Как показано на фиг. 7, в ходе работы жидкокристаллического устройства отображения, первый тактовый сигнал CKA предоставляется на входной контактный вывод 45, и второй тактовый сигнал CKB предоставляется на входной контактный вывод 46, аналогично прямому сканированию.

В течение периода перед моментом t0 времени потенциал netA и потенциал сигнала GOUT сканирования (потенциал выходного контактного вывода 51) имеют низкий уровень. При достижении момента t0 времени импульс первого сигнала RESET1 сброса предоставляется на входной контактный вывод 43. Соответственно тонкопленочный транзистор T3 переходит во включенное состояние, и потенциал netA поддерживается на низком уровне. При достижении момента t1 времени импульс второго сигнала SET2 задания предоставляется на входной контактный вывод 42. Поскольку тонкопленочный транзистор T2 находится в диодном включении, как показано на фиг. 5, тонкопленочный транзистор T2 переходит во включенное состояние посредством импульса второго сигнала SET2 задания, и конденсатор C1 заряжается. Соответственно потенциал netA изменяется от низкого уровня к высокому уровню, и тонкопленочный транзистор TS переходит во включенное состояние. В период от момента t1 времени до момента t2 времени первый тактовый сигнал CKA имеет низкий уровень. Следовательно, в течение этого периода сигнал GOUT сканирования поддерживается на низком уровне.

При достижении момента t2 времени первый тактовый сигнал CKA изменяется от низкого уровня к высокому уровню. В это время, поскольку тонкопленочный транзистор TS находится во включенном состоянии, потенциал выходного контактного вывода 51 увеличивается с увеличением потенциала входного контактного вывода 45. В этом случае, поскольку конденсатор C1 предоставляется между netA и выходным контактным выводом 51, как показано на фиг. 5, потенциал netA также увеличивается (netA использует компенсационную обратную связь) с увеличением потенциала выходного контактного вывода 51. Как результат, большое напряжение прикладывается к тонкопленочному транзистору TS, и потенциал сигнала GOUT сканирования увеличивается до потенциала высокого уровня первого тактового сигнала CKA. Следовательно, линия шины затворов, подключенная к выходному контактному выводу 51 этой бистабильной схемы, переходит в выбранное состояние.

При достижении момента t3 времени импульс первого сигнала SET1 задания предоставляется на входной контактный вывод 41. Поскольку тонкопленочный транзистор T1 находится в диодном включении, как показано на фиг. 5, тонкопленочный транзистор T1 переходит во включенное состояние посредством импульса первого сигнала SET1 задания. Тем не менее, поскольку потенциал netA уже является высоким вследствие использования компенсационной обратной связи, потенциал netA не варьируется вследствие перехода во включенное состояние тонкопленочного транзистора T1. Дополнительно, поскольку потенциал первого тактового сигнала CKA и потенциал второго тактового сигнала CKB не изменяются в момент t3 времени, netA и сигнал GOUT сканирования поддерживают потенциалы от момента t2 времени до момента t3 времени.

При достижении момента t4 времени первый тактовый сигнал CKA изменяется от высокого уровня к низкому уровню. Соответственно потенциал выходного контактного вывода 51 снижается со снижением потенциала входного контактного вывода 45, и потенциал netA также снижается через конденсатор C1. Следует отметить, что поскольку потенциал netA снижается только посредством приблизительно снижения потенциала выходного контактного вывода 51, потенциал netA не снижается до низкого уровня и поддерживается на высоком уровне. Дополнительно, в момент t4 времени, второй тактовый сигнал CKB изменяется от низкого уровня к высокому уровню. Соответственно тонкопленочный транзистор T14 переходит во включенное состояние, и потенциал выходного контактного вывода 51, т.е. потенциал сигнала GOUT сканирования переходит к низкому уровню.

При достижении момента t5 времени импульс второго сигнала RESET2 сброса предоставляется на входной контактный вывод 44. Соответственно тонкопленочный транзистор T4 переходит во включенное состояние, и потенциал netA изменяется от высокого уровня к низкому уровню.

В период от момента t1 времени до момента t5 времени потенциал netA не снижается до низкого уровня, и в период от момента времени t2 до момента t4 времени потенциал сигнала GOUT сканирования не снижается до низкого уровня, аналогично прямому сканированию.

Как описано выше, когда обратное сканирование выполняется, второй сигнал SET2 задания выступает в качестве сигнала для увеличения потенциала netA от низкого уровня к высокому уровню, чтобы формировать активный сигнал GOUT сканирования, и второй сигнал RESET2 сброса выступает в качестве сигнала для снижения потенциала высокого уровня netA до низкого уровня. Посредством перехода первого тактового сигнала CKA к высокому уровню в течение периода, когда потенциал netA имеет высокий уровень, активный сигнал GOUT сканирования выводится из бистабильной схемы.

1.4.2. Общая работа сдвигового регистра

Работа каждого каскада (бистабильной схемы) сдвигового регистра 410 описывается со ссылкой на фиг. 1-7. Следует отметить, что фиг. 8 является временной диаграммой, когда прямое сканирование выполняется, а фиг. 5 является временной диаграммой, когда обратное сканирование выполняется.

1.4.2.1. Работа, когда выполняется прямое сканирование

Общая работа сдвигового регистра 410 при выполнении прямого сканирования описывается. В ходе работы жидкокристаллического устройства отображения, как показано на фиг. 8, первый-четвертый стробирующие синхросигналы GCK1-GCK4 предоставляются в сдвиговый регистр 410. На основе первого стробирующего синхросигнала GCK1 фаза второго стробирующего синхросигнала GCK2 запаздывает на 90 градусов, фаза третьего стробирующего синхросигнала GCK3 запаздывает на 180 градусов, и фаза четвертого стробирующего синхросигнала GCK4 запаздывает на 270 градусов.

В течение периода перед моментом ta времени потенциал netA имеет низкий уровень во всех каскадах, и потенциал сигнала GOUT сканирования, выводимого из всех каскадов, имеет низкий уровень. При достижении момента ta времени импульс третьего сигнала CNT3 управления сканированием предоставляется в этот сдвиговый регистр 410. Как показано на фиг. 1, третий сигнал CNT3 управления сканированием предоставляется в первый каскад SR(1) в качестве первого сигнала SET1 задания и предоставляется в третий каскад SR(3) в качестве второго сигнала RESET2 сброса. Соответственно потенциал netA первого каскада SR(1) изменяется от низкого уровня к высокому уровню. Потенциал netA третьего каскада SR(3) поддерживается на низком уровне.

При достижении момента tb времени первый стробирующий синхросигнал GCK1 изменяется от низкого уровня к высокому уровню. В это время, поскольку потенциал входного контактного вывода 45 (см. фиг. 5) изменяется от низкого уровня к высокому уровню в первом каскаде SR(1), потенциал netA первого каскада SR(1) дополнительно увеличивается. Как результат, сигнал GOUT(1) сканирования, выводимый из первого каскада SR(1), переходит к высокому уровню. Как показано на фиг. 1, сигнал GOUT(1) сканирования, выводимый из первого каскада SR(1), предоставляется во второй каскад SR(2) в качестве первого сигнала SET1 задания и предоставляется в четвертый каскад SR(4) в качестве второго сигнала RESET2 сброса. Соответственно в момент tb времени потенциал netA второго каскада SR(2) задается равным высокому уровню, и потенциал netA четвертого каскада SR(4) поддерживается на низком уровне.

При достижении момента tc времени второй стробирующий синхросигнал GCK2 изменяется от низкого уровня к высокому уровню. В это время, поскольку потенциал входного контактного вывода 45 изменяется от низкого уровня к высокому уровню во втором каскаде SR(2), потенциал netA второго каскада SR(2) дополнительно увеличивается. Как результат, сигнал GOUT(2) сканирования, выводимый из второго каскада SR(2), переходит к высокому уровню. Сигнал GOUT(2) сканирования, выводимый из второго каскада SR(2), предоставляется в первый каскад SR(1) в качестве второго сигнала SET2 задания. В первом каскаде SR(1), поскольку потенциал netA уже является высоким вследствие использования компенсационной обратной связи, потенциал netA не варьируется вследствие сигнала GOUT(2) сканирования. Дополнительно, в момент tc времени, потенциалы первого стробирующего синхросигнала GCK1 и третьего стробирующего синхросигнала GCK3, которые предоставляются в первый каскад SR(1), не изменяются. Следовательно, в первом каскаде SR(1), для потенциала netA и потенциала сигнала GOUT сканирования, потенциалы от момента tb времени до момента tc времени поддерживаются. Сигнал GOUT(2) сканирования, выводимый из второго каскада SR(2), предоставляется в третий каскад SR(3) в качестве первого сигнала SET1 задания и также предоставляется в пятый каскад SR(5) в качестве второго сигнала RESET2 сброса. Соответственно в момент tc времени потенциал netA третьего каскада SR(3) задается равным высокому уровню, и потенциал netA пятого каскада SR(5) поддерживается на низком уровне.