Изобретение относится к вычислительной технике и может быть использовано при разработке и изготовлении распределителей имнульсов, сдвиговых и накопительных регистров.

Известна ячейка памяти для регистра сдвига, содержащая два инвертора, выполненные на МДП транзисторах, и два тактовых МДП транзистора, затвор из которых подключен к соответствующей тактовой машине.

Известная схема обладает такими недостатками, как большой величиной напряжения иарафазных тактовых импульсов, большой потребляемой мощностью при работе последовательно соединенных элементов в режиме распределения импульсов по различным каналам связи, низкой частотой.распределения импульсов по каналам связи.

Для улучшения эксплуатационных характеристик предлагаемая ячейка содержит два конденсатора связи, первая обкладка каждого из которых подключена к стоку МДП транзистора соответствующего инвертора, вторая- к стоку соответствующего тактового транзистора и к затвору МДП транзистора последующего инвертора, а истоки тактовых МДП транзисторов подключены к шине нулевого потенциала.

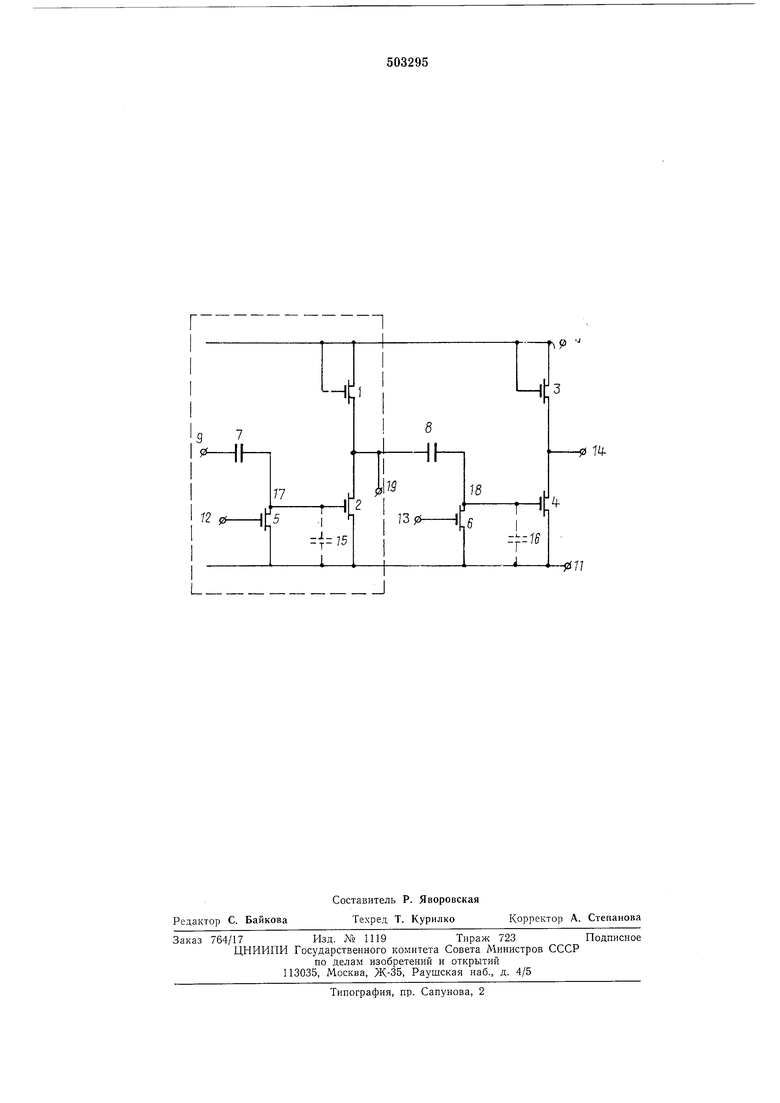

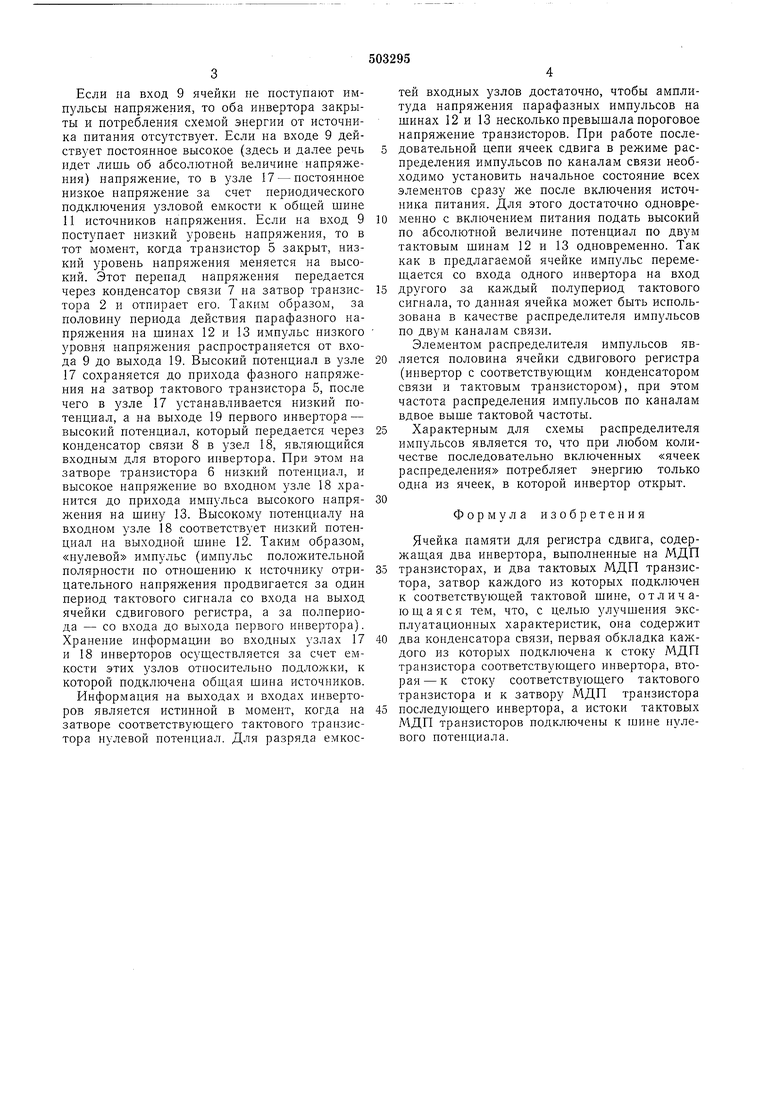

На чертеже представлена ячейка регистра сдвига.

Предлагаемая ячейка сдвигового регистра построена на МДП транзисторах 1-6. Первые (ключевые) транзисторы 2 и 4 и вторые (нагрузочные) транзисторы и 3попарно об; разуют два инвертора, включенные последовательно. К затвору первого (ключевого) транзистора 2 и стоку тактового транзистора

5подключена одна обкладка конденсатора связи 7, а к затвору первого (ключевого) транзистора 4 и стоку тактового транзистора

6- обкладка второго коиденсатора связи 8. Вторые обкладки конденсаторов связи 7 и 8 соединены, соответственно, с входной 9 шиной ячейки и со стоком ключевого транзисто)а 2. Затворы и стоки вторых (нагрузочных) транзисторов 1 и 3 соединены с шиной 10 источника питания, а истоки ключевых транзисторов 2 и 4, тактовых траизисторов 5 и 6- с общей шиной 11 источников напряжения. Затворы тактовых транзисторов 5 и 6 соединены с тактовыми шинами 12 и 13 источников фазовых HMnyvTbcoB. Сток транзистора 4 соединен с выходной шиной 14 ячейки. Позициями 15, 16 обозначены емкости сток-затвор транзисторов 2 и 4, соответственно, а позициями 17, 18 - выделенные узлы схемы, 19 - выход первого инвертора.

Ячейка регистра сдвига работает следующим образом.

Если на вход 9 ячейки не поступают импульсы напряжения, то оба инвертора закрыты и потребления схемой энергии от источника питания отсутствует. Если на входе 9 действует постоянное высокое (здесь и далее речь идет лишь об абсолютной величине напряжения) напряжение, то в узле 17 - постоянное низкое напряжение за счет периодического подключения узловой емкости к общей шине 11 источников напряжения. Если на вход 9 поступает низкий уровень напряжения, то в тот момент, когда транзистор 5 закрыт, ннзкий уровень напряжения меняется на высокий. Этот перепад папряжения передается через копденсатор связи 7 на затвор транзистора 2 и отпирает его. Таким образом, за половину периода действия парафазного напряжения на шинах 12 и 13 импульс низкого уровня напряжения распространяется от входа 9 до выхода 19. Высокий потенциал в узле 17 сохраняется до нрихода фазного напряжения на затвор тактового транзистора 5, после чего в узле 17 устанавливается низкий потенциал, а на выходе 19 первого инвертора - высокий потенциал, который передается через конденсатор связи 8 в узел 18, являющийся входным для второго инвертора. При этом на затворе транзистора 6 низкий потенциал, и высокое напряжение во входном узле 18 хранится до прихода импульса высокого напряжения на шину 13. Высокому потенциалу на входном узле 18 соответствует низкий потенциал на выходной шине 12. Таким образом, «нулевой импульс (имиульс положительной полярности по отношению к источнику отрицательного напряжения продвигается за один период тактового сигнала со входа на выход ячейки сдвигового регистра, а за нолпериода - со входа до выхода первого инвертора). Хранение информации во входных узлах 17 и 18 инверторов осуществляется за счет емкости этих узлов относительно подложки, к которой подключена общая щина источников.

Информация на выходах и входах инверторов является истинной в момент, когда на затворе соответствующего тактового транзистора нулевой потенциал. Для разряда емкостей входных узлов достаточно, чтобы амплитуда напряжения нарафазных импульсов на шинах 12 и 13 несколько превышала пороговое напряжение транзисторов. При работе последовательной цепи ячеек сдвига в режиме распределения импульсов по каналам связи необходимо установить начальное состояние всех элементов сразу же после включения источника питания. Для этого достаточно одновременно с включением питания подать высокий по абсолютной величине потенциал по двум тактовым шинам 12 и 13 одновременно. Так как в предлагаемой ячейке импульс перемещается со входа одного инвертора на вход

5 другого за каждый полупериод тактового сигнала, то данная ячейка может быть использована в качестве распределителя импульсов по двум каналам связи.

Элементом распределителя импульсов является половина ячейки сдвигового регистра (инвертор с соответствующим конденсатором связи и тактовЫлМ транзистором), при этом частота распределения импульсов по каналам вдвое выше тактовой частоты.

5 Характерным для схемы распределителя импульсов является то, что при любом количестве последовательно включенных «ячеек распределения потребляет энергию только одна из ячеек, в которой инвертор открыт.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая два инвертора, выполненные на МДП

5 транзисторах, и два тактовых МДП транзистора, затвор каждого из которых подключен к соответствующей тактовой шине, отличающаяся тем, что, с целью улучщения эксплуатационных характеристик, она содержит

0 два конденсатора связи, первая обкладка каждого из которых подключена к стоку МДП транзистора соответствующего инвертора, вторая- к стоку соответствующего тактового транзистора и к затвору МДП транзистора

5 последующего инвертора, а истоки тактовых МДП транзисторов подключены к шине нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов на мдптранзисторах | 1974 |

|

SU668092A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Четырехтактный динамический регистр на мдп-транзисторах | 1973 |

|

SU438106A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ФОТОЧУВСТВИТЕЛЬНОЕ УСТРОЙСТВО | 1988 |

|

RU1526522C |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

Авторы

Даты

1976-02-15—Публикация

1972-11-24—Подача