Область техники, к которой относится изобретение

Настоящее изобретение относится к возбуждающей схеме дисплейной панели и сдвиговому регистру для использования в такой возбуждающей схеме дисплейной панели.

Уровень техники

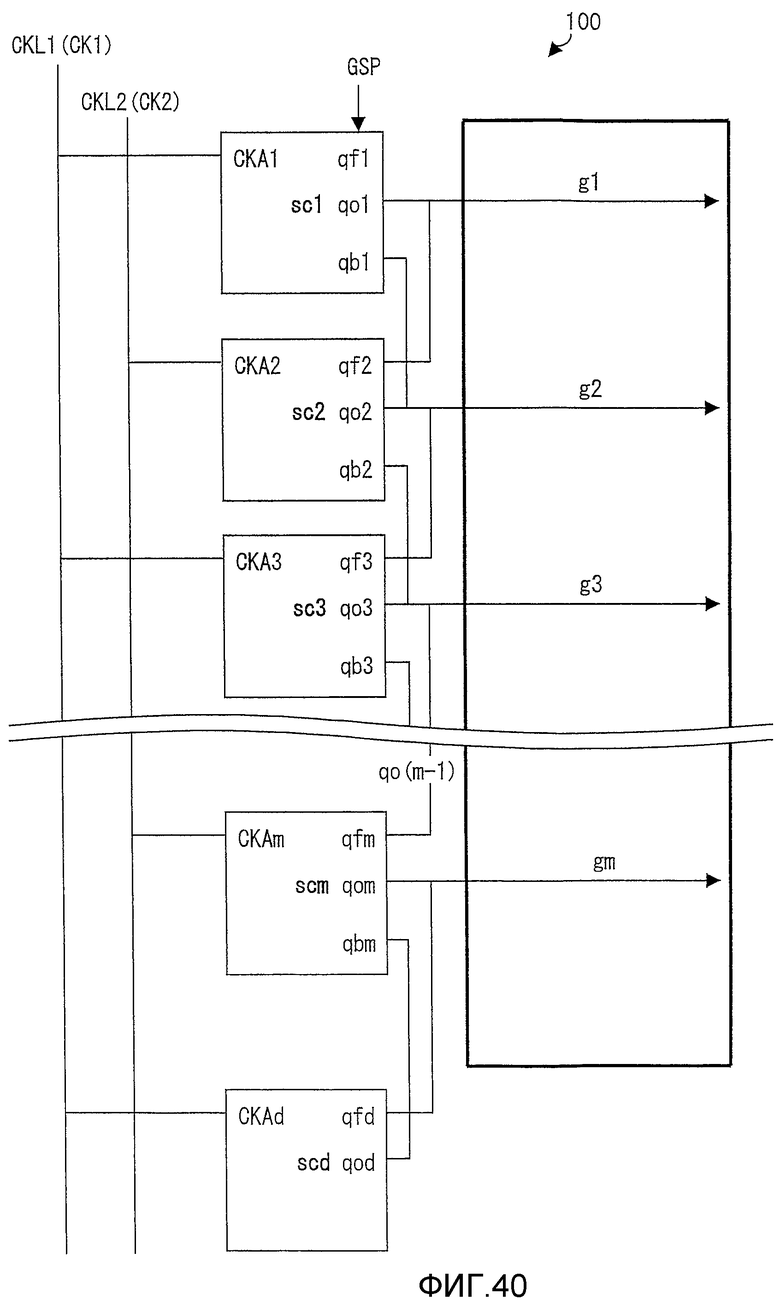

Фиг.40 является принципиальной схемой, иллюстрирующей традиционный сдвиговый регистр для использования в драйвере затвора, который включен в жидкокристаллическое дисплейное устройство. Как показано на фиг.40, традиционный сдвиговый регистр 100 состоит из множества схем sc1, sc2, …, scm и scd сдвига (модульных схем), которые подключаются каскадно. Каждая из схем sci сдвига (i=1, 2, 3, …, или m) включает в себя входные узлы qfi, qbi и CKAi и выходной узел qoi. Схема scd сдвига, которая является фиктивной схемой сдвига, включает в себя входные узлы qfd и CKAd и выходной узел qod.

Схема sc1 сдвига имеет узел qf1, подключенный к выходному контактному выводу, через который выводится сигнал GSP импульса начала стробирования, имеет узел qb1, подключенный к узлу qo2 схемы sc2 сдвига, и имеет узел CKA1, подключенный к первой линии CKL1 синхросигнала, в которую подается первый синхросигнал; и из узла qo1 выводится сигнал g1 отпирающего импульса (сигнал выбора сигнальной линии). Дополнительно, каждая из схем sci сдвига (i=2, 3, …, или m-1) имеет узел qfi, подключенный к узлу qo(i-1) схемы sc(i-1) сдвига, имеет узел qbi, подключенный к узлу qo(i+с) схемы sc(i+1) сдвига, и имеет узел CKAi, подключенный к первой линии CKL1 синхросигнала или второй линии CKL2 синхросигнала, в которую подается второй синхросигнал; и из узла qoi выводится сигнал gi отпирающего импульса (сигнал выбора сигнальной линии). В случае если i является нечетным числом, узел CKAi подключается к первой линии CKL1 синхросигнала, а в случае если i является четным числом, узел CKAi подключается ко второй линии CKL2 синхросигнала.

Схема scm сдвига имеет узел qfm, подключенный к узлу qo(m-1) схемы sc(m-1) сдвига, имеет узел qbm, подключенный к узлу qod фиктивной схемы scd сдвига, и имеет узел CKAm, подключенный к первой линии CKL1 синхросигнала или второй линии CKL2 синхросигнала; и из узла qom выводится сигнал gm отпирающего импульса (сигнал выбора сигнальной линии). В случае если m является нечетным числом, схема scm сдвига имеет узел CKAi, подключенный к первой линии CKL1 синхросигнала, а в случае если m является четным числом, схема scm сдвига имеет узел CKAi, подключенный ко второй линии CKL2 синхросигнала. Фиктивная схема scd сдвига имеет узел qfd, подключенный к узлу qom схемы scm сдвига, и узел CKAd, подключенный к первой линии CKL1 синхросигнала или второй линии CKL2 синхросигнала. В случае если m является нечетным числом, фиктивная схема scd сдвига имеет узел CKAd, подключенный ко второй линии CKL2 синхросигнала, а в случае если m является четным числом, фиктивная схема scd сдвига имеет узел CKAd, подключенный к первой линии CKL1 синхросигнала.

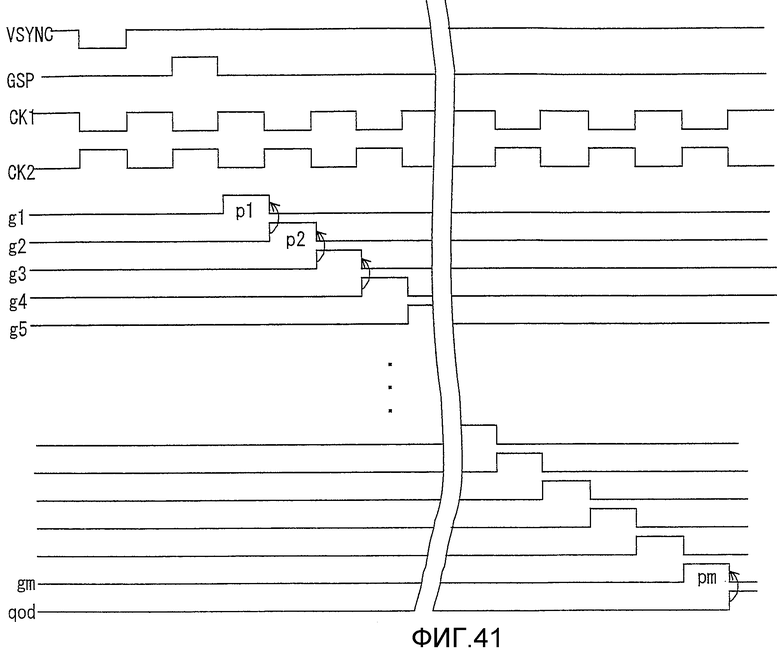

Фиг.41 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и вывода через узел qod. Следует отметить, что каждый из первого синхросигнала CK1 и второго синхросигнала CK2 включает в себя, в одном цикле, один "H (высокий)" (активный) тактовый интервал и один "L (низкий)" (неактивный) тактовый интервал; синхронно с активацией (повышением) одного из синхросигналов CK1 и CK2, другой из синхросигналов CK1 и CK2 деактивируется (падает).

В схеме sc1 сдвига в первом каскаде электрический потенциал узла qf1 повышается при активации сигнала GSP импульса начала стробирования. Как результат, первый синхросигнал CK1 выводится через узел qo1, и, соответственно, сигнал g1 отпирающего импульса активируется. Кроме того, в схеме sc2 сдвига в последующем каскаде, электрический потенциал узла qf2 повышается при активации сигнала g1 отпирающего импульса. Как результат, второй синхросигнал CK2 выводится через узел qo2, и, соответственно, сигнал g2 отпирающего импульса активируется. Эта активация сигнала g2 отпирающего импульса приводит к тому, что первый синхросигнал CK1 больше не выводится через узел qo1 в схеме sc1 сдвига, а электрический потенциал источника питания на стороне с более низким потенциалом выводится через узел qo1. Следовательно, сигнал g1 отпирающего импульса деактивируется после активности в течение определенного периода времени, что, как результат, формирует импульс P1.

Таким образом, в схеме sci сдвига (i=2, 3, …, или m-1) электрический потенциал узла qfi повышается при активации сигнала g(i-1) отпирающего импульса. Как результат, синхросигнал (CK1 или CK2) выводится через узел qoi, и, соответственно, сигнал gi отпирающего импульса активируется. Кроме того, в схеме sc(i+1) сдвига в последующем каскаде, электрический потенциал узла qf(i+1) повышается при активации сигнала gi отпирающего импульса. Как результат, синхросигнал (CK2 или CK1) выводится через узел qo(i+1), и, соответственно, сигнал g(i+1) отпирающего импульса активируется. Эта активация сигнала g(i+1) отпирающего импульса приводит к тому, что синхросигнал больше не выводится через узел qoi в схеме sci сдвига, а электрический потенциал источника питания на стороне с более низким потенциалом выводится через узел qoi. Следовательно, сигнал gi отпирающего импульса деактивируется после активности в течение определенного периода времени, что, как результат, формирует импульс Pi.

Кроме того, в схеме scm сдвига, электрический потенциал узла qfm повышается при активации сигнала g(m-1) отпирающего импульса. Как результат, синхросигнал (CK1 или CK2) выводится через узел qom, и, соответственно, сигнал gm отпирающего импульса активируется. Дополнительно, в фиктивной схеме scd сдвига в последующем каскаде, электрический потенциал узла qfd повышается при активации сигнала gm отпирающего импульса. Как результат, синхросигнал (CK2 или CK1) выводится через узел qod (т.е. электрический потенциал в узле qod повышается). Повышение электрического потенциала узла qod приводит к тому, что синхросигнал больше не выводится через узел qom в схеме scm сдвига, а электрический потенциал источника питания на стороне с более низким потенциалом выводится через узел qom. Следовательно, сигнал gm отпирающего импульса деактивируется после активности в течение определенного периода времени, что, как результат, формирует импульс Pm.

Как пояснено выше, в сдвиговом регистре 100, сигналы отпирающего импульса, выводимые из соответствующих схем сдвига, последовательно активируются в течение определенного периода времени, и импульс выводится последовательно из соответствующих схем сдвига согласно порядковому номеру с началом в схеме sc1 сдвига в первом каскаде до схемы scm сдвига в конечном каскаде. Следует отметить, что следующие патентные документы 1-3 являются известными документами, релевантными для технологии, описанной выше.

Патентный документ 1. Публикация заявки на патент (Япония), Tokukai, номер 2001-273785 A (Дата публикации: 5 октября 2001 года)

Патентный документ 2. Публикация заявки на патент (Япония), Tokukai, номер 2006-24350 A (Дата публикации: 26 января 2006 года)

Патентный документ 3. Публикация заявки на патент (Япония), Tokukai, номер 2007-114771 A (Дата публикации: 10 мая 2007 года)

Сущность изобретения

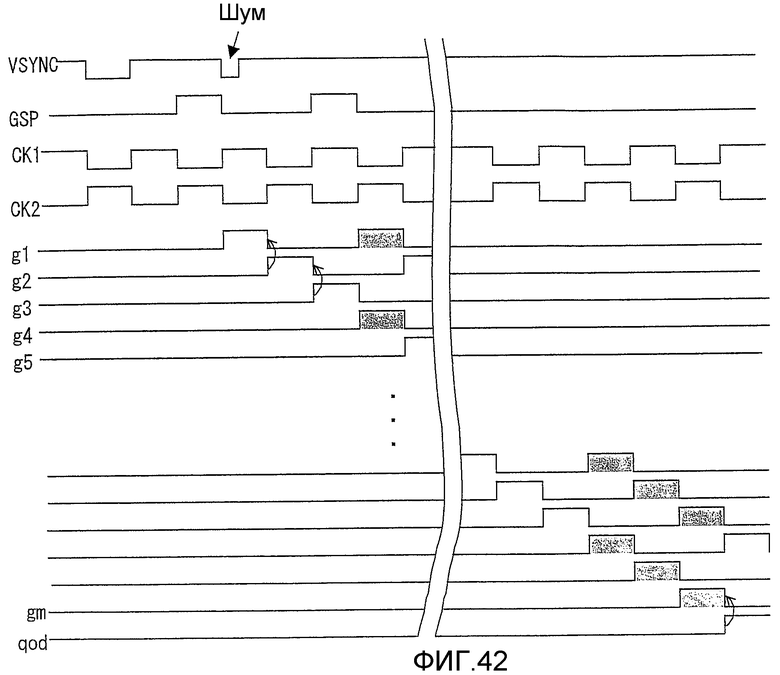

В традиционном сдвиговом регистре сигнал GSP импульса начала стробирования активируется в связи с выводом импульса сигнала VSYNC вертикальной синхронизации. В этом случае, как проиллюстрировано на фиг.42, например, если шум формируется в сигнале VSYNC вертикальной синхронизации, сигнал GSP импульса начала стробирования становится активированным в связи с шумом, тем самым инструктируя двум импульсам выводиться из двух схем сдвига одновременно. Такая аномальность, что два импульса выводятся одновременно, может продолжаться до конечного каскада сдвигового регистра. Кроме того, например, если шум формируется в сигнале HSYNC горизонтальной синхронизации, синхросигнал становится разупорядоченным, и такая аномальность, что ширина импульса сигнала отпирающего импульса становится небольшой, может продолжаться до конечного каскада сдвигового регистра.

Как описано выше, при традиционном сдвиговом регистре, аномальность в сигнале отпирающего импульса продолжается до конечного каскада в случае, если сигнал синхронизации, такой как сигнал VSYNC вертикальной синхронизации, сигнал HSYNC горизонтальной синхронизации, сигнал DE разрешения передачи данных и т.п., включает в себя аномальность, такую как шум. Это приводит к разупорядочению отображения на панели и предусматривает большую нагрузку на источник питания при возбуждении панели.

Настоящее изобретение предлагает возбуждающую схему дисплейной панели, которая дает возможность подавлять (i) разупорядочение отображения, и (ii) увеличение нагрузки на источник питания, в случае если аномальность возникает в сигнале синхронизации (VSYNC или HSYNC или DE). Настоящее изобретение дополнительно предлагает сдвиговый регистр для использования в такой возбуждающей схеме дисплейной панели.

Дополнительно, традиционный сдвиговый регистр требует предоставления схемы scd сдвига (фиктивного каскада) для сброса схемы scm сдвига (конечного каскада). Это приводит к увеличению размера площади схемы в сдвиговом регистре.

Настоящее изобретение предлагает возбуждающую схему дисплейной панели, которая дает возможность сдерживать размер площади схемы в сдвиговом регистре. Настоящее изобретение дополнительно предлагает сдвиговый регистр для использования в такой возбуждающей схеме дисплейной панели.

Возбуждающая схема дисплейной панели настоящего изобретения - это возбуждающая схема дисплейной панели, принимающая сигнал синхронизации извне, причем возбуждающая схема дисплейной панели включает в себя сдвиговый регистр, состоящий из модульных схем, подключенных каскадно, при этом модульные схемы выводят сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом импульсы выводятся последовательно из соответствующих модульных схем согласно порядковому номеру с началом в первом каскаде до конечного каскада, причем каждая из модульных схем принимает (i) синхросигнал, (ii) сигнал пускового импульса или сигнал выбора сигнальной линии, сформированный в каскаде, отличном от собственного каскада, и (iii) сигнал очистки, при этом сигнал очистки становится активным в случае, если аномальность включена, по меньшей мере, в сигнал синхронизации, и импульсы не выводятся из сдвигового регистра после того, как сигнал очистки становится активным до тех пор, пока последующий период вертикального сканирования не начинается.

Кроме того, возбуждающая схема дисплейной панели настоящего изобретения - это возбуждающая схема дисплейной панели, принимающая сигнал синхронизации извне, причем возбуждающая схема дисплейной панели включает в себя сдвиговый регистр, состоящий из модульных схем, подключенных каскадно, при этом каждая из модульных схем принимает синхросигнал и выводит соответствующий импульс при помощи принимаемого синхросигнала, причем импульсы выводятся последовательно из каждого из каскадов, при этом каждая из модульных схем имеет выходной транзистор, предусмотренный между входным контактным выводом синхросигнала и выходным контактным выводом соответствующей модульной схемы, причем сигнал очистки формируется и вводится в каждую из модульных схем, при этом сигнал очистки становится активным в случае, если аномальность включена, по меньшей мере, в сигнал синхронизации, и после того, как сигнал очистки становится активным, выходной транзистор, предусмотренный в каждой из модульных схем, отключается до тех пор, пока последующий период вертикального сканирования не начинается.

Согласно возбуждающей схеме дисплейной панели настоящего изобретения, после того, как сигнал очистки становится активным вследствие аномальности в сигнале синхронизации, импульс, выводимый из сдвигового регистра, прекращается в дальнейшем. Следовательно, можно предотвращать разупорядочение отображения и подавлять увеличение нагрузки, подаваемой на источник питания.

Возбуждающая схема дисплейной панели может быть выполнена таким образом, что синхросигнал, сигнал пускового импульса и сигнал очистки формируются на основе сигнала синхронизации.

Возбуждающая схема дисплейной панели может быть выполнена таким образом, что сигнал синхронизации включает в себя, по меньшей мере, один из сигнала вертикальной синхронизации, сигнала горизонтальной синхронизации и сигнала разрешения передачи данных.

Возбуждающая схема дисплейной панели может быть выполнена таким образом, что, независимо от того, включена или нет аномальность в сигнал синхронизации, сигнал очистки становится активным после того, как конечный каскад выводит соответствующий импульс, так что сигнал выбора сигнальной линии, выводимый из конечного каскада, остается неактивным.

Возбуждающая схема дисплейной панели может быть выполнена таким образом, что независимо от того, включена или нет аномальность в сигнал синхронизации, сигнал очистки становится активным после того, как импульс выводится из модульной схемы в конечном каскаде, так что выходной транзистор в каждой из модульных схем отключается до тех пор, пока последующий период вертикального сканирования не начинается.

Возбуждающая схема дисплейной панели может быть выполнена таким образом, что сигнал очистки становится активным во время, когда импульсы не выводятся, или во время, когда импульс становится неактивным.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждая из модульных схем за исключением схемы в конечном каскаде включает в себя транзистор задания, выходной транзистор, транзистор сброса, транзистор очистки и конденсатор, при этом транзистор задания, выходной транзистор, транзистор сброса и транзистор очистки имеют управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, и конденсатор имеет первый электрод и второй электрод, причем транзистор очистки принимает сигнал очистки через управляющий контактный вывод, причем транзистор сброса принимает, через управляющий контактный вывод, сигнал выбора сигнальной линии, выводимый из каскада, следующего после собственного каскада, причем транзистор задания принимает, через управляющий контактный вывод, сигнал пускового импульса или сигнал выбора сигнальной линии, выводимый из каскада, предшествующего собственному каскаду, причем выходной транзистор принимает синхросигнал через первый проводящий контактный вывод, при этом второй проводящий контактный вывод выходного транзистора подключается к первому электроду конденсатора, управляющий контактный вывод транзистора задания и первый проводящий контактный вывод транзистора задания подключаются друг к другу, а второй проводящий контактный вывод транзистора задания подключается к (i) управляющему контактному выводу выходного транзистора и (ii) второму электроду конденсатора, при этом первый проводящий контактный вывод транзистора очистки подключается к управляющему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора очистки подключается к источнику постоянного напряжения, причем первый проводящий контактный вывод транзистора сброса подключается к управляющему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора сброса подключается к источнику постоянного напряжения, и причем второй проводящий контактный вывод выходного транзистора выступает в качестве выходного контактного вывода соответствующей модульной схемы. Следует отметить, что, в настоящей заявке, один из контактного вывода истока и контактного вывода стока транзистора задан как первый проводящий контактный вывод, а другой из контактного вывода истока и контактного вывода стока транзистора задан как второй проводящий контактный вывод. В зависимости от схемы транзистора первый проводник всех транзисторов может быть контактным выводом истока, или первый транзистор определенного транзистора может быть контактным выводом стока, и первые транзисторы оставшихся транзисторов могут быть контактным выводом истока.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждая из модульных схем за исключением схемы в конечном каскаде дополнительно включает в себя транзистор подачи электрического потенциала, причем транзистор подачи электрического потенциала имеет управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, при этом первый проводящий контактный вывод транзистора подачи электрического потенциала подключается ко второму проводящему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора подачи электрического потенциала подключается к источнику постоянного напряжения, причем транзистор подачи электрического потенциала принимает, через управляющий контактный вывод, сигнал выбора сигнальной линии, выводимый из каскада, следующего после собственного каскада.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждая из модульных схем за исключением схемы в конечном каскаде дополнительно включает в себя транзистор подачи электрического потенциала, причем транзистор подачи электрического потенциала имеет управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, при этом первый проводящий контактный вывод транзистора подачи электрического потенциала подключается ко второму проводящему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора подачи электрического потенциала подключается к источнику постоянного напряжения, причем транзистор подачи электрического потенциала принимает, через управляющий контактный вывод, синхросигнал, отличный от синхросигнала, принимаемого через первый проводящий контактный вывод выходного транзистора.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что модульная схема в конечном каскаде включает в себя транзистор задания, выходной транзистор, транзистор очистки и конденсатор, при этом транзистор задания, выходной транзистор и транзистор очистки имеют управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, и конденсатор имеет первый электрод и второй электрод, причем транзистор очистки принимает сигнал очистки через управляющий контактный вывод, причем транзистор задания принимает, через управляющий контактный вывод, сигнал выбора сигнальной линии, выводимый из каскада, предшествующего собственному каскаду, и причем выходной транзистор принимает синхросигнал через первый проводящий контактный вывод, при этом второй проводящий контактный вывод выходного транзистора подключается к первому электроду конденсатора, управляющий контактный вывод транзистора задания и первый проводящий контактный вывод транзистора задания подключаются друг к другу, а второй проводящий контактный вывод транзистора задания подключается к (i) управляющему контактному выводу выходного транзистора и (ii) второму электроду конденсатора, при этом первый проводящий контактный вывод транзистора очистки подключается к управляющему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора очистки подключается к источнику постоянного напряжения, и причем второй проводящий контактный вывод выходного транзистора выступает в качестве выходного контактного вывода модульной схемы в конечном каскаде.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что модульная схема в конечном каскаде дополнительно включает в себя транзистор подачи электрического потенциала, причем транзистор подачи электрического потенциала имеет управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, при этом транзистор подачи электрического потенциала принимает сигнал очистки через свой управляющий контактный вывод, при этом первый проводящий контактный вывод транзистора подачи электрического потенциала подключается ко второму проводящему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора подачи электрического потенциала подключается к источнику постоянного напряжения.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что сигнал очистки становится активным во время, когда сигнал выбора сигнальной линии, принимаемый из соответствующего каскада, становится неактивным, или становится неактивным в то время, когда сигнал выбора сигнальной линии, принимаемый из соответствующего каскада, является неактивным.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что множество синхросигналов, каждый из которых имеет фазы, отличные друг от друга, вводится в сдвиговый регистр, при этом множество синхросигналов принимается посредством выходных транзисторов различных модульных схем, соответственно.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждый из множества синхросигналов имеет неактивный период, который частично совпадает с неактивным периодом другого из множества синхросигналов.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что множество синхросигналов включает в себя два синхросигнала, которые сдвинуты по фазе на половину цикла.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что, по меньшей мере, один из множества синхросигналов становится неактивным в то время, когда сигнал очистки становится активным.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждый из транзистора задания, выходного транзистора, транзистора сброса и транзистора очистки является транзистором с каналом n-типа.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждый из транзистора задания, выходного транзистора, транзистора сброса, транзистора очистки и транзистора подачи электрического потенциала является транзистором с каналом n-типа.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что первый проводящий контактный вывод каждого из транзисторов является контактным выводом стока, а второй проводящий контактный вывод каждого из транзисторов является контактным выводом истока.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что первый проводящий контактный вывод каждого из транзисторов является контактным выводом истока, а второй проводящий контактный вывод каждого из транзисторов является контактным выводом стока.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена так, что дополнительно включает в себя контроллер синхронизации, в который вводится сигнал синхронизации, для формирования синхросигнала, сигнала пускового импульса и сигнала очистки с использованием таким образом введенного сигнала синхронизации.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена так, что дополнительно включает в себя схему определения аномальности для определения аномальности сигнала синхронизации, при этом сигнал очистки формируется на основе результата определения.

Жидкокристаллическое дисплейное устройство настоящего изобретения включает в себя возбуждающую схему дисплейной панели; и жидкокристаллическую панель.

Жидкокристаллическое дисплейное устройство настоящего изобретения может быть выполнено таким образом, что сдвиговый регистр предусмотрен монолитно в жидкокристаллической панели.

В жидкокристаллическом дисплейном устройстве настоящего изобретения жидкокристаллическая панель может формироваться при помощи аморфного кремнийорганического соединения. Кроме того, жидкокристаллическая панель может формироваться при помощи поликристаллического кремния.

Сдвиговый регистр настоящего изобретения предусмотрен в возбуждающей схеме дисплейной панели, который принимает сигнал синхронизации, причем сдвиговый регистр состоит из модульных схем, подключенных каскадно, при этом модульные схемы формируют сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом импульсы выводятся последовательно из соответствующих модульных схем, согласно порядковому номеру с началом в первом каскаде до конечного каскада, причем каждая из модульных схем принимает (i) синхросигнал, (ii) сигнал пускового импульса или сигнал выбора сигнальной линии, сформированный посредством каскада, отличного от собственного каскада, и (iii) сигнал очистки, при этом сигнал очистки становится активным в случае, если аномальность включена, по меньшей мере, в сигнал синхронизации, и импульсы не выводятся после того, как сигнал очистки становится активным до тех пор, пока последующий период вертикального сканирования не начинается. В этом случае сдвиговый регистр может быть выполнен монолитно.

Способ настоящего изобретения для возбуждения дисплейного устройства, причем дисплейное устройство принимает сигнал синхронизации извне и включает в себя сдвиговый регистр, состоящий из модульных схем, подключенных каскадно, при этом модульные схемы формируют сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом сдвиговый регистр выводит импульсы последовательно из соответствующих модульных схем согласно порядковому номеру с началом в первом каскаде до конечного каскада, является способом, включающим в себя: ввод, в каждую из модульных схем, (i) синхросигнала, (ii) сигнала пускового импульса или сигнала выбора сигнальной линии, сформированного в каскаде, отличном от собственного каскада, и (iii) сигнала очистки; и активацию сигнала очистки в случае, если аномальность включена, по меньшей мере, в сигнал синхронизации, так что импульсы не выводятся из сдвигового регистра после того, как сигнал очистки становится активным до тех пор, пока последующий период вертикального сканирования не начинается.

Возбуждающая схема дисплейной панели настоящего изобретения включает в себя: сдвиговый регистр, состоящий из модульных схем, подключенных каскадно, при этом модульные схемы выводят сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом сдвиговый регистр выводит импульсы последовательно из соответствующих модульных схем согласно порядковому номеру с началом в первом каскаде до конечного каскада, причем модульная схема в конечном каскаде принимает (i) сигнал выбора сигнальной линии, сформированный в каскаде, отличном от собственного каскада, (ii) синхросигнал и (iii) сигнал очистки, и при этом сигнал очистки становится активным после того, как конечный каскад выводит соответствующий импульс, так что сигнал выбора сигнальной линии, выводимый из конечного каскада, остается неактивным.

Согласно возбуждающей схеме дисплейной панели настоящего изобретения сброс может выполняться при помощи сигнала очистки в конечном каскаде (модульной схеме). Следовательно, фиктивный каскад (фиктивная схема сдвига) не требуется, как в традиционной технологии, и тем самым можно уменьшать площадь схемы сдвигового регистра.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что каждая из модульных схем за исключением модульной схемы в конечном каскаде включает в себя транзистор задания, выходной транзистор, транзистор сброса и конденсатор, при этом транзистор задания, выходной транзистор и транзистор сброса имеют управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, и конденсатор имеет первый электрод и второй электрод, причем транзистор задания принимает, через управляющий контактный вывод, сигнал пускового импульса или сигнал выбора сигнальной линии, выводимый из каскада, предшествующего собственному каскаду, причем транзистор сброса принимает, через управляющий контактный вывод, сигнал выбора сигнальной линии, выводимый из каскада, следующего после собственного каскада, и причем выходной транзистор принимает синхросигнал через первый проводящий контактный вывод, при этом второй проводящий контактный вывод выходного транзистора подключается к первому электроду конденсатора, управляющий контактный вывод транзистора задания и первый проводящий контактный вывод транзистора задания подключаются друг к другу, а второй проводящий контактный вывод транзистора задания подключается к (i) управляющему контактному выводу выходного транзистора и (ii) второму электроду конденсатора, причем первый проводящий контактный вывод транзистора сброса подключается к управляющему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора сброса подключается к источнику постоянного напряжения, и причем второй проводящий контактный вывод выходного транзистора выступает в качестве выходного контактного вывода соответствующей модульной схемы.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что модульная схема в конечном каскаде включает в себя транзистор задания, выходной транзистор, транзистор очистки, предусмотренный для сброса конечного каскада, и конденсатор; при этом транзистор задания, выходной транзистор и транзистор очистки имеют управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, и конденсатор имеет первый электрод и второй электрод, причем транзистор задания принимает, через управляющий контактный вывод, сигнал выбора сигнальной линии, выводимый из каскада, предшествующего собственному каскаду, причем транзистор очистки принимает сигнал очистки через управляющий контактный вывод, и причем выходной транзистор принимает синхросигнал через первый проводящий контактный вывод, при этом второй проводящий контактный вывод выходного транзистора подключается к первому электроду конденсатора, управляющий контактный вывод транзистора задания и первый проводящий контактный вывод транзистора задания подключаются друг к другу, а второй проводящий контактный вывод транзистора задания подключается к (i) управляющему контактному выводу выходного транзистора и (ii) второму электроду конденсатора, при этом первый проводящий контактный вывод транзистора очистки подключается к управляющему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора очистки подключается к источнику постоянного напряжения, и причем второй проводящий контактный вывод выходного транзистора выступает в качестве выходного контактного вывода модульной схемы в конечном каскаде.

Возбуждающая схема дисплейной панели настоящего изобретения может быть выполнена таким образом, что модульная схема конечного каскада дополнительно включает в себя транзистор подачи электрического потенциала, причем транзистор подачи электрического потенциала имеет управляющий контактный вывод, первый проводящий контактный вывод и второй проводящий контактный вывод, при этом транзистор подачи электрического потенциала принимает сигнал очистки через управляющий контактный вывод, при этом первый проводящий контактный вывод транзистора подачи электрического потенциала подключается ко второму проводящему контактному выводу выходного транзистора, а второй проводящий контактный вывод транзистора подачи электрического потенциала подключается к источнику постоянного напряжения.

Сдвиговый регистр настоящего изобретения - это сдвиговый регистр, предусмотренный в возбуждающей схеме дисплейной панели, причем сдвиговый регистр состоит из модульных схем, подключенных каскадно, при этом модульные схемы формируют сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом импульсы выводятся последовательно из соответствующих модульных схем согласно порядковому номеру с началом в первом каскаде до конечного каскада, причем модульная схема в конечном каскаде принимает (i) сигнал выбора сигнальной линии, сформированный в каскаде, отличном от собственного каскада, (ii) синхросигнал и (iii) сигнал очистки, и при этом сигнал очистки становится активным после того, как импульс выводится из конечного каскада, так что сигнал выбора сигнальной линии, выводимый из конечного каскада, остается неактивным.

Способ настоящего изобретения для возбуждения дисплейного устройства, включающего в себя сдвиговый регистр, состоящий из модульных схем, подключенных каскадно, при этом модульные схемы формируют сигналы выбора сигнальной линии, соответственно, причем каждый из сигналов выбора сигнальной линии становится активным в течение соответствующего определенного периода времени, чтобы формировать соответствующий импульс, при этом сдвиговый регистр выводит импульсы последовательно из соответствующих модульных схем согласно порядковому номеру с началом в первом каскаде до конечного каскада, является способом, включающим в себя: ввод, в модульную схему в конечном каскаде, (i) сигнала выбора сигнальной линии, сформированного в каскаде, отличном от собственного каскада, (ii) синхросигнала и (iii) сигнала очистки; и активацию сигнала очистки после того, как импульс выводится из конечного каскада, так что сигнал выбора сигнальной линии, выводимый из конечного каскада, остается неактивным.

Согласно возбуждающей схеме дисплейной панели настоящего изобретения, после того, как сигнал очистки становится активным вследствие аномальности в сигнале синхронизации, импульс, выводимый из сдвигового регистра, прекращается в дальнейшем. Следовательно, можно предотвращать разупорядочение отображения и подавлять увеличение нагрузки, подаваемой на источник питания.

Кроме того, согласно возбуждающей схеме дисплейной панели настоящего изобретения, можно сбрасывать сдвиговый регистр при помощи сигнала очистки в конечном каскаде (модульной схеме). Следовательно, фиктивный каскад (фиктивная схема сдвига) не требуется, как в традиционной возбуждающей схеме дисплейной панели, тем самым давая возможность уменьшения площади схемы в сдвиговом регистре.

Краткое описание чертежей

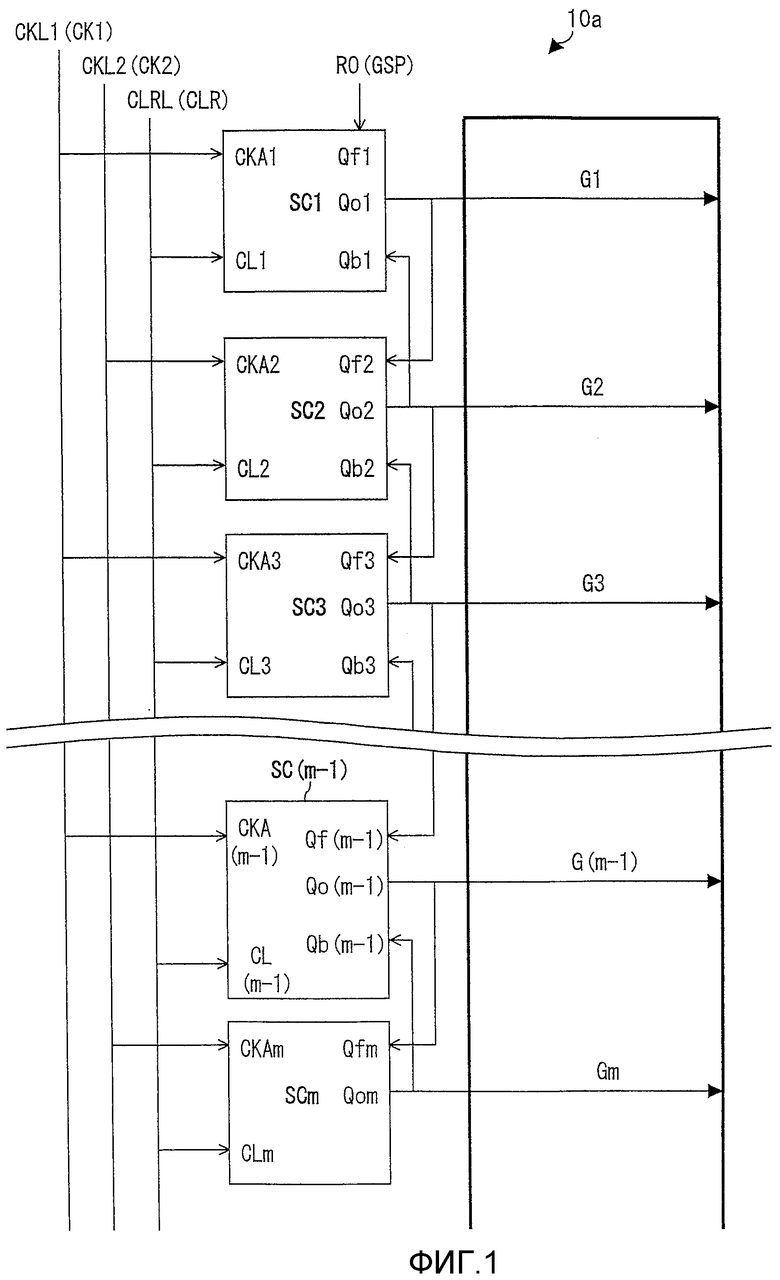

Фиг.1 является блок-схемой, иллюстрирующей конфигурацию настоящего сдвигового регистра.

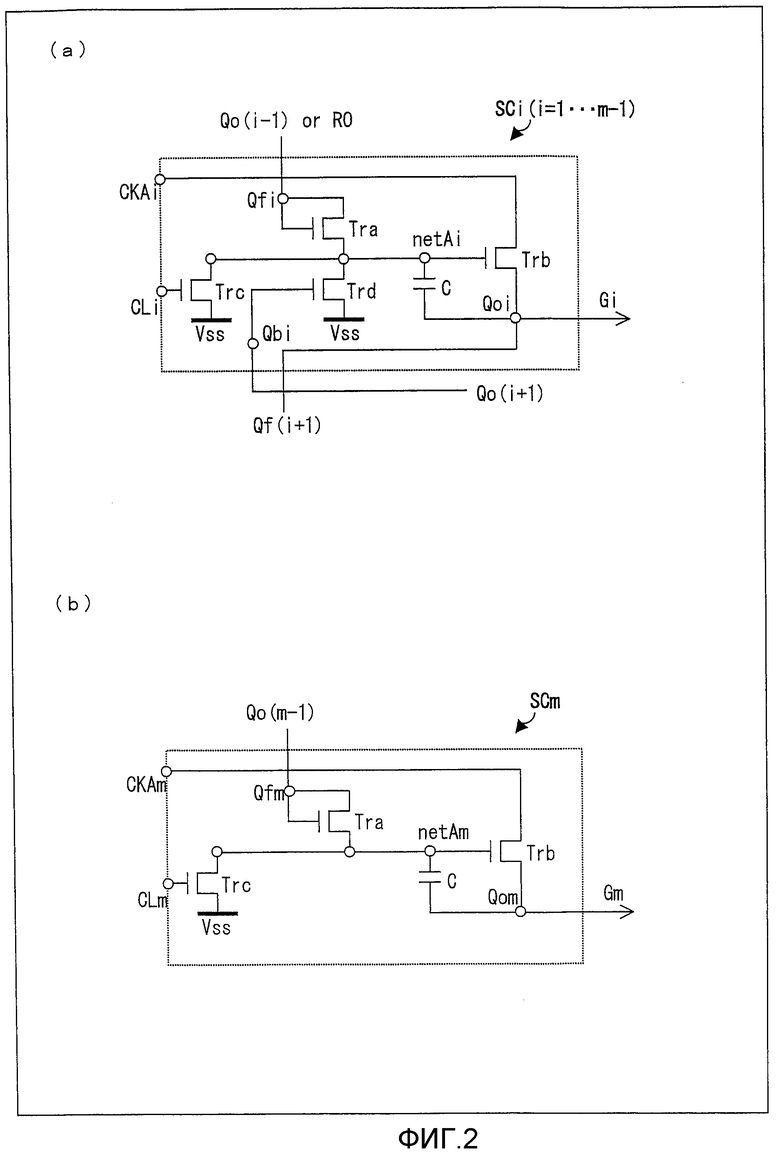

Части (a) и (b) по фиг.2 являются принципиальными схемами, иллюстрирующими конфигурацию модульной схемы сдвигового регистра.

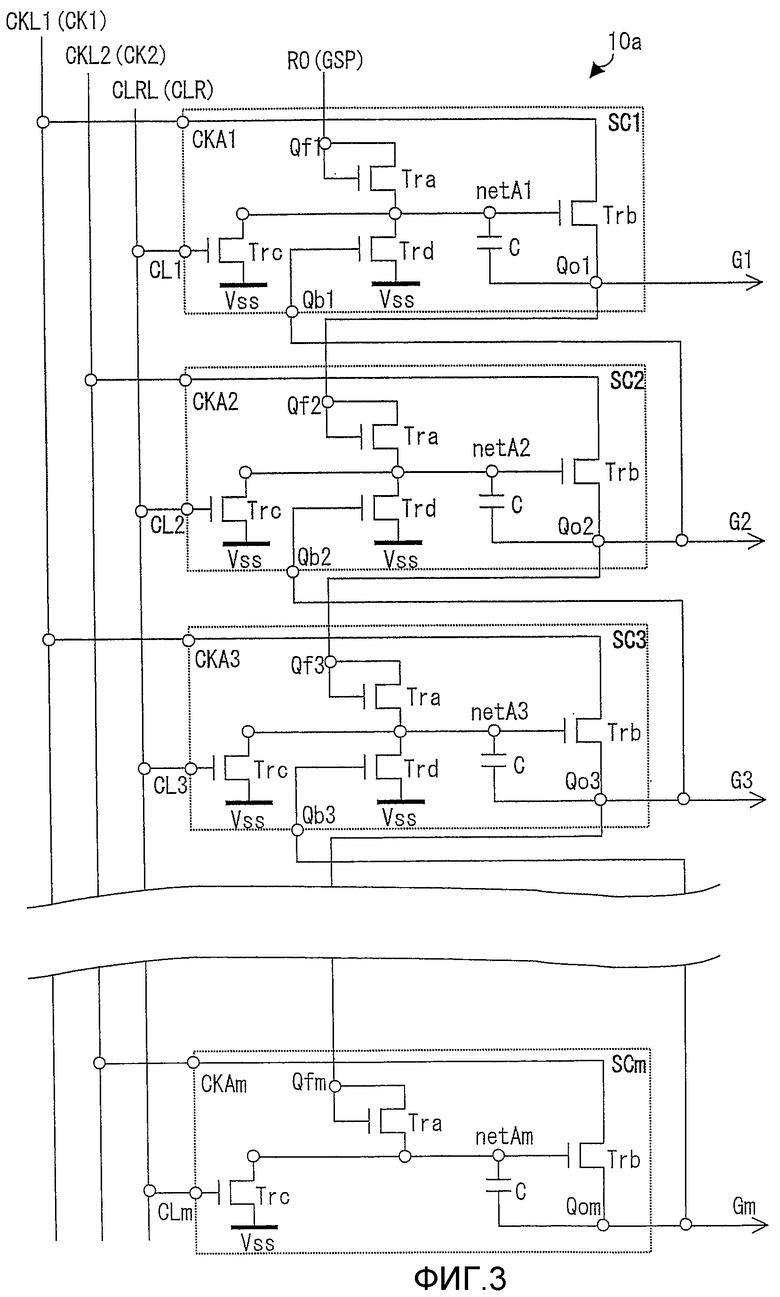

Фиг.3 является принципиальной схемой, иллюстрирующей конфигурацию настоящего сдвигового регистра.

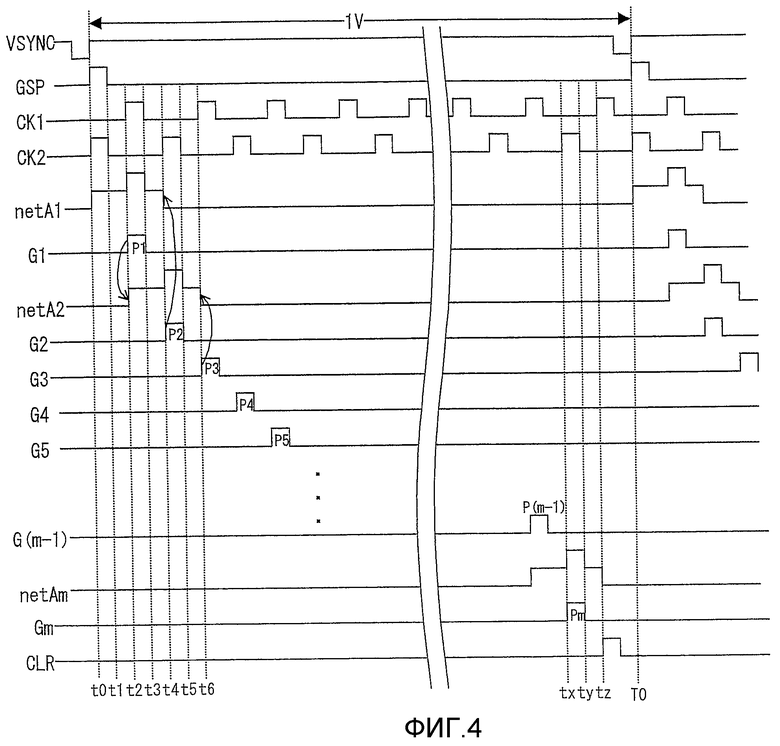

Фиг.4 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.3.

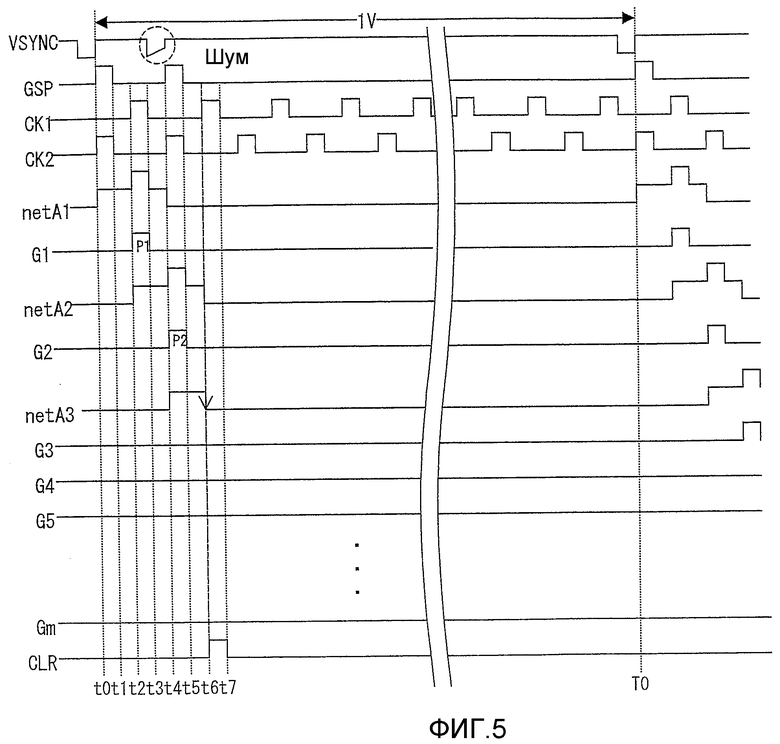

Фиг.5 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.3.

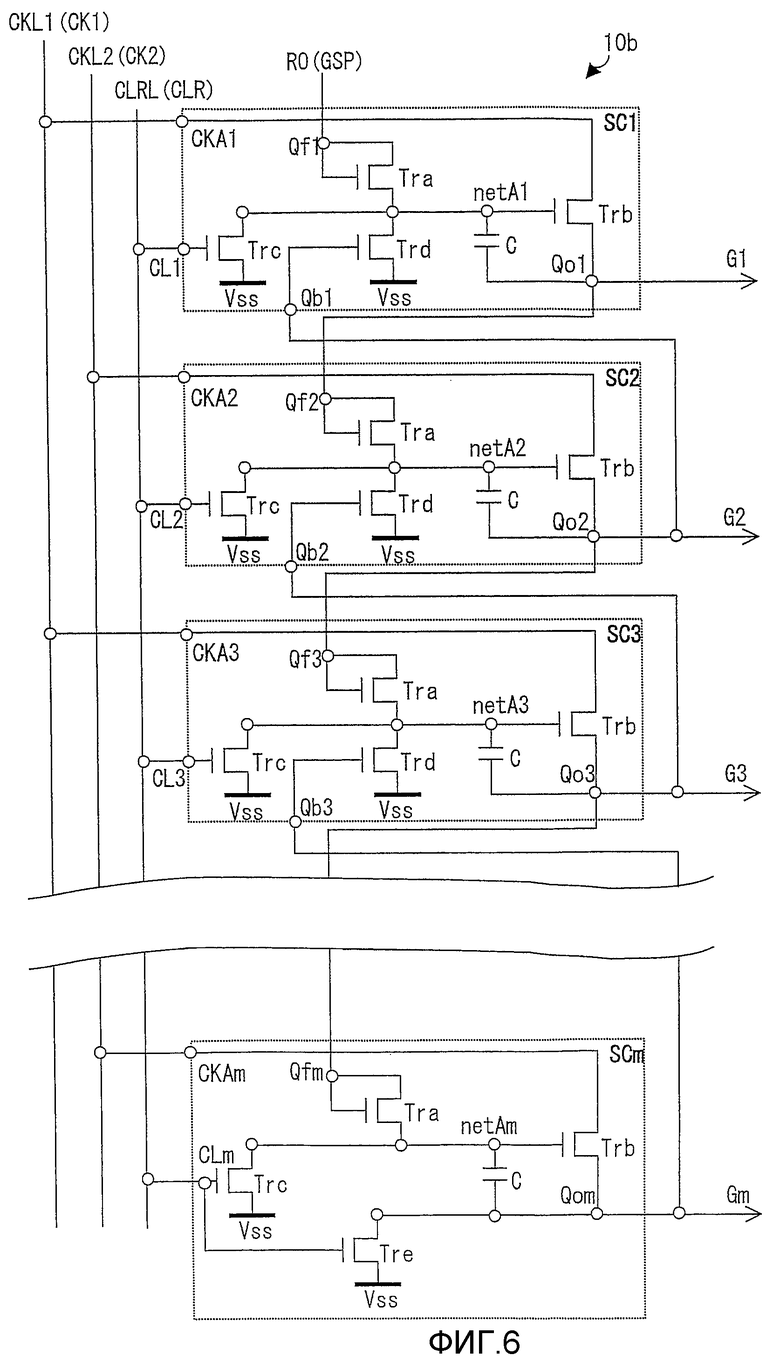

Фиг.6 является принципиальной схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

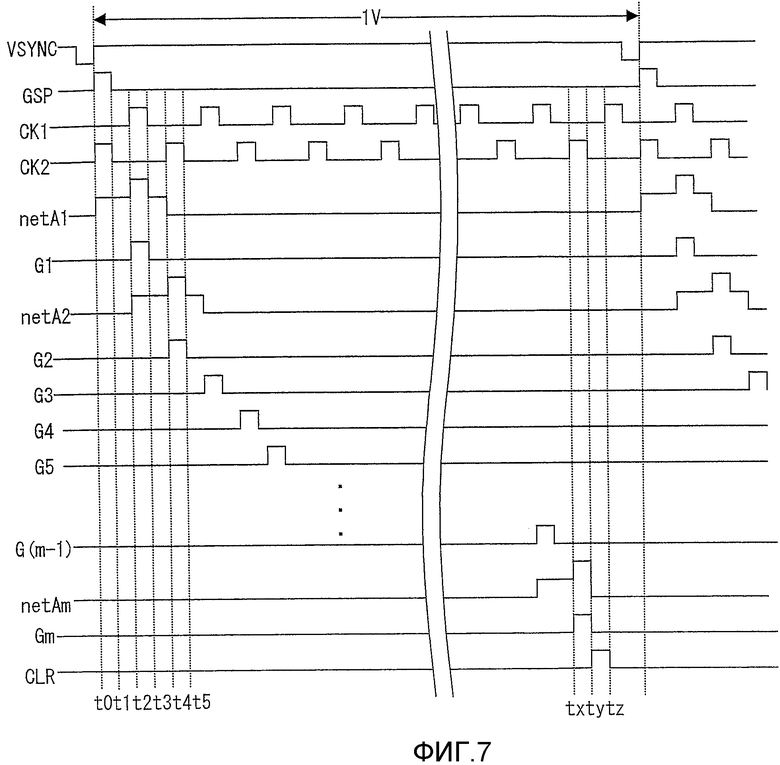

Фиг.7 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.6.

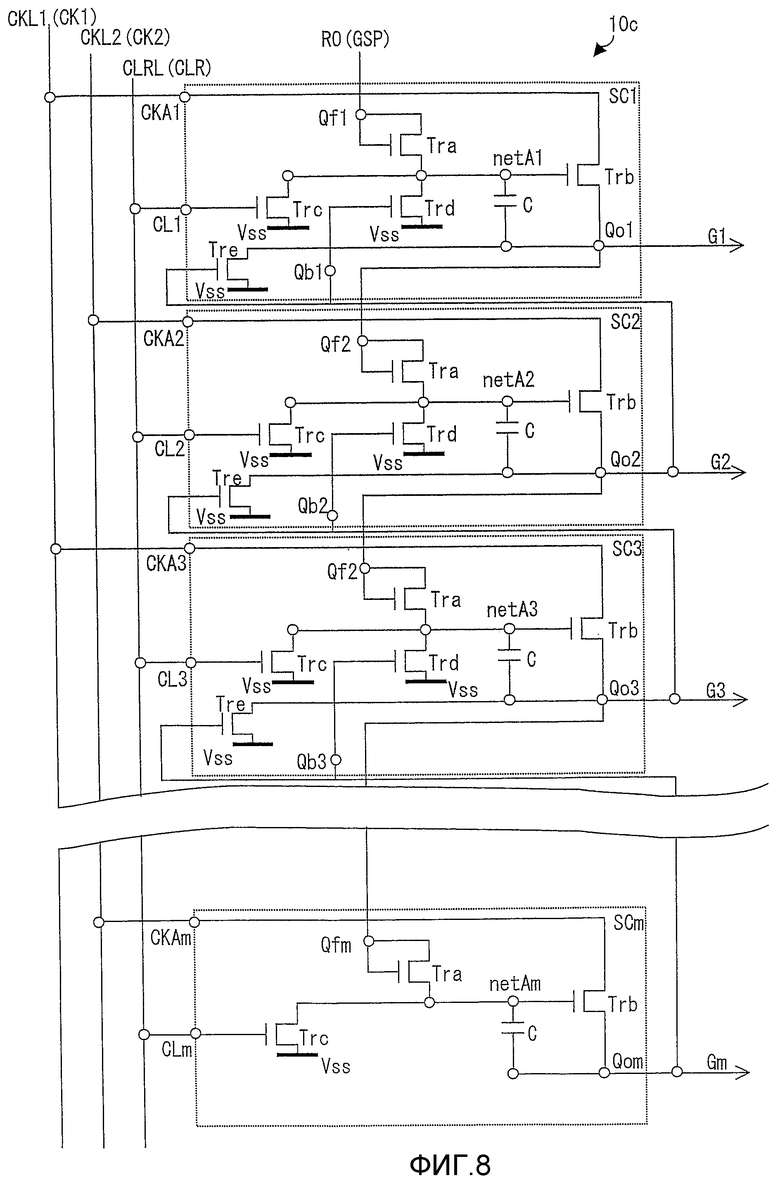

Фиг.8 является принципиальной схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

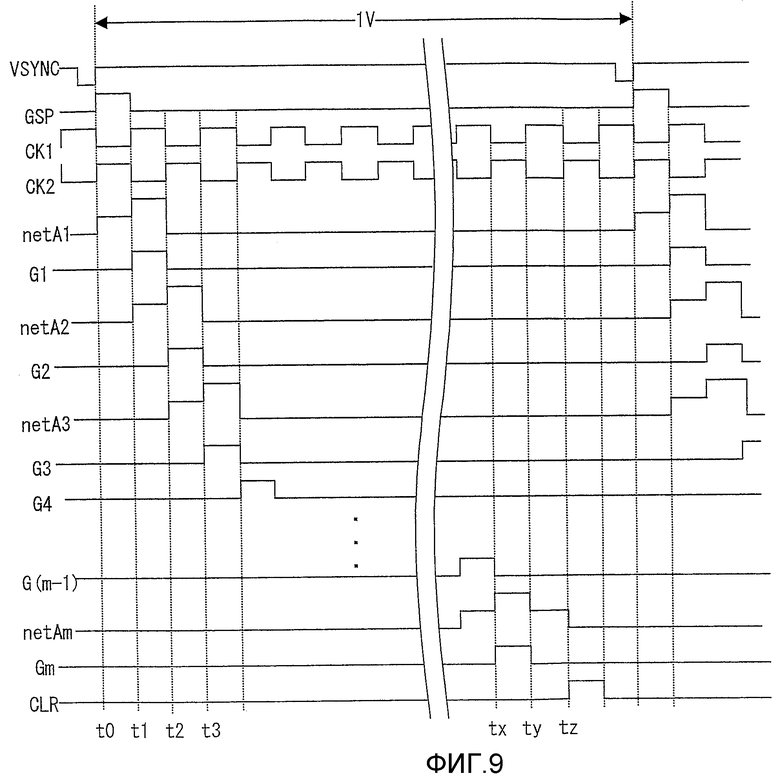

Фиг.9 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.8.

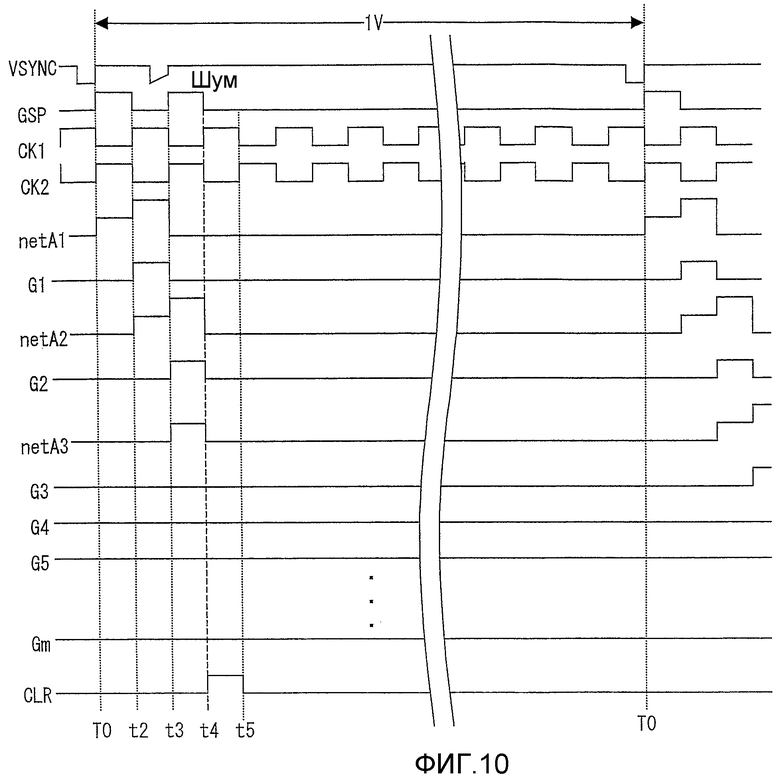

Фиг.10 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.8.

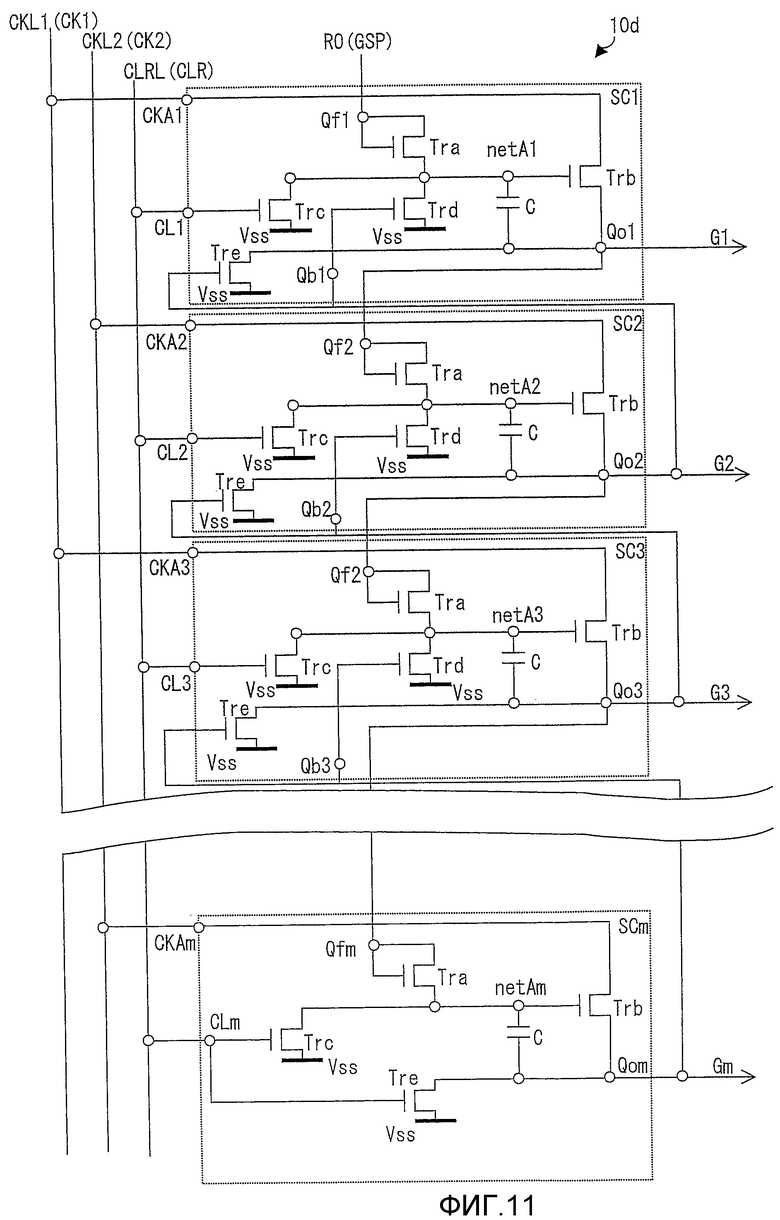

Фиг.11 является принципиальной схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

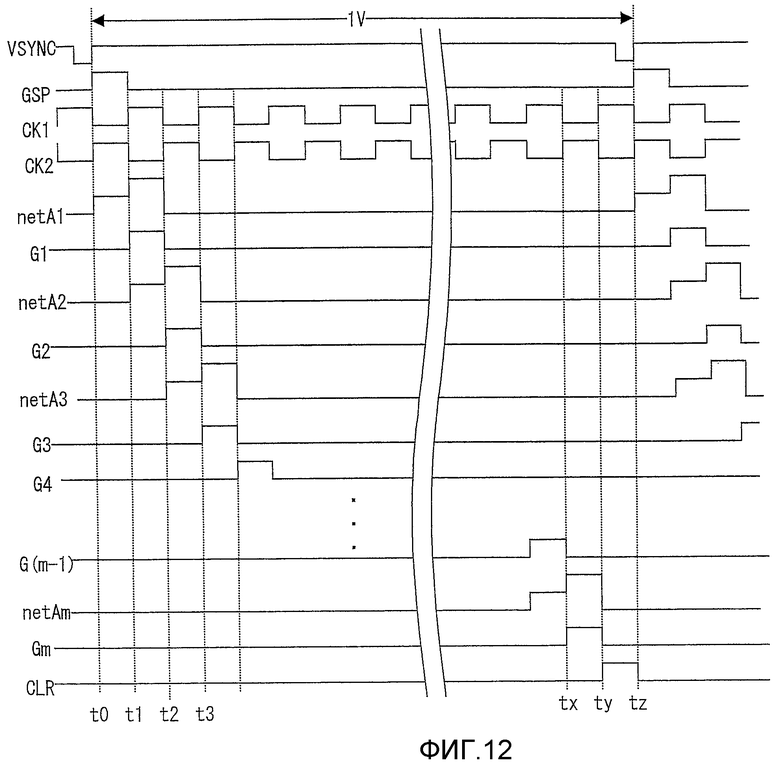

Фиг.12 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.11.

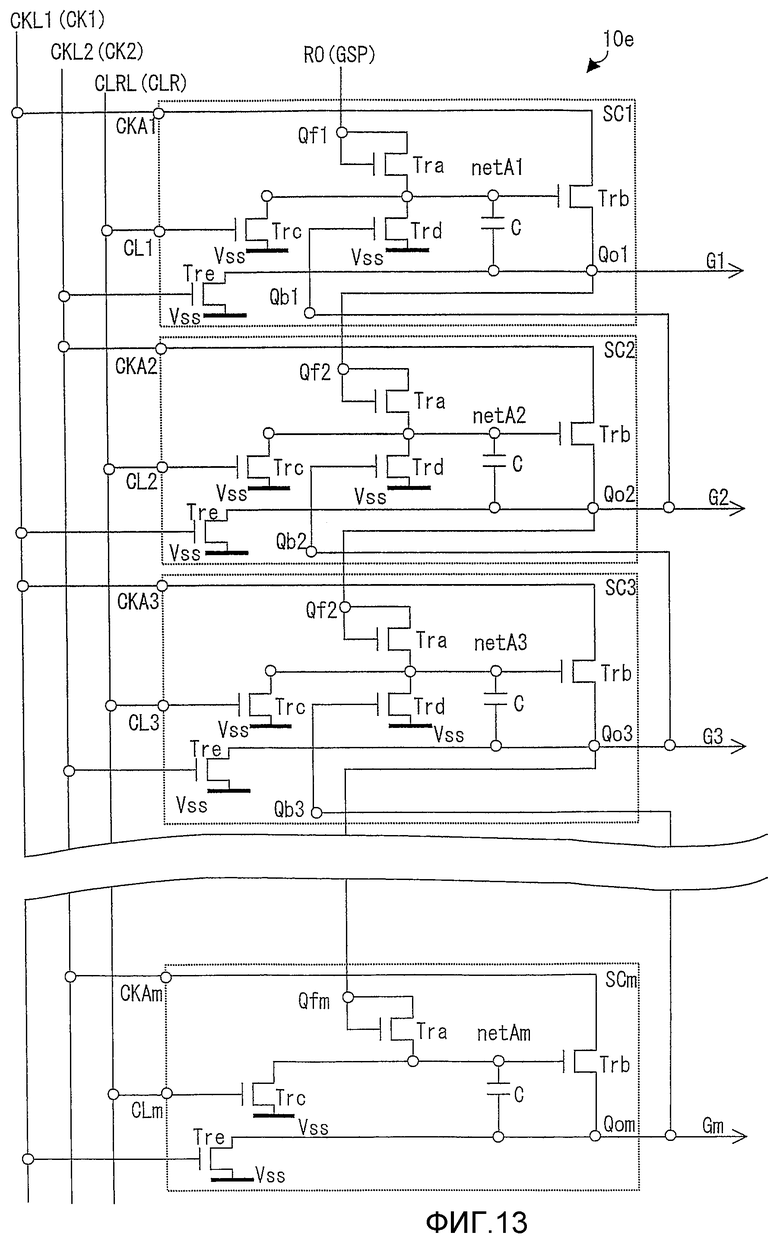

Фиг.13 является принципиальной схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

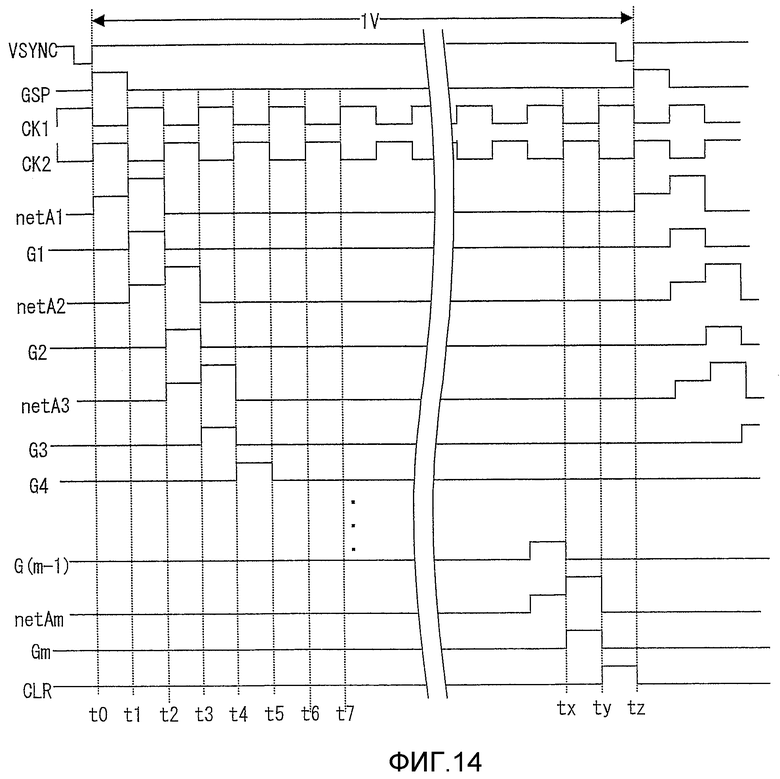

Фиг.14 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.13.

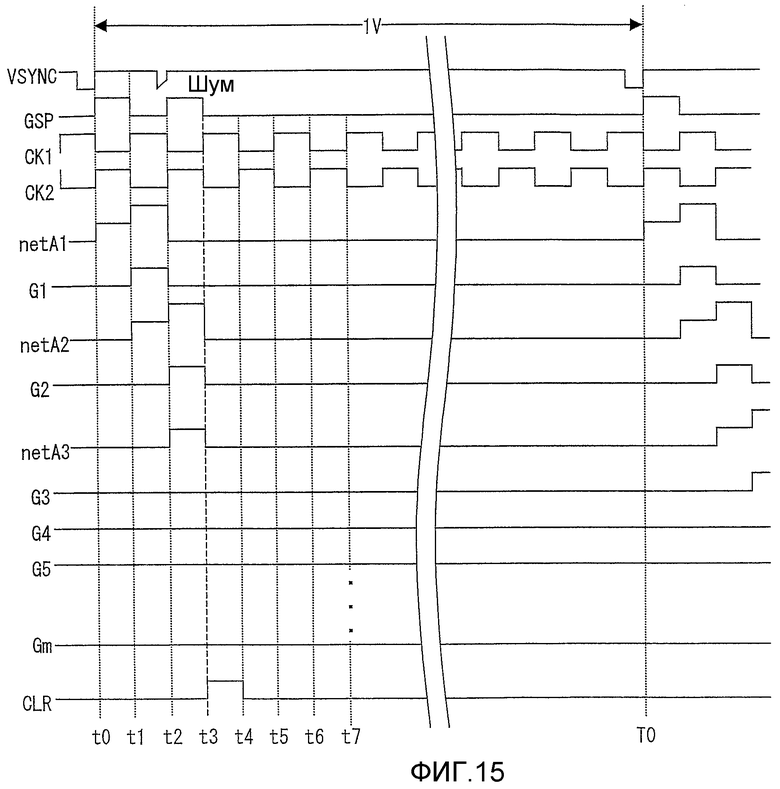

Фиг.15 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.13.

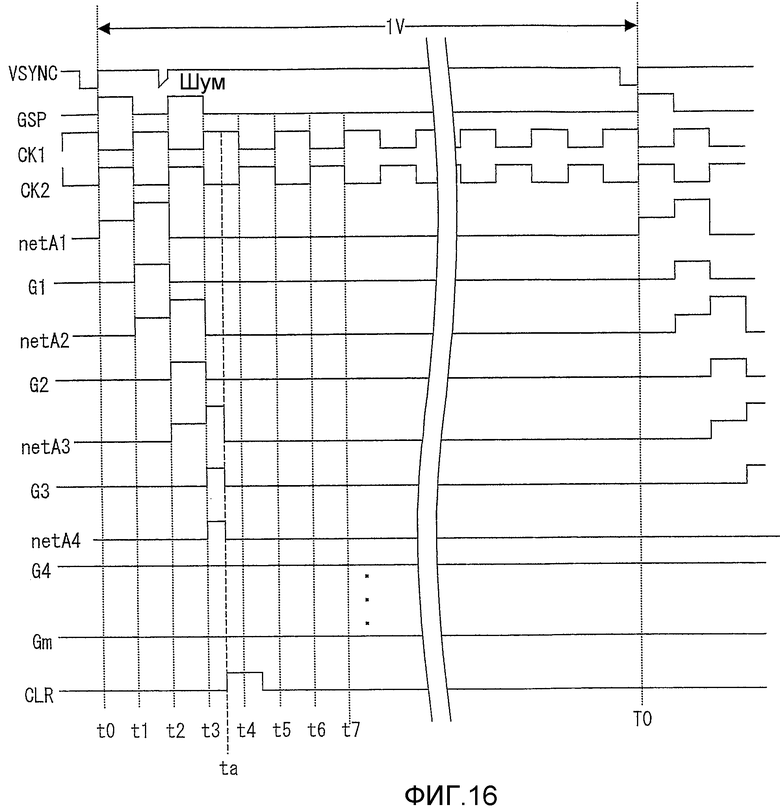

Фиг.16 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.13.

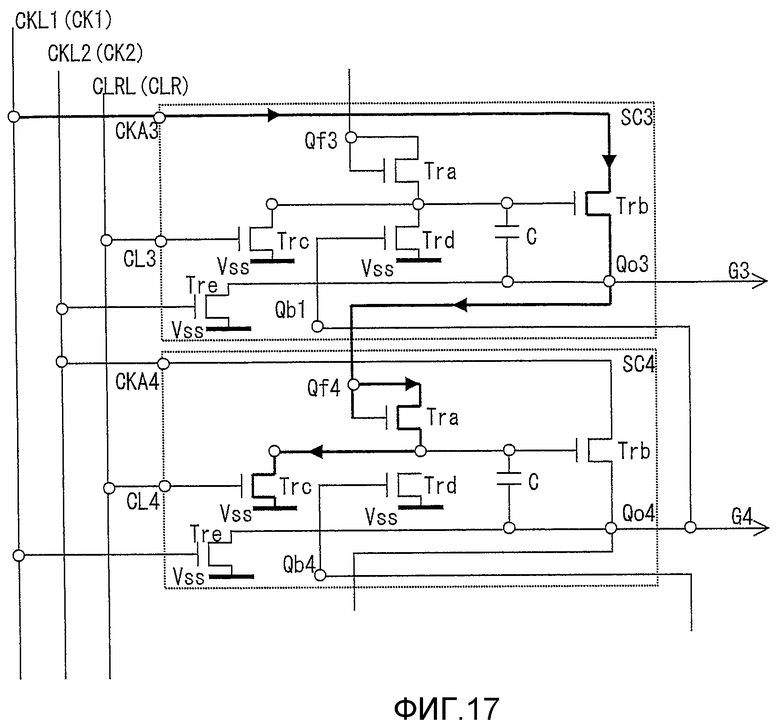

Фиг.17 является принципиальной схемой, иллюстрирующей сквозной ток.

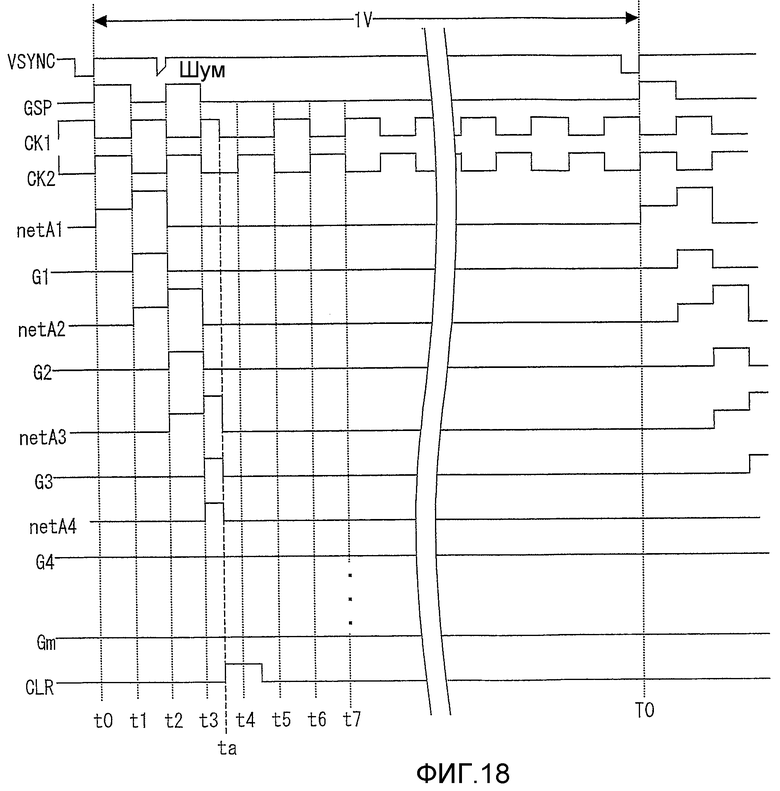

Фиг.18 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.13.

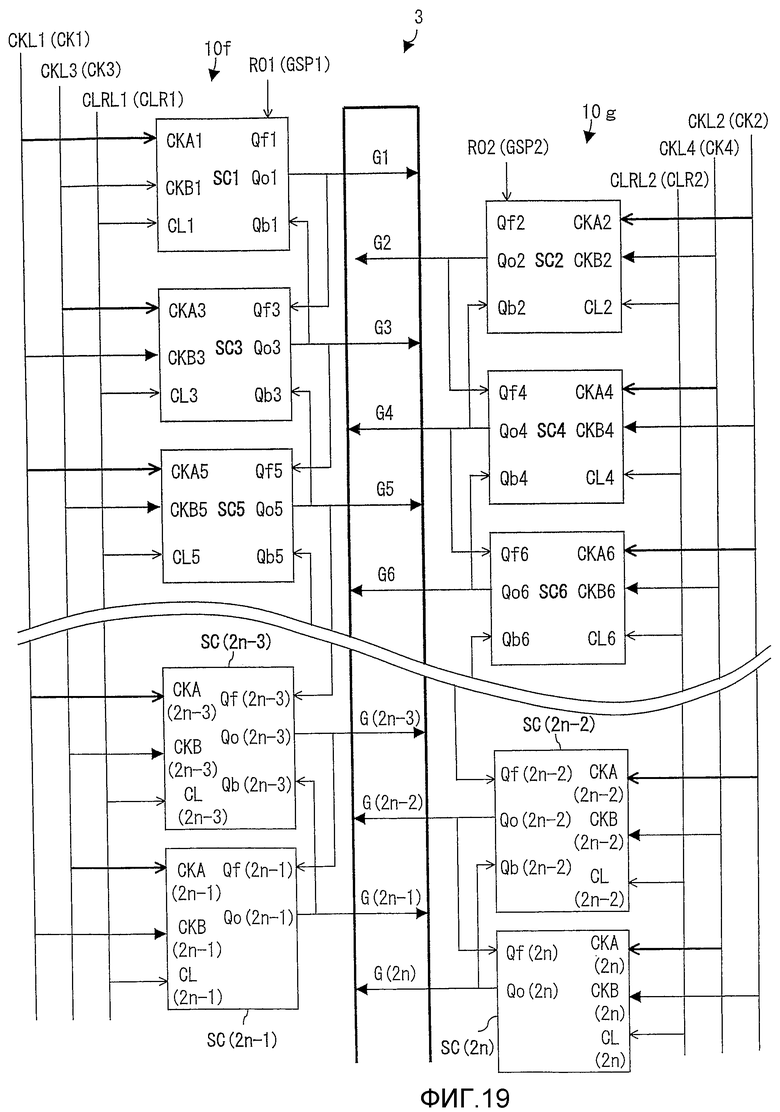

Фиг.19 является блок-схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

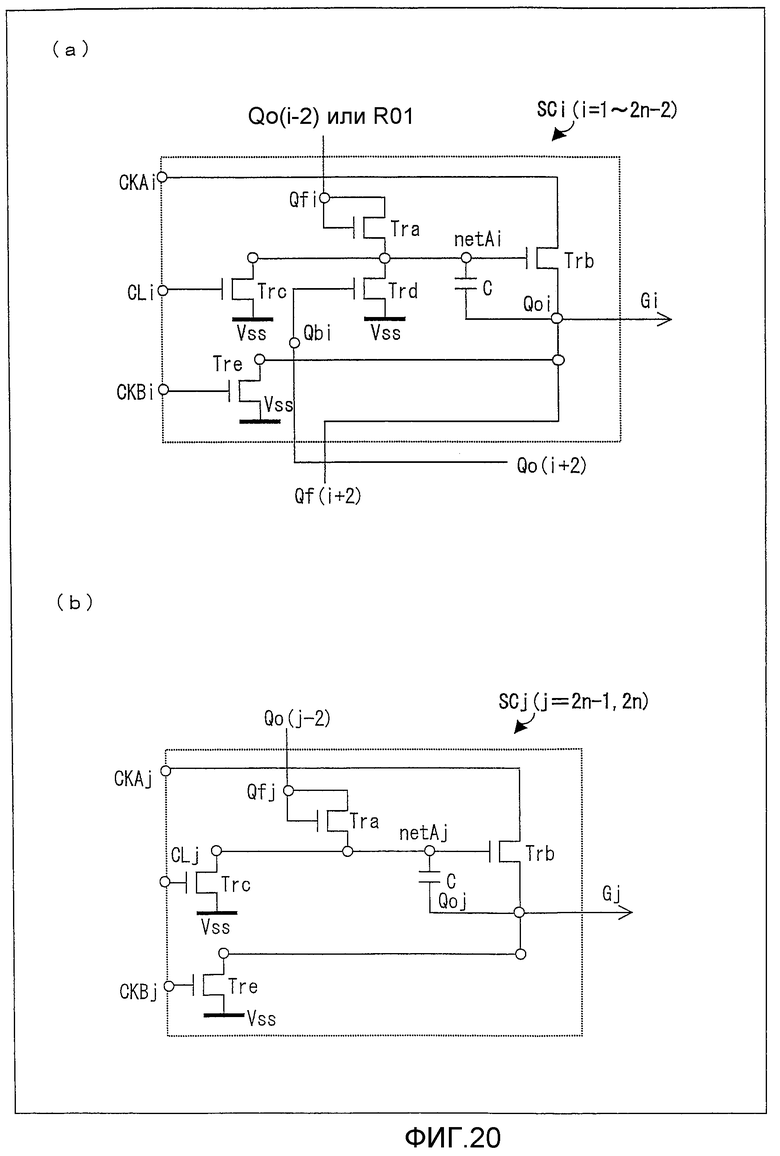

Части (a) и (b) по фиг.20 являются принципиальными схемами, иллюстрирующими конфигурацию модульной схемы настоящего сдвигового регистра.

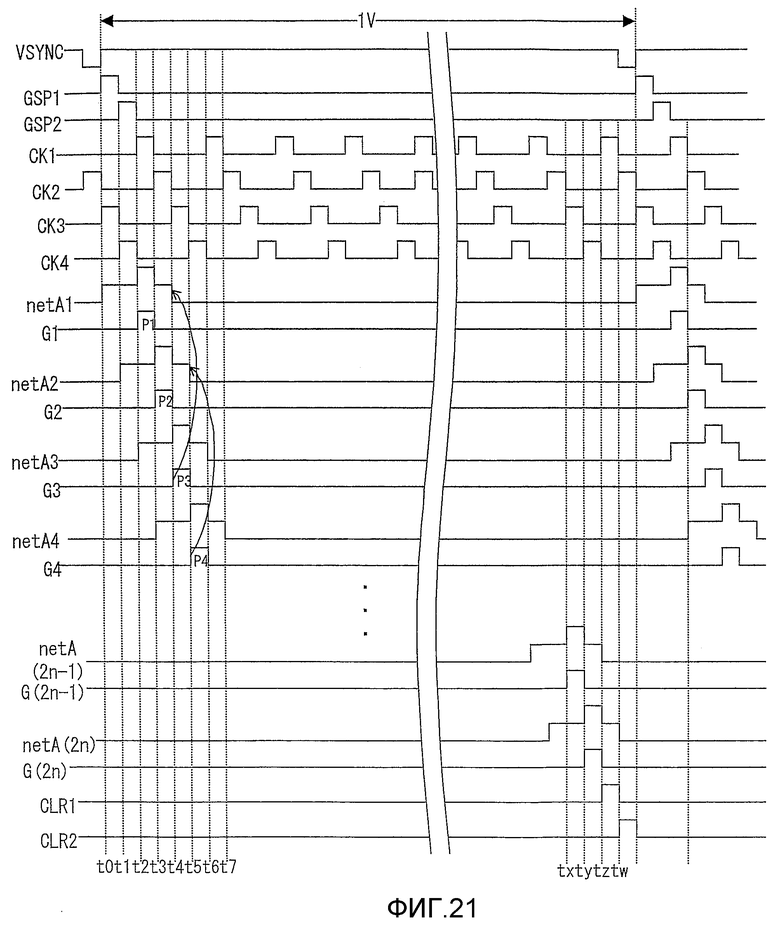

Фиг.21 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.19.

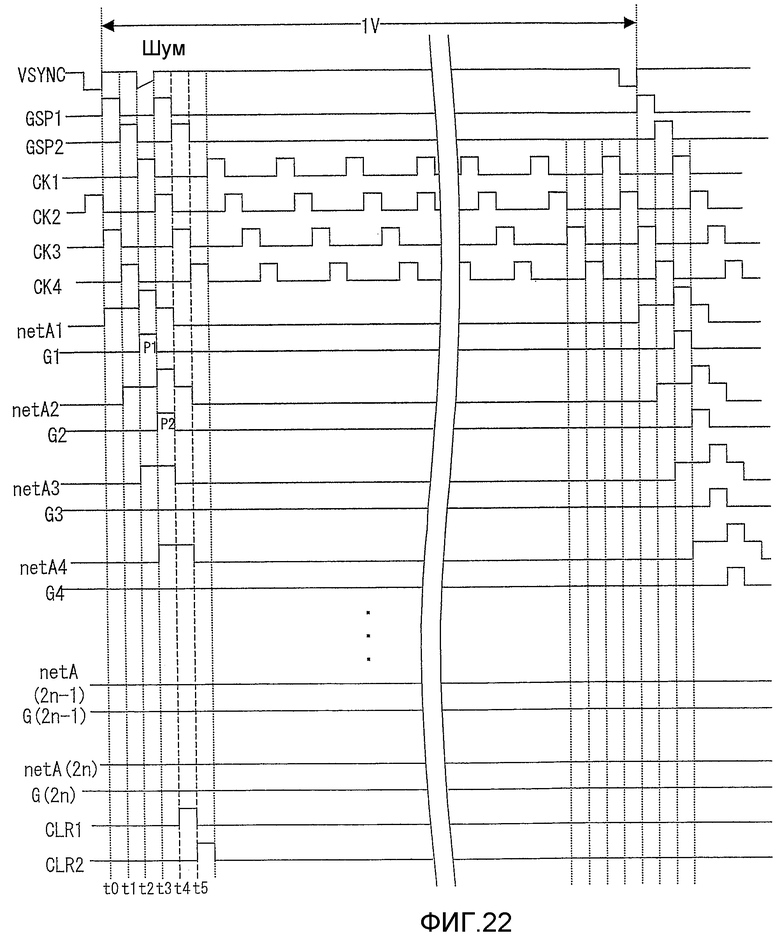

Фиг.22 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации включает в себя аномальность) сдвигового регистра, показанного на фиг.19.

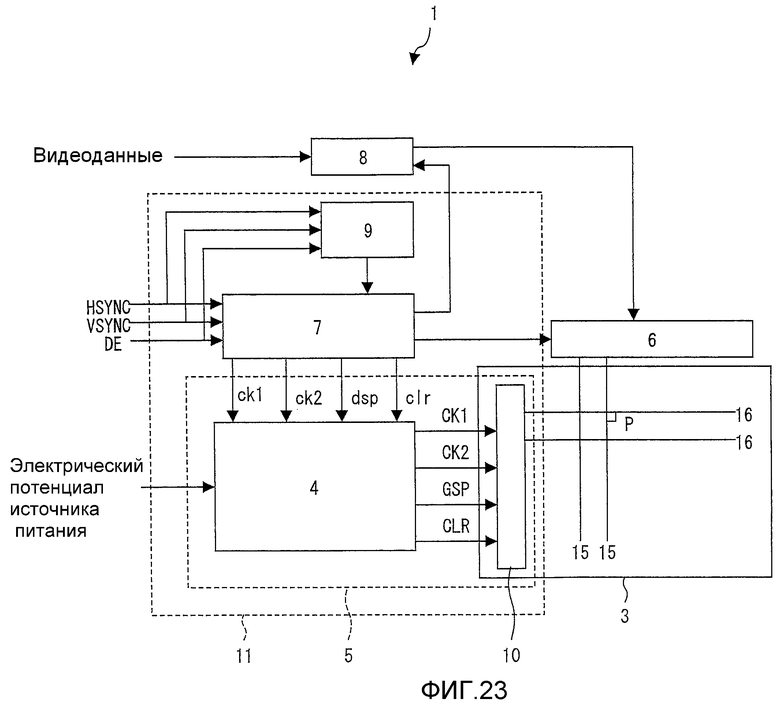

Фиг.23 является блок-схемой, иллюстрирующей конфигурацию жидкокристаллического дисплейного устройства вариантов осуществления 1 и 2.

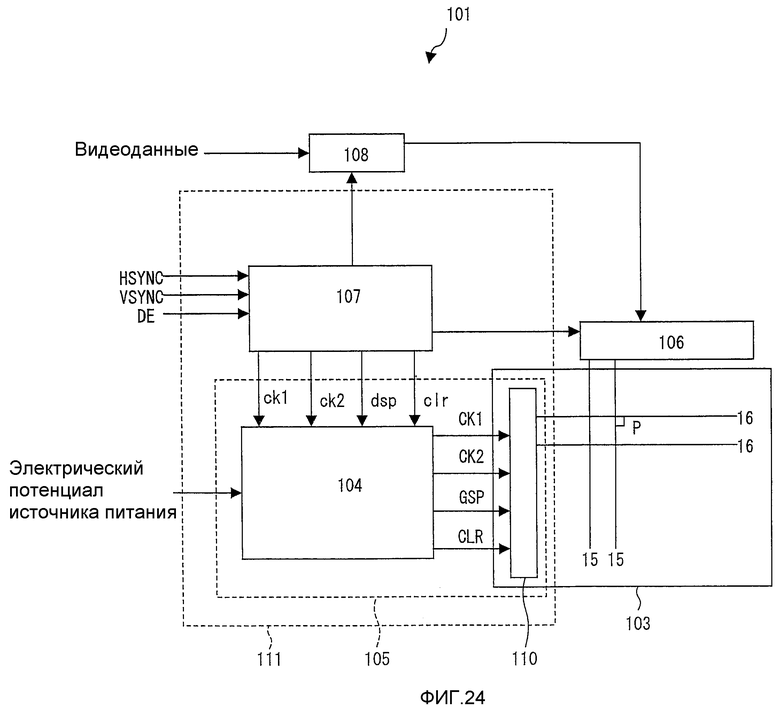

Фиг.24 является блок-схемой, иллюстрирующей конфигурацию жидкокристаллического дисплейного устройства вариантов осуществления 3 и 4.

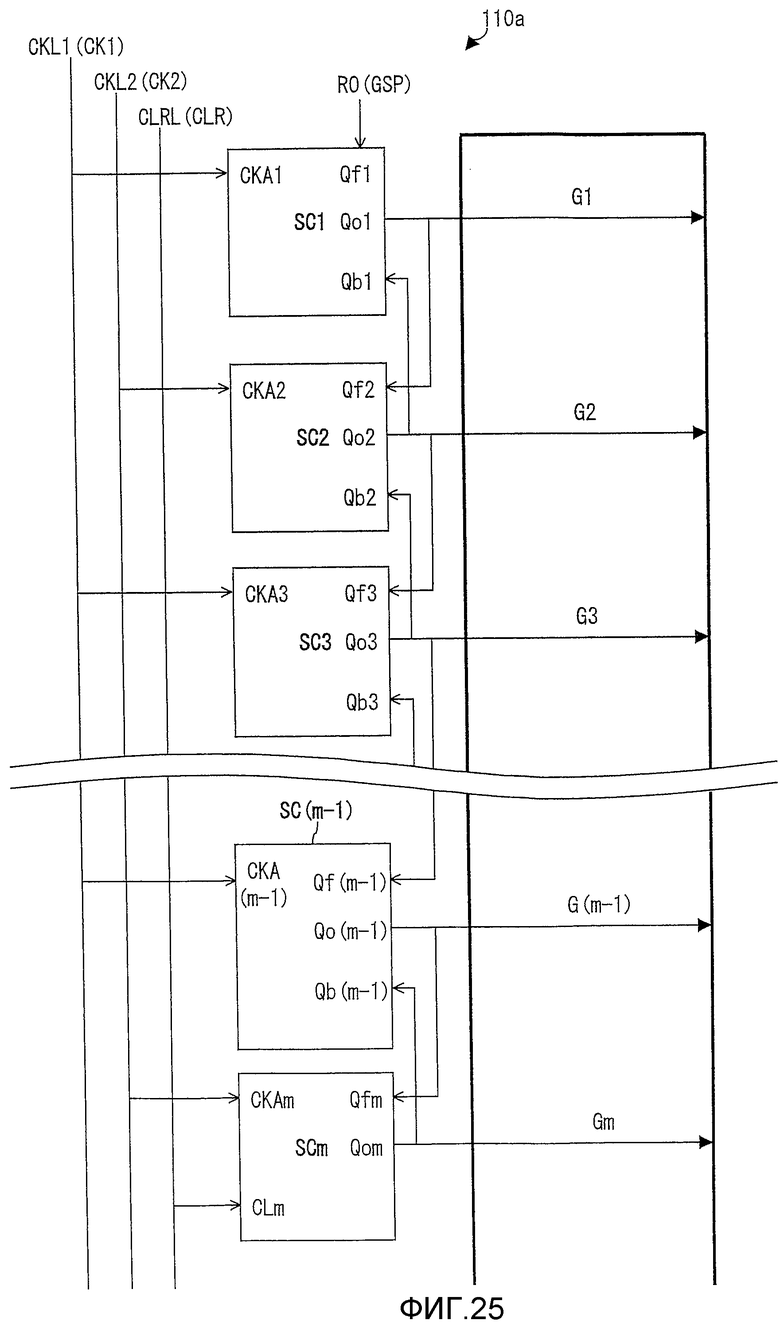

Фиг.25 является блок-схемой, иллюстрирующей конфигурацию сдвигового регистра варианта осуществления 3.

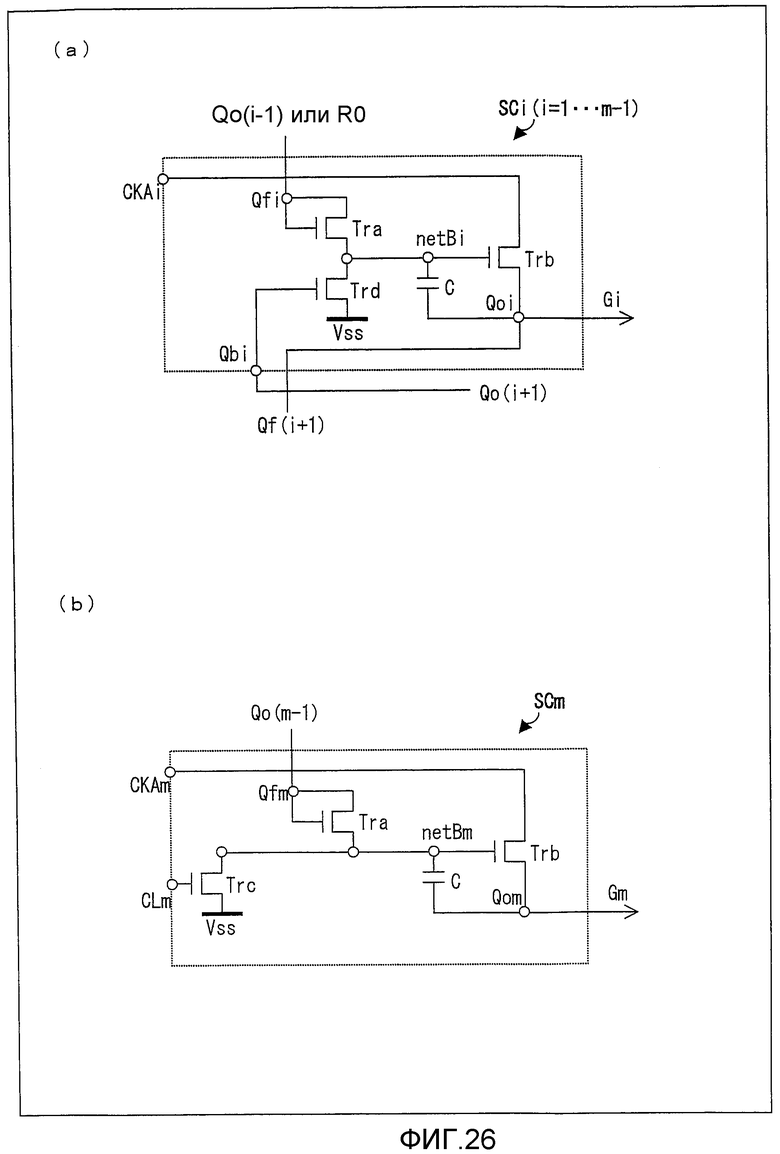

Части (a) и (b) по фиг.26 являются принципиальными схемами, иллюстрирующими конфигурацию модульной схемы сдвигового регистра варианта осуществления 3.

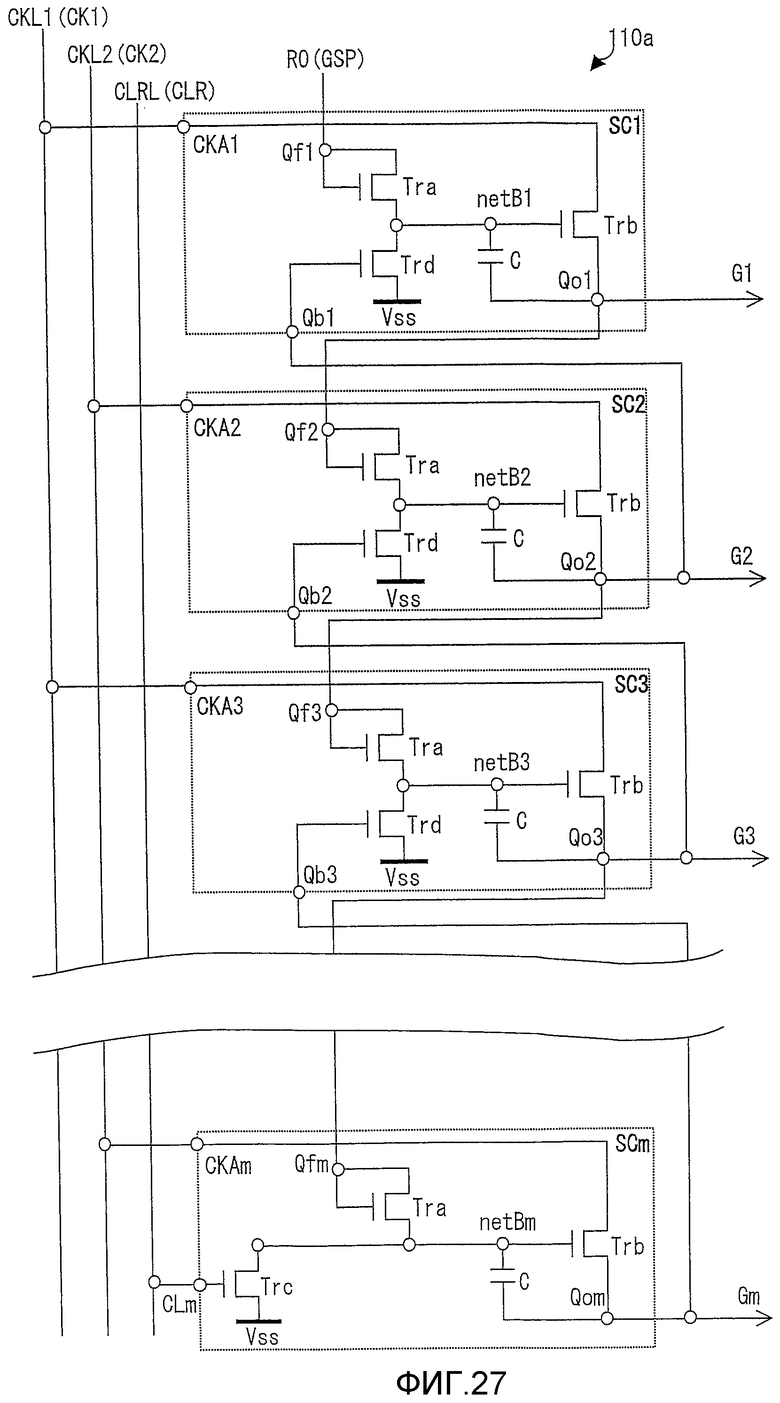

Фиг.27 является принципиальной схемой, иллюстрирующей конфигурацию сдвигового регистра варианта осуществления 3.

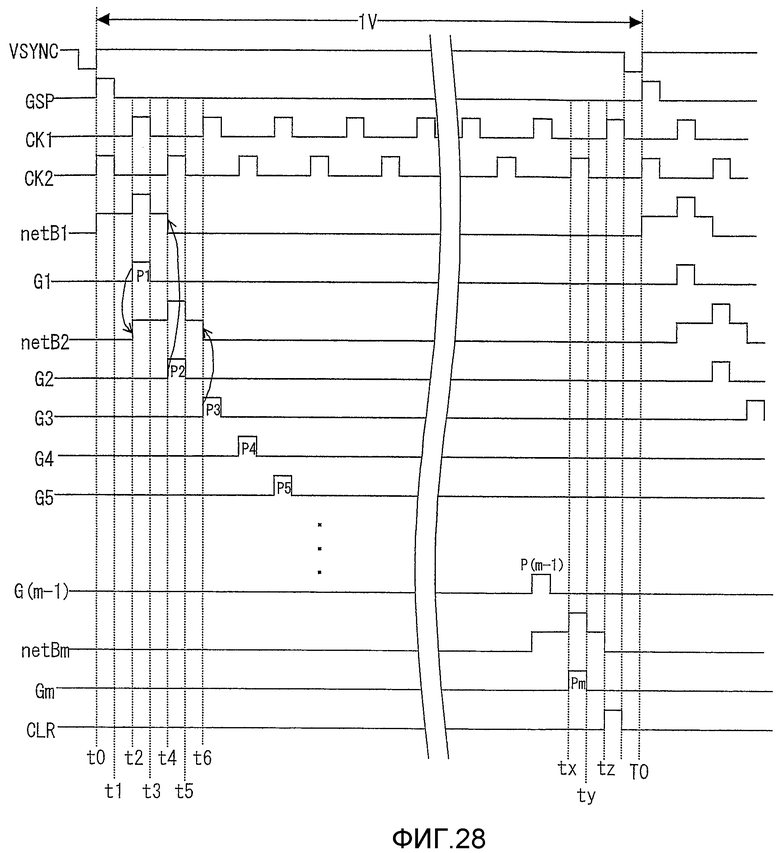

Фиг.28 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.27.

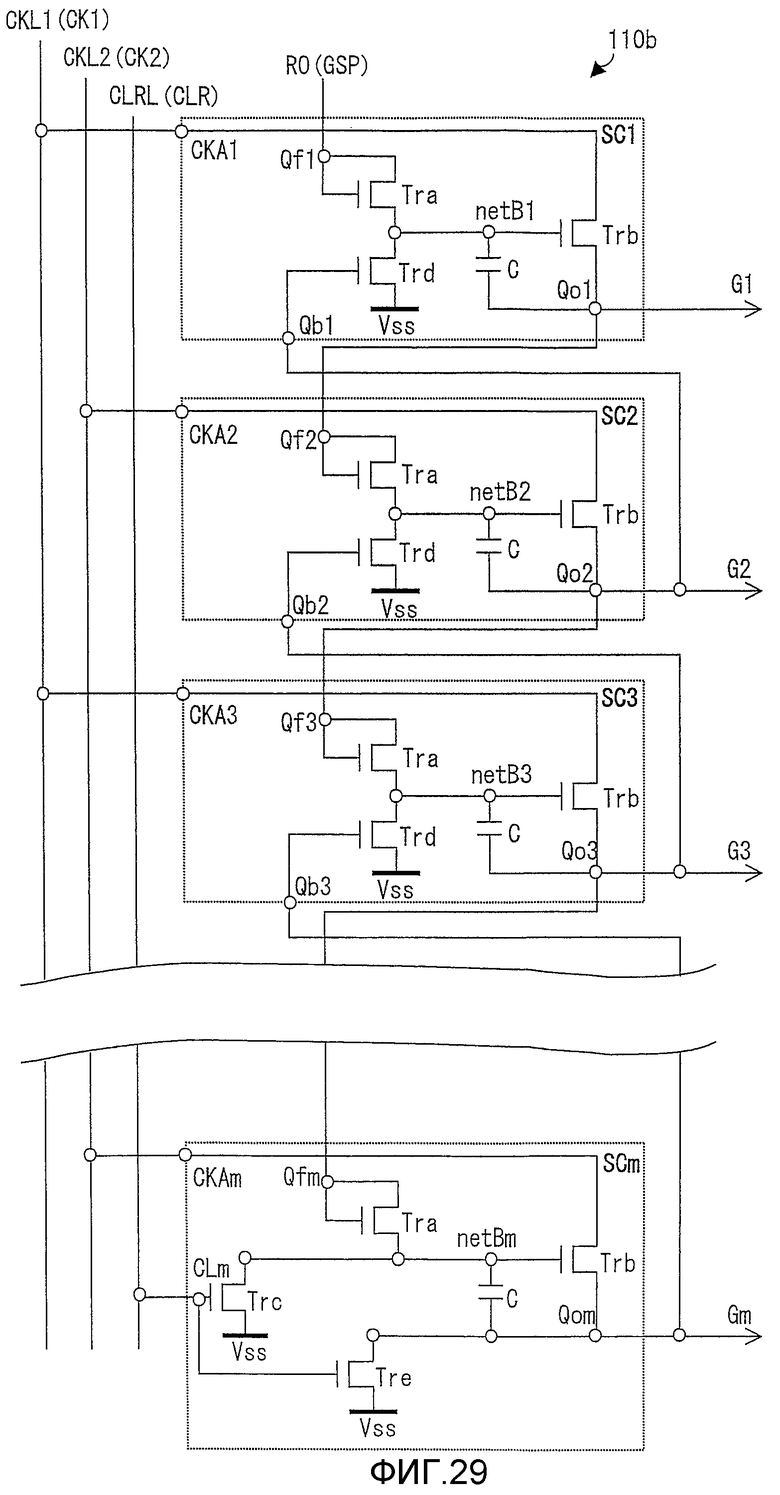

Фиг.29 является принципиальной схемой, иллюстрирующей другую конфигурацию настоящего сдвигового регистра.

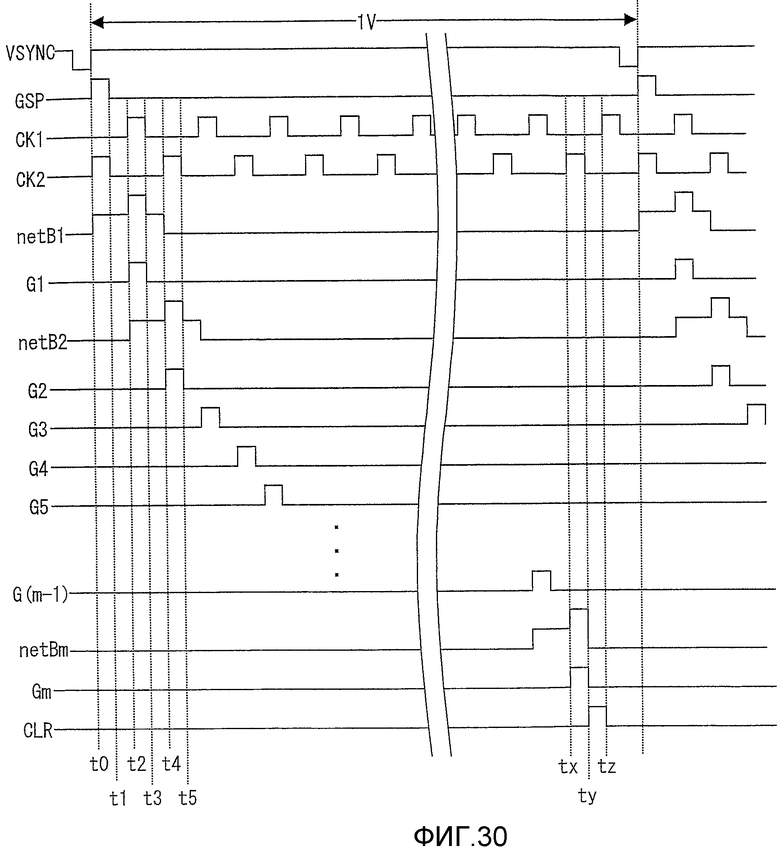

Фиг.30 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.29.

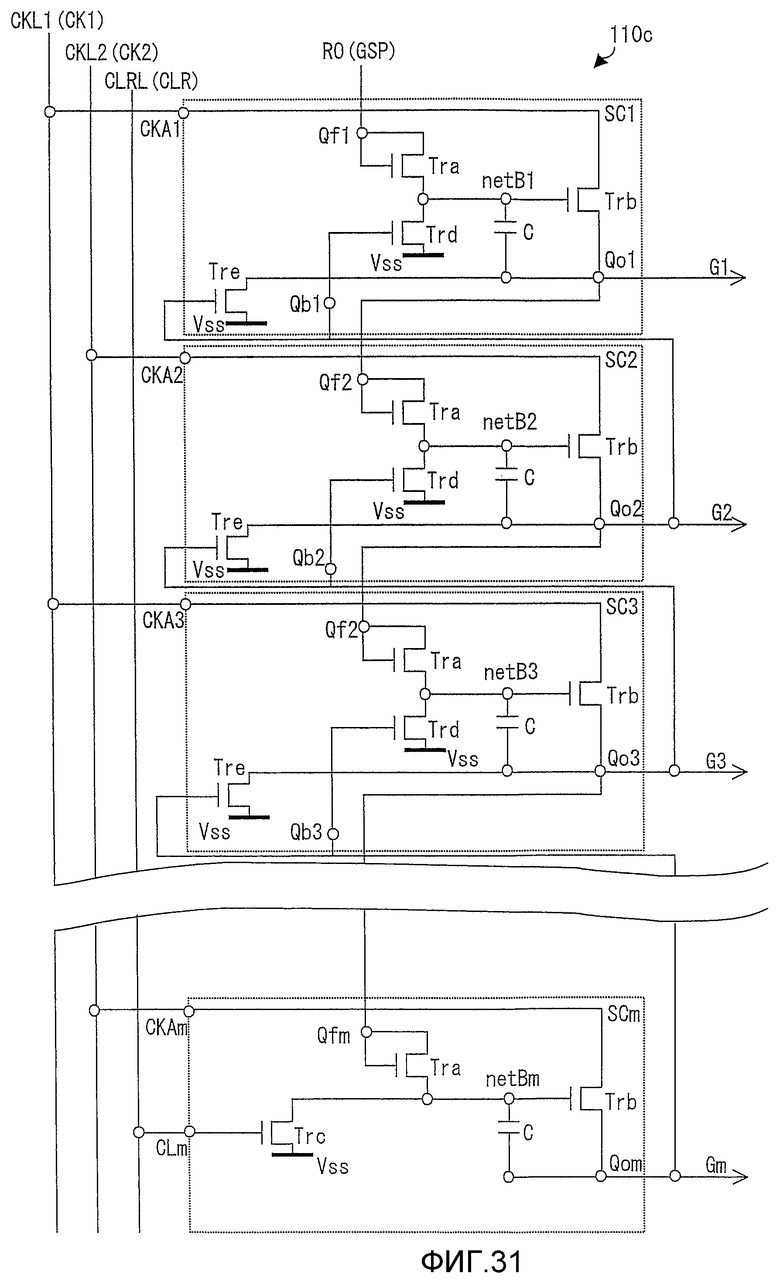

Фиг.31 является принципиальной схемой, иллюстрирующей другую конфигурацию сдвигового регистра варианта осуществления 3.

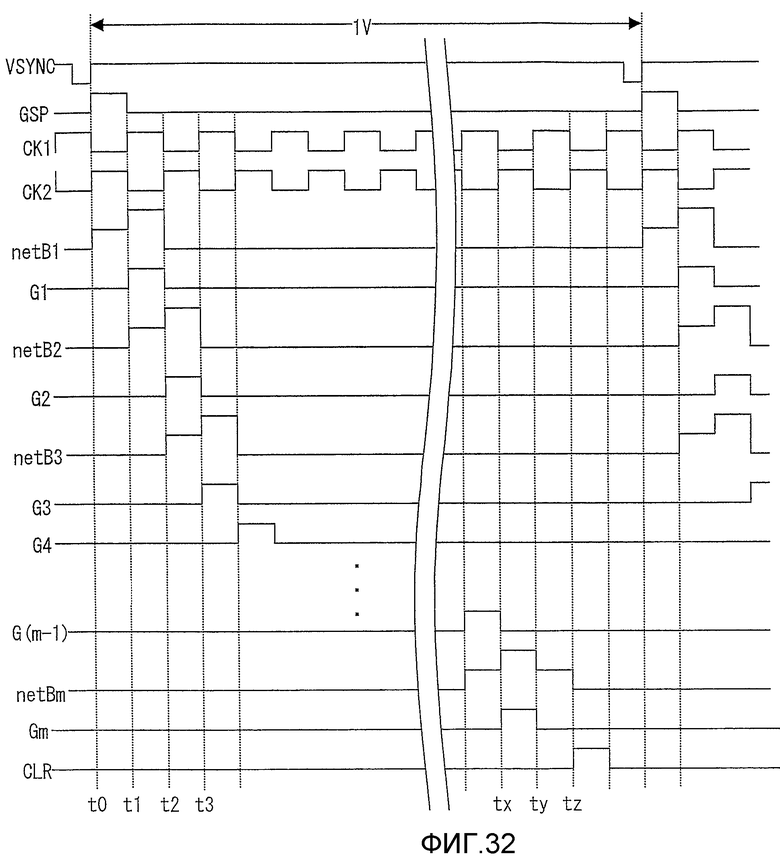

Фиг.32 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.31.

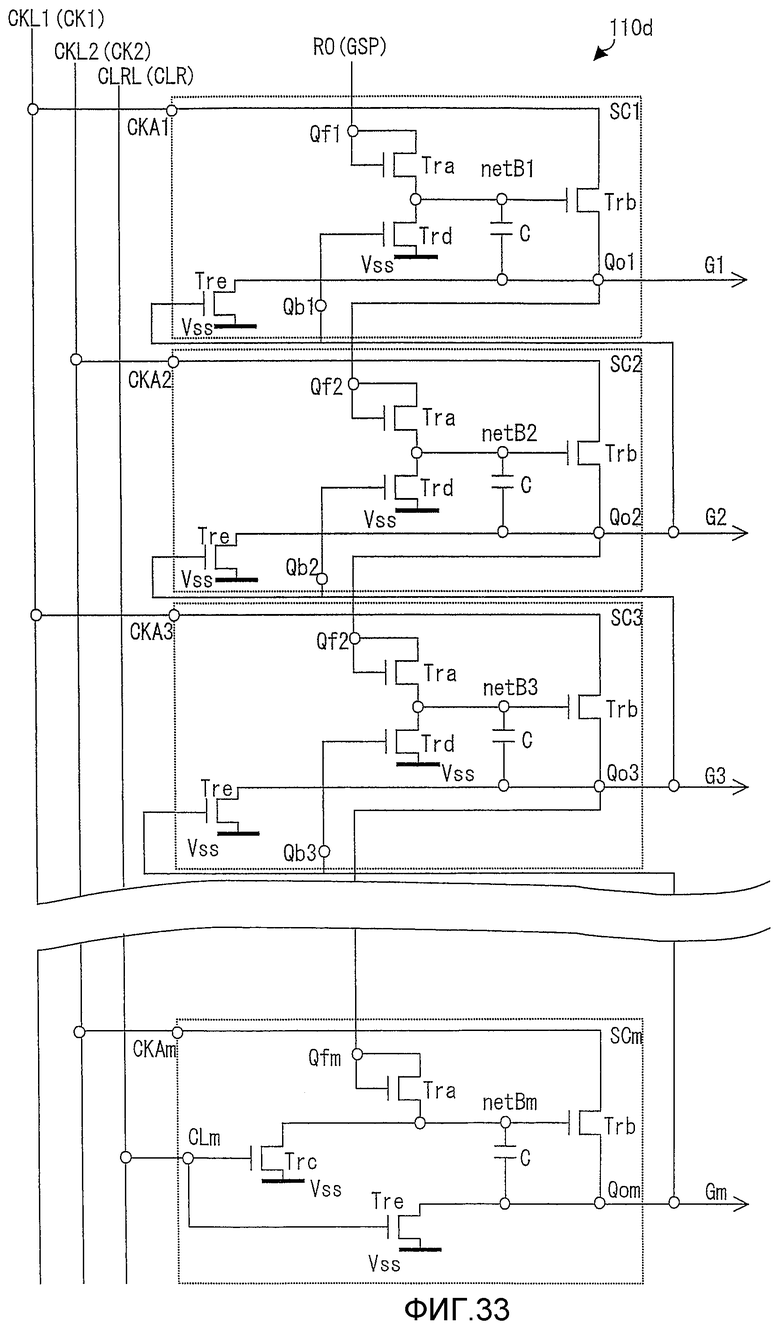

Фиг.33 является принципиальной схемой, иллюстрирующей другую конфигурацию сдвигового регистра варианта осуществления 3.

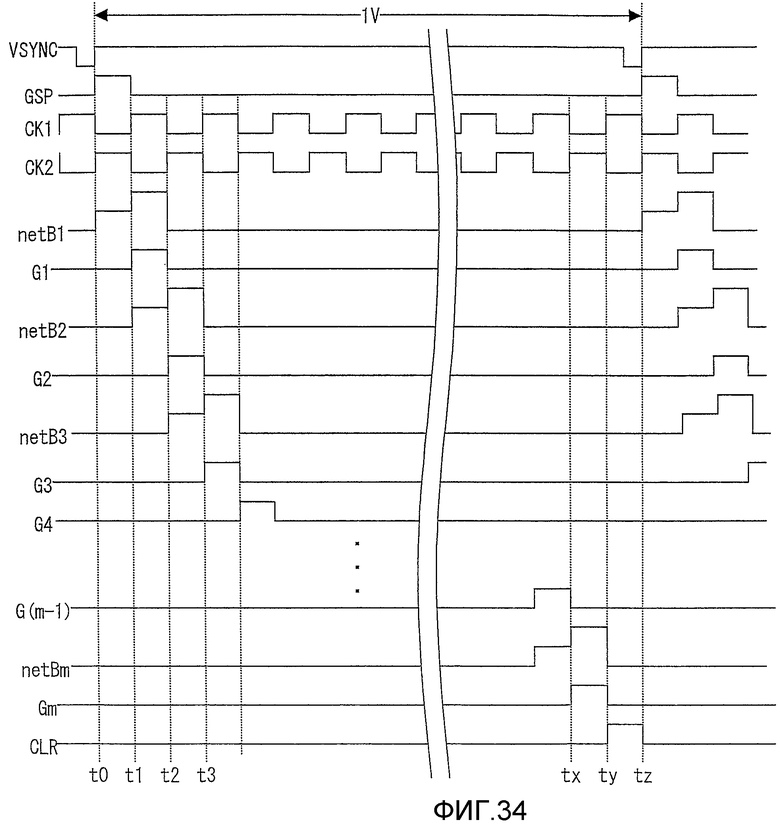

Фиг.34 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.33.

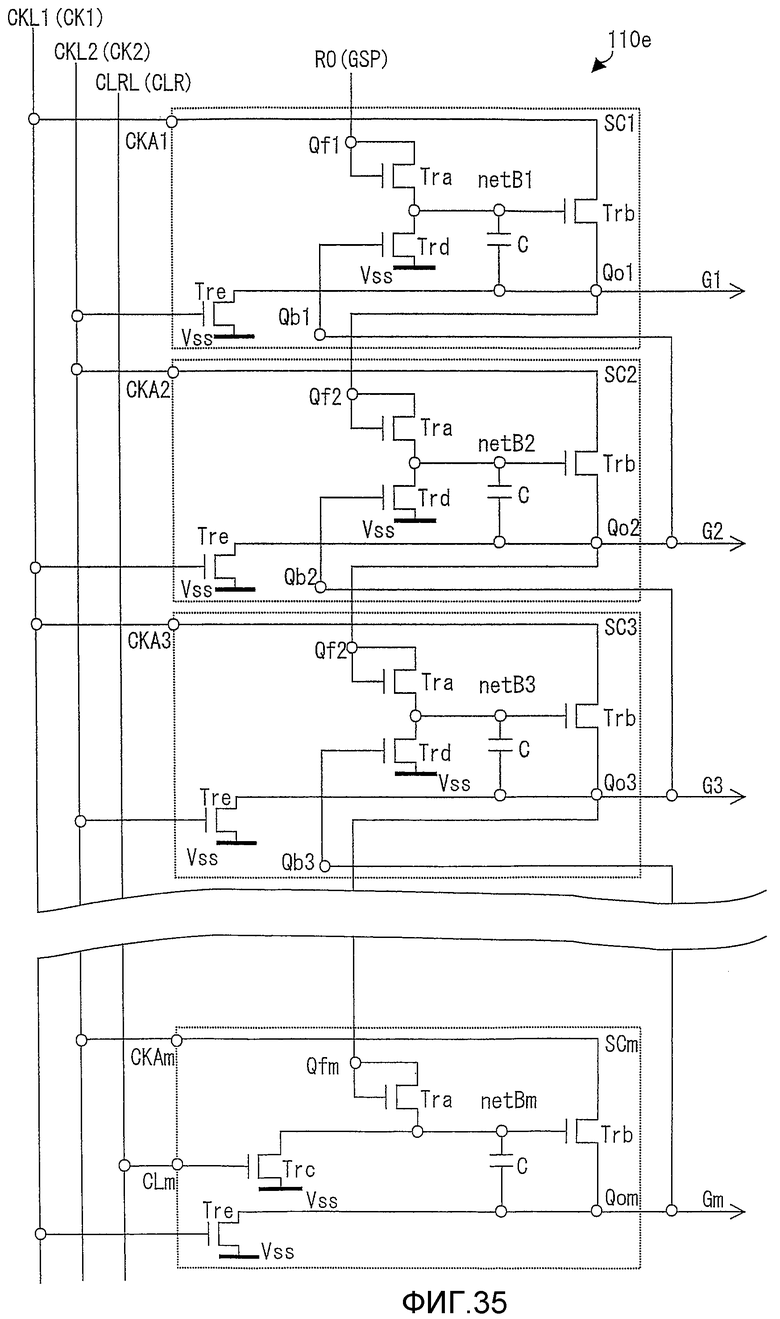

Фиг.35 является принципиальной схемой, иллюстрирующей другую конфигурацию сдвигового регистра варианта осуществления 3.

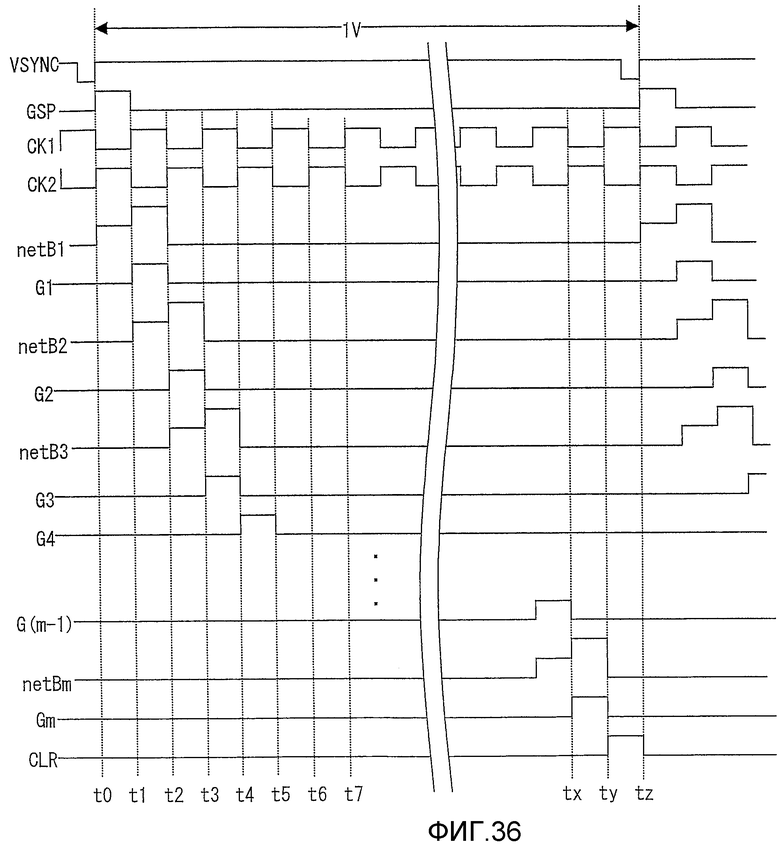

Фиг.36 является временной диаграммой, иллюстрирующей работу (в случае, если сигнал синхронизации не включает в себя аномальность) сдвигового регистра, показанного на фиг.35.

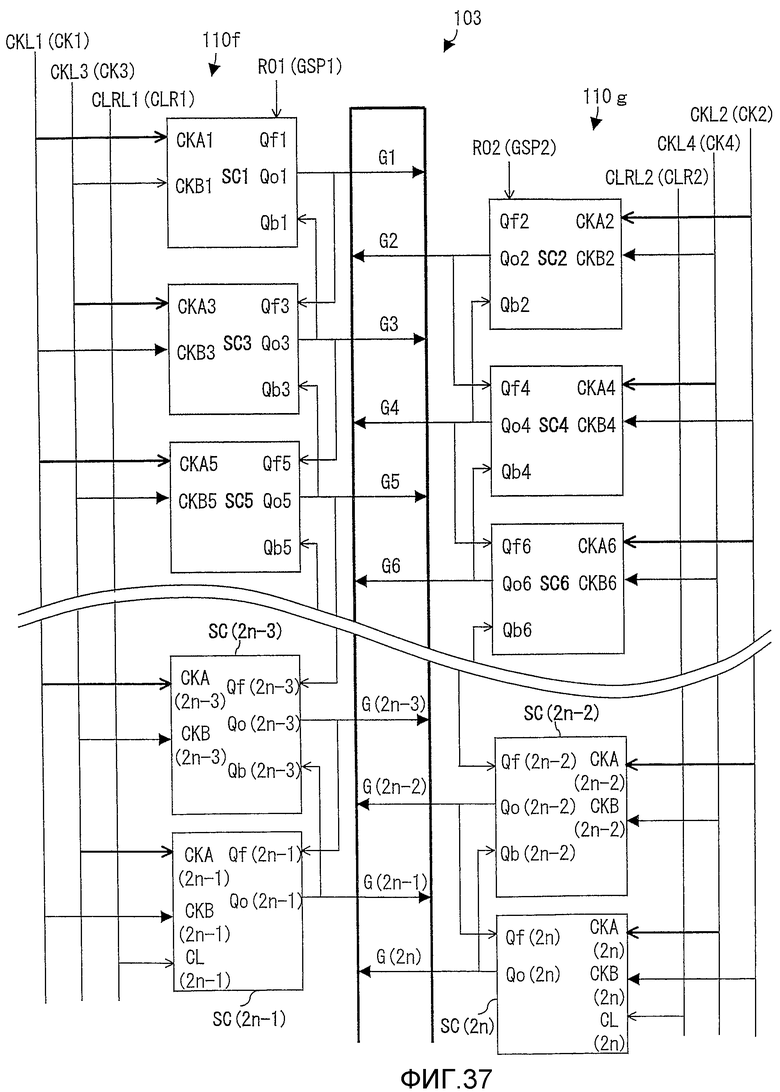

Фиг.37 является блок-схемой, иллюстрирующей конфигурацию сдвигового регистра варианта осуществления 4.

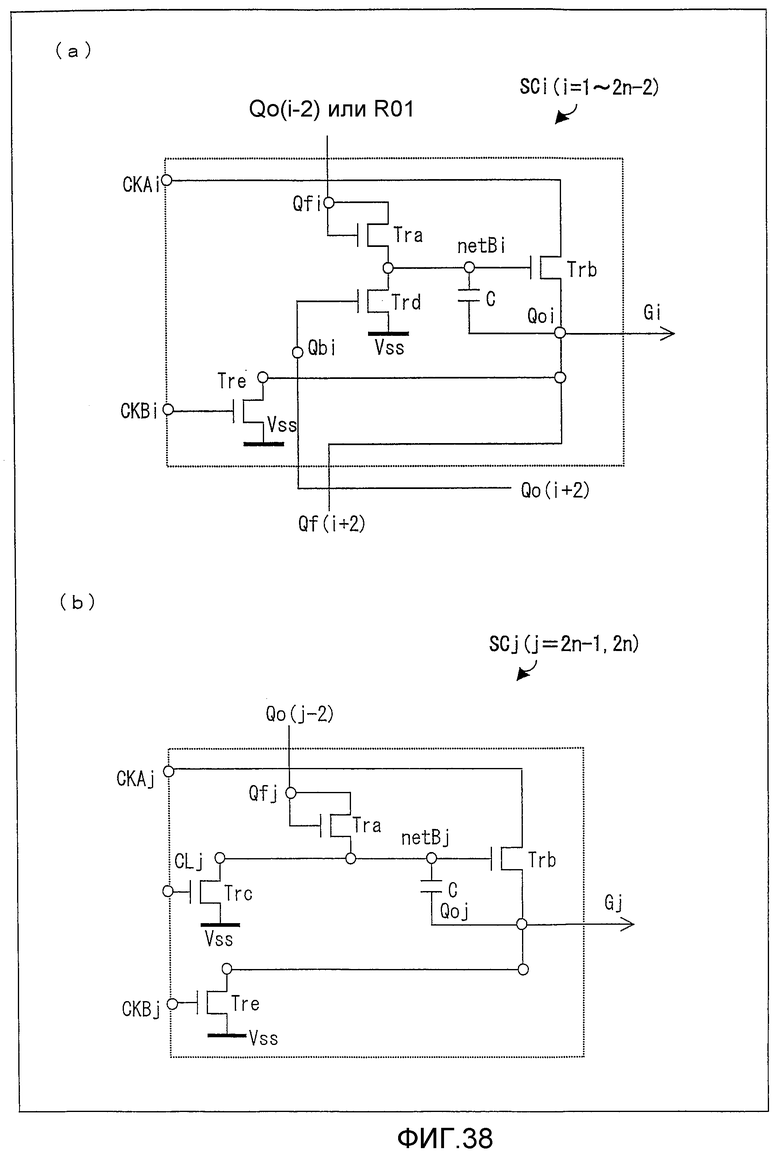

Части (a) и (b) по фиг.38 являются принципиальными схемами, иллюстрирующими конфигурацию модульной схемы сдвигового регистра варианта осуществления 4.

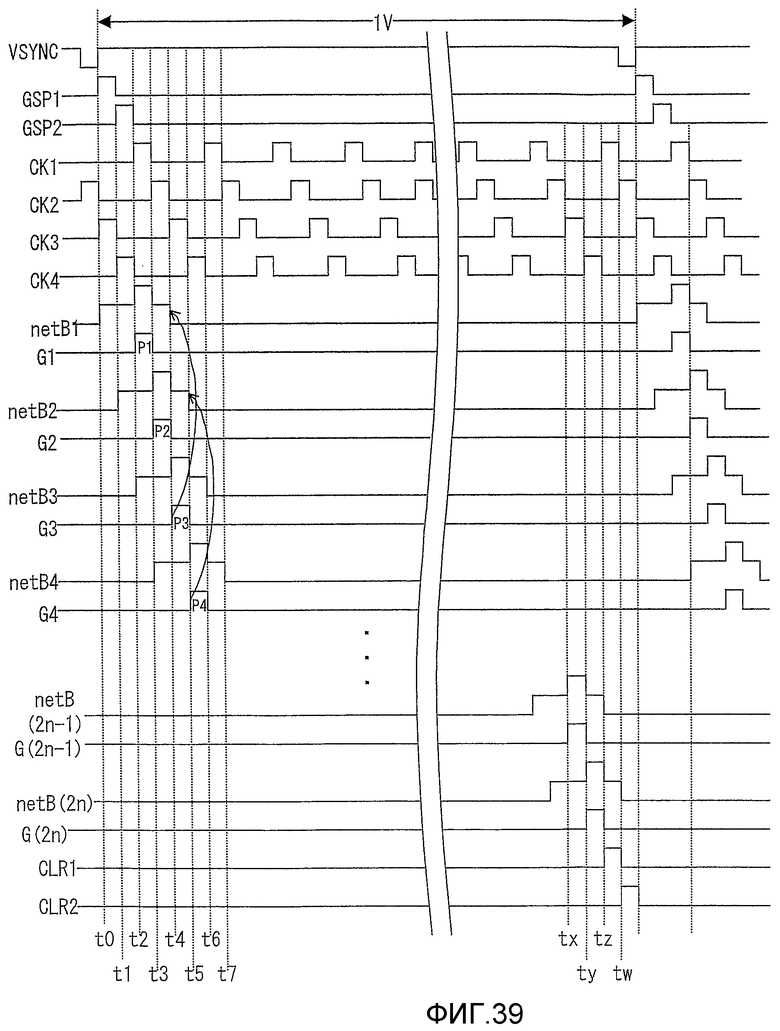

Фиг.39 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.37.

Фиг.40 является блок-схемой, иллюстрирующей конфигурацию традиционного сдвигового регистра.

Фиг.41 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.40.

Фиг.42 является временной диаграммой, иллюстрирующей работу сдвигового регистра, показанного на фиг.40.

Список номеров ссылок

1 - жидкокристаллическое дисплейное устройство (дисплейное устройство)

10, 10a-10g - сдвиговый регистр

G1-Gm - отпирающий импульс (сигнал выбора сигнальной линии)

SC1-SCm - схема сдвига (модульная схема)

GSP - импульс начала стробирования

CK1 - первый синхросигнал

CK2 - второй синхросигнал

CLR - сигнал очистки

Tra - транзистор задания

Trb - выходной транзистор

Trc - транзистор очистки

Trd - транзистор сброса

Tre - транзистор подачи с низким потенциалом

Описание вариантов осуществления

Далее описывается один вариант осуществления настоящего изобретения со ссылкой на фиг.1-39.

Фиг.23 является блок-схемой, иллюстрирующей конфигурацию жидкокристаллического дисплейного устройства настоящего изобретения. Как показано на фиг.23, жидкокристаллическое дисплейное устройство 1 настоящего изобретения включает в себя жидкокристаллическую панель 3, драйвер 5 затвора, драйвер 6 истока, контроллер 7 синхронизации, схему 8 обработки данных и схему 9 определения аномальности. Драйвер 5 затвора включает в себя сдвиговый регистр 10 и модуль 4 сдвига уровня. Драйвер 5 затвора, контроллер 7 синхронизации и схема 9 определения аномальности составляют возбуждающую схему 11 жидкокристаллической панели. Следует отметить, что, в настоящем варианте осуществления, модуль 4 сдвига уровня включен в драйвер 5 затвора. Тем не менее модуль 4 сдвига уровня может быть предусмотрен вне драйвера 5 затвора.

Жидкокристаллическая панель 3 включает в себя линии 16 сигналов сканирования, возбуждаемые посредством драйвера 5 затвора, линии 15 сигналов данных, возбуждаемые посредством драйвера 6 истока, пикселы P, провода накопительного конденсатора (не проиллюстрирован) и т.п. Дополнительно, сдвиговый регистр 10 монолитно предусмотрен в жидкокристаллической панели 3. Каждый из пикселов P содержит (i) транзистор (TFT), который подключается к одной из линий 16 сигналов сканирования и одной из линий 15 сигналов данных, и (ii), пикселный электрод, подключенный к транзистору. Следует отметить, что транзисторы, предусмотренные в пикселах, и транзистор сдвигового регистра могут формироваться при помощи аморфного кремния, поликристаллического кремния, CG-кремния и т.п.

Контроллер 7 синхронизации принимает, извне жидкокристаллического дисплейного устройства 1, сигнал VSYNC вертикальной синхронизации, сигнал HSYNC горизонтальной синхронизации и сигнал DE разрешения передачи данных, каждый из которых является сигналом синхронизации. Следует отметить, что эти сигналы синхронизации (VSYNC, HSYNC и DE) подаются также в схему 9 определения аномальности. Кроме того, схема 8 обработки данных принимает видеоданные (цифровые RGB-данные) извне жидкокристаллического дисплейного устройства 1. Схема 9 определения аномальности определяет аномальность в сигналах синхронизации и отправляет сигнал ошибки в контроллер 7 синхронизации в случае, если схема 9 определения аномальности определяет аномальность в сигнале синхронизации. Следует отметить, что схема 9 определения аномальности может определять аномальность в сигналах синхронизации с использованием, например, способа, раскрытого в публикации заявки на патент (Япония) номер 2003-167545. Контроллер 7 синхронизации формирует множество синхросигналов истока (ck1, ck2 и т.д.), сигнал очистки истока (clr) и сигнал импульса начала стробирования истока (gsp) с использованием сигналов синхронизации и сигнала ошибки, отправляемого из схемы 9 определения аномальности. Следует отметить, что синхросигналы истока (например, ck1 и ck2), сигнал очистки истока (clr) и сигнал импульса начала стробирования истока (gsp) сдвигаются по уровню посредством модуля 6 сдвига уровня так, чтобы становиться синхросигналами (CK1, CK2 и т.д.), сигналом очистки (CLR) и сигналом импульса начала стробирования (GSP), соответственно. Контроллер 7 синхронизации выводит управляющий сигнал в схему 8 обработки данных и также выводит синхронизирующий сигнал истока в драйвер 6 истока на основе принимаемых сигналов синхронизации (VSYNC, HSYNC и DE).

Синхросигналы (CKA, CKB и т.д.), сигнал очистки (CLR) и сигнал импульса начала стробирования (GSP) подаются в сдвиговый регистр 10. Сигнал очистки (CLR) становится "L" (неактивным) в случае, если сигналы синхронизации (VSYNC, HSYNC и DE) не включают в себя аномальность, становится "H" (активным) в случае, если, по меньшей мере, один из сигналов синхронизации (VSYNC, HSYNC и DE) включает в себя аномальность, и становится "H" (активным) после того, как импульс выводится из конечного каскада независимо от того, включена или нет аномальность в сигналы синхронизации. Сдвиговый регистр 10 формирует сигналы отпирающих импульсов с использованием этих сигналов (CKA, CKB и т.д.; CLR; и GSP) и выводит сигналы отпирающих импульсов в линии сигналов сканирования, предусмотренные в жидкокристаллической панели 3. Сдвиговый регистр 10 включает в себя схемы сдвига, подключенные каскадно, причем каждая из схем сдвига формирует сигнал отпирающего импульса. Сигналы отпирающих импульсов, сформированные в каскадах (схемах сдвига), последовательно активируются в течение соответствующего данного периода. Это инструктирует импульсам (импульсам включения) выводиться последовательно согласно порядковому номеру от первого каскада до конечного каскада. После этого, в жидкокристаллической панели 3, линии сигналов сканирования последовательно выбираются, в соответствии с импульсами.

Схема 8 обработки данных выполняет заранее определенный процесс для видеоданных и выводит сигнал данных в драйвер 6 истока в соответствии с управляющим сигналом, выводимым из контроллера 7 синхронизации. Драйвер 6 истока формирует электрический потенциал сигнала с использованием (i) сигнала данных, выводимого из схемы 8 обработки данных, и (ii) синхронизирующего сигнала истока, выводимого из контроллера 7 синхронизации, и выводит сформированный электрический потенциал сигнала в линии сигналов данных, предусмотренные в жидкокристаллической панели 3. Электрические потенциалы сигналов записываются в пикселные электроды пикселов через транзисторы пикселов.

Первый вариант осуществления

Фиг.1 иллюстрирует конфигурацию сдвигового регистра 10a в соответствии с настоящим вариантом осуществления 1. Как показано на фиг.1, сдвиговый регистр 10a состоит из множества схем SC1, SC2, …, и SCm сдвига (модульных схем), подключенных каскадно. Каждая из схем SCi сдвига (i=1, 2, 3, …, и m-1) включает в себя входные узлы Qfi, Qbi, CKAi и CLi и выходной узел Qoi. Схема scm сдвига включает в себя входные узлы Qfm, CKAm и CLm и выходной узел Qom.

Схема SC1 сдвига имеет узел Qf1, подключенный к выходному контактному выводу RO GSP модуля сдвига уровня (см. фиг.23). Дополнительно, схема сдвига имеет узел Qb1, подключенный к узлу Qo2 схемы SC2 сдвига, имеет узел CKA1, подключенный к первой линии CKL1 синхросигнала, в которую подается первый синхросигнал, и имеет узел CL1, подключенный к линии CLRL очистки, в которую подается сигнал очистки (CLR). Дополнительно, схема SC1 сдвига выводит сигнал G1 отпирающего импульса (сигнал выбора сигнальной линии) через узел Qo1.

Каждая из схем SCi сдвига (i=2 к m-1) имеет узел Qfi, подключенный к узлу Qo(i-1) схемы SC(i-1) сдвига, и имеет узел Qbi, подключенный к узлу Qo(i+1) схемы SC(i+1) сдвига. В случае если i является нечетным числом, узел CKAi подключается к первой линии CKL1 синхросигнала, а в случае если i является четным числом, узел CKAi подключается ко второй линии CKL2 синхросигнала. Дополнительно, узел CLi каждой из схем SCi сдвига подключается к линии CLRL очистки. Кроме того, каждая из схем SCi сдвига выводит сигнал Gi отпирающего импульса (сигнал выбора сигнальной линии) через узел Qoi.

Схема scm сдвига имеет узел Qfm, подключенный к узлу Qo(m-1) схемы SC(m-1) сдвига, имеет узел CKAm, подключенный ко второй линии CKL2 синхросигнала, и имеет узел CLm, подключенный к линии CLRL очистки. Дополнительно, схема SCm сдвига выводит сигнал Gm отпирающего импульса (сигнал выбора сигнальной линии) через узел Qom.

Конкретно проиллюстрирована в (a) по фиг.2 принципиальная схема конфигурации, используемой посредством каждой из схем SCi сдвига (i=1-m-1). Как проиллюстрировано на (a) по фиг.2, каждая из схем SCi сдвига (i=1-m-1) включает в себя транзистор Tra задания, выходной транзистор Trb, транзистор Trc очистки, транзистор Trd сброса и конденсатор C. Следует отметить, что каждый из транзисторов Tra-Trd является транзистором с каналом n-типа.

Транзистор Trb имеет контактный вывод истока, подключенный к первому электроду конденсатора C. Транзистор Tra имеет контактный вывод затвора (управляющий контактный вывод) и контактный вывод стока, подключенные друг к другу, и имеет контактный вывод истока, подключенный к (i) контактному выводу затвора транзистора Trb и (ii) второму электроду конденсатора C. Транзистор Trc имеет контактный вывод стока, подключенный к контактному выводу затвора транзистора Trb, и контактный вывод истока, подключенный к источнику Vss питания на стороне с более низким потенциалом. Транзистор Trd имеет контактный вывод стока, подключенный к контактному выводу затвора транзистора Trb, и контактный вывод истока, подключенный к источнику Vss питания на стороне с более низким потенциалом. Контактный вывод затвора транзистора Tra подключается к узлу Qfi, транзистор Trb имеет контактный вывод стока, подключенный к узлу CKAi, транзистор Trc имеет контактный вывод затвора, подключенный к узлу CLi; транзистор Trd имеет контактный вывод затвора, подключенный к узлу Qbi; и контактный вывод истока транзистора Trb подключается к узлу Qoi. Следует отметить, что точка соединения контактного вывода истока транзистора Tra, второго электрода конденсатора C и контактного вывода затвора транзистора Trb задана как узел netAi.

Конкретно проиллюстрирована в (b) по фиг.2 принципиальная схема конфигурации схемы scm сдвига. Как проиллюстрировано на (b) по фиг.2, схема scm сдвига включает в себя транзистор Tra задания, выходной транзистор Trb, транзистор Trc очистки и конденсатор C. Следует отметить, что каждый из транзисторов Tra-Trc является транзистором с каналом n-типа, и конденсатор C также может быть паразитным конденсатором. Транзистор Trb имеет контактный вывод истока, подключенный к первому электроду конденсатора C. Транзистор Tra имеет контактный вывод затвора (управляющий контактный вывод) и контактный вывод стока, подключенные друг к другу, и транзистор Tra имеет контактный вывод истока, подключенный к (i) контактному выводу затвора транзистора Trb и (ii) второму электроду конденсатора C. Транзистор Trc имеет контактный вывод стока, подключенный к контактному выводу затвора транзистора Trb, и имеет контактный вывод истока, подключенный к источнику Vss питания на стороне с более низким потенциалом. Контактный вывод затвора транзистора Tra подключается к узлу Qfm, транзистор Trb имеет контактный вывод стока, подключенный к узлу CKAm, транзистор Trc имеет контактный вывод затвора, подключенный к узлу CLm, и контактный вывод истока транзистора Trb подключается к узлу Qom. Следует отметить, что точка соединения контактного вывода истока транзистора Tra, второго электрода конденсатора C и контактного вывода затвора транзистора Trb задана как узел netAm.

Узлы (Qfi, Qbi, CKAi, CLi и Qoi) в каждой из схем SCi сдвига (i=1-m-1) и узлы (Qfm, CKAm, CLm и Qom) в схеме scm сдвига подключаются к соответствующим точкам назначения, как проиллюстрировано на фиг.1. Конфигурация всего сдвигового регистра 10a является такой, как конкретно проиллюстрировано на фиг.3.

Далее описываются операции сдвигового регистра 10a, проиллюстрированного на фиг.3. Фиг.4 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR) в случае, если сигналы синхронизации не включают в себя аномальность. Следует отметить, что каждый из первого синхросигнала CK1 и второго синхросигнала CK2 включает в себя, в одном цикле, один тактовый интервал "H" (активного) периода и три тактовых интервала "L" (неактивного) периода. После того, как один из синхросигналов CK1 и CK2 деактивируется (падает), другой из синхросигналов CK1 и CK2 активируется (повышается) с задержкой в один тактовый интервал. Это является просто примером первого и второго синхросигналов CK1 и CK2; период "H" и период "L" могут произвольно задаваться до тех пор, пока имеется период, в который оба синхросигнала совпадают как "L".

В t0 на фиг.4 активация сигнала GSP импульса начала стробирования приводит к повышению электрического потенциала Qf1. Это повышение электрического потенциала включает Tra SC1, тем самым заставляя электрический потенциал в netA1 изменяться с "L" на "H". Как результат, Trb SC1 также включается, и, соответственно, CK1 выводится через qo1. Согласно конфигурации G1 остается в "L". В t1, которое является временем в один тактовый интервал, истекший после t0, GSP падает (деактивируется) и становится "L". Тем не менее электрический потенциал в узле netA1 поддерживается в "H" посредством конденсатора C SC1, и, соответственно, Trb SC1 также остается включенным.

В t2, которое является временем в один тактовый интервал, истекший после t1, CK1 повышается (активируется), тем самым инструктируя G1 активироваться и становиться "H". Здесь, электрический потенциал в netA1 повышается до электрического потенциала выше "H" посредством конденсатора C. Кроме того, активация G1 заставляет электрический потенциал в Qf2 повышаться. Как результат, Tra SC2 включается, тем самым заставляя электрический потенциал в netA2 изменяться от "L" к "H". Это также инструктирует Trb SC2 включаться, и, соответственно, CK2 выводится через Qo2. Согласно конфигурации G2 остается в "L".

В t3, которое является временем в один тактовый интервал, истекший после t2, CK1 падает и становится "L", и электрический потенциал в netA1 также возвращается обратно к "H". Тем не менее, поскольку Trb SC1 остается включенным, CK1 непрерывно выводится через qo1. Согласно конфигурации, G1 деактивируется от "H" к "L", и это состояние "L" поддерживается. Следует отметить, что, даже если G1 деактивируется и становится "L", электрический потенциал в netA2 поддерживается в "H" посредством конденсатора C SC2, и Trb SC2 остается включенным.

В t4, которое является временем в один тактовый интервал, истекший после t3, CK2 повышается, тем самым инструктируя G2 активироваться и становиться "H". Здесь, электрический потенциал в netA2 повышается до электрического потенциала выше "H" посредством конденсатора C. Кроме того, активация G2 заставляет электрический потенциал в Qb1 повышаться; следовательно, Trd SC1 включается, что подключает netA1 к Vss, тем самым заставляя электрический потенциал в netA1 изменяться от "H" к "L". Как результат, Trb SC1 отключается, и CK1 больше не выводится через Qo1.

В t5, которое является временем в один тактовый интервал, истекший после t4, CK2 падает и становится "L", и электрический потенциал в netA2 также возвращается обратно к "H". Тем не менее, поскольку Trb SC2 остается включенным, CK2 непрерывно выводится через Qo2. Согласно конфигурации G2 деактивируется от "H" к "L", и это состояние "L" поддерживается.

Дополнительно, в tx, CK2 повышается, и, соответственно, Gm также активируется и становится "H". Здесь, электрический потенциал в netAm повышается до электрического потенциала выше "H" посредством конденсатора C.

В ty, которое является временем в один тактовый интервал, истекший после tx, CK2 падает и становится "L", и электрический потенциал в netAm также возвращается обратно к "H". Тем не менее, поскольку Trb SCm остается включенным, CK2 непрерывно выводится через Qom. Согласно конфигурации Gm деактивируется от "H" к "L", и это состояние "L" поддерживается.

В tz, которое является временем в один тактовый интервал, истекший после ty, CK2 остается в "L". Тем не менее, поскольку сигнал CLR очистки активируется и становится "H", Trc SCm включается, что подключает netAm к Vss, тем самым заставляя электрический потенциал в netAm изменяться от "H" к "L". Как результат, Trb SCm отключается, и CK2 больше не выводится через Qom.

Следует отметить, что, на фиг.4, сигнал CLR очистки активируется в tz (который составляет один тактовый интервал, истекший после падения Gm). Тем не менее настоящее изобретение не ограничено этим. Например, сигнал CLR очистки может быть активирован между ty и tz (исключая ty). Тем не менее сигнал CLR очистки не должен активироваться в ty. Это обусловлено тем, что, если сигнал CLR очистки активируется в ty, Gm поддерживает свое "H" (активное) состояние.

Как описано выше, в случае если сигнал синхронизации не включает в себя аномальность, сигналы Gi отпирающего импульса, выводимые из соответствующих схем SCi сдвига (i=1-m), последовательно становятся активными в течение соответствующего определенного периода времени в сдвиговом регистре 10a, и, соответственно, импульсы P1-Pm выводятся последовательно из соответствующих схем сдвига согласно порядковому номеру, от схемы SC1 сдвига в первом каскаде до схемы scm сдвига в конечном каскаде.

Фиг.5 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR) в случае, если сигнал синхронизации включает в себя аномальность.

Операции сдвигового регистра 10a от t0 до t5 на фиг.5 являются идентичными операциям, проиллюстрированным на фиг.4. В t5 CK2 падает и становится "L", и электрический потенциал в netA2 также возвращается к "H"; тем не менее, поскольку Trb SC2 остается включенным, CK2 непрерывно выводится через Qo2. Согласно конфигурации G2 деактивируется от "H" к "L", и это состояние "L" поддерживается. В t5 G2 деактивируется и становится "L", но электрический потенциал в netA3 поддерживается в "H" посредством конденсатора C схемы SC3 сдвига, и, соответственно, транзистор Trb схемы SC3 сдвига остается включенным.

В случае если, как проиллюстрировано на фиг.5, шум формируется в сигнале VSYNC вертикальной синхронизации между t3 и t4, и, соответственно, GSP активируется в непредвиденное время (t4), сигнал CLR очистки активируется и становится "H" в t6. Это инструктирует Trc SC3 включаться, что подключает netA3 к Vss, тем самым заставляя электрический потенциал в netA3 изменяться от "H" к "L". Как результат, Trb SC3 отключается, и CK1 больше не выводится через Qo3. Соответственно G3 остается в "L" (неактивным). Согласно конфигурации импульсы не выводятся из SC3; это не допускает включения Trb SC4, SC5, ..., и SCm, причем эти схемы сдвига являются схемами сдвига в последующих каскадах, и, как результат, импульсы не выводятся из этих схем сдвига. Следовательно, в течение текущего периода вертикального сканирования импульсы не выводятся из схем сдвига, следующих после схемы SC2 сдвига (импульс P2), и, соответственно, сигналы отпирающих импульсов, выводимые из соответствующих каскадов, остаются в "L" (неактивным) до тех пор, пока последующий период вертикального сканирования (TO) не начинается.

Следует отметить, что, на фиг.5, сигнал CLR очистки активируется в t6, тем не менее настоящее изобретение не ограничено этим. Сигнал CLR очистки может быть активирован между t5 и t6.

Согласно варианту осуществления сигнал CLR очистки становится "H" (активным) в случае, если сигнал синхронизации (VSYNC, HSYNC или DE) включает в себя аномальность, и импульсы не выводятся из сдвигового регистра после этого, до тех пор, пока последующий период вертикального сканирования не начинается. Это позволяет предотвращать возникновение разупорядочения отображения и подавлять увеличение нагрузки, подаваемой на источник питания.

Следует отметить, что сдвиговый регистр 10a, проиллюстрированный на фиг.3, может быть выполнен идентично сдвиговому регистру 10b, проиллюстрированному на фиг.6. Сдвиговый регистр 10b, в дополнение к конфигурации сдвигового регистра 10a, включает в себя транзистор Tre подачи с низким потенциалом с каналом n-типа в схеме scm сдвига в конечном каскаде. Транзистор Tre имеет контактный вывод истока, подключенный к источнику питания на стороне с более низким потенциалом, контактный вывод стока, подключенный к узлу Qom, и контактный вывод затвора, подключенный к узлу CLm.

Согласно конфигурации сдвигового регистра 10b, можно инструктировать Gm падать посредством активации сигнала CLR очистки. Соответственно, как показано на фиг.7, сигнал CLR очистки активируется синхронно с падением (деактивацией) Gm, в ty.

Альтернативно, сдвиговый регистр 10a, проиллюстрированный на фиг.3, может быть выполнен идентично сдвиговому регистру 10c, проиллюстрированному на фиг.8. Сдвиговый регистр 10c, в дополнение к конфигурации сдвигового регистра 10a, включает в себя транзистор Tre подачи с низким потенциалом с каналом n-типа в каждой из схем SCi сдвига (i=1-m-1). Транзистор Tre имеет контактный вывод истока, подключенный к источнику питания на стороне с более низким потенциалом, контактный вывод стока, подключенный к узлу Qoi, и контактный вывод затвора, подключенный к узлу Qbi.

Далее описываются операции сдвигового регистра 10c, проиллюстрированного на фиг.8. Фиг.9 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR) в случае, если сигнал синхронизации не включает в себя аномальность. Следует отметить, что каждый из первого синхросигнала CK1 и второго синхросигнала CK2 включает в себя, в одном цикле, один тактовый интервал "H" (активного) периода и один тактовый интервал "L" (неактивного) периода. При падении одного из синхросигналов CK1 и CK2 синхронно повышается другой из синхросигналов CK1 и CK2.

В t0 на фиг.9 активация GSP приводит к повышению электрического потенциала Qf1. Это повышение электрического потенциала включает Tra SC1, тем самым заставляя электрический потенциал в netA1 изменяться с "L" на "H". Как результат, Trb SC1 включается, и, соответственно, CK1 выводится через qo1. Согласно конфигурации сигнал G1 отпирающего импульса остается в "L".

В t1, которое является временем в один тактовый интервал, истекший после t0, GSP падает (деактивируется) и становится "L". Тем не менее падения электрического потенциала в netA1 посредством конденсатора C SC1 не происходит, и, соответственно, Trb SC1 остается включенным. Согласно конфигурации повышение CK1 инструктирует G1 активироваться и приводит к тому, что G1 становится "H". Здесь, электрический потенциал в netA1 повышается до электрического потенциала выше "H" посредством конденсатора C. Кроме того, активация G1 заставляет электрический потенциал в Qf2 повышаться. Как результат, Tra SC2 включается, тем самым заставляя электрический потенциал в netA2 изменяться от "L" к "H". Это также инструктирует Trb SC2 включаться, и, соответственно, CK2 выводится через Qo2. Согласно конфигурации G2 остается в "L".

В t2, которое является временем в один тактовый интервал, истекший после t1, CK2 повышается, тем самым инструктируя G2 активироваться и становиться "H". Здесь, электрический потенциал в netA2 повышается до электрического потенциала выше "H" посредством конденсатора C. Кроме того, активация G2 заставляет электрический потенциал в Qb1 повышаться; следовательно, Trd SC1 включается, что подключает netA1 к Vss, тем самым заставляя электрический потенциал в netA1 изменяться от "H" к "L". Как результат, Trb SC1 отключается, и CK1 больше не выводится через qo1. Кроме того, активация G2 заставляет электрический потенциал Qb1 повышаться; следовательно, Tre SC1 включается, что подключает qo1 к Vss, тем самым заставляя электрический потенциал в qo1 изменяться от "H" к "L". Согласно конфигурации G1 деактивируется от "H" к "L", и это состояние "L" поддерживается. Следует отметить, что, даже если G1 деактивируется и становится "L", электрический потенциал в netA2 поддерживается посредством конденсатора C SC2, и, соответственно, Trb SC2 остается включенным. Кроме того, когда сигнал g2 отпирающего импульса активируется, и электрический потенциал Qf3 повышается, Tra SC3 включается, и, соответственно, электрический потенциал в netA3 изменяется от "L" к "H". Как результат, Trb SC3 включается, что инструктирует CK1 выводиться через Qo3. Согласно конфигурации G3 остается в "L".

В t3, которое является временем в один тактовый интервал, истекший после t2, CK1 повышается, тем самым инструктируя G3 активироваться и становиться "H". Кроме того, активация G3 заставляет электрический потенциал Qb2 повышаться. Как результат, Trd схемы SC2 сдвига включается, что подключает netA2 к Vss, тем самым заставляя электрический потенциал в netA2 изменяться от "H" к "L". Соответственно Trb SC2 отключается, и CK2 больше не выводится через Qo2. Кроме того, активация G3 заставляет электрический потенциал Qb2 повышаться. Как результат, Tre SC2 включается, что подключает Qo2 к Vss, и тем самым электрический потенциал в Qo2 изменяется от "H" к "L". Согласно конфигурации G2 деактивируется от "H" к "L", и это состояние "L" поддерживается.

Дополнительно, в tx, CK2 повышается, и, соответственно, Gm также активируется и становится "H". Здесь, электрический потенциал в netAm повышается до электрического потенциала выше "H" посредством конденсатора C.

В ty, которое является временем в один тактовый интервал, истекший после tx, CK2 падает и становится "L", и электрический потенциал в netAm также возвращается обратно к "H". Тем не менее, поскольку Trb SCm остаются включенным, CK2 непрерывно выводится через Qom. Согласно конфигурации Gm деактивируется от "H" к "L", и это состояние "L" поддерживается.

В tz, которое является временем в один тактовый интервал, истекший после ty, сигнал CLR очистки активируется и становится "H". Соответственно, Trc SCm включается, что подключает netAm к Vss, тем самым заставляя электрический потенциал в netAm изменяться от "H" к "L". Как результат, Trb SCm отключается, и CK2 больше не выводится через Qom.

Следует отметить, что, на фиг.9, сигнал CLR очистки активируется в tz (который составляет один тактовый интервал, истекший после падения Gm). Тем не менее настоящее изобретение не ограничено этим. Например, сигнал CLR очистки может быть активирован между ty и tz (исключая ty). Тем не менее сигнал CLR очистки не должен активироваться в ty. Это обусловлено тем, что, если сигнал CLR очистки активируется в ty, Gm поддерживает свое "H" (активное) состояние.

Как описано выше, в случае если сигнал синхронизации не включает в себя аномальность, сигналы gi отпирающих импульсов, выводимые из соответствующих схем SCi сдвига (i=1-m), последовательно активируются в течение соответствующего определенного периода времени в сдвиговом регистре 10b, и, соответственно, импульсы выводятся последовательно из соответствующих схем сдвига согласно порядковому номеру, от схемы SC1 сдвига в первом каскаде до схемы scm сдвига в конечном каскаде.

Фиг.10 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR), в случае если сигнал синхронизации включает в себя аномальность.

Операции сдвигового регистра 10c от t0 до t3 на фиг.10 являются идентичными операциям, показанным на фиг.9. В случае, если шум формируется в сигнале VSYNC вертикальной синхронизации между t2 и t3, и, соответственно, GSP активируется в непредвиденное время (t3) (см. фиг.10), сигнал CLR очистки активируется и становится "H" в t4. Это инструктирует Trc SC3 включаться, что подключает netA3 к Vss, тем самым заставляя электрический потенциал в netA3 изменяться от "H" к "L". Как результат, Trb SC3 отключается, и CK1 больше не выводится через Qo3. Соответственно сигнал G3 отпирающего импульса остается в "L" (неактивным). Согласно конфигурации импульсы не выводятся из SC3; это не допускает включения Trb SC4, SC5, …, и SCm, причем эти схемы сдвига являются схемами сдвига в последующих каскадах, и, как результат, импульсы не выводятся из этих схем сдвига. Соответственно, в течение текущего периода вертикального сканирования, импульсы не выводятся из схем сдвига, следующих после схемы SC2 сдвига, и, соответственно, сигналы отпирающих импульсов, выводимые из соответствующих каскадов, остаются в "L" (неактивным) до тех пор, пока последующий период вертикального сканирования (TO) не начинается.

Следует отметить, что, на фиг.10, сигнал CLR очистки активируется в t4, тем не менее настоящее изобретение не ограничено этим. Сигнал CLR очистки также может быть активирован в t5.

Следует отметить, что сдвиговый регистр 10c, проиллюстрированный на фиг.8, может быть выполнен идентично сдвиговому регистру 10d, проиллюстрированному на фиг.11. Сдвиговый регистр 10d, в дополнение к конфигурации сдвигового регистра 10c, включает в себя транзистор Tre подачи с низким потенциалом с каналом n-типа в схеме scm сдвига в конечном каскаде. Транзистор Tre имеет контактный вывод истока, подключенный к источнику питания на стороне с более низким потенциалом, контактный вывод стока, подключенный к узлу Qom, и контактный вывод затвора, подключенный к узлу CLm.

Согласно конфигурации сдвигового регистра 10d, можно инструктировать Gm падать посредством активации сигнала CLR очистки. Соответственно, как показано на фиг.12, сигнал CLR очистки активируется синхронно с падением (деактивацией) Gm, в ty.

Альтернативно, сдвиговый регистр 10a, проиллюстрированный на фиг.3, может быть выполнен идентично сдвиговому регистру 10e, проиллюстрированному на фиг.13. Сдвиговый регистр 10e, в дополнение к конфигурации сдвигового регистра 10a, включает в себя транзистор Tre подачи с низким потенциалом с каналом n-типа в каждой из схем SCi сдвига (i=1-m). Транзистор Tre имеет контактный вывод истока, подключенный к источнику питания на стороне с более низким потенциалом, контактный вывод стока, подключенный к узлу Qoi, и контактный вывод затвора, подключенный к первой линии CKL1 синхросигнала или второй линии CKL2 синхросигнала. Следует отметить, что, в случае если i является нечетным числом, контактный вывод затвора транзистора Tre схемы SCi сдвига подключается ко второй линии CKL2 синхросигнала, а в случае если i является четным числом, контактный вывод затвора транзистора Tre подключается к первой линии CKL1 синхросигнала.

Далее описываются операции сдвигового регистра 10e, проиллюстрированного на фиг.13. Фиг.14 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR), в случае если сигнал синхронизации не включает в себя аномальность. Следует отметить, что каждый из первого синхросигнала CK1 и второго синхросигнала CK2 включает в себя, в одном цикле, один тактовый интервал "H" (активного) периода и один тактовый интервал "L" (неактивного) периода. При падении одного из синхросигналов CK1 и CK2 синхронно повышается другой из синхросигналов CK1 и CK2.

В t0 на фиг.14 активация GSP приводит к повышению электрического потенциала Qf1. Повышение электрического потенциала включает Tra SC1, тем самым заставляя электрический потенциал в netA1 изменяться от "L" к "H". Как результат, Trb SC1 включается, и, соответственно, CK1 выводится через Qo1.

В t1, которое является временем в один тактовый интервал, истекший после t0, GSP падает (деактивируется) и становится "L". Тем не менее падения электрического потенциала в netA1 посредством конденсатора C SC1 не происходит, и, соответственно, Trb SC1 остается включенным. Согласно конфигурации, повышение CK1 инструктирует G1 активироваться и приводит к тому, что G1 становится "H". Здесь, электрический потенциал в netA1 повышается до электрического потенциала выше "H" посредством конденсатора C.

Кроме того, активация G1 заставляет электрический потенциал в Qf2 повышаться. Как результат, Tra SC2 включается, тем самым заставляя электрический потенциал в netA2 изменяться от "L" к "H". Это также инструктирует Trb SC2 включаться, и, соответственно, CK2 выводится через Qo2. Согласно конфигурации G2 остается в "L".

В t2, которое является временем в один тактовый интервал, истекший после t1, CK2 повышается, тем самым инструктируя G2 активироваться и становиться "H". Здесь, электрический потенциал в netA2 повышается до электрического потенциала выше "H" посредством конденсатора C. Кроме того, активация G2 заставляет электрический потенциал в Qb1 повышаться; следовательно, Trd SC1 включается, что подключает netA1 к Vss, тем самым заставляя электрический потенциал в netA1 изменяться от "H" к "L". Как результат, Trb SC1 отключается, и CK1 больше не выводится через qo1. Кроме того, поскольку CK2 повышается в t2, Tre SC1 включается, что подключает qo1 к Vss, тем самым заставляя электрический потенциал в qo1 изменяться от "H" к "L". Согласно конфигурации сигнал g1 отпирающего импульса деактивируется от "H" к "L", и это состояние "L" поддерживается. Следует отметить, что, даже если G1 деактивируется и становится "L", электрический потенциал в netA2 поддерживается посредством конденсатора C SC2, и, соответственно, Trb SC2 остается включенным. Кроме того, когда сигнал g2 отпирающего импульса активируется, и электрический потенциал Qf3 повышается, Tra SC3 включается, и, соответственно, электрический потенциал в netA3 изменяется от "L" к "H". Как результат, Trb SC3 включается, что инструктирует CK1 выводиться через Qo3. Согласно конфигурации G3 остается в "L".

В t3, которое является временем в один тактовый интервал, истекший после t2, CK1 повышается, тем самым инструктируя G3 активироваться и становиться "H". Кроме того, активация G3 заставляет электрический потенциал Qb2 повышаться. Как результат, Trd SC2 включается, что подключает netA2 к Vss, тем самым заставляя электрический потенциал в netA2 изменяться от "H" к "L". Соответственно, Trb SC2 отключается, и CK2 больше не выводится через Qo2. Кроме того, в t3, CK1 повышается. Это инструктирует Tre SC2 включаться, что подключает Qo2 к Vss, тем самым заставляя электрический потенциал в узле Qo2 изменяться от "H" к "L". Согласно конфигурации G2 деактивируется от "H" к "L", и это состояние "L" поддерживается.

Следует отметить, что, в сдвиговом регистре 10e, CK2 находится в "H" в течение t4-t5 и в течение t6-t7. Соответственно Tre SC1 включается, что подключает qo1 к Vss. Это позволяет инструктировать G1 падать до "L" снова (т.е. приводиться к "L"). Аналогично, CK1 находится в "H" в течение t5-t6. Соответственно, Tre SC2 включается, что подключает Qo2 к Vss. Это позволяет инструктировать G2 падать до "L" снова (приводиться к "L").

Дополнительно, в tx, CK2 повышается; соответственно Gm активируется и становится "H". Здесь, электрический потенциал в netAm повышается до электрического потенциала выше "H" посредством конденсатора C.

В ty, которое является временем в один тактовый интервал, истекший после tx, сигнал CLR очистки активируется и становится "H". Соответственно транзистор Trc схемы scm сдвига включается, что подключает netAm к Vss. Это заставляет электрический потенциал в netAm падать до "L". Как результат, Trb SCm отключается, и CK2 больше не выводится через Qom. Дополнительно, в ty, CK1 повышается. Соответственно Tre SCm включается, что подключает Qom к Vss. Как результат, Gm деактивируется и становится. Следует отметить, что, на фиг.14, сигнал CLR очистки активируется в ty, тем не менее настоящее изобретение не ограничено этим. Например, сигнал CLR очистки может быть активирован между ty и tz (ty и tz включительно).

Как описано выше, в случае если сигнал синхронизации не включает в себя аномальность, сигналы gi отпирающих импульсов, выводимые из соответствующих схем SCi сдвига (i=1-m), последовательно активируются в течение соответствующего определенного периода времени в сдвиговом регистре 10e, и, соответственно, импульсы выводятся последовательно из соответствующих схем сдвига согласно порядковому номеру, от схемы SC1 сдвига в первом каскаде до схемы scm сдвига в конечном каскаде.

Фиг.15 является временной диаграммой, иллюстрирующей формы сигналов для сигнала VSYNC вертикальной синхронизации, сигнала GSP импульса начала стробирования, первого синхросигнала CK1, второго синхросигнала CK2, сигналов Gi отпирающих импульсов (i=1-m) и сигнала очистки (CLR), в случае если сигнал синхронизации включает в себя аномальность.

Операции сдвигового регистра 10b от t0 до t3 на фиг.15 являются идентичными операциям, проиллюстрированным на фиг.14. В случае если шум формируется в сигнале VSYNC вертикальной синхронизации между t1 и t2 и, соответственно, сигнал GSP импульса начала стробирования активируется в непредвиденное время (t2) (см. фиг.15), сигнал CLR очистки активируется и становится "H" в t3. Это инструктирует Trc SC3 включаться, что подключает netA3 к Vss, тем самым заставляя электрический потенциал в netA3 изменяться от "H" к "L". Как результат, Trb SC3 отключается, и CK1 больше не выводится через Qo3. Соответственно G3 остается в "L" (неактивным). Согласно конфигурации импульсы не выводятся из SC3; это не допускает включения Trb SC4, SC5, …, и SCm, причем эти схемы сдвига являются схемами сдвига в последующих каскадах, и, как результат, импульсы не выводятся из этих схем сдвига. Соответственно, в течение текущего периода вертикального сканирования, импульсы не выводятся из схем сдвига, следующих после схемы SC2 сдвига, и, соответственно, сигналы отпирающих импульсов, выводимые из соответствующих каскадов, остаются в "L" (неактивным) до тех пор, пока последующий период вертикального сканирования (TO) не начинается.

В этом случае также CK2 находится в "H" в течение t4-t5 и в течение t6-t7. Соответственно Tre SC1 включается, что подключает qo1 к Vss. Это позволяет инструктировать G1 падать до "L" снова (т.е. приводиться к "L"). Аналогично, CK1 находится в "H" в течение t5-t6. Соответственно транзистор Tre схемы SC2 сдвига включается, что подключает Qo2 к Vss. Это позволяет инструктировать G2 падать до "L" снова (приводиться к "L").