Изобретение относится к способам и средствам криптографического преобразования информации в электронных вычислительных комплексах и ЭВМ.

Известен способ поточного криптографического преобразования информации [RU 2357365, С2, H04L 9/06, 27.05.2009], заключающийся в том, что криптографическое вычисление осуществляют в электронном компоненте согласно определенному криптографическому алгоритму, включающему, по меньшей мере, одну точно определенную нелинейную операцию на k-битовых блоках данных, при этом k является целым числом больше 2, генерируют несколько промежуточных маскированных блоков данных из j бит (b⊕ m, с⊕ m2, Δ⊕n) на основании исходного блока данных из k бит, где j является целым числом, меньшим k, затем производят нелинейную операцию S, по меньшей мере, на одном j-битовом маскированном промежуточном блоке данных (Δ⊕n) при помощи таблицы замещения с 2j входами, получая j-битовый измененный блок данных (S(Δ)⊕n), который объединяют, по меньшей мере, с некоторыми из указанных j-битовых маскированных промежуточных блоков данных в один итоговый k-битовый блок, соответствующий исходному k-битовому блоку данных, через преобразование, включающее указанную точно определенную нелинейную операцию [RU 2357365, С2, H04L 9/06, 27.05.2009].

Недостатком способа является его относительно высокая сложность при аппаратной и программной реализации.

Известен также способ шифрования и дешифрования информации [RU 2266622, C1, H04L 9/06, 20.12.2005], характеризуемый использованием блочных взаимообратных однозначных двухпараметрических, шифрующего и дешифрующего, преобразований на основе таблиц со случайным заполнением размером N строк каждая с участием последовательности гаммы от независимого от информации датчика случайных чисел, причем для блока шифрования длиной α байт вырабатывают последовательность гаммы длиной α байт, изменяющейся для каждого блока, при этом каждый байт преобразуют с помощью двухпараметрического преобразования байт vi =F(ui, ξi) с участием квазислучайных значений последовательности гаммы ξi длиной 1 байт, затем выполняется в два этапа операция формирования блока шифрования путем объединения байт, причем шифрующее преобразование объединения байт первой ступени с номерами i, имеющими значения от 1 до α, выполняют суммированием определенных исходных ui и преобразованных значений vi байт:

аi=vi+vi+1+ui для i=l,…,(α-1); аα=vα+u1+u2+…+uα,

шифрующее преобразование объединения байт второй ступени аi с номерами i, имеющими значения от 1 до α, выполняют в виде рекуррентных операций F следующим образом: Xi=F(ai,ai+1) для i=l,…, (α-1); Xα=aα, дешифрующее преобразование байт выполняют в обратной последовательности, причем сначала выполняют дешифрующее преобразование второй ступени для значений каждого принятого байта X'i с номером i, имеющим значения от 1 до α, в виде рекуррентных операций F-1 следующим образом: а'α=X'α; a'I=F-1(X'i, a'i+1) для i=α-1, α-2,…, 1, затем выполняют дешифрующее преобразование первой ступени для значений каждого байта ai с номером i, имеющим значения от 1 до α, в виде рекуррентных операций F1 следующим образом:

Недостатком способа является его относительно высокая сложность при аппаратной и программной реализации.

Кроме того, известен способ шифрования двоичной информации [RU 2091983, C1, H04L 9/00, G06F 12/16, 27.09.1997], заключающийся в том, что формируют N-битный секретный ключ, с помощью которого формируют поточный шифр, который суммируют по модулю два с информационным текстом, причем поточный шифр формируют в виде К групп по N бит в каждой, где KN - длина текста двоичной информации, первую группу поточного шифра формируют путем возведения N-битного секретного ключа в степень n по модулю Р, вторую группу поточного шифра формируют путем возведения N-битного кода первой группы поточного шифра в степень n по модулю Р, где n - значение бит младших разрядов секретного ключа, причем 1<n N<Р 1, а каждую последующую i группу поточного шифра, где i 3, 4, К формируют путем возведения N-битного кода (i 1)-группы поточного шифра в степень m по модулю Р, где m значение бит младших разрядов (i 2)-группы поточного шифра, причем m<n, а перед суммированием по модулю два в каждой из К групп сформированного поточного шифра биты перемешивают по случайному закону и запоминают.

Недостатком способа является его относительно высокая сложность при аппаратной и программной реализации.

Наиболее близким по технической сущности к предлагаемому способу является способ поточного криптографического преобразования информации, основанный на разбивке исходного 32-разрядного входного вектора на восемь последовательно идущих 4-разрядных входных векторов, каждый из которых преобразуется в 4-разрядный выходной вектор соответствующим ему узлом замены, осуществляющего преобразование 4-разрядного входного вектора в 4-разрядный выходной вектор путем использования предварительно размещенной в нем таблицы преобразования из шестнадцати строк, содержащих по четыре бита заполнения в строке, при этом каждый из 4-разрядных входных векторов определяет адрес строки в таблице, а заполнение соответствующей строки в таблице является соответствующим ему 4-разрядным выходным вектором, которые последовательно объединяются в 32-разрядный выходной вектор [Системы обработки информации. Защита криптографическая. Алгоритм криптографического преобразования. ГОСТ 28147-89, п.1.2, с.2].

Недостатком способа является относительно низкая скрытность криптографического преобразования при его реализации в ЭВМ, поскольку способ реализует тетрадные (по четыре бита) перестановки в 32-битном слове, но реализация таких перестановок на регистрах процессоров современных ЭВМ затруднена, поскольку архитектура процессоров х86/64 и его система команд не способна манипулировать тетрадами. По этой причине реализация такого преобразования в виде программно реализуемого блока подстановки из восьми узлов замены с памятью 64 бита каждый осуществляется в оперативной памяти ЭВМ, что снижает скорость криптографического преобразования из-за медленного доступа к таблицам, размещенных в оперативной памяти, а также скрытность криптографического преобразования из-за размещения конфиденциальной информации в оперативной памяти с общим доступом.

Требуемый технический результат заключается в повышении скрытности и оперативности криптографического преобразования при его реализации на персональных ЭВМ.

Требуемый технический результат относительно предложенного способа достигается тем, что в способе, основанном на разбивке исходного 32-разрядного входного вектора на восемь последовательно идущих 4-разрядных входных векторов, каждый из которых соответствующим ему узлом замены преобразуется в 4-разрядный выходной вектор, которые последовательно объединяются в 32-разрядный выходной вектор, причем предварительно в каждом узле замены размещают таблицы преобразования из шестнадцати строк каждая, содержащих по четыре бита заполнения в строке, являющихся соответствующими 4-разрядным выходными векторами, используют четыре узла замены по одному для каждой пары 4-разрядных входных векторов, причем в каждом узле замены используют регистр центрального процессора с размером, равным или большим 16 байт, в который размещают по две таблицы преобразования, а преобразование пар 4-разрядных входных векторов в пары 4-разрядных выходных векторов в соответствующем узле замены осуществляют коммутацией предварительно размещенных строк таблиц преобразования в регистр центрального процессора соответствующего узла замены путем использования пар 4-разрядных входных векторов в виде адресов коммутации.

Кроме того, требуемый технический результат достигается тем, что в качестве регистров центрального процессора используют SSE-регистры.

Известны также устройства для криптографического преобразования информации.

Одно из таких устройств [RU 2091983, C1, H04L 9/00, G06F 12/16, 27.09.1997] содержит первый сумматор по модулю два, регистр для хранения секретного ключа, блок возведения в n степень по модулю Р, параллельно-последовательный регистр ключевой группы, четыре последовательно-параллельных регистра, регистр показателя степени, блок перемешивания бит последовательности, второй сумматор по модулю два, блок управления, ключ и элементы И и ИЛИ, причем выход блока возведения в n степень по модулю Р соединен с соответствующими входами регистра для хранения секретного ключа и параллельно-последовательного регистра ключевой группы, с входом основания степени блока возведения в n степень по модулю Р, с выходами первого последовательно-параллельного регистра и регистра для хранения секретного ключа, выходы n младших разрядов блока возведения в n степень по модулю Р подключены к соответствующим входам регистра показателя степени, выходы разрядов которого соединены с входами n младших разрядов показателя степени блока возведения в n степень по модулю Р, входы всех разрядов показателя степени которого соединены с выходами соответствующих разрядов второго последовательно-параллельного регистра, выходы m старших разрядов блока возведения в n степень по модулю Р, где m<n, соединены с первыми информационными входами блока перемешивания бит последовательности, входы модуля и обратной величины модуля блока возведения в n степень по модулю Р соединены, соответственно, с соответствующими выходами третьего и четвертого последовательно-параллельных регистров, причем информационные входы второго, третьего и четвертого последовательно-параллельных регистров являются соответственно входами начальной установки значений показателя степени, модуля и обратной величины, модуля устройства, а информационный вход первого последовательно-параллельного регистра соединен с выходом элемента ИЛИ, первый вход которого является входом начальной установки значения основания степени устройства, второй вход элемента ИЛИ соединен с выходом первого элемента И и входом сигнала о приеме шифрованного текста блока управления, выход второго элемента И соединен с первыми входами блока управления и второго сумматора по модулю два и с входом-выходом ключа и является входом открытого текста устройства, входы начальной установки первого, второго, третьего и четвертого последовательно-параллельных регистров и блока возведения в n степень по модулю Р соединены между собой и с соответствующим выходом блока управления, первые входы первого и второго элементов И соединены между собой и являются входом для приема закрытого текста устройства, вторые входы первого и второго элементов И соединены с соответствующими выходами блока управления, второй вход второго сумматора по модулю два соединен с выходом блока перемешивания бит последовательности и первым входом первого сумматора по модулю два, второй вход которого соединен с выходом ключа, с входом которого соединен выход второго сумматора по модулю два, а вход управления ключа соединен с соответствующим выходом блока управления и является выходом выработки сигнала разрешения приема открытого текста устройства, выход первого сумматора по модулю два соединен с выходом третьего элемента И и является выходом закрытого текста устройства, первый вход третьего элемента И соединен с выходом регистра ключевой группы и вторым информационным входом блока перемешивания бит последовательности, вход управления которого соединен с соответствующим выходом блока управления, другие выходы которого соединены соответственно с вторым входом третьего элемента И, входами приема сигналов начала возведения в степень и синхроимпульсов сопровождения блоков возведения в n степень по модулю Р и входами управления регистров показателя степени секретного ключа и ключевой группы, выход сигнала конца возведения в степень блока возведения в n степень по модулю Р соединен с соответствующим входом блока управления, другие входы которого являются соответственно входами определения режимов шифрации-дешифрации, выработки ключевой последовательности, открытого ключа, подачи задающей частоты и начальной установки устройства.

Недостатком устройства является его относительно высокая сложность.

Известно также устройство [RU 2389141, С2, H04L 9/00, 10.05.2010], содержащее на передающей стороне последовательно соединенные генератор ключа, блок формирования ключевой матрицы, шифрующий блок, второй вход которого соединен с выходом блока формирования информационного вектора, первый вход которого соединен с выходом блока формирования порождающей матрицы, второй вход является информационным входом устройства, а на приемной стороне последовательно соединенные блок сортировки элементов вектора, другой вход которого соединен с выходом блока формирования ключевой матрицы, вход которого соединен с выходом генератора ключа, блок замены элементов кодового вектора, блок умножения кодового вектора на матрицу Адамара, другой вход которого соединен с выходом блока формирования матрицы Адамара, блок принятия решения, второй вход которого соединен с выходом блока формирования порождающей матрицы, блок обратного преобразования, выход которого является информационным выходом устройства, при этом передающая сторона содержит также блок управления, формирующий управляющий сигнала для выбора длины информационного вектора, подлежащего шифрованию, выход которого является другим входом шифрующего блока, а на приемной стороне - блок сравнения, выход которого соединен с соответствующим входом блока принятия решения, первый вход бока сравнения соединен с выходом блока умножения, а второй вход - с выходом блока оптимизации, вход которого соединен с выходом блока обратного преобразования.

Недостатком устройства также является его относительно высокая сложность.

Недостатком устройства является относительно низкая скрытность криптографического преобразования при его программно-технической реализации с использованием ЭВМ, поскольку реализация предложенных в известном устройстве функциональных узлов и преобразований, например, блока умножения кодового вектора на матрицу Адамара, может осуществляется в оперативной памяти ЭВМ, что снижает скрытность криптографического преобразования из-за размещения конфиденциальной информации в оперативной памяти с общим доступом, а также быстродействие устройства из-за наличия сложных преобразований информации.

Требуемый технический результат заключается в повышении скрытности криптографического преобразования, а также быстродействия устройства, что повышает оперативность криптографического преобразования при его реализации на персональных ЭВМ.

Требуемый технический результат достигается тем, что в устройство, содержащее блок формирования информационного вектора, введены входной 32-разрядный регистр и четыре узла замены, каждый их которых содержит SSE-регистр и два коммутатора, при этом блок формирования информационного вектора выполнен в виде 32-разрядного выходного регистра, восемь входов которого соединены с выходами соответствующих коммутаторов узлов замены, информационные входы которых соединены с выходами SSE-регистра соответствующих им узлов замены, а адресные входы соединены с соответствующими выходами входного 32-разрядного регистра.

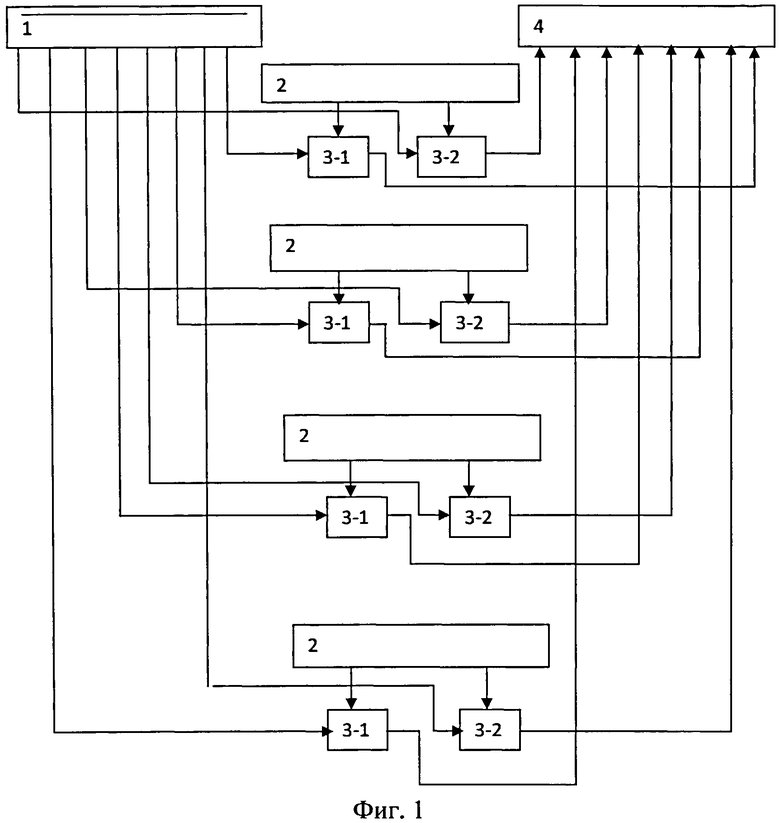

На чертеже представлены:

на фиг.1 - электрическая структурная схема устройства для криптографического преобразования информации;

на фиг.2 - пример схемы управления коммутаторами.

Устройство для криптографического преобразования информации содержит входной 32-разрядный регистр 1 и четыре узла замены, каждый их которых содержит регистр 2 центрального процессора, например SSE-регистры размером 16 или 32 байта (ХММ или UMM регистры), и два коммутатора 3-1 и 3-2, управлении которыми реализовано либо стандартной командой управления коммутаторами, либо командой, реализованной в блоке микропрограммного управления центрального процессора ЭВМ.

Кроме того, устройство для криптографического преобразования информации содержит 32-разрядный выходной регистр 4, восемь входов которого соединены с выходами соответствующих коммутаторов 3-1 и 3-2, информационные входы которых соединены с выходами регистра 2 центрального процессора соответствующих им узлов замены, а адресные входы соединены с соответствующими выходами входного 32-разрядного регистра 1.

Предложенный способ криптографического преобразования информации реализуется в устройстве для его реализации следующим образом.

В устройстве используется четыре узла замены, выполненных, например, на SSE-регистрах центрального процессора, которые относятся к внутреннему оборудованию центральных процессоров современных ЭВМ - 128-битных регистрах ХММ, либо 256-битных регистрах YMM. Современные процессоры архитектуры х86/64 имеют в своем составе набор регистров SSE размером 16 байт и специализированные FPU-многовходовые байтовые коммутаторы (как минимум два) для выполнения различных операций над этими регистрами. На одном SSE-регистре можно разместить сразу две таблицы из 16 строк. Таким образом, четыре SSE-регистра позволят полностью разместить все таблицы замен. Единственным условием такого размещения является требование чередования, согласно которому тетрады одного байта должны помещаться в разные SSE-регистры. Кроме этого целесообразно размещать младшие и старшие тетрады входных байтов соответственно в младших и старших тетрадах байтов SSE-регистров. Эти требования обуславливаются оптимизацией под имеющийся набор AVX команд.

Таким образом, каждый байт SSE-регистра будет содержать две тетрады, относящиеся к разным байтам входного регистра блока подстановок, при этом позиция байта на SSE-регистре однозначно соответствует индексу в таблице преобразования узла замен.

Размещение конфиденциальной информации в предложенном устройстве с использованием SSE-регистров повышает скрытность криптографического преобразования и его оперативность.

Для эффективной выборки из SSE-регистров могут быть использованы имеющиеся в составе процессоров FPU многовходовые байтовые коммутаторы. Эти коммутаторы позволяют осуществлять пересылки из любого байта источника в любой байт приемника, по индексам находящемся в специальном индексном SSE-регистре. Причем параллельно выполняется пересылка для всех 16 байт SSE-регистра-приемника. Управление коммутаторами производится либо стандартной командой управления коммутаторами, либо специальной командой, реализованной в блоке микропрограммного управления центрального процессора. В этом случае работой коммутаторов управляет специальная трехадресная команда AVX VPSHUFB, первый операнд которой является приемником информации из коммутаторов, второй операнд является источником, к которому подключены входы коммутаторов, а третий операнд является управляющим регистром для коммутаторов, каждый байт которого ассоциирован с соответствующим коммутатором и значение в нем задает номер направления, с которого коммутатор считывает информацию.

Реализация этой команды изображена на фиг.2 на примере половины SSE-регистров, поскольку для второй половины все аналогично.

Имея узлы хранения подстановок на SSE-регистрах и многовходовый коммутатор в блоках FPU, можно организовать следующее преобразование в блоке подстановок. В этой схеме входной регистр в каждой тетраде задает адрес для соответствующего коммутатора, который по шине данных передает из SSE-регистров информацию в выходной регистр. Это дает возможность параллельно обрабатывать сразу четыре блока по 32 бита, т.е. в параллель рассчитывать четыре криптопроцедуры.

Таким образом, благодаря предложенной реализации способа криптографического преобразования информации и реализующему этот способ устройству достигается требуемый технический результат повышения скрытности преобразования и его оперативности при программно-технической реализации способа в современных ЭВМ, поскольку оперативность и соответствующее быстродействие обеспечивается исключением использования оперативной памяти, а скрытность - за счет исключения размещения конфиденциальной информации в оперативной памяти с общим доступом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ криптографического преобразования информации | 2016 |

|

RU2630423C1 |

| СПОСОБ ИТЕРАТИВНОГО КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ | 2012 |

|

RU2504911C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ RDOZEN | 2015 |

|

RU2591015C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ DOZEN | 2012 |

|

RU2503994C1 |

| Способ формирования ключей шифрования | 2016 |

|

RU2656578C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ | 2017 |

|

RU2683689C1 |

| СПОСОБ БЛОЧНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ ДАННЫХ НА ОСНОВЕ РЕГИСТРА СДВИГА ДЛИНЫ ВОСЕМЬ С 32-БИТОВЫМИ ЯЧЕЙКАМИ И С ТРЕМЯ ОБРАТНЫМИ СВЯЗЯМИ | 2022 |

|

RU2796629C1 |

| СПОСОБ КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ В ИНФОРМАЦИОННЫХ ТЕХНОЛОГИЯХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2206182C2 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2024209C1 |

| СПОСОБ ПОТОЧНОГО ШИФРОВАНИЯ ДАННЫХ | 2005 |

|

RU2291578C1 |

Изобретение относится к способам и средствам криптографического преобразования информации в электронных вычислительных комплексах и ЭВМ. Повышение скрытности и оперативности преобразования достигается тем, что в способе, основанном на разбивке исходного 32-разрядного входного вектора на восемь последовательно идущих 4-разрядных входных векторов, каждый из которых соответствующим ему узлом замены преобразуется в 4-разрядный выходной вектор, которые последовательно объединяются в 32-разрядный выходной вектор, причем предварительно в каждом узле замены размещают таблицы преобразования из шестнадцати строк каждая, содержащих по четыре бита заполнения в строке, являющихся соответствующими 4-разрядными выходными векторами, используют четыре узла замены по одному для каждой пары 4-разрядных входных векторов, причем в каждом узле замены используют регистр центрального процессора, в который размещают по две таблицы преобразования, а преобразование пар 4-разрядных входных векторов в пары 4-разрядных выходных векторов в соответствующем узле замены осуществляют коммутацией предварительно размещенных строк таблиц преобразования в регистр центрального процессора соответствующего узла замены путем использования пар 4-разрядных входных векторов в виде адресов коммутации. В реализующем этот способ устройстве используются 32-разрядный выходной регистр, 32-разрядный входной регистр и четыре узла замены, каждый их которых содержит SSE-регистр и два коммутатора. 2 н. и 1 з.п. ф-лы, 2 ил.

1. Способ криптографического преобразования информации, основанный на разбивке исходного 32-разрядного входного вектора на восемь последовательно идущих 4-разрядных входных векторов, каждый из которых соответствующим ему узлом замены преобразуется в 4-разрядный выходной вектор, которые последовательно объединяются в 32-разрядный выходной вектор, причем предварительно в каждом узле замены размещают таблицы преобразования из шестнадцати строк каждая, содержащих по четыре бита заполнения в строке, являющихся соответствующими 4-разрядными выходными векторами, отличающийся тем, что используют четыре узла замены по одному для каждой пары 4-разрядных входных векторов, причем в каждом узле замены используют регистр центрального процессора с размером, равным или большим 16 байт, в который размещают по две таблицы преобразования, а преобразование пар 4-разрядных входных векторов в пары 4-разрядных выходных векторов в соответствующем узле замены осуществляют коммутацией предварительно размещенных строк таблиц преобразования в регистр центрального процессора соответствующего узла замены путем использования пар 4-разрядных входных векторов в виде адресов коммутации.

2. Способ по п.1, отличающийся тем, что в качестве регистров центрального процессора используют SSE-регистры.

3. Устройство для реализации способа по п.1, содержащее блок формирования информационного вектора, отличающееся тем, что введены входной 32-разрядный регистр и четыре узла замены, каждый их которых содержит SSE-регистр и два коммутатора, при этом блок формирования информационного вектора выполнен в виде 32-разрядного выходного регистра, восемь входов которого соединены с выходами соответствующих коммутаторов узлов замены, информационные входы которых соединены с выходами SSE-регистра соответствующих им узлов замены, а адресные входы соединены с соответствующими выходами входного 32-разрядного регистра.

| RU 2010110344 A, 27.09.2011 | |||

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

2013-12-27—Публикация

2012-05-29—Подача