Изобретение относится к криптографическим преобразованиям и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации.

Целью изобретения является шифрование информации блоками различной длины с использованием ключа такой длины, которая обеспечивает невозможность его опробования за разумное время.

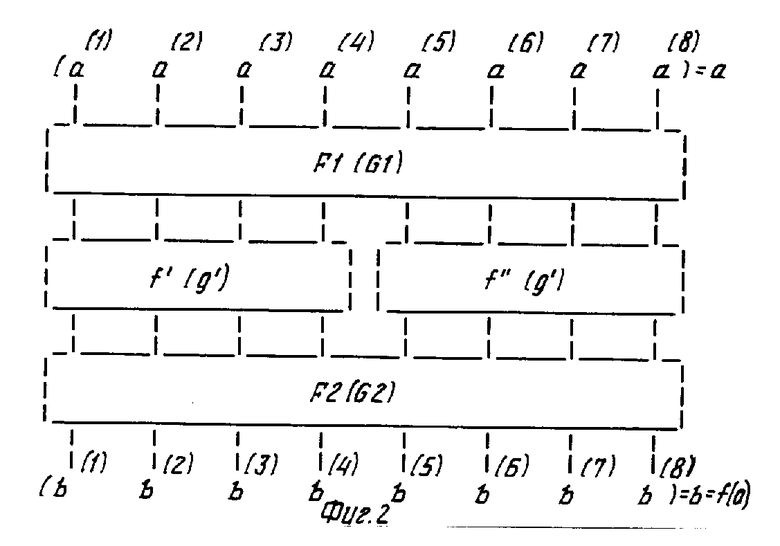

На фиг. 1 представлена блок-схема устройства шифрования двоичной информации.

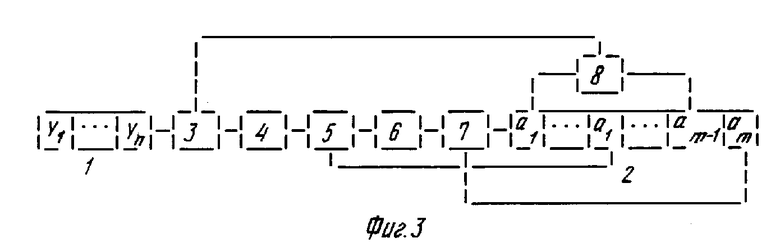

Подстановки f и g множества {0, 1 ,..., 255} реализуются либо таблицами объема 256 байт каждая, либо устройством, изображенным на фиг. 2.

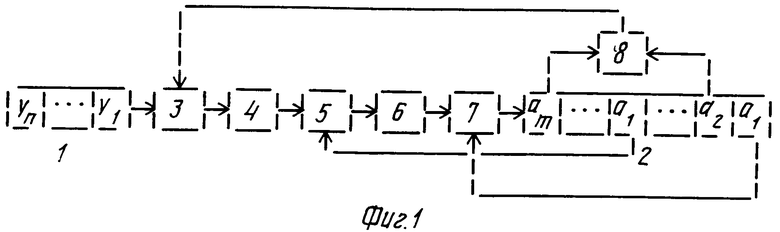

На фиг. 3 представлена структурная схема устройства расшифрования.

Устройство шифрования двоичной информации содержит 8n-разрядный ключевой регистр 1,8m-разрядный (m ⇒ 4) информационный регистр 2, первый 8-разрядный сумматор 3 по модулю 2 или 28, блок 4 8-разрядного функционального преобразования f, второй 8-разрядный сумматор 5 по модулю 2 или 28, блок 6 8-разрядного функционального преобразования g, 8-разрядный сумматор 7 по модулю 2, третий 8-разрядный сумматор 8 по модулю 2 или 28.

Устройство шифрования двоичной информации работает следующим образом.

m Байт исходной информации am, ..., a1 записываются в 8m-разрядный информационный регистр 2. Устройство шифрования работает n циклов, после которых содержимое m-байтного информационного регистра 2 является результирующей информацией. Все циклы работы устройства шифрования идентичны, В i-й цикл 1 ⇐ i ⇐ n , 2-й и m-й байты 8m-разрядного информационного регистра 2 складываются в третьем 8-разрядном сумматоре 8, сумма складывается в первом 8-разрядном сумматоре 3 с i-м байтом 8n-разрядного ключевого регистра 1, полученная сумма преобразуется блоком 4 и складывается во втором 8-разрядном сумматоре 5 с r-й (3 ≅ r ≅ m - 1) байтом 8m-разрядного информационного регистра 2, вновь полученная сумма преобразуется дополнительным блоком 6 и складывается по модулю 2 в 8-разрядном сумматоре 7 с первым байтом 8m-разрядного информационного регистра 2, последняя сумма записывается на место m-го байта в 8m-разрядный информационный регистр 2, содержимое которого предварительно сдвинуто на один байт в сторону младших байтов (вправо).

Если обозначить побайтное содержимое 8n-разрядного ключевого регистра 1 через y1, . .., yn, a 8m-разрядного информационного регистра 2 в i-й цикл через а1(i), ..., am(i), то в i + 1-й цикл содержимое 8m-разрядного информационного регистра 2 станет

am(i+1) = g(f(a2(i)+am(i)+yi)+ar(i))⊕ a1(i),

am-1(i+1) = am(i), .... ,a1(i+1) = a2(i), где знак "+" - сложение по модулю 2 или 28 в зависимости от выбранного сумматора;

знак ⊕ - сложение по модулю 2;

f и g - подстановки степени 28,

am(1), ..., a1(1) - исходная информация,

am(n + 1), ..., a1(n + 1) - результирующая информация.

Например, если выбрать f = g, а первый, второй и третий 8-разрядные сумматоры 3, 5, 8 - по модулю 28, то устройство шифрования за один цикл будет реализовать следующее преобразование

am(i+1) = f(f(a2(i) am(i)

am(i) Yi)

Yi) ar(i))⊕ai(i) ,

ar(i))⊕ai(i) ,

am-1(i+1) = am(i), ..., a1(i+1) = a2(i), где знак  - сложение по модулю 28.

- сложение по модулю 28.

Рекомендуется длину m-разрядного информационного регистра 2 выбирать в пределах от 4 до 8 байт. Реальная длина ключа (значение t) от 4 до 32 байт. Длину n 8n-разрядного ключевого регистра 1 рекомендуется выбирать от 32 до 64 байт при 4 ⇐ t ⇐ 16 и от 64 до 128 байт при 17 ⇐ t ⇐ 32 .

n байт y1, ..., yn заполнения 8n-разрядного ключевого регистра 1 формируются из t байт ключа х1, ..., хt, например, следующим образом:

y1,..., yn = xi1, xi2, ..., xin где {i1, i2, ..., in} Э {1, 2, ..., t},

ij∈ {1,2, ...., t}, 1 ⇐ j ⇐ n ,

Например, при 16-байтном исходном ключе х1, х2, ..., х16 в 32-байтный ключевой регистр 1 можно записать 32 байта

х1, х2, ..., х16,

х1, х4, х7, х10, х13, х16, х3, х6, х9, х12, х15, х2, х5, х8, х11, х14

Чтобы существенно усложнить процедуру получения какой-либо информации о ключе, рекомендуется заполнение n-байтного ключевого регистра 1 формировать более сложно с использованием самого устройства шифрования, а именно

/yn, ... y1/ = / n+1/, ...

n+1/, ...  n+1// =

n+1// =  +1/ ,

+1/ ,

/y2m, ... ym+1/ = / n+1/, ...

n+1/, ...  n+1// =

n+1// =  +1/ ,

+1/ ,

. . . . . . .

/ . . . , yn, . . . ysm+1/ = / n+1/, ... ,

n+1/, ... ,  n+1// =

n+1// =  +1/ : где а(1)/n+1/, . . ., a(s)/n+1/ - содержимые 8m-разрядного информационного регистра 2 после n циклов работы устройства шифрования, если в 8m-разрядный информационный регистр 2 установлены попарно различные m-байтные исходные состояния а(1)/1/, а(2)/1/, ..., а(s)/1/, а в 8n-разрядный ключевой регистр 1 записаны n байт хi1, xi2, ..., xin.

+1/ : где а(1)/n+1/, . . ., a(s)/n+1/ - содержимые 8m-разрядного информационного регистра 2 после n циклов работы устройства шифрования, если в 8m-разрядный информационный регистр 2 установлены попарно различные m-байтные исходные состояния а(1)/1/, а(2)/1/, ..., а(s)/1/, а в 8n-разрядный ключевой регистр 1 записаны n байт хi1, xi2, ..., xin.

Значение s должно удовлетворять неравенству sm ⇒ n . Например, если n = 32, то s = 4 при m = 8, s = 5 при m = 7 и т.д.

Другими словами, сначала устройство шифрования вырабатывает содержимое 8n-разрядного ключевого регистра 1, а затем уже обрабатывает исходную информацию. Работу по выработке содержимого 8n-разрядного ключевого регистра 1 можно проделать заранее.

Подобным образом можно обновлять заполнение 8n-разрядного ключевого регистра 1 при каждом очередном сеансе связи или периодически в определенные моменты времени. Для этого в 8n-разрядный ключевой регистр 1 записываются ранее выработанные n байт y1, ..., yn, а в 8m-разрядный информационный регистр 2-последовательно различные исходные состояния, содержащие фиксированную отличительную информацию данного акта выработки нового заполнения ключевого регистра. Например, / = /T, 0000/,

/ = /T, 0000/,  / = /T,0001/, ...

/ = /T,0001/, ...  = /T,1111/ , где Т - это, например, реальное время выработки ключа, занимающее 8m - 4 двоичных разрядов. В младшие четыре разряда записываются комбинации 0000, 0001, 0010, ...

= /T,1111/ , где Т - это, например, реальное время выработки ключа, занимающее 8m - 4 двоичных разрядов. В младшие четыре разряда записываются комбинации 0000, 0001, 0010, ...

Полученные результирующие состояния 8m-разрядного информационного регистра 2 используются устройством шифрования в качестве n-байтного заполнения ключевого регистра для очередного сеанса связи или на очередной промежуток времени.

Подстановки f и g множества /0, 1, ..., 255/ (взаимно однозначные функции 28-значной логики) реализуются либо устройством, изображенным на фиг. 2, либо таблично с использованием памяти объема 256 байт.

На фиг. 2:

a =  ...

...  b = /

b = / ...

...  {0,1 ... 255/}

{0,1 ... 255/}

0,1/},1⇐ j ⇐ 8 ,

0,1/},1⇐ j ⇐ 8 ,

F1, F2, G1, G2 - перестановки бит в байте,

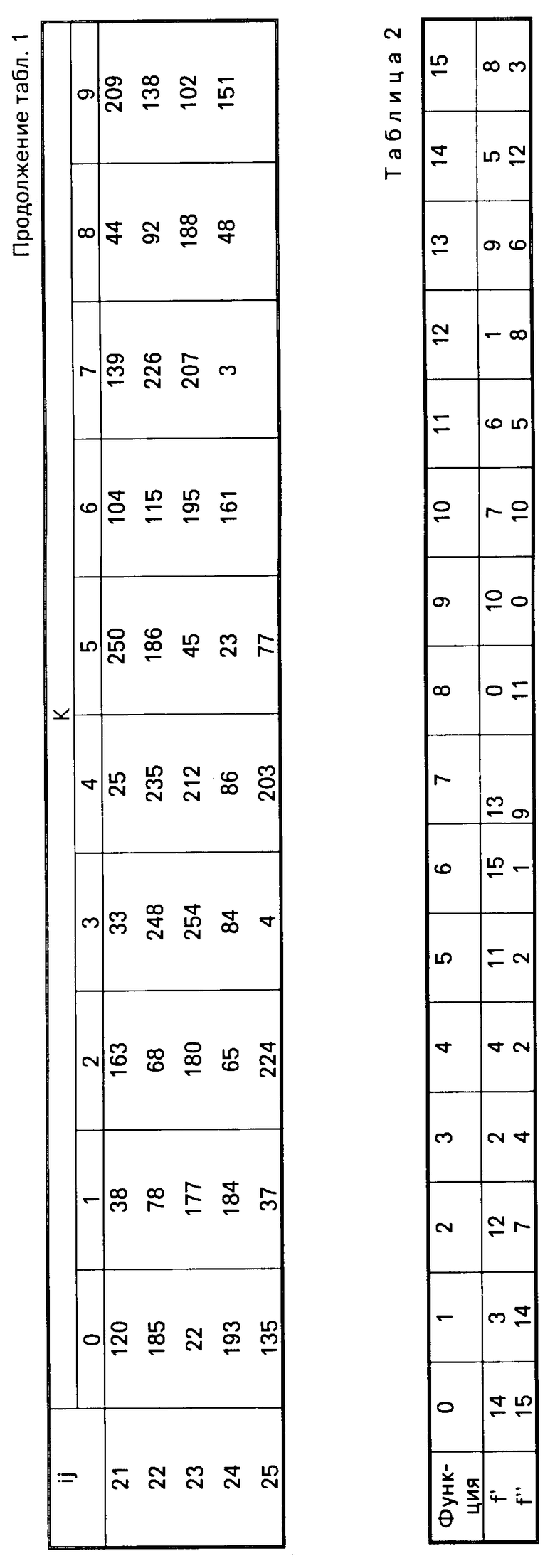

f', f'', g', g'' - подстановки множества /0, 1, ..., 15/ (взаимно однозначные функции 24-значной логики), реализуемые таблично с использованием двух массивов памяти по 16 полубайт каждый либо аппаратным воспроизведением соответствующих дизъюнктивных форм.

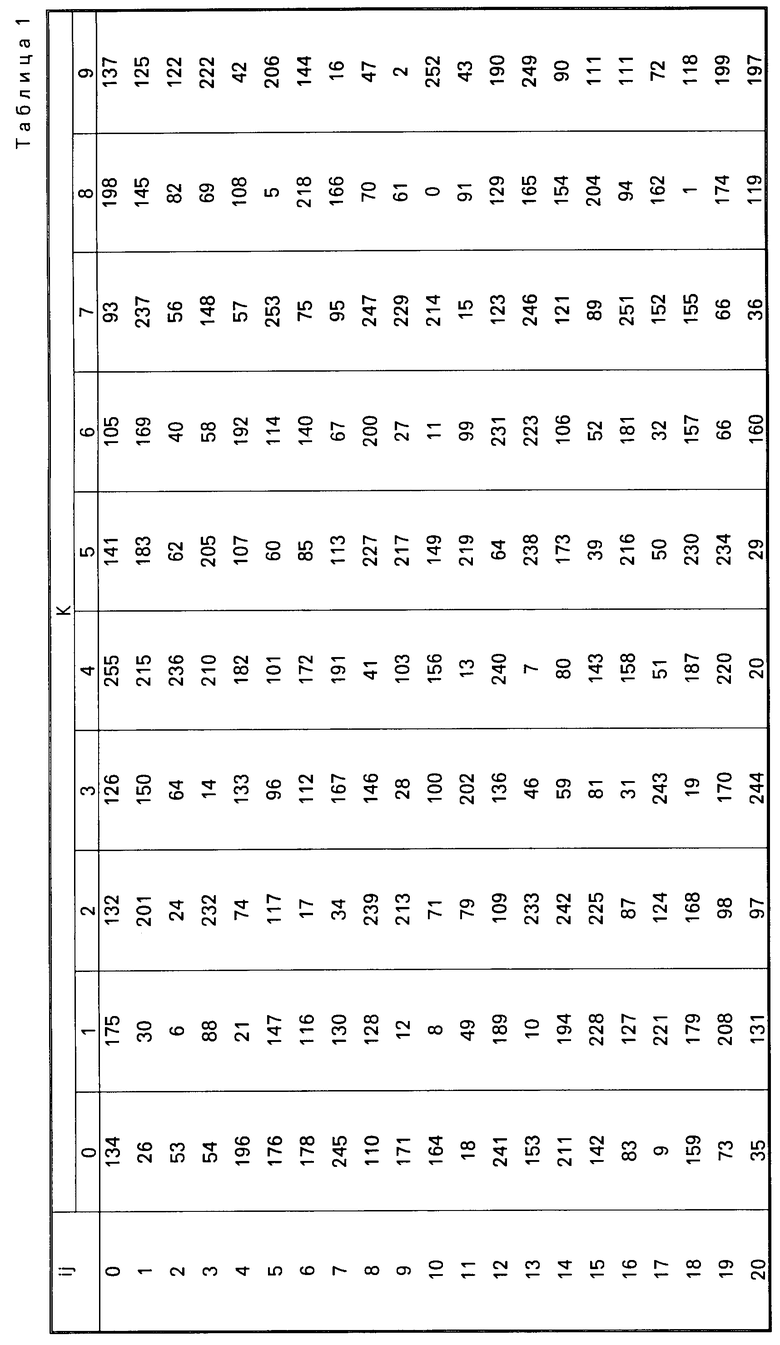

При табличной реализации подстановки f можно выбрать, например, табл. 1, в которой значение функции f(ijk), где ijk - десятичная запись аргумента, находится на пересечении строки ij и столбца k.

При реализации подстановки f устройством, изображенным на фиг. 2, можно выбрать функции f' и f'', задаваемые табл. 2 и следующие перестановки бит в байте:

F1=

, F2=

, F2=

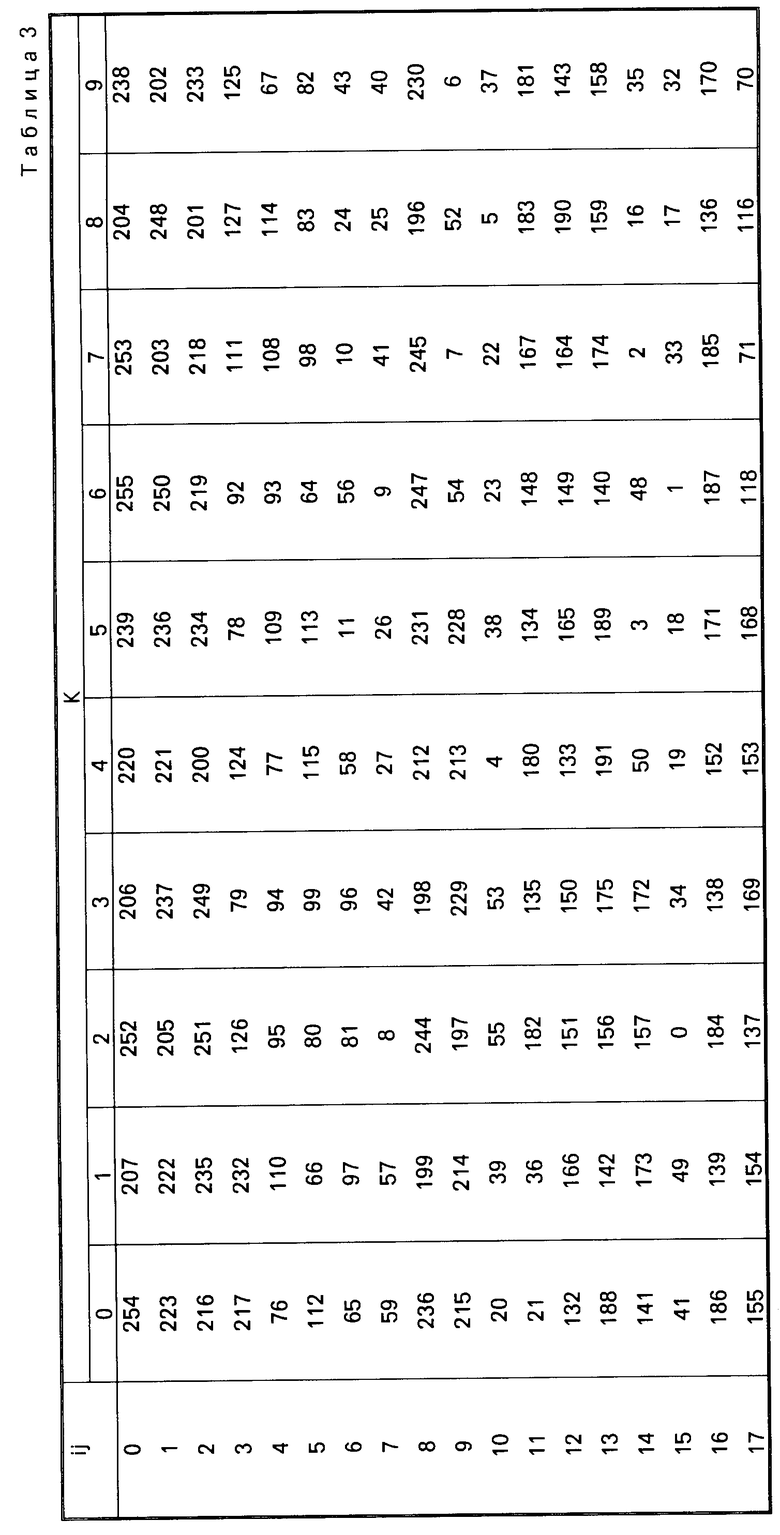

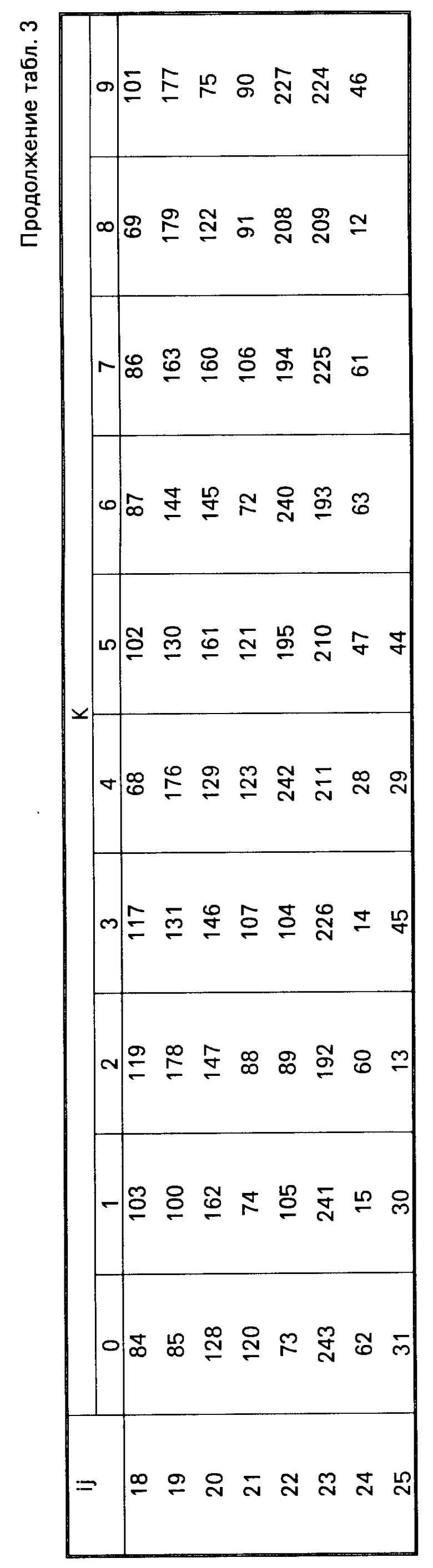

В этом случае результирующая подстановка f будет задаваться табл. 3.

Устройство шифрования реализует шифры гаммирования и замены.

В случае шифра гаммирования в качестве последовательности блоков исходной информации, записываемых в 8n-разрядный информационный регистр 2, используются любые отличающиеся друг от друга состояния этого регистра. Вырабатываемые биты результирующих состояний прибавляются по модулю 2 к битам шифруемого сообщения, т.е.

Ш = O ⊕ A, где О - открытая информация,

Ш - зашифрованная информация,

А - результирующее состояние 8m-разрядного информационного регистра 2.

Формировать различные исходные состояния 8m-разрядного информационного регистра 2 можно рекуррентным способом, например, при помощи N-разрядного двоичного регистра сдвига максимального периода 2N-1 с линейной функцией в обратной связи. В качестве исходных состояний 8m-разрядного информационного регистра 2 используются заполнения младших 8m двоичных разрядов (либо все заполнение, если N N ⇐ 8m) 8m) регистра сдвига после его очередного сдвига на один разряд.

Если очередное состояние регистра сдвига обозначить через

...

...  где

где  0,1.., i =

0,1.., i =  , то следующее состояние примет вид

, то следующее состояние примет вид . . .

. . .

c2

c2 ...⊕ c

...⊕ c ci= 0,1, i =

ci= 0,1, i =  Коэффициенты с2, ..., сN выбираются так, чтобы обеспечить максимальный период регистра сдвига. Например,

Коэффициенты с2, ..., сN выбираются так, чтобы обеспечить максимальный период регистра сдвига. Например,

при N = 63 c2 = 1, ci = 0 i = 2

Начальное состояние регистра сдвига формируется устройством шифрования тем же способом, что и заполнение 8n-разрядного ключевого регистра 1. Такая процедура предварительного шифрования начального состояния лишает пытающегося расшифровать сообщение аналитика информации об исходных состояниях 8m-разрядного информационного регистра 2.

В случае шифра замены 8m бит открытой информации записываются в 8m-разрядный информационный регистр 2 и соответствующее результирующее состояние 8m-разрядного информационного регистра 2 - это зашифрованная информация. Расшифрование зашифрованной информации осуществляется устройством расшифрования, изображенным на фиг. 2. Устройство расшифрования содержит те же блоки, что и устройство шифрования. Информация в ключевой и информационный регистры 1 и 2 устройства расшифрования записывается в порядке, обратном принятому в устройстве шифрования. При m = 8, r = 5, m = 6, r = 4, m = 4 устройства шифрования и расшифрования идентичны.

Если в устройстве шифрования использовать 16-байтный или более длинный ключ, это сделает абсолютно невозможным его опробование за приемлемое время. Информационный регистр можно выбрать разной длины, что позволяет шифровать информацию блоками от 4 до 8 и более байт. При длине блока 8, 6 , 4 точки съема в информационном регистре можно выбрать так, чтобы устройства шифрования и расшифрования совпадали.

Заполнение 8n-разрядного ключевого регистра можно формировать из t байт ключа при помощи самого устройства шифрования криптографически сложным способом и затем таким же способом периодически обновлять во время работы.

В режиме гаммирования заполнения 8m-разрядного информационного регистра можно формировать рекуррентным способом при помощи N-разрядного двоичного регистра, начальное состояние которого с целью скрытия его от окружающих вырабатывается самим устройством шифрования и зависит от ключа.

Использование: в криптографических преобразованиях в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Сущность изобретения: устройство содержит n-разрядный ключевой регистр 1, m-разрядный информационный регистр 2, первый, второй, третий 8-разрядные сумматоры 3, 5, 8 по модулю 28 , блок 4 8-разрядного функционального преобразователя f, блок 6 8-разрядного функционального преобразования 9, 8-разрядный сумматор 7 по модулю два. Устройство обеспечивает изменения конструктивных параметров применительно к условиям эксплуатации. Пользователь может выбирать длину ключа, длину шифруемого блока, количество циклов обработки информации, внутреннюю логическую схему, включая функциональные преобразования. 3 ил., 3 табл.

Устройство шифрования двоичной информации, содержащее ключевой регистр, блок многоразрядного функционального преобразования f, последовательно соединенные многоразрядный сумматор по модулю два и информационный регистр, первый многоразрядный выход которого подключен к первому входу многоразрядного сумматора по модулю два, отличающееся тем, что в нем ключевой регистр выполнен в виде 8 n-разрядного ключевого регистра, информационный регистр - в виде 8 m-разрядного информационного регистра, многоразрядный сумматор по модулю два - в виде 8-разрядного сумматора по модулю два, блок многоразрядного функциального преобразования - в виде блока 8-разрядного функционального преобразования, при этом в него введены первый, второй и третий 8-разрядные сумматоры и блок 8-разрядного функционального преобразования g, выход которого подключен к второму входу 8-разрядного сумматора по модулю два, при этом выход 8 n-разрядного ключевого регистра подключен к первому входу первого 8-разрядного сумматора, к второму входу которого подключен выход третьего 8-разрядного сумматора, к первому и второму входам которого подключены соответственно m-й и второй 8-разрядный выходы 8m-разрядного информационного регистра, r-й (3 ≅ r ≅ m - 1) 8-разрядный выход которого подключен к первому входу второго 8-разрядного сумматора, первый вход которого и выход подключены соответственно к выходу блока 8-разрядного функционального преобразователя f и входу блока 8-разрядного функционального преобразования g, выход первого 8-разрядного сумматора подключен к входу блока 8-разрядного функционального преобразования f.

| Сяо Д., Керр Д | |||

| и С.Мэдник | |||

| Защита ЭВМ | |||

| М:Мир, 1982,с.137-162. |

Авторы

Даты

1994-11-30—Публикация

1991-10-30—Подача