Изобретение относится к области вычислительной техники и может использоваться в микропроцессорных системах с подсистемами памяти, где необходимо высокое быстродействие.

Известен способ копирования данных, использующий стандартные команды микропроцессора и реализованный в операционной системе Linux.

Известен также способ и устройство, производящее копирование данных из одной области памяти в другую, при этом адреса обоих областей памяти задаются (определяются) одной командой. Контроллер получает значения начальных и конечных адресов областей памяти, предназначенных для копирования из одной области в другую, и производит копирование данных от начального адреса до конечного (Заявка US №2004/0049649, Кл. G06F 12/00, опубл. 11.03.2004).

Известен способ и устройство, производящее копирование данных из одной области памяти в другую без использования инструкций загрузки/сохранения данных, оперируя значениями начальных и конечных адресов областей памяти, предназначенных для копирования из одной области в другую, и счетчиком, показывающим количество одиночных операций копирования данных (Заявка US 2010/1099054, Кл. G06F 12/00, опубл. 2010).

Недостатком описанных выше способов и устройств копирования данных является сложность осуществления данных способов из-за отсутствия из пользовательского приложения прямого доступа к системному контроллеру, выполняющему операции копирования. Наиболее близким по технической сути и достигаемому техническому результату является способ копирования данных, включающий вычисление виртуальных адресов для чтения по адресу источника данных и записи по адресу приемника данных по инструкции, трансляцию виртуальных адресов источника и приемника данных в физические адреса, обращение по ним в кэш-память первого уровня и кэш-память второго уровня и загрузку данных по адресу источника данных из внешней памяти в кэш-память первого и второго уровней, и устройство, осуществляющее способ, включающее сумматор адресов, блок трансляции адресов, кэш-память первого и второго уровней и внешнюю память (Патент RU №2359315, Кл. G06F 9/30, опубл. 2008).

Недостатком описанного способа и устройства является низкая производительность системы, в частности низкая скорость копирования данных из памяти в память, так как размер данных, пересылаемых с использованием регистрового файла, меньше размера строк кэш-памяти первого и второго уровней и для пересылки одной строки требуется выполнить несколько последовательных операций загрузки/сохранения.

Технический результат от использования данного изобретения состоит в повышении скорости копирования данных, путем прямой записи копируемых данных, не используя регистровый файл.

Указанный технический результат достигается тем, что в способе копирования данных, включающем вычисление виртуальных адресов для чтения по адресу источника данных и записи по адресу приемника данных по инструкции, трансляцию виртуальных адресов источника и приемника данных в физические адреса, обращение по ним в кэш-память первого уровня и кэш-память второго уровня и загрузку данных по адресу источника данных из внешней памяти в кэш-память первого и второго уровней, согласно изобретению добавляют инструкцию, проводящую копирование целой кэш-линии в кэш-памяти первого и второго уровней, не используя пересылку данных через регистры процессора, причем виртуальные адреса источника данных для чтения и приемника данных для записи формируют последовательно, затем транслируют их в физические адреса для обращения в кэш-память первого и второго уровней, при этом данные, загруженные по адресу источника данных в объеме одной кэш-линии, записывают в кэш-память первого и второго уровней по адресу приемника данных. Способ осуществляется устройством, включающим сумматор адресов, блок трансляции адресов, кэш-память первого и второго уровней и внешнюю память, в котором согласно изобретению кэш-память первого уровня имеет блок мультиплексирования входных данных, связанный с внешней памятью и кэш-памятью второго уровня, для выбора данных для записи в кэш-память первого уровня, а кэш-память второго уровня содержит блок мультиплексирования входных данных, связанный с внешней памятью и кэш-памятью второго уровня, для выбора данных для записи в кэш-память второго уровня.

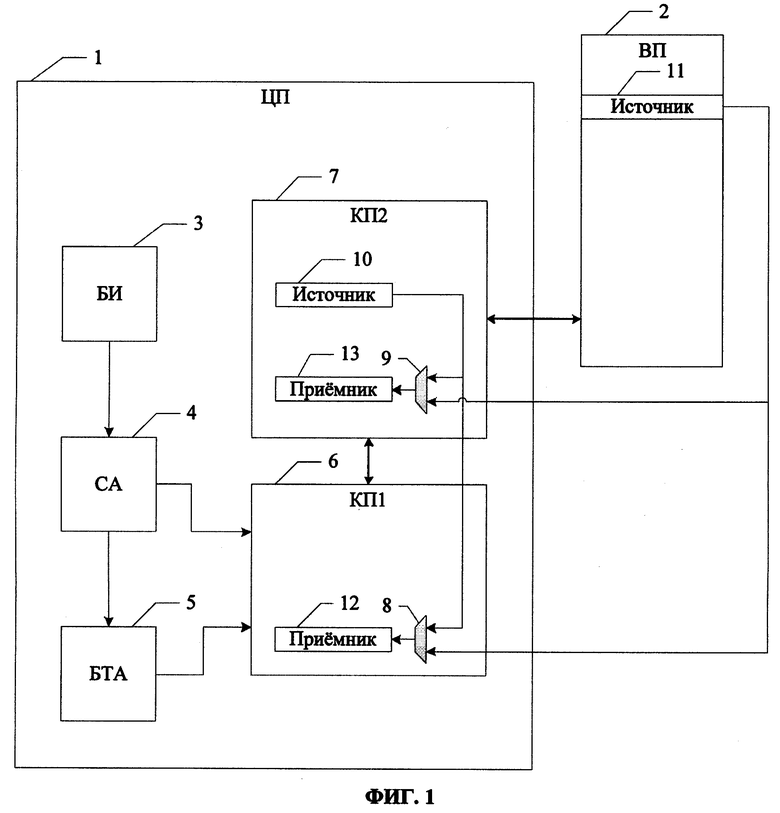

Изобретение поясняется чертежом, на котором представлена схема копирования памяти.

Устройство состоит из центрального процессора (ЦП) 1 и внешней памяти (ВП) 2. Процессор состоит из буфера инструкций (БИ) 3, сумматора адресов (СА) 4, блока трансляции адресов (БТА) 5, подсистема памяти состоит из кэш-памяти первого уровня (КП1) 6 и кэш-памяти второго уровня (КП2) 7, включающих блоки мультиплексирования входных данных 8 и 9 соответственно. В подсистеме памяти имеются ячейки памяти по адресам источника данных 10 в блоке КП2 7 и 11 в блоке ВП 2 и ячейки по адресам приемника данных 12 в блоке КП1 6 и 13 в блоке КП2 7.

Копирование данных по способу при помощи описанного выше устройства осуществляют следующим образом. К набору инструкций устройства добавляют новую инструкцию копирования кэш-линии. Выполняя программу, декодируют инструкцию копирования кэш-линии, буфером инструкций (БИ) 3, посредством которого разбивают ее на две, последовательно подаваемые такты на сумматор адресов (СА) 4. В сумматоре адресов (СА) 4 вычисляют виртуальные адреса и передают их на блок трансляции адресов (БТА) 5, и транслируют их в физические адреса. Первый из полученных адресов интерпретируют как адрес источника данных, второй (в следующем такте) - как адрес приемника данных.

По адресам источника данных (виртуальному с выхода сумматора адресов (СА) 4 и физическому с выхода блока трансляции адресов (БТА) 5) обращаются в кэш-память первого (КП1) 6 и второго (КП2) 7 уровней и во внешнюю память (ВП) 2. Виртуальный адрес используют для адресации кэш-памяти первого (КП1) 6 и второго (КП2) 7 уровней, а физический - для проверки тегов и обращений во внешнюю память (ВП) 2.

В случае, если данные по адресу источника данных есть в кэш-памяти второго уровня (КП2) 7, то производят чтение всей строки кэш-линии. В противном случае, обращаются во внешнюю память (ВП) 2 по адресу источника данных 11. Чтение по адресу источника данных из внешней памяти производят шириной в кэш-линию. На следующем такте прочитанные данные подают на вход мультиплексоров данных 8 и 9 в кэш-памяти первого (КП1) 6 и второго (КП2) 7 уровней соответственно для записи их по адресу приемника данных 12 и 13.

Посредством мультиплексоров 8 и 9 выбирают данные, считанные из кэш-памяти второго уровня (КП2) 7 (источник 10) или из внешней памяти (ВП) 2 (источник 11) в зависимости от попадания (или промаха) в кэш-память второго уровня (КП2) 7. Данные, выбранные мультиплексорами 8 и 9, записывают по адресу приемника данных 12 в кэш-память первого уровня (КП1) 6 и по адресу приемника данных 13 в кэш-память второго уровня (КП2) 7. Запись производят по виртуальному адресу приемника данных, полученному с выхода сумматора адресов (СА) 4, с использованием для записи тегов физического адреса приемника данных, полученному с выхода блока трансляции адресов (БТА) 5.

Описанные способ и устройство позволяют копировать данные размером, кратным одной кэш-линии, по невыровненным на границу кэш-линии адресам, производя чтение данных из двух кэш-линий подряд (по адресу источника) и используя мультиплексоры 8 и 9 для сдвига записываемых данных (по адресу приемника).

Описанные способ и устройство позволяют повысить производительность операций копирования данных по сравнению с известными способами и подсистемами памяти. Использование копирования по невыровненным на границу кэш-линии адресам позволяет использовать единую процедуру копирования для данных с любого адреса с точностью до одного байта размером, кратным размеру кэш-линии.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВА ОБРАБОТКИ ВИРТУАЛИЗАЦИИ И КОМПЬЮТЕРНАЯ СИСТЕМА | 2012 |

|

RU2573219C2 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УСТАНОВКИ ПОЛИТИКИ КЭШИРОВАНИЯ В ПРОЦЕССОРЕ | 2008 |

|

RU2427892C2 |

| ГИБРИДНЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2556364C1 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| СПОСОБ И УСТРОЙСТВО ТРАНСЛЯЦИИ АДРЕСА | 2008 |

|

RU2461870C2 |

| УНИФИЦИРОВАННЫЙ ДОСТУП К СОВМЕСТНО ИСПОЛЬЗУЕМОЙ И УПРАВЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2641244C2 |

| УСТРОЙСТВО ПРИВОДА ОПТИЧЕСКОГО ДИСКА | 2009 |

|

RU2440629C1 |

| УСТАНОВКА, СПОСОБ И СИСТЕМА КЭШИРОВАНИЯ | 2008 |

|

RU2483347C2 |

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА УМЕНЬШЕНИЯ ВРЕМЕНИ ВОЗОБНОВЛЕНИЯ РАБОТЫ ДЛЯ КОРНЕВЫХ ПОРТОВ И КОНЕЧНЫХ ТОЧЕК, ИНТЕГРИРОВАННЫХ В КОРНЕВЫЕ ПОРТЫ | 2014 |

|

RU2645596C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении скорости копирования данных, путем прямой записи копируемых данных, не используя регистровый файл. Способ копирования данных включает вычисление виртуальных адресов для чтения по адресу источника данных и записи по адресу приемника данных по инструкции, трансляцию виртуальных адресов источника и приемника данных в физические адреса, обращение по ним в кэш-память первого уровня и кэш-память второго уровня и загрузку данных по адресу источника данных из внешней памяти в кэш-память первого и второго уровней, причем добавляют инструкцию, проводящую копирование целой кэш-линии в кэш-памяти первого и второго уровней, не используя пересылку данных через регистры процессора, причем виртуальные адреса источника данных для чтения и приемника данных для записи формируют последовательно, затем транслируют их в физические адреса для обращения в кэш-память первого и второго уровней, при этом данные, загруженные по адресу источника данных в объеме одной кэш-линии, записывают в кэш-память первого и второго уровней по адресу приемника данных. 2 н.п. ф-лы, 1 ил.

1. Способ копирования данных, включающий вычисление виртуальных адресов для чтения по адресу источника данных и записи по адресу приемника данных по инструкции, трансляцию виртуальных адресов источника и приемника данных в физические адреса, обращение по ним в кэш-память первого уровня и кэш-память второго уровня и загрузку данных по адресу источника данных из внешней памяти в кэш-память первого и второго уровней, отличающийся тем, что добавляют инструкцию, проводящую копирование целой кэш-линии в кэш-памяти первого и второго уровней, не используя пересылку данных через регистры процессора, причем виртуальные адреса источника данных для чтения и приемника данных для записи формируют последовательно, затем транслируют их в физические адреса для обращения в кэш-память первого и второго уровней, при этом данные, загруженные по адресу источника данных в объеме одной кэш-линии, записывают в кэш-память первого и второго уровней по адресу приемника данных.

2. Устройство для осуществления способа по п.1, включающее сумматор адресов, блок трансляции адресов, кэш-память первого и второго уровней и внешнюю память, отличающееся тем, что кэш-память первого уровня дополнительно имеет блок мультиплексирования входных данных, связанный с внешней памятью и кэш-памятью второго уровня, для выбора данных для записи в кэш-память первого уровня, а кэш-память второго уровня имеет блок мультиплексирования входных данных, связанный с внешней памятью и кэш-памятью второго уровня, для выбора данных для записи в кэш-память второго уровня.

| US 7310712 B1, 18.12.2007 | |||

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| US 6970976 B1, 29.11.2005 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 7330958 B2, 12.02.2008 | |||

| US 7278008 B1, 02.10.2007. | |||

Авторы

Даты

2014-01-10—Публикация

2012-07-20—Подача