Изобретение относится к области вычислительной техники и может использоваться в микропроцессорных системах с подсистемами памяти, где необходимо высокое быстродействие.

Известен блок управления памятью в составе гибридного микропроцессора, включающего центральный процессор, системный контроллер, внешнюю память, двухуровневую кэш-память (Патент RU №2359315, кл. G06F 9/30, опубл. 20.06.2009).

Недостатком описанного блока является низкая производительность системы, низкая ее помехоустойчивость.

Наиболее близким по технической сути и достигаемому техническому результату является подсистема памяти, связанная с центральным процессором, системным контроллером, внешней памятью и включающая кэш-память, набор буферов данных и инструкций, состоящий из буфера для сохраняемых данных, буфера для обратных записей и буфера для загружаемых данных (Патент US №2010/0211746 А1, кл. G06F 12/08, опубл. 16.02.2010).

Недостатком описанной подсистемы памяти ядра микропроцессора является низкая производительность системы, низкая помехоустойчивость системы, не решена задача ускорения загрузки данных из основной памяти в кэш-память; при чтении по адресам данных, содержащихся в буфере для сохраняемых данных, данные сначала будут выгружены в кэш-память и только затем будут считаны в буфер для загружаемых данных, что приводит к дополнительным задержкам.

Технический результат от использования данного изобретения состоит в повышении производительности устройства, повышении помехоустойчивости системы и исключении дополнительных задержек при считывании и загрузке данных.

Указанный технический результат достигается тем, что в подсистеме памяти, связанной с центральным процессором, системным контроллером внешней памятью и включающей кэш-память, набор буферов данных и инструкций, состоящей из буфера для сохраняемых данных, буфера для обратных записей, буфера для загружаемых данных, подсистема содержит дополнительные буферы для сохраняемых данных, при этом кэш-память выполнена двухуровневой, первый уровень которой соединен с центральным процессором, кэш-памятью второго уровня и буфером для обратных записей, а второй уровень соединен с буферами для сохраняемых данных, с буфером для загружаемых данных и буфером для обратных записей, причем буфер для сохраняемых данных, попавших в кэш память второго уровня, содержит биты четности для помехоустойчивого кодирования и имеет связь с буфером для обратных записей,

а также тем, что кэш-память первого уровня содержит память данных и память для инструкций, которая связана с буфером для обратных записей,

и тем, что буфер для загружаемых данных расположен между кэш-памятью второго уровня и системным контроллером.

Наличие буфера для загружаемых данных, расположенного между кэш-памятью второго уровня и системным контроллером, благодаря предварительной выборке позволяет избежать задержек при чтении данных из памяти. Наличие буферов для сохраняемых данных позволяет без дополнительных задержек обрабатывать команды сохранения следующие подряд. Наличие битов четности в буфере для сохраняемых данных повышает помехоустойчивость системы.

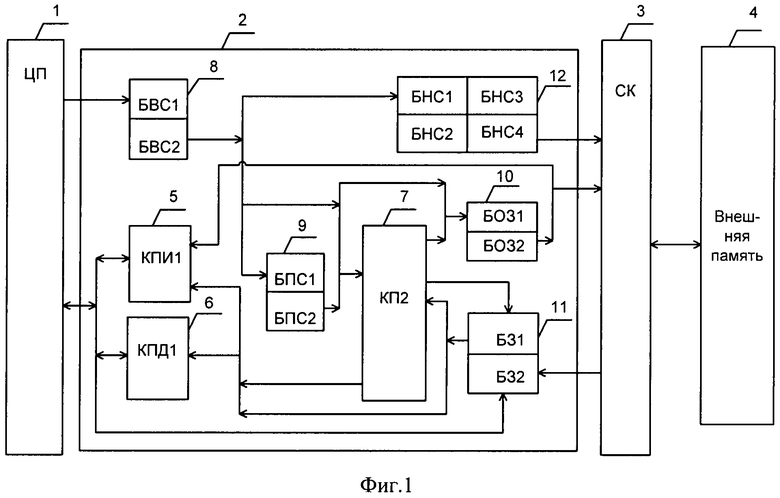

Изобретение поясняется чертежом, где на фиг.1 изображена блок-схема вычислительной системы, включающей подсистему памяти микропроцессорной системы.

Вычислительная система состоит из центрального процессора (ЦП) 1, подсистемы памяти ядра микропроцессора 2, системного контроллера (СК) 3 и внешней памяти 4. Подсистема памяти ядра микропроцессора 2 состоит из кэш-памяти первого уровня инструкций (КПИ1) 5 и данных (КПД1) 6, кэш-памяти второго уровня (КП2) 7 и интеллектуальных буферов для данных и инструкций 8, 9, 10, 11, 12.

Подсистема памяти ядра микропроцессора работает следующим образом. При декодировании ЦП 1 команды сохранения данные с выхода ЦП подаются на вход входного буфера для сохраняемых данных (БВС) 8, состоящего из двух ячеек БВС1 и БВС2. В рассматриваемом случае ячейки имеют размер 64 разряда. Данные записываются в свободную ячейку, если заняты обе, запись данных будет задержана, пока не освободится одна из ячеек. Одновременно с записью данных в ячейку БВС1 или БВС2 проверяется наличие запрашиваемой строки в КПД1 6 и КП2 7.

В случае обнаружения запрашиваемой строки в КП2 7 (то есть зафиксировано попадание в КП2 7), данные с выхода буфера 7 подаются на вход буфера для попавших в кэш-память второго уровня данных (БПС) 9, состоящего в данном случае из двух ячеек по 128 бит, то есть по половине кэш-линии. Это ограничение связано с тем, что за один такт в память данных КП2 7 возможна запись не более чем 128 бит. Буфер содержит биты четности для помехоустойчивого кодирования (код Хэмминга или модифицированный код Хэмминга-Хсяо). Так же как и для буфера 8 выбирается свободная ячейка буфера 9 БПС1 или БПС2. При освобождении памяти данных КП2 7 с выхода буфера БПС 9 будет выдана хранящаяся в нем информация на вход КП2 7. В буфере присутствует механизм «склейки», который позволяет объединять данные от двух и более разных запросов по соседним адресам в одной ячейке (при условии, что все эти запросы идут в одну половину строки КП2). Это позволяет сократить количество тактов записи, в отличие от буфера без «склейки», в котором подобные обращения обрабатываются за два и более тактов. БПС 9 также позволяет сократить время обработки запроса для ситуации обратной записи в условиях большой плотности следования команд сохранения. При поступлении запроса на загрузку/сохранение с промахом в КП2 7, требующего обратной записи в память, в случае отсутствия БПС 9 необходимо сначала произвести запись всех данных от предыдущих запросов на сохранение и только затем считать из КП2 7 данные для обратной записи. БПС 9 позволяет отложить запись данных в КП2 7 от предыдущих команд сохранения и немедленно считать данные для обратной записи. Если хотя бы в одной ячейке БПС1 или БПС2 находятся данные по адресу обратной записи, буфер напрямую выдает их на шину с выхода БПС 9 на вход БОЗ 10, минуя стадию записи в память данных КП2 7. Затем ячейка БПС1 или БПС2 помечается как недействительная для того, чтобы избежать лишней записи в память данных КП2 7. В БПС 9 имеется функция «прослушивания», т.е. определения того, нужны ли данные и тэги (в случае команды CACHE), находящиеся в ячейках буфера БПС1 или БПС2 для обработки текущего запроса. При этом, если данные также будут обнаружены в КПД1 6, то записаны они будут в КПД1 6 с выхода ЦП 1.

В случае не обнаружения запрашиваемой строки в КП2 7, но обнаружения ее в КПД1 6 (то есть зафиксировано попадание в КПД1 6 и не попадание в КП2 7), данные с выхода буфера БВС 8 поступают на вход буфера для не попавших или некэшируемых сохраняемых данных (БНС) 12 в одну из четырех 64-разрядных свободных ячеек БНС1-БНС4.

В случае не обнаружения запрашиваемой строки в КП2 7 и КПД1 6 (то есть зафиксировано не попадание в КПД1 6 и КП2 7), данные находятся в буфере БВС 8 до тех пор, пока строка из памяти 4 не подтянется в КП2 7, затем данные с выхода буфера БВС 8 поступают на вход КП2 7.

При обращении на запись с некэшируемой политикой, данные с выхода буфера БВС 8 поступают на вход буфера для не попавших или некэшируемых сохраняемых данных (БНС) 12. Выход буфера БНС 12 связан с входом СК 3.

В случае обратной записи данные с выхода КП2 7 будут поданы на вход буфера для обратных записей (БОЗ) 10, где будет выбрана одна из свободных ячеек БОЗ1 или БОЗ2. Каждая ячейка рассчитана на 64 бита данных. Выход буфера связан со входом СК 3. Если в БОЗ1 или БОЗ2 будут обнаружены инструкции, запрашиваемые ЦП 1, то с выхода БОЗ10 они будут поданы на вход КПИ1 5. Буфер позволяет не блокировать следующие запросы при единичной обратной записи. При этом, если заполнены обе ячейки БОЗ1 и БОЗ2, поступление следующих команд загрузки/сохранения задерживается до того момента, пока данные от первого запроса не будут записаны во внешнюю память 4.

При запрашивании ЦП 1 данных не попавшие в КПД1 6 запросы подаются в КП2 7 и на вход буфера для загружаемых данных (БЗ) 11. После трех идущих подряд не попавших в КП2 7 запросов и при поступлении в КПД1 6 двух подряд не попавших запросов на загрузку данных буфер выполняет предвыборку данных. В первом случае буфер БЗ 11 анализирует входные запросы и считает количество промахов в КП2 7, после трех подряд не попавших запросов БЗ 11 вычисляет следующий адрес и передает данные по предсказанному адресу с выхода СК 3 на вход БЗ 11. В другом случае второй запрос передается в БЗ 11 до завершения обработки первого запроса, и только после этого буфер БЗ 11 проверят наличие данных для второго запроса в КП2 7, если данные отсутствуют в КП2, то БЗ 11 начинает предварительную выборку данных с выхода СК 3 на вход БЗ 11. Начитав данные, БЗ 11 ожидает запроса от ЦП 1 или КПД 1 6 на их загрузку. Если адрес следующего запроса от ЦП 1 совпадает с адресом данных, считанных БЗ 11 (ситуация попадания в буфер предварительного считывания), то происходит выдача данных с выхода БЗ 11 на вход КПД1 6 и одновременно запись в КП2 7 с выхода БЗ 11 через вход КП2 7. Затем буфер снова вычисляет адрес и выставляет запрос на считывание данных из памяти 4. В случае предвыборки данных для второго запроса, не попавшего в КПД1 6, после попадания в БЗ 11 вычисления следующего адреса и выставления запроса на считывание данных из памяти 4 не происходит. При несовпадении адреса данных, считанных буфером БЗ 11, и адреса на загрузку данных от ЦП1 (ситуация промаха в буфер предварительного считывания) данные в буфере БЗ 11 помечаются как недействительные и вычисления следующего адреса и выставления запроса на предварительную выборку данных в СК 3 не происходит. Далее буфер БЗ 11 снова начинает анализировать поступающие запросы и считать количество промахов в КП2 7. Вычисление следующего адреса и выставление запроса на предварительную выборку данных происходит после двух подряд не попавших следующих запросов (первым запросом считается запрос, вызвавший промах в БЗ 11).

Аналогичный механизм реализован и для запросов от инструкций: данные с выхода БЗ 11 подаются на вход КПИ1 5, но не записываются в память данных КП2 7. Запросы от команд загрузки более приоритетные, поэтому при прочих равных условиях предварительная выборка данных будет выполняться для операции загрузки.

Описанная подсистема памяти ядра микропроцессора позволяет повысить производительность и помехоустойчивость системы по сравнению с известными подсистемами и исключить дополнительные задержки при считывании и загрузке данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ И УСТРОЙСТВО ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ | 2014 |

|

RU2592465C2 |

| СПОСОБ КОПИРОВАНИЯ ДАННЫХ В КЭШ-ПАМЯТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2504000C1 |

| УСТРОЙСТВО И СПОСОБ ДЛЯ ИНИЦИИРОВАНИЯ УСЛУГИ ТРАНСЛЯЦИИ МОБИЛЬНОЙ СТАНЦИЕЙ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2002 |

|

RU2264694C2 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| ГИБРИДНЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2556364C1 |

| ОТСРОЧКА ОБНОВЛЕНИЙ СОСТОЯНИЙ КЭША В НЕСПЕКУЛЯТИВНОЙ КЭШ-ПАМЯТИ В ПРОЦЕССОРНОЙ СИСТЕМЕ В ОТВЕТ НА СПЕКУЛЯТИВНЫЙ ЗАПРОС ДАННЫХ ДО ТЕХ ПОР, ПОКА СПЕКУЛЯТИВНЫЙ ЗАПРОС ДАННЫХ НЕ СТАНЕТ НЕСПЕКУЛЯТИВНЫМ | 2020 |

|

RU2817624C1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ ПОТОКОВ ДАННЫХ, СЧИТЫВАЕМЫХ ИЗ ОЗУ | 2011 |

|

RU2475817C1 |

| ОПРЕДЕЛЕНИЕ ФОРМАТОВ ТРАНСЛЯЦИИ ДЛЯ ФУНКЦИЙ АДАПТЕРА ВО ВРЕМЯ ВЫПОЛНЕНИЯ | 2010 |

|

RU2556418C2 |

| ГИБРИДНЫЙ ПОТОКОВЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2584470C2 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении производительности устройства, повышении помехоустойчивости системы и исключении дополнительных задержек при считывании и загрузке данных. Подсистема памяти, связанная с центральным процессором, системным контроллером, внешней памятью и включающая кэш-память, набор буферов данных и инструкций, состоящий из буфера для сохраняемых данных, буфера для обратных записей, буфера для загружаемых данных, причем подсистема памяти содержит дополнительные буферы для сохраняемых данных, при этом кэш-память выполнена двухуровневой, первый уровень которой соединен с центральным процессором, кэш-памятью второго уровня и буфером для обратных записей, а второй уровень соединен с буферами для сохраняемых данных, с буфером для загружаемых данных и буфером для обратных записей, причем буфер для сохраняемых данных, попавших в кэш память второго уровня, содержит биты четности для помехоустойчивого кодирования и имеет связь с буфером для обратных записей. 2 з.п. ф-лы, 1 ил.

1. Подсистема памяти, связанная с центральным процессором, системным контроллером, внешней памятью и включающая кэш-память, набор буферов данных и инструкций, состоящий из буфера для сохраняемых данных, буфера для обратных записей, буфера для загружаемых данных, отличающаяся тем, что она содержит дополнительные буферы для сохраняемых данных, при этом кэш-память выполнена двухуровневой, первый уровень которой соединен с центральным процессором, кэш-памятью второго уровня и буфером для обратных записей, а второй уровень соединен с буферами для сохраняемых данных, с буфером для загружаемых данных и буфером для обратных записей, причем буфер для сохраняемых данных, попавших в кэш-память второго уровня, содержит биты четности для помехоустойчивого кодирования и имеет связь с буфером для обратных записей.

2. Подсистема памяти по п.1, отличающаяся тем, что кэш-память первого уровня содержит память данных и память для инструкций, которая связана с буфером для обратных записей.

3. Подсистема памяти по п.1, отличающаяся тем, что буфер для загружаемых данных расположен между кэш-памятью второго уровня и системным контроллером.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| EP 0793178 A2, 03.09.1997 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| ИНДИКАТОР ИЗМЕНЕНИЙ ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ ПРИ НЕУДАЧНЫХ ОБРАЩЕНИЯХ К КЭШ-ПАМЯТИ | 2006 |

|

RU2390855C2 |

| ЭНЕРГОЭФФЕКТИВНЫЙ МЕХАНИЗМ УПРЕЖДАЮЩЕЙ ВЫБОРКИ ИНСТРУКЦИЙ | 2006 |

|

RU2375745C2 |

Авторы

Даты

2013-02-20—Публикация

2011-12-08—Подача