СП

со

Изобретение относится к технике декодирования линейных блоковых кодов и может быть использовано в системах передачи дискретной информации по каналам с шумами, в частности по стандартным телефонным каналам.

Цель изобретения - повышение достоверности передаваемой информации путем осуществления мажоритарного декодирования в целом.

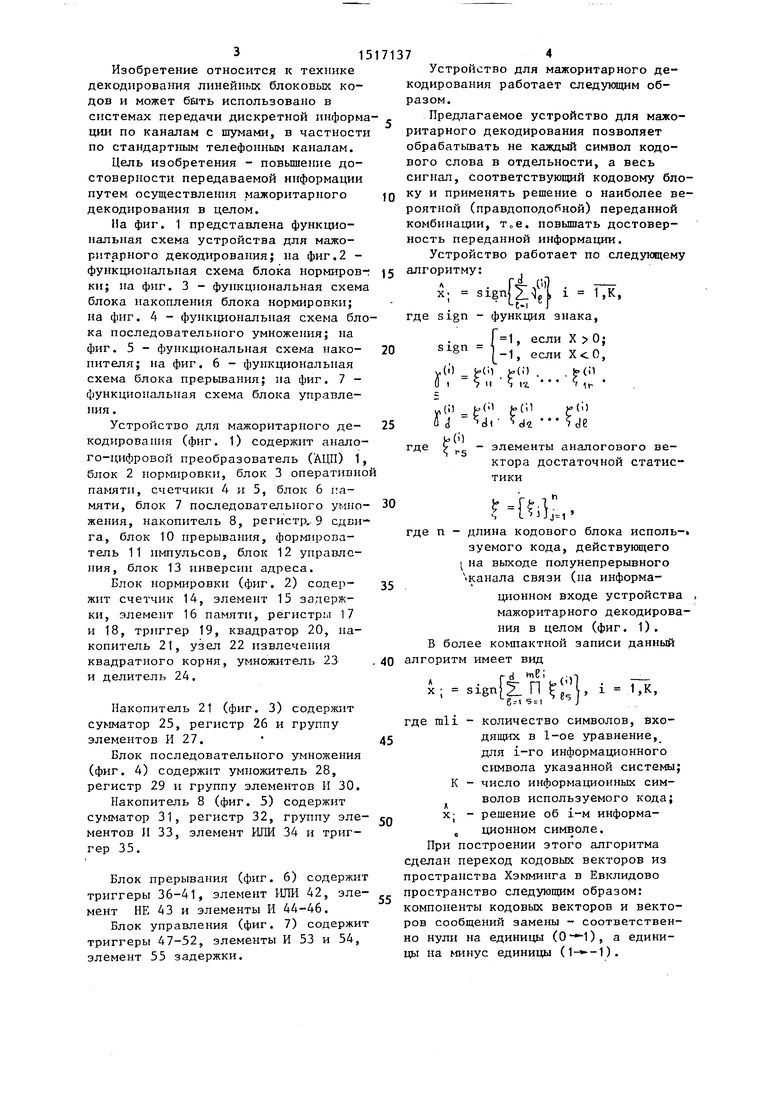

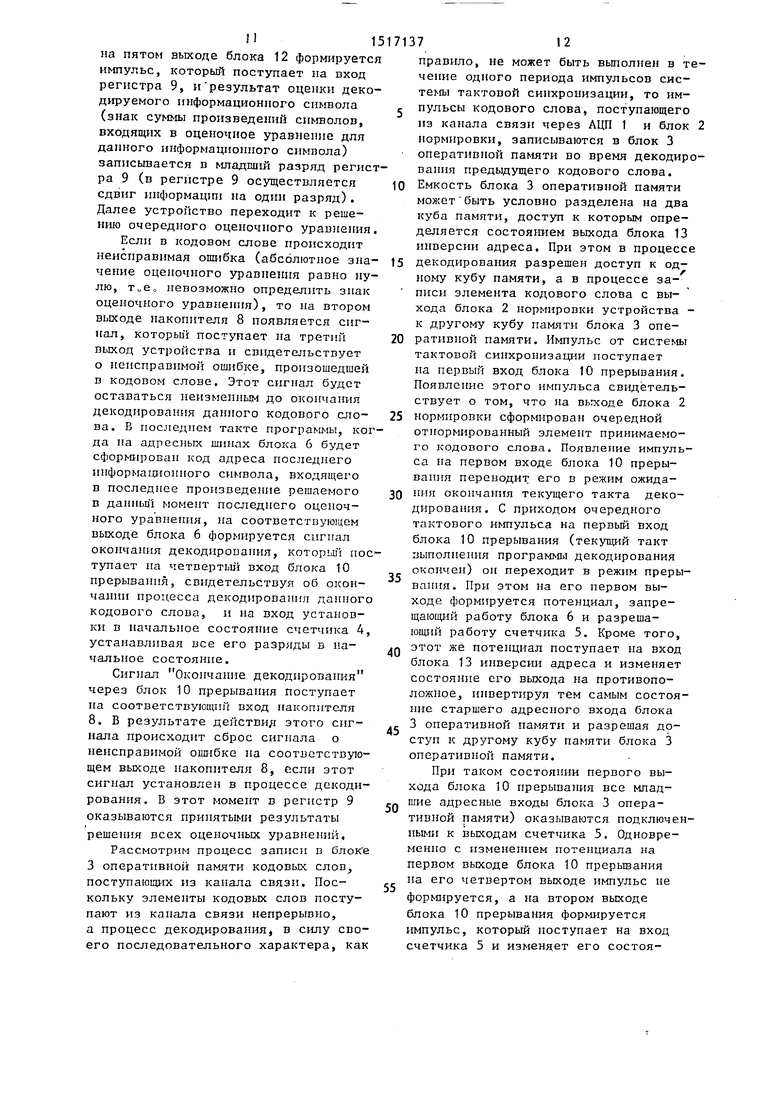

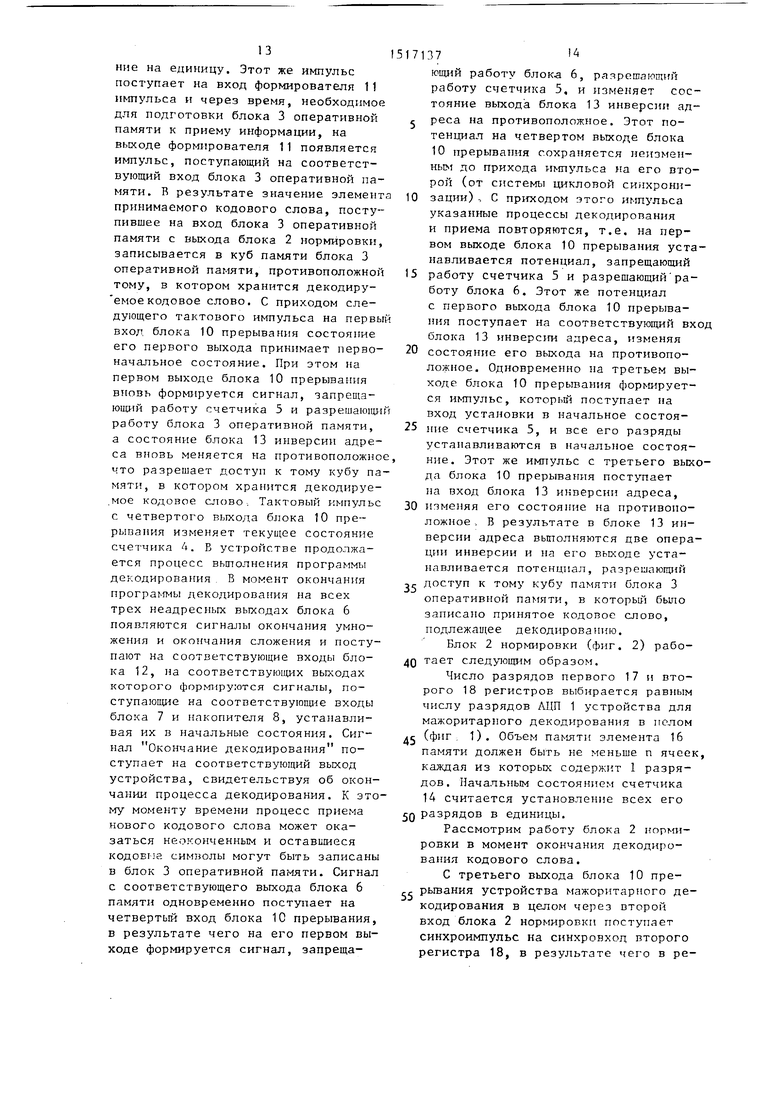

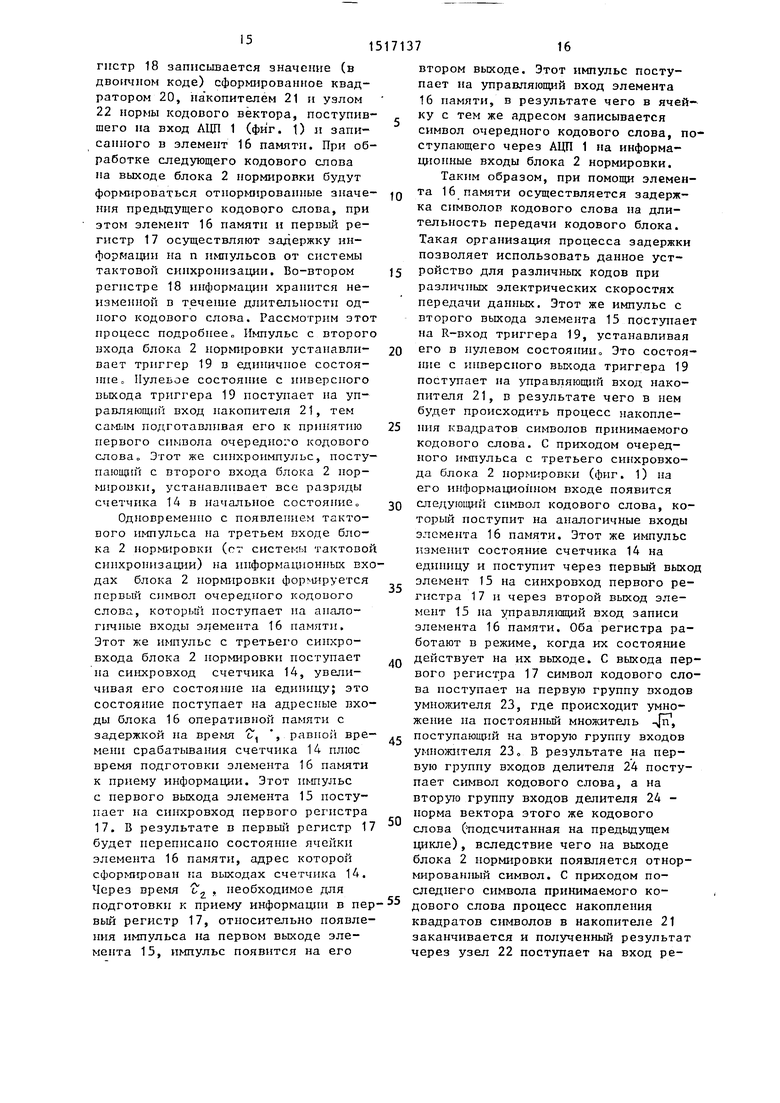

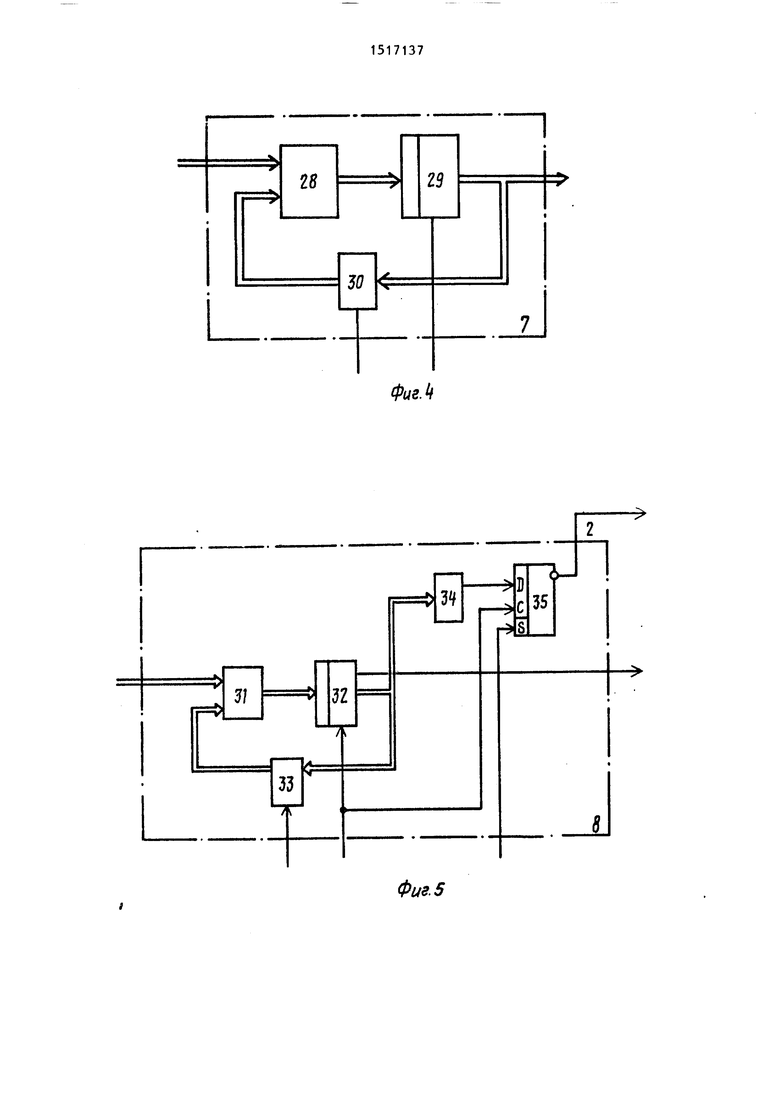

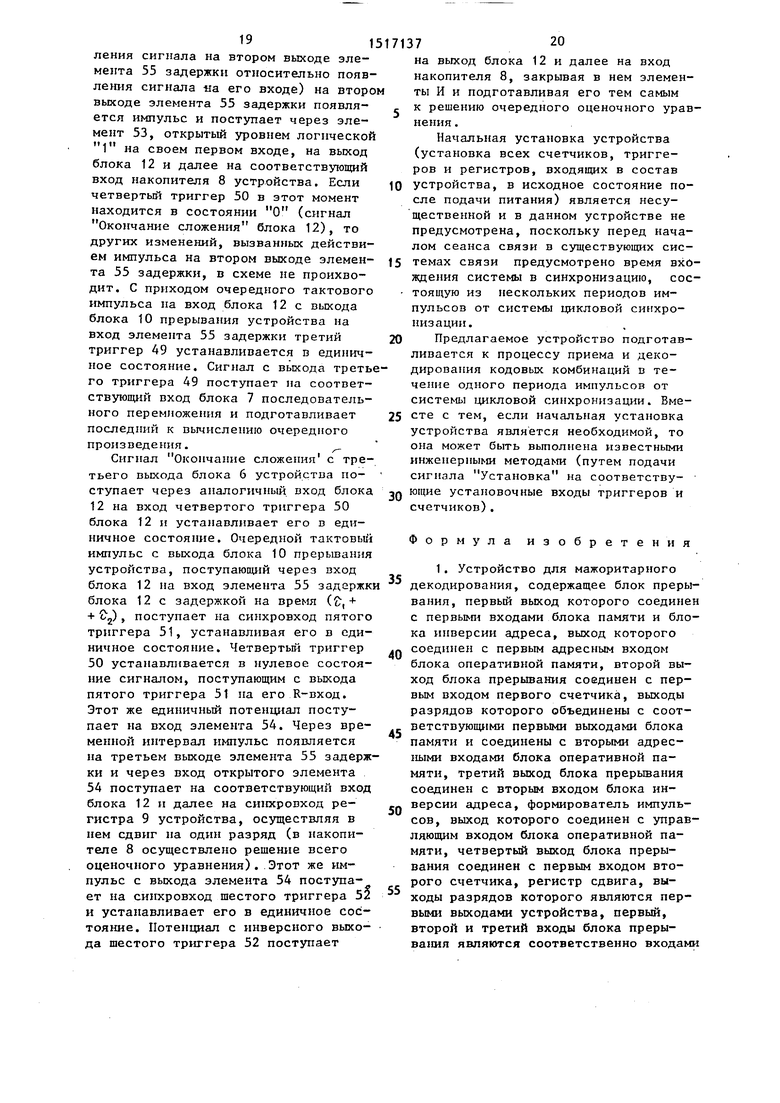

На фиг. 1 представлена функциональная схема устройства для мажоритарного декодирования; на фиг.2 - функцио}1апьная схема блока нормировг ки; на фиг. 3 - функциональная схема блока накопления блока нормировки; на фиг. t - функциональная схема блока последовательного умножения; на фиг. 5 - функц11ональная схема нако- пителя; на фиг. 6 - функциональная схема блока прерьшания; на фиг. 7 - функциональная схема блока управления .

Устройство для мажоритарного де- кодирования (фиг. 1) содержит аналого-цифровой преобразователь (АЦП) 1, блок 2 нормировки, блок 3 оперативно памяти, счетчики 4 и 5, блок 6 памяти, блок 7 последовательного умно- жения, накопитель 8, регистр,-9 сдвига, блок 10 прерьшания, формирователь 11 импульсов, блок 12 управления, блок 13 инверсии адреса.

Блок нормировки (фиг. 2) содер- жит счетчик 14, элемент 15 задержки, элемент 16 памяти, регистры 17 и 18, триггер 19, квадратор 20, накопитель 21, узел 22 извлечения квадратного корня, умножитель 23 и делитель 24.

Накопитель 21 (фиг. 3) содержит сумматор 25, регистр 26 и группу элементов И 27.

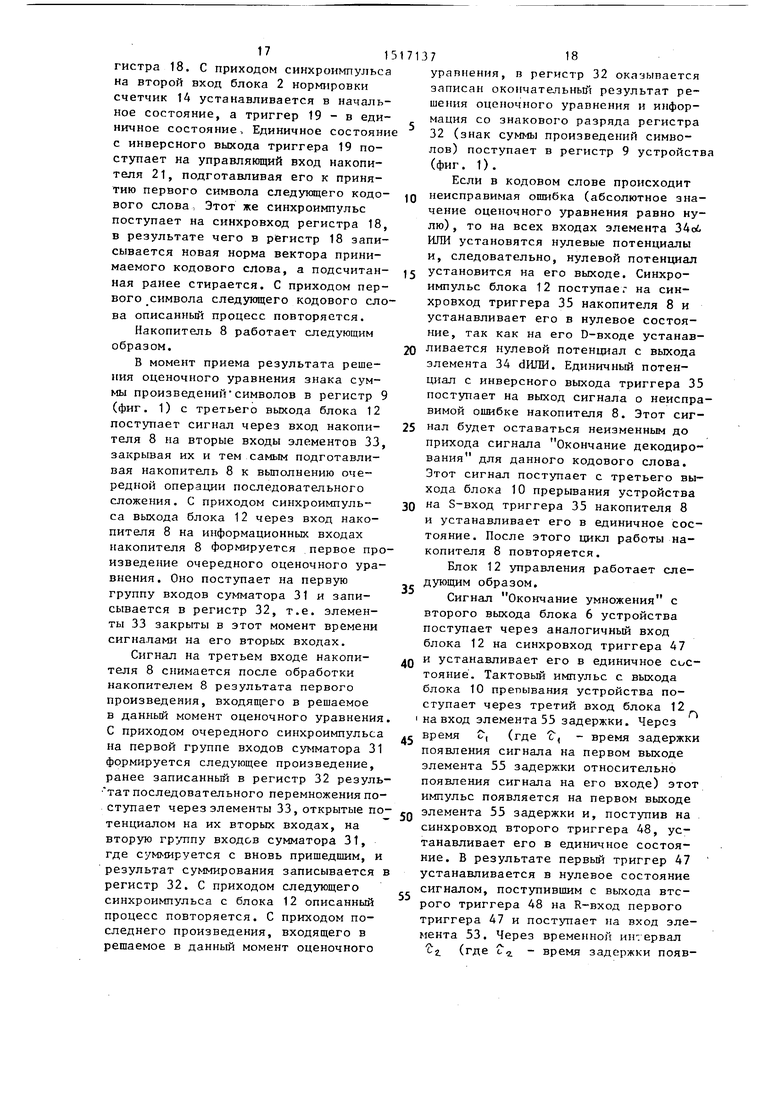

Блок последовательного умножения (фиг. 4) содержит умножитель 28, регистр 29 и группу элементов И 3D.

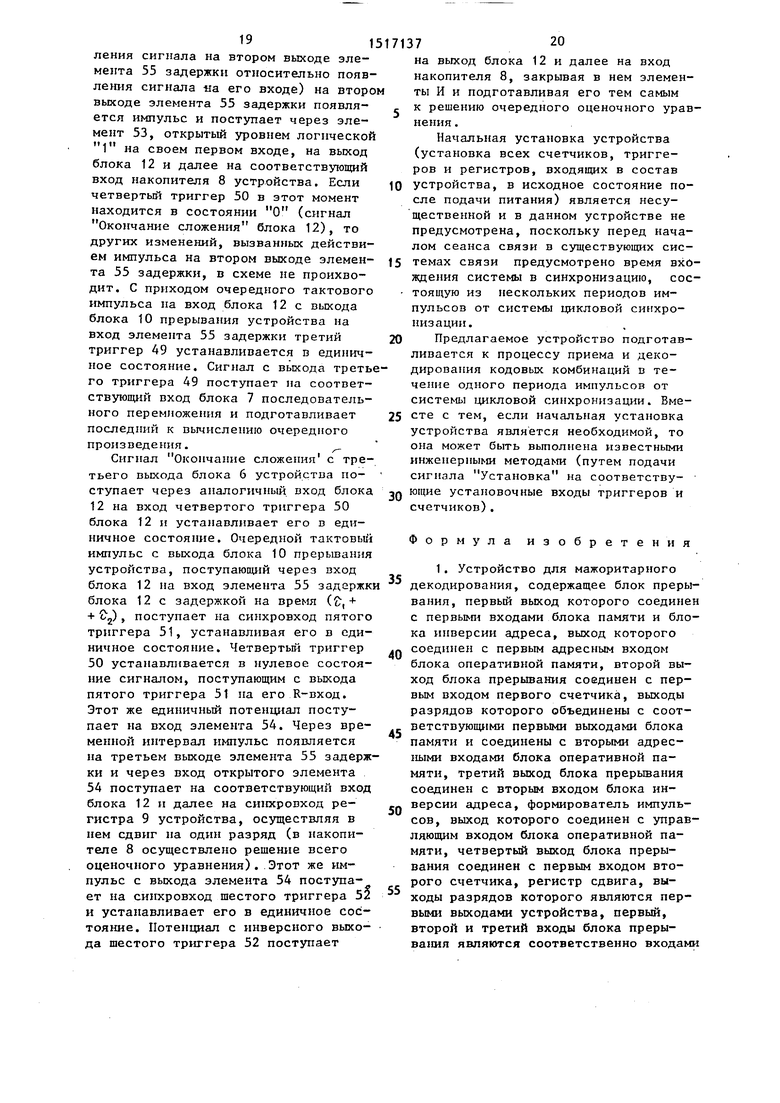

Накопитель 8 (фиг. 5) содержит сумматор 31, регистр 32, группу эле- ментов И 33, элемент ИЛИ 34 и триггер 35.

Блок прерывания (фиг. 6) содержит триггеры 36-41, элемент ИЛИ 42, эле- мент НЕ 43 и элементы И 44-46.

Блок управления (фиг. 7) содержит триггеры 47-52, элементы И 53 и 54, элемент 55 задержки.

Устройство для мажоритарного декодирования работает следующим образом.

Предлагаемое устройство для мажоритарного декодирования позволяет обрабатьшать не каждый символ кодового слова в отдельности, а весь сигнал, соответствующий кодовому блоку и применять решение о наиболее вероятной (правдоподобной) переданной комбинации, Тое. повышать достоверность переданной информации.

Устройство работает по следующему алгоритму:

л хsignfe i 1,К, -t-i

- функция знака,

если X 0; если , .(О . . ip(ii

г

|:|;

(il f(i ) ,К (

ч S iz

де

(i) .(П )c.(;i(i

и cJ i(ir di dl M l

(i)

de

S

- элементы аналогового вектора достаточной статистики

,.

где п - длина кодового блока используемого кода, действующего I на выходе полунепрерывного канала связи (на информационном входе устройства мажоритарного декодирования в целом (фиг. 1). В более кo maктнoй записи данный алгоритм имеет вид

. r4-7i H l Пг

х; sign П g , 1 1,К,

В - t 5 - 1 J

где mli - количество символов, входящих в 1-ое уравнение, для i-ro информационного символа указанной системы; К - число информационных символов используемого кода; х- - решение об i-м информа, ционном символе. При построении этого алгоритма сделан переход кодовых векторов из пространства Хэмминга в Евклидово пространство следующим образом: компоненты кодовых векторов и векторов сообщений замены - соответственно нули на единицы (), а единицы на минус единицы ().

515171376

Рассмотрим работу устройства на Однако если в.се величины - ,

примере линейного (п , К)кода Хэм- минга, имеющего длину п 7, количество информационных символов .

Код Хэмминга, поступающий на вход декодирующего устройства, образуется с помощью порождающей матрицы G, имеющей вид

j 1,п существенно меньше или б ше единицы, что может быть вызва

5 например, длинными замираниями в

кана/ie связи, то это может приве неправильному декодированию. Для борьбы с этим эффектом, принимае мый вектор необходимо отнорми

G

1 00 11 01 О 10 10 11 О 01 01 11

Декодирование информации осущестj 1,п существенно меньше или больше единицы, что может быть вызвано,

например, длинными замираниями в

кана/ie связи, то это может привести к неправильному декодированию. Для борьбы с этим эффектом, принимаемый вектор необходимо отнормировать по следующей формуле:

ср.

4РГ

Для этой цели служит блок 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Декодирующее устройство | 1989 |

|

SU1785083A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2007866C1 |

Изобретение относится к технике декодирования линейных блоковых кодов и может быть использовано в системах передачи дискретной информации по каналам с шумами, в частности по стандартным телефонным каналам. Цель изобретения - повышение достоверности передаваемой информации путем осуществления мажоритарного декодирования в целом. Устройство для мажоритарного декодирования содержит аналого-цифровой преобразователь 1, блок 2 нормировки, блок 3 оперативной памяти, счетчики 4,5, блок 6 памяти, блок 7 последовательного умножения, накопитель 8, регистр 9 сдвига, блок 10 прерывания, формирователь 11 импульсов, блок 12 управления, блок 13 инверсии адреса. 6 з.п.ф-лы, 7 ил.

вляется путем решения системы прове- 15 нормировки устройства (фиг. 1).

рочных уравнений

Необходимость нормировки пояс ется на простом примере (п. К) .к (7, 3). Пусть передается кодовое слово 1111111 и принятое кодов 20 слово имеет вид

Уравнение кодирования с учетом

замены О на 1

rillII II

на

глядит следующим образом:

к

-1 выгде g

у(Х)у;(хЪ П(Х) Д

гЬ - Jrliэлемент порождающие матрицы G; Z - вектор принимаемого кодового слова.

-0,9; 1; -06; 1; 1; 0,8; l.

Воспользовавшись уравнениями д данного, кода, имеют

25 А

Х. sign(-0,94-1-0,6+0,8)sign(+0,

(-0,9-0,48+1)sign(+0,62) (-0,6-0,9+0,8+1)sign(+0,3

Декодирование происходит верно

Дпя рассматриваемого кода проце- 30 Однако, уменьшив длину принятого

дура вынесения решения в предлагаемом устройстве принимает следующий вид:

35

Кодовый вектор при -0,45, 0,5, -0,3:0, Тогда решения об инф

волах представляются

разом , /

x, sign(,-K,r.4,r.4.r.); х, sign(f,.r,r,-r3re-.r.);

Х, sign(,-H,,).

X, sign(-0,45-1-0,25+(-0,15)-t-0,2)sign(20,5)-1; xj. signCO,5-0,225-0,12-ю,25)sign(+0,4) 1; Хз sign(20,3-0,225-ю,2+0,25)sign(-0,075)-1.

В процессе декодирования происходит ошибка.

Чтобы декодирование происходило правильно, необходимо отнормировать

45

принятый кодовый вектор в соотве I ствии с алгоритмом

. л|,/JJ: лГ7 .(-0,45)/л|о,45+0,5+0,3+0,5+0,5-Ю,4-Ю,,79 ; q i .0,5/1,,88; tf, .(-0,3)/1,,529;

qi .0,5/1,,88; q) -17.0,5/1,,88. 47.0,4/1,,7; tp 47-0,5/1,5 0,88

Необходимость нормировки поясняется на простом примере (п. К) .кода (7, 3). Пусть передается кодовое слово 1111111 и принятое кодовое слово имеет вид

-0,9; 1; -06; 1; 1; 0,8; l.

Воспользовавшись уравнениями для данного, кода, имеют

А

Х. sign(-0,94-1-0,6+0,8)sign(+0,3) 1;

(-0,9-0,48+1)sign(+0,62)1; (-0,6-0,9+0,8+1)sign(+0,3)1.

Декодирование происходит верно.

35

кодового вектора в два раза, получают следующий результат.

Кодовый вектор принимает вид -0,45, 0,5, -0,3:0,5:0,5; 0,4:0,5. Тогда решения об информационных сим волах представляются следующим об разом , /

45

принятый кодовый вектор в соответ- I ствии с алгоритмом

Таким образом, отиормированный ко- довьй вектор имеет ввд

-0,79; 0,88; -0,529; 0,88; 0,7; 0,88,

X, sign(-0,79+0,88-0,88-0,529;0,88+0,7.0,88)sign(+1,l34)1; г sign(0,88-t),79. 0,88-0,5290,7+0,88.0,88)sign(+0,5892) 1;

Хэ sign(-0,529-0,790,88+0,88 О, 7+0,88-0,88) sign(-fO,0318) 1.

Как видно из примера, декодирование после нормировки принятого кодового, вектора происходит верно.

Компоненты аналогового вектора достаточной статистики 1

15

представляющие собой результат оптимальной посимвольной обработки сигнала в приемш ке, поступают на вход АЦП 1 с выхода которого код каждого символа , j 1,п в порядке их следования поступает в блок 2 норгафовки. Поскольку для проведения операции нормирования необходимо знание всех компонент вектора , то на выходах блока 2 нормировки двоичньШ код ка ф;ргр рунрр- мированного вектора tp: прдвляется с задержкой на п тактов и записывается в блок 3 оперативной памяти о Запись производится через информационные входы блока 3 в ячейку с адресом, сформированным на вькодах первого счетчика 5„

Коэффициент пересчета счетчи.ка 5 должен быть больше или равен п, Начальным состоянием счетчиков 4 и 5 следует считать установление всех их разрядов D единицы. Число разрядов регистра 9 выбирается равным К.

Коэ(} фициент пересчета счетчика 4 должен быть не меньше суммы количества элементов, входящих в оценочные уравнения, используемые для данного кода, т,

20

25

30

е.

kcJ

большего целого числа от выраже стоящего внутри квадратных скоб

Объем блока 3 оперативной па должен .быть не меньше 2п ячеек, дая из которых состоит из 1 раз где 1 - разрядность АЦП 1. При условно объем блока 3 оперативн памяти может быть разделен на д куба памяти по п ячеек в каждом одном из кубов памяти блока 3 о тивной памяти хранятся двоичные символов декодируемого кодового ва, а в другой куб памяти осуще ется запись двоичных кодов симв очередного кодового слова, пост ющего из канала связи. Разрешен доступа к тому или иному кубу п осуществляется блоком 13 инверс адреса о

Теку1цее состояние блока 13 и сии адреса определяет номер куб памяти блока 3 (первый или втор к KOTopohry разрешен доступ в те момент временно При этом в проц 35 декодирования доступ разрешен к ному из кубов памяти, а в проце приема элемента очередного (при мого) слова - к другому.

Рассмотрим цикл работы устро с момента окончания приема очер ного кодового слова в один из к памяти блока 3 оперативной памя Импульс, поступающий с второго хровхода устройства (от систем цикловой синхронизации), поступ на второй вход блока 10 прерьша После этого на первом выходе бл 10 прерывания устанавливается п тенциал, запрещающий работу сче ка 5 и разрешающий работу блока

40

Ш

коэффициент пересчета второго счетчика 5; число символов, входящих

в одно произведение оценочного уравнения, используемого для данного кода. блока 6 должен быть не меньше

р X ( + 3) ячеек.

где квадратными скобками . обозначена операция нахождения бл11жайшего

а решения от информационньк символах получаются следующими:

большего целого числа от выражения, стоящего внутри квадратных скобок.

Объем блока 3 оперативной памяти должен .быть не меньше 2п ячеек, каждая из которых состоит из 1 разрядов, где 1 - разрядность АЦП 1. При этом условно объем блока 3 оперативной памяти может быть разделен на два куба памяти по п ячеек в каждом В одном из кубов памяти блока 3 оперативной памяти хранятся двоичные коды символов декодируемого кодового слова, а в другой куб памяти осуществляется запись двоичных кодов символов очередного кодового слова, поступающего из канала связи. Разрешение доступа к тому или иному кубу памяти осуществляется блоком 13 инверсии адреса о

Теку1цее состояние блока 13 инверсии адреса определяет номер куба памяти блока 3 (первый или второй), к KOTopohry разрешен доступ в текущий момент временно При этом в процессе декодирования доступ разрешен к одному из кубов памяти, а в процессе приема элемента очередного (принимаемого) слова - к другому.

Рассмотрим цикл работы устройства с момента окончания приема очередного кодового слова в один из кубов памяти блока 3 оперативной памяти. Импульс, поступающий с второго син- хровхода устройства (от системы цикловой синхронизации), поступает на второй вход блока 10 прерьшания. После этого на первом выходе блока 10 прерывания устанавливается потенциал, запрещающий работу счетчика 5 и разрешающий работу блока 6.

Этот же потенциал с первого выхода блока 10 прерывания поступает на первый вход блока 13 инверсии

адреса, изменяя состояние его выхода на противоположное Одновременно на третьем выходе блока 10 прерывания формируется импульс, который поступает на вход установки

91

в начальное состояние счетчика 5, и все его разряды устанавливаются в единичное состояние. Этот же импульс с третьего выхода блока 10 прерывания поступает на второй вход блока 13 инверсии адреса, изменяя его состояние на противоположное. В результате в блоке 13 инверсии адреса выпоняются две операции инверсии и на его выходе устанавливается потенциал, разрешающий доступ к тому кубу памяти блока 3 оперативной памяти, в который было записано принятое кодовое слово (подлежащее декодированию) о

Блок 7 последовательного умножения и накопитель 8 устанавливаются в начальное состояние и все разряды счетчика А устанавливаются в начальное состояние при окончании декодирования предыдущего кодового слова. Тактовый импульс поступает с третьего синхровхода устройства (от местного тактового генератора поступает на третий вход блока 10 прерывания, в результате чего на его четвертом импульсном выходе формируется нмпулъс, который поступает на синхровход блока 12 и на вход счетчика , увеличивая его состояние на единицу (в данном случае все разряды счетчика 4 устанавливаются в нулевое состояние). Это состояние счетчика 4 поступает на адресные входы блока 6 и на его адресных выходах появляется код адреса элемента кодового слова, хранящегося в блоке 3 оперативной памяти, который является первым элементом первого произведения оценочного уравнения для первого информационного символа.

С этого момента начинается выполнение программы декодирования, хранящейся в блоке 6. Значение символа, считанное из блока 3 оперативной памяти, поступает на вход блока 7 последовательного умножения в котором осуществляется последовательное умножение элементов, входящих в решаемое в данный момент произведение. Выполнение операции последовательного перемножения в блоке 7 последовательного умножения синхронизируется и myльcaми, поступающими с первого выхода блока 12 на второй вход блока 7 последовательного умножения. С приходом очередного импуль7137

10

0

5

0

5

0

5

0

5

са с третьего синхровхода устройства на третий вход блока 10 прерывания на его четвертом выходе формируется импульс, поступающий на третий вход блока 12, в котором формируются сигналы, синхронизирующие работу блока 7, накопителя 8 и регистра 9. Этот же импульс с четвертого выхода блока 10 прерьшания поступает на вход счетчика 4, увеличивая его состояние на единицу, В результате на адресных выходах блока 6 формируется код адреса ячейки блока 3 опера- тивной памяти, в которой хранитч:я символ декодируемого кодового слова, входящий в решаемое в данный тактовый момент времени произведение блоком 7, когда все символы декодирующего кодового слова, входящие в решаемое произведение (в данном случае первое), будут перемножены. Одновременно с адресом последнего символа, входящего в первое произведение данного оценочного уравнения, на выходе Окончание умножения блока 6 появляется сигнал Окончание умножения, который поступает на аналогичный вход блока 12. В результате на третьем выходе блока 12 формируется потенциал, поступающий на третий вход накопителя 8 и разрешающий прием в накопитель 8 результата последовательного перемножения, сформированного в блоке 7, а на втором выходе блока 12 формируется потеН1щал, поступающий на третий вход блока 7, подготавливающий его к выполнению очередной процедуры последовательного умножения.

Когда в устройстве осуществляется вычисление всех произведений, входящих в решаемое оценочное уравнение, одновременно с форму{рованием кода адреса элемента кодового слова, входящего последним в последнее произведение оценочного уравнения, на соответствующем выходе блока 6 формируется сигнал, свидетельствующий об окончании выполнения операции умножения, а на третьем его выходе формируется сигнал, свидетельствующий о том, что все оценочное уравнение для данного (в данном случае первого) информационного символа решено. Этот поте(гг1иал поступает на второй вход блока 12. В результате, после вьтолпенпя пос.педне й операции cлoжe tия, в илкоптолс 8

П1

на пятом выходе блока 12 формируется импульс, который поступает на вход регпстра 9, и результат оценки декодируемого информационного символа (знак суммы произведений символов, входящих в оценочное уравнение для данного информацио1И1ого символа) записьшается D младпшй разряд регистра 9 (в регистре 9 осуществляется сдвиг информацш на один разряд). Далее устройство переходит к реше- шш очередного оценочного уравнения.

Если в кодовом слове происходит неисправимая ошибка (абсолютное зна- чение оценочного уравнения равно нулю, Toe, невозможно определить знак оценочного уравнения), то на втором выходе накопителя 8 появляется сигнал, KOTopbiii поступает на третий выход устройства и свидетельствует о неисправимой ошибке, произошедшей в кодовом слове. Этот сигнал будет оставаться неизменным до окончания декодирования данного кодового ело- ва. В последнем такте программы, когда на адресных шинах блока 6 будет сформирован код адреса последнего информационного символа, входящего в последнее произведение решаемого в данный момент последнего оценочного уравнения, на соответствующем выходе блока 6 формируется сигнал окончания декодирования, которьп поступает на четвертш вход блока 10 прерывания, свидетельствуя об окончании процесса декодирования данного кодового слова, и на вход установки в начальное состояние счетчика 4, устанавливая все его разряды в начальное состояние.

Сигнал Окончание декодирования через блок 10 прерывания поступает на соответствующий вход накопителя 8. В результате действие этого сигнала происходит сброс сигнала о неисправимой ошибке на соответствующем выходе накопителя 8, если этот сигнал установлен в процессе декодирования. В этот момент в регистр 9 оказываются принятыми результаты решения всех оценочных уравнений.

Рассмотрим процесс записи в блок е 3 оперативной памяти кодовых слов, поступающих из канала связи. Пос- кольку элементы кодовых слов поступают из канала связи непрерывно, а процесс декодирования, в силу своего последовательного характера, как

Q

5 0 5 O

5

0

5

0

3712

правило, не может быть выполнен в течение одного периода импульсов системы тактовой синхронизации, то импульсы кодового слова, поступающего из канала связи через АЦП 1 и блок 2 нормировки, записываются в блок 3 оперативной памяти во время декодирования предыдущего кодового слова. Емкость блока 3 оперативной памяти может быть условно разделена на два куба памяти, доступ к которым определяется состоянием выхода блока 13 инверсии адреса. При этом в процессе декодирования разрешен доступ к одному кубу памяти, а в процессе записи элемента кодового слова с выхода блока 2 нормировки устройства - к другому кубу памяти блока 3 оперативной памяти. Импульс от системы тактовой синхронизации поступает на первый вход блока 10 прерывания. Появление этого импульса свидетельствует о том, что на выходе блока 2 нормировки сформирован очередной отнормированныр элемент принимаемого кодового слова. Появление импульса на первом входе блока 10 прерывания переводит его в режим ожидания окончания текущего такта декодирования. С приходом очередного тактового и myльca на первьй вход блока 10 прерывания (текущий такт выполнения програмьш декодирования окончен) он переходит в режим прерывания. При этом на его первом выходе формируется потенциал, запрещающий работу блока 6 и разреша- ЮШД1Й работу счетчика 5. Кроме того, этот же потенциал поступает на вход блока 13 инверсии адреса и изменяет состояние его выхода на противоположное, инвертируя тем самым состояние старшего адресного входа блока 3 оперативной памяти и разрешая до- стуи к другому кубу памяти блока 3 оперативной памяти.

При таком состоянии первого выхода блока 10 прерывания все младшие адресные входы блока 3 оперативной памяти) оказываются подключенными к выходам счетчика 5. Одновременно с изменением потенциала на первом выходе блока 10 прерьтания на его четвертом выходе импульс не формируется, а на втором выходе блока 10 прерывания фop шpyeтcя импульс, который поступает на вход счетчика 5 и изменяет его состоя13

нне на единицу. Этот же импульс поступает на вход формирователя 11 HNmynbca и через время, необходимое для подготовки блока 3 оперативной памяти к приему информации, на выходе формирователя 11 появляется импульс, поступающий на соответствующий вход блока 3 оперативной памяти. В результате значение элемент принимаемого кодового слова, поступившее на вход блока 3 оперативной памяти с выхода блока 2 нормировки, записывается в куб памяти блока 3 оперативной памяти, противоположной тому, в котором хранится декодиру- емоекодовое слово. С приходом следующего тактового импульса на первы вхол, блока 10 прерывания состояние его первого выхода принимает первоначальное состояние. При этом на первом выходе блока 10 прерывания вновь формируется сигнал, запрещающий работу счетчика 5 и разрешаю1ци работу блока 3 оперативной памяти, а состояние блока 13 инверсии адреса вновь меняется на противоположно что разрешает доступ к тому кубу памяти, в котором хранится декодируе- ,мое кодовое слово. Тактовый импульс с четвертого вькола блока 10 прерывания изменяет текущее состояние счетчика 4. В устройстве продолжается процесс выполнения программы декодирования , В момент окончания программы декодирования на всех трех неадресных выходах блока 6 появляются сигналы окончания умножения и окончания сложения и поступают на соответствующие входы блока 12, на соответствующих выходах которого формируются сигналы, поступающие на соответствующие входы блока 7 и накопителя 8, устанавливая их в начальные состояния. Сигнал Окончание декодирования поступает на соответствующий выход устройства, свидетельствуя об окончании процесса декодирования. К этому моменту времени процесс приема нового кодового слова может оказаться не.оконченным и оставшиеся КОДОВ, символы могут быть записаны в блок 3 оперативной памяти. Сигнал с соответствующего выхода блока 6 памяти одновременно поступает на четвертый вход блока 10 прерывания, в результате чего на его первом выходе формируется сигнал, запреща7

ющий работу блока 6, разрешающий работу счетчика 5, и изменяет состояние выхода блока 13 инверсии ад- реса на противоположное. Этот потенциал на четвертом выходе блока 10 прерывания сохраняется неизменным до прихода импульса на его второй (от системы цикловой сиихронизации) , С пр11ходом этого импульса указанные процессы декодирования и приема повторяются, т.е. на первом выходе блока 10 прерывания устанавливается потенциал, запрещающий

работу счетчика 5 и разрещающий работу блока 6. Этот же потенциал с первого выхода блока 10 прерывания поступает на соответствующий вход блока 13 инверсгш адреса, изменяя

состояние его выхода на противоположное. Одновременно на третьем выходе блока 10 прерывания формируется и myльc, которьй поступает на вход установки в начальное состояиие счетчика 5, и все его разряды устанавливаются в начальное состояние. Этот же импульс с третьего выхода блока 10 прерывания поступает на вход блока 13 инверсии адреса,

изменяя его состояние на противоположное, В результате в блоке 13 инверсии адреса выполняются две операции инверсии и на его выходе устанавливается потенциал, разрешающий

доступ к тому кубу памяти блока 3 оперативной памяти, в который бьшо записано принятое кодовое слово, подлежащее декодированию.

Блок 2 нop шpoвки (фиг. 2) работает следующим образом.

Число разрядов первого 17 и второго 18 регистров выбирается равным числу разрядов АЦП 1 устройства для мажоритарного декодирования в пслом

(фиг, 1). Объем памяти элемента 16 памяти должен быть не меньше п ячеек, каждая из которых содержит 1 разрядов. Начальным состоянием счетчика 14 считается установление всех его

разрядов в единицы.

Рассмотрим работу блока 2 нормировки в момент окончания декодирования кодового слова.

С третьего выхода блока 10 прерьгоания устройства мажоритарного декодирования в целом через второй вход блока 2 нормировкг поступает синхроимпульс на синхровход второго регистра 18, в результате чего в регпстр 18 записывается значение (в двоичном коде) сформированное квадратором 20, на копителем 21 н узлом 22 нормы кодового вектора, поступившего на вход АЦП 1 (фиг. 1) п записанного в элемент 16 памяти. При обработке следующего кодового слова на выходе блока 2 нормировки будут формироваться отноршфовапные значения предьщущего кодового слова, при этом элемент 16 памяти и первый регистр 17 осуществляют задержку информации на п и fflyльcoв от системы тактовой синхронизации. Во-втором регистре 18 информации хранится неизменной в течеш1е длительности одного кодового слова. Рассмотрим этот процесс подробнее. 1 шульс с второго входа блока 2 нормировки устанавливает триггер 19 D единичное состояние „ Пулевое состояние с инверсного выхода триггера 19 поступает на управляющий вход накопителя 21, тем самым подготавливая его к пр1П1ятию первого символа очередного кодового слова о Этот же синхроимпульс, поступающий с второго входа блока 2 нормировки, устанавливает все разряды счетчика 14 в начальное состояние

Одновременно с появлением тактового импульса на третьем входе блока 2 нормировки (от системы тактовой синхронизащш) на информационных входах блока 2 нормировки формируется первый символ очередного кодового слова, которьш поступает на аналогичные входы элемента 16 памяти. Этот же и шульс с третьег о синхро- входа блока 2 нормировки поступает на синхровход счетчика 14, увеличивая его состояние на единицу; это состояние поступает на адресные входы блока 16 оперативной памяти с

задержкой на время .

равной времени срабатывания счетчика 14 плюс время подготовки элемента 16 памяти к приему информации. Этот и fflyльc с первого вькода элемента 15 поступает на синхровход первого регистра 17. В результате в первьй регистр 17 будет переписано состояние ячейки элемента 16 памяти, адрес которой сформирован на выходах счетчика 14. Через время L , необходимое для подготовки к приему информации в первый регистр 17, относительно появления импульса на первом вькоде элемента 15, импульс появится на его

0

5

0

5

0

5

0

5

0

5

втором выходе. Этот импульс поступает на управляющий вход элемента 16 памяти, в результате чего в ячей ку с тем же адресом записывается символ очередного кодового слова, поступающего через АЦП 1 на информационные входы блока 2 нормировки.

Таким образом, при помощи элемента 16 памяти осуществляется задержка С1шволов кодового слова на длительность передачи кодового блока. Такая организация процесса задержки позволяет использовать данное устройство для различных кодов при различных электрических скоростях передачи данных. Этот же импульс с второго выхода элемента 15 поступает на R-вход триггера 19, устанавливая его в нулевом состоянии Это состояние с инверсного вькода триггера 19 поступает на управляющий вход накопителя 21, в результате чего в нем будет происходить процесс накопления квадратов символов принимаемого кодового слова. С приходом очередного и fflyльca с третьего сиихровхо- да блока 2 нормировки (фиг. 1) на его информационном входе появится следуюищй символ кодового слова, который поступит на аналогичные входы элемента 16 памяти. Этот же импульс изменит состояние счетчика 14 на единицу и поступит через первый вькод элемент 15 на синхровход первого регистра 17 и через второй выход элемент 15 на управляющий вход записи элемента 16 памяти. Оба регистра работают в режиме, когда их состояние действует на их выходе. С выхода первого регистра 17 символ кодового слова поступает на первую группу входов умножителя 23, где происходит умножение на постоянный множитель -J7 поступающий на вторую группу входов умножителя 23 В результате на первую группу входов делителя 24 поступает символ кодового слова, а на вторую группу входов делителя 24 - норма вектора этого же кодового слова (подсчитанная на предьщущем цикле), вследствие чего на выходе блока 2 нормировки появляется отнор- мированный символ. С приходом последнего символа принимаемого кодового слова процесс накопления квадратов символов в накопителе 21 заканчивается И полученный результат через узел 22 поступает ка вход ре1715

гистра 18. С приходом синхроимпульса на второй вход блока 2 нормировки счетчик 14 устанавливается в начальное состояние, а триггер 19 - в единичное состояние. Единичное состояни с инверсного выхода триггера 19 поступает на управляющий вход накопителя 21, подготавливая его к принятию первого символа следующего кодового слова, Этот же синхроимпульс поступает на синхровход регистра 18, в результате чего в регистр 18 записывается новая норма вектора принимаемого кодового слова, а подсчитанная ранее стирается, С приходом первого символа следующего кодового слова описанньй процесс повторяется.

Накопитель 8 работает следующим образом.

В момент приема результата решения оценочного уравнения знака суммы произведений символов в регистр 9 (фиг. 1) с третьего выхода блока 12 поступает сигнал через вход накопителя 8 на вторые входы элементов 33, закрывая их и тем самым подготавливая накопитель 8 к вьтолнению очередной операции последовательного сложения. С приходом синхроимпульса выхода блока 12 через вход накопителя 8 на информационных входах накопителя 8 формируется первое произведение очередного оценочного уравнения. Оно поступает на первую группу входов сумматора 31 и записывается в регистр 32, т.е. элементы 33 закрыты в этот момент времени сигналами на его вторых входах.

Сигнал на третьем входе накопителя 8 снимается после обработки накопителем 8 результата первого произведения, входящего в решаемое в данный момент оценочного уравнения С приходом очередного синхроимпульса на первой группе входов сумматора 31 Формируется следующее произведение, ранее записанный в регистр 32 резуль тат последовательного перемножения поступает через элементы 33, открытые потенциалом на их вторых входах, на вторую группу входов сумматора 31, где суммируется с вновь пришедшим, и результат суммирования записывается регистр 32. С приходом следующего синхроимпульса с блока 12 описанный процесс повторяется. С приходом последнего произведения, входящего в решаемое в данный момент оценочного

718

уравнения, в регистр 32 оказывается записан окончательньв1 результат решения оценочного уравнения и информация со знакового разряда регистра 32 (знак суммы произведений символов) поступает в регистр 9 устройства (фиг. 1).

Если в кодовом слове происходит

неисправимая ошибка (абсолютное значение оценочного уравнения равно нулю) , то на всех входах элемента 34(А ИЛИ установятся нулевые потенциалы и, следовательно, нулевой потенциал

установится на его выходе. Синхроимпульс блока 12 поступаем- на синхровход триггера 35 накопителя 8 и устанавливает его в нулевое состояние, так как на его D-входе устанавливается нулевой потенциал с выхода элемента 34 бИЛИ. Единичный потенциал с инверсного выхода триггера 35 поступает на выход сигнала о неисправимой ощибке накопителя 8. Этот сигнал будет оставаться неизменным до прихода сигнала Окончание декодирования для данного кодового слова. Этот сигнал поступает с третьего выхода блока 10 прерывания устройства

на S-вход триггера 35 накопителя 8 и устанавливает его в единичное состояние. После этого цикл работы накопителя 8 повторяется.

Блок 12 управления работает следующим образом.

Сигнал Окончание умножения с второго выхода блока 6 устройства поступает через аналогичный вход блока 12 на синхровход триггера 47

и устанавливает его в единичное состояние. Тактовый импульс с выхода блока 10 прерывания устройства поступает через третий вход блока 12 I на вход элемента 55 задержки. Через время о , (где с, - время задержки появления сигнала на первом выходе элемента 55 задержки относительно появления сигнала на его входе) этот импульс появляется на первом выходе

элемента 55 задержки и, поступив на синхровход второго триггера 48, устанавливает его в единичное состояние. В результате первый триггер 47 устанавливается в нулевое состояние сигналом, поступившим с выхода втс- рого триггера 48 на R-вход первого триггера 47 и поступает на вход элемента 53. Через временной интервал 2. (где С - время задержки появ

ления сигнала на втором выходе элемента 55 задержки относительно появления сигнала «а его входе) на второ выходе элемента 55 задержки появляется импульс и поступает через элемент 53, открытый уровнем логической 1 на своем первом входе, на выход блока 12 и далее на соответствующий вход накопителя 8 устройства. Если четвертый триггер 50 в этот момент находится в состоянии О (сигнал Окончание сложения блока 12), то других изменений, вызванных действием импульса на втором выходе элемента 55 задержки, в схеме не проихво- дит, С приходом очередного тактового импульса на вход блока 12 с выхода блока 10 прерывания устройства на вход элемента 55 задержки третий триггер 49 устанавливается в единичное состояние. Сигнал с выхода третьго триггера 49 поступает на соответ- ствуюпщй вход блока 7 последовательного перемножения и подготавливает последний к вычислению очередного произведения.

Сигнал Окончание сложения с третьего выхода блока 6 устройства поступает через аналогичный, вход блока 12 на вход четвертого триггера 50 блока 12 и устанавливает его в единичное состояние. Очередной тактовьш импульс с выхода блока 10 прерьшания устройства, поступаюпдш через вход блока 12 на вход элемента 55 задержк блока 12 с задержкой на время (, + + C g) , поступает на синхровход пятого триггера 51, устанавливая его в единичное состояние. Четвертый триггер 50 устанавливается в нулевое состояние сигналом, поступающим с выхода пятого триггера 51 па его R-вход. Этот же единичный потенциал поступает на вход элемента 54. Через временной интервал импульс появляется на третьем выходе элемента 55 задержки и через вход открытого элемента 54 поступает на соответствующий вход блока 12 и далее на синхровход регистра 9 устройства, осуществляя в нем сдвиг на один разряд (в накопителе 8 осуществлено рещение всего оценочного уравнения). Этот же импульс с выхода элемента 54 поступает на синхровход шестого триггера 52 и устанавливает его в единичное состояние. Потенциал с инверсного выхода шестого триггера 52 поступает

на выход блока 12 и далее на вход накопителя 8, закрывая в нем элементы И и подготавливая его тем самым к решению очередного оценочного уравнения .

Начальная установка устройства (установка всех счетчиков, триггеров и регистров, входящих в состав

устройства, в исходное состояние после подачи питания) является несущественной и в данном устройстве не предусмотрена, поскольку перед началом сеанса связи в существующих системах связи предусмотрено время вхождения системы в синхронизацию, сос- тоящую из нескольких периодов импульсов от системы цикловой синхронизации.

Предлагаемое устройство подготавливается к процессу приема и декодирования кодовьк комбинаций в течение одного периода импульсов от системы цикловой синхронизации. Вместе с тем, если начальная установка устройства является необходимой, то она может быть вьтолнена известными инженерными методами (путем подачи сигнала Установка на соответствующие установочные входы триггеров и счетчиков) .

5

0

5

0

5

Формула изобретения

21

тактовой, кадровой и цикловой синхронизации устройства, отличающееся тем, что, с целью повышения достоверности устройства, в него введены блок последовательного умножения, накопитель, блок управления , блок нормировки и аналого-цифровой преобразователь, выходы кото15

рого соединены с первыми входами бло- ,о шестого триггера, выход которого

ка нормировки, выходы которого соединены с информационными входами блока оперативной памяти, выходы которого соединены с первыми входами блока последовательного умножения, выходы которого соединены с первыми входами накопителя, первый выход которого соединен с первым входом регистра сдвига, вторые входы блока нормировки, первого счетчика и накопителя объединены и подключены к третьему выходу блока прерьгеания, третий вход блока нормцровки объединен с первым входом блока прерьшания, третий вход первого счетчика и вход формирователя импульсов подключены соответственно к первому и второму выходам блока прерьшания, второй и третий выходы блока памяти соединены соответственно с первым и вторым входами блока управления, третий вход которого подключен к четвертому выходу блока прерывания, выходы разрядов второго счетчика соединены с вторыми входами блока памяти, четвертый выход которого соединен с четвертым входом блока прерывания, вторым входом второго счетчика и является вторым выходом устройства, первый и второй выходы блока управления соединены соответственно с вторым и третьим входами блока последовательного умнол ения, третий и четвертый выходы блока управления соединены соответственно с третьим и четвертым входами накопителя, второй выход которого является третьим выходом устройства, пятый выход блока управления соединен с вторым входом регистра сдвига, вход аналого-цифрового преобразователя является информационным входом устройства.

2 о Устройство по п. 1, отличающееся тем, что блок прерывания содержит триггеры, элемент ИЛИ, элемент НЕ и элементы И, выход первого триггера соединен с первым входом элемента ИЛИ, выход второго триггера соединен с D-входом третье15

20

25

30

соединен с R-входом первого тригг ра и первым входом второго элемен И, выход элемента НЕ соединен с п вым входом третьего элемента И, в рые входы элементов И,ли входы си хронизации третьего, пятого и шес того триггеров объединены и являются третьим входом блока прерыва ния, О-входы второго и четвертого триггеров объединены и подключены к шине логической единицы, вход синхронизации второго и четвертог триггеров и- S-вход первого тригге являются соответственно первым, в рым и четвертым входами блока пре вания, выход элемента ИЛИ соедине с входом элемента НЕ и является п вым выходом блока прерывания, вых первого, второго и третьего элеме тов И являются соответственно вт рым, третьим и четвертым выходами блока прерывания.

35

40

50

55

го триггера, вькод которого соединен с R-входом второго триггера, первым входом первого элемента И и с вторым входом элемента ИЛИ, выход четвертого триггера соединен с D-входом пятого триггера, выход которого соединен с R-входом четвертого триггера и с D-входом

0

5

0

соединен с R-входом первого триггера и первым входом второго элемента И, выход элемента НЕ соединен с первым входом третьего элемента И, вторые входы элементов И,ли входы синхронизации третьего, пятого и шестого триггеров объединены и являются третьим входом блока прерывания, О-входы второго и четвертого триггеров объединены и подключены к шине логической единицы, входы синхронизации второго и четвертого триггеров и- S-вход первого триггера являются соответственно первым, вторым и четвертым входами блока прерывания, выход элемента ИЛИ соединен с входом элемента НЕ и является первым выходом блока прерывания, выходы первого, второго и третьего элементов И являются соответственно вторым, третьим и четвертым выходами блока прерывания.

0

0

5

231

торого соединен с входом синхронизации шестого триггера и является пятым выходом блока управления, D-BXO ды первого и четвертого триггеров объединены и подключены к шине логической единицы, входы синхронизации первого и четвертого триггеров и вход элемента задержки являются соответственно первым, вторым и третьим входами блока управления, вькод третьего триггера и инверсный выход шестого триггера являются соответственно первым и третьим выходами блока управления.

с объединенными третьими входами элементов И группы и является пер724

вым выходом накопителя, инверсный выход триггера янляется вторым выходом накопителя.

первого регистра, выход которого соединен с первым входом делителя, выход элемента паг-шти соединен с информационным входом второго регистра, выход которого соединен с первым

входом умножителя, выход которого соединен с вторым входом делителя, первый выход элемента задержки соединен с сиихронизируюпц м входом второго регистра, второй выход элемента задержки соединен с управляющим входом элемента намяти и R-входом триггера, инверсный выход которого соединен с первым входом накопителя, второй вход умножителя подключен к

шине сигнала -, где п - разрядность кода, выходы разрядов счетчика соединены с соответствую1Щ1ми адресными входами элемента памяти, информационный вход которого объединен с входом квадратора и является первым входом блока нормировки, выход квадратора соединен с вторым входом накопителя, входы синхронизации первого регистра и триггера и установоч- ньш вход счетчика объединены и являются вторым входом блока нормировки, D-вход триггера подключен к шине логической единицы, третий вход накопителя, вход элемента задержки и вход синхронизации счетчика объединены и являются третьим входом блока нормировки, выход делителя является выходом блока нормировки

25

сумматора и регистра являются соответственно вторым и третьим входами блока накопления, вторые входы

.

151713726

элементов И группы объединены ц являются первым входом блока накопления.

Фие.г

Фиг.З

2ff

25

Фиг.

Физ.З

«vl

}

Щ

hU

| Мажоритарное декодирующее устройство корректирующего кода Рида-Маллера | 1980 |

|

SU902283A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-23—Публикация

1987-08-03—Подача