Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны аналоговые логические элементы (см., например, рис.936 на стр.120 в книге Волгин Л.И. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. Таллинн: Валгус, 1989 г.), которые воспроизводят операцию «запрет минимального и максимального значений информационного сигнала», совершаемую над тремя входными аналоговыми сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных аналоговых логических элементов, относятся ограниченные функциональные возможности, обусловленные прежде всего тем, что не допускается обработка n+1 (n≥2) аналоговых сигналов.

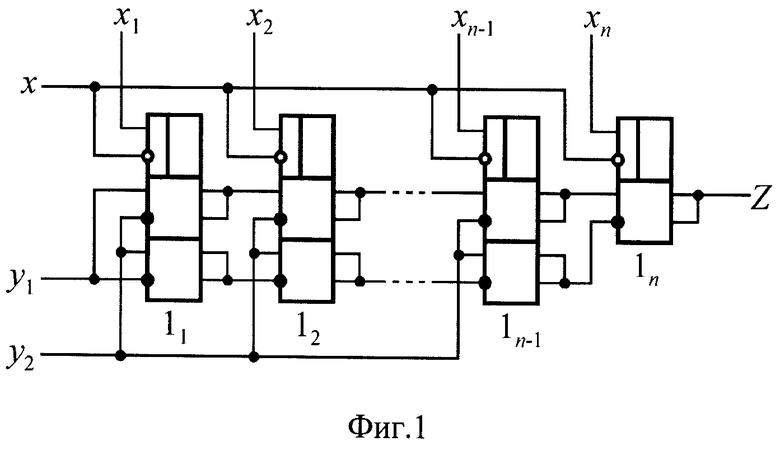

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип аналоговый логический элемент (фиг.1 в описании изобретения к патенту РФ 2130200, кл. G06G 7/25, 1999 г.), который содержит реляторы и воспроизводит операцию «запрет минимального и максимального значений информационного сигнала», совершаемую над n+1 (n≥2) входными аналоговыми сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не воспроизводится операция «запрет срединных значений информационного сигнала».

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения воспроизведения любой из операций «запрет минимального и максимального значений информационного

сигнала», «запрет срединных значений информационного сигнала», совершаемых над n+1 (n≥2) входными аналоговыми сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в аналоговом логическом элементе, содержащем n (n≥2) реляторов, каждый из которых содержит компаратор, подсоединенный выходом к управляющему входу первого,…,четвертого ключей в j-м

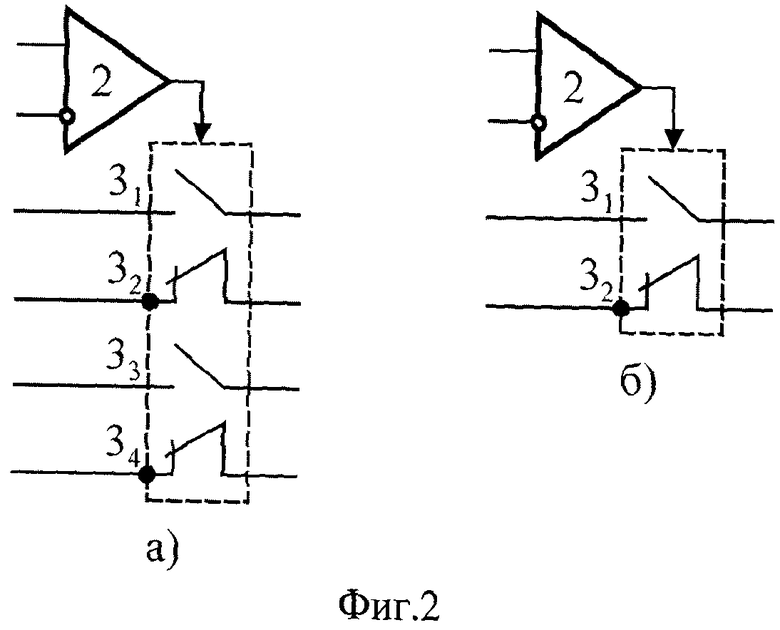

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого аналогового логического элемента и схемы реляторов, использованных при построении указанного элемента.

Аналоговый логический элемент содержит реляторы 11,…,1n (n≥2). Каждый релятор содержит компаратор 2, подсоединенный выходом к управляющему входу первого,…,четвертого ключей 31,…,34 в реляторе 1k

Работа предлагаемого аналогового логического элемента осуществляется следующим образом. На вход информационного и вход i-го

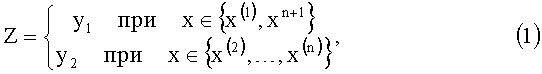

где надстрочный индекс r∈{1,…,n+1} есть ранг (порядковый номер) сигнала x=x(r) в последовательности x(1),…,x(n+1), полученной ранжированием сигналов х,х1,…,xn в порядке их возрастания, то есть в указанной последовательности x(1)=min(x,x1,…,xn), =x(n+1)=max(х,х1,…,xn). Согласно (1) при y1=0, y2=х либо при y1=x, y2=0 воспроизводится соответственно операция «запрет минимального и максимального значений информационного сигнала» либо операция «запрет срединных значений информационного сигнала».

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый аналоговый логический элемент обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает воспроизведение любой из операций «запрет минимального и максимального значений информационного сигнала», «запрет срединных значений информационного сигнала», совершаемых над n+1 (n≥2) входными аналоговыми сигналами.

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является обеспечение воспроизведения любой из операций «запрет минимального и максимального значений информационного сигнала», «запрет срединных значений информационного сигнала». Устройство содержит n реляторов (11,…,1n), каждый из которых содержит компаратор (2), подсоединенный выходом к управляющему входу двух ключей (31 32) в последнем реляторе и управляющему входу четырех ключей (31 32, 33, 34) во всех реляторах, кроме последнего. 2 ил.

Аналоговый логический элемент, предназначенный для ранговой обработки аналоговых сигналов, содержащий n(n≥2) реляторов, каждый из которых содержит компаратор, подсоединенный выходом к управляющему входу первого,…, четвертого ключей в j-м  реляторе и управляющему входу первого, второго ключей в n-ом реляторе, причем четные и нечетные ключи реляторов выполнены соответственно размыкающими и замыкающими, вход и выход каждого ключа образуют соответственно одноименные с его номером переключательные вход и выход его релятора, неинвертирующий и инвертирующий компараторные входы i-го

реляторе и управляющему входу первого, второго ключей в n-ом реляторе, причем четные и нечетные ключи реляторов выполнены соответственно размыкающими и замыкающими, вход и выход каждого ключа образуют соответственно одноименные с его номером переключательные вход и выход его релятора, неинвертирующий и инвертирующий компараторные входы i-го  релятора соединены соответственно с входом i-го задающего и входом информационного сигналов, первый и четвертый переключательные выходы предыдущего четырехключевого релятора соединены соответственно с первым и четвертым переключательными входами последующего четырехключевого релятора, а первый и второй переключательные выходы n-го релятора соединены с выходом аналогового логического элемента, отличающийся тем, что в первый релятор введены первый,…, четвертый ключи так, что он стал идентичен j-му релятору, первый и четвертый переключательные выходы j-го, первый и второй переключательные входы n-го реляторов соединены соответственно с вторым и третьим переключательными выходами j-го, первым и четвертым переключательными выходами (n-1)-го реляторов, а первый и четвертый переключательные входы второго релятора соединены соответственно с объединенными первым, вторым и объединенными третьим, четвертым переключательными выходами первого релятора, первый и четвертый переключательные входы которого соединены с первым настроечным входом аналогового логического элемента, подсоединенного вторым настроечным входом к объединенным второму и третьему переключательным входам первого,…, (n-1)-го реляторов.

релятора соединены соответственно с входом i-го задающего и входом информационного сигналов, первый и четвертый переключательные выходы предыдущего четырехключевого релятора соединены соответственно с первым и четвертым переключательными входами последующего четырехключевого релятора, а первый и второй переключательные выходы n-го релятора соединены с выходом аналогового логического элемента, отличающийся тем, что в первый релятор введены первый,…, четвертый ключи так, что он стал идентичен j-му релятору, первый и четвертый переключательные выходы j-го, первый и второй переключательные входы n-го реляторов соединены соответственно с вторым и третьим переключательными выходами j-го, первым и четвертым переключательными выходами (n-1)-го реляторов, а первый и четвертый переключательные входы второго релятора соединены соответственно с объединенными первым, вторым и объединенными третьим, четвертым переключательными выходами первого релятора, первый и четвертый переключательные входы которого соединены с первым настроечным входом аналогового логического элемента, подсоединенного вторым настроечным входом к объединенным второму и третьему переключательным входам первого,…, (n-1)-го реляторов.

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ЗАПРЕТ МИНИМАЛЬНОГО И МАКСИМАЛЬНОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОЙ ПЕРЕМЕННОЙ" | 1995 |

|

RU2130200C1 |

| КОНЪЮНКТИВНО-ДИЗЪЮНКТИВНЫЙ РЕЛЯТОР С БЛОКИРОВКОЙ | 2003 |

|

RU2257612C1 |

| Мультиплексорный решающий усилитель | 1987 |

|

SU1413649A1 |

| JP 59221770 A, 13.12.1984 | |||

| US 6188251 B1, 13.02.2001 | |||

| JP 07160793 A, 23.06.1995 | |||

Авторы

Даты

2014-05-10—Публикация

2013-02-01—Подача