Изобретение относится к области аналоговой вычислительной техники, автоматики и систем управления и может быть использовано в качестве схемно-элементного базиса аналоговых электронно-вычислительных средств и, в частности, в качестве базового элемента импликативной и предикатной алгебры выбора - конъюнктивные и(или) дизъюнктивные реляторы, непрерывной (бесконечнозначной) логики - амплитудные селекторы, двухзначной алгебры логики - булевы конъюнкторы и(или) дизъюнкторы, для построения логических аналоговых преобразователей, реляторных процессоров, нейротехнических сетей и др.

Известны аналоговые логические элементы - реляторы, воспроизводящие одну из бинарных операций импликативной алгебры выбора (ИАВ) - ИАВ-конъюнкцию, либо ИАВ-дизъюнкцию, что ограничивает их функциональные возможности (авт. свид. СССР №1270777, пп. G 06 G 7/25; Волгин Л.И. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллин: изд-во Валгус, 1989, с.70, рис.26).

Известны также кодоуправляемые реляторы, которые воспроизводят обе бинарные операции: ИАВ конъюнкцию, ИАВ дизъюнкцию, в которых переключение осуществляется через введение логической схемы "исключающее ИЛИ", на управляющие входы которой подаются логические сигналы "0" или "1" (см. патент РФ №2143739, кл. 6 G 06 G 7/48, 7/25, 7/122 "Логическое устройство для ранговой обработки аналоговых сигналов" фиг.2).

Недостатком известных реляторов являются ограниченные функциональные возможности.

Наиболее близким к заявляемому изобретению по совокупности признаков и схемным элементам того же назначения является конъюнктивно-дизъюнктивный релятор, содержащий основной двухканальный релятор RL1 и дополнительный двухканальный релятор RL2, каждый из которых состоит из дифференциального компаратора и двух переключательных каналов, содержащих замыкающий и размыкающий ключи с управляющими входами, соединенными с выходом компаратора, входные выводы ключей образуют переключательные входы релятора, объединенные выводы ключей в каждом переключательном канале образуют выходы релятора, а неинвертирующий и инвертирующий входы компаратора образуют компараторные входы релятора. Первый и второй выходы второго релятора соединены соответственно с первым и вторым компараторными входами первого релятора, а во втором реляторе входные выводы замыкающего и размыкающего ключей первого переключательного канала соединены соответственно с входными выводами размыкающего и замыкающего ключей второго переключательного канала, причем компараторные входы и входные выводы замыкающего и размыкающего ключей первого переключательного канала второго релятора образуют соответственно компараторные и управляющие входы, а переключательные входы и выходы первого релятора являются соответственно переключательными входами и выходами конъюнктивно-дизъюнктивного релятора (патент №2143730, 6 G 06 G 7/25, фиг.1), принятые за прототип.

Прототип также обладает ограниченными функциональными возможностями, т.е. воспроизводит две операции ИАВ-конъюнкцию, ИАВ-дизъюнкцию и не позволяет производить операцию блокировки (запрет прохождения сигнала).

Технический результат расширения функциональных возможностей достигается тем, что коммутационные ключи инвертирования типа воспроизводимых бинарных операций (импликативные конъюнкция либо дизъюнкция) перенесены из компараторного канала релятора в переключательный канал, введением унарной операции "запрет прохождения сигнала" (блокировка) и введением для управления операцией "блокировка" дополнительного компаратора, а предлагаемый конъюнктивно-дизъюнктивный релятор с блокировкой, содержащий первый компаратор, второй компаратор, размыкающие и замыкающие ключи со схемой управления, входные выводы ключей соединены с переключательными входами релятора, объединенные выходные выводы в каждой переключательной группе образуют выходы релятора, а неинвертирующий и инвертирующий входы компараторов образуют компараторные входы релятора, в котором в устройство введен аналоговый коммутатор со входом блокировки и двумя группами аналоговых ключей, каждая из которых имеет четыре входа и один выход, ключи которого используются в качестве размыкающих и замыкающих ключей релятора, третий компаратор, входы которого образуют два дополнительных компараторных входа релятора, а выход соединен со входом блокировки коммутатора, выходы первого и второго компараторов соединены соответственно с первым и вторым управляющими входами аналогового коммутатора, вход первого ключа первой переключательной группы соединен со входами четвертого ключа первой переключательной группы, второго и третьего ключей второй переключательной группы и образует первый переключательный вход релятора, вход второго ключа первой переключательной группы соединен со входами третьего ключа первой переключательной группы, первого четвертого ключей второй переключательной группы, и образует второй переключательный вход релятора.

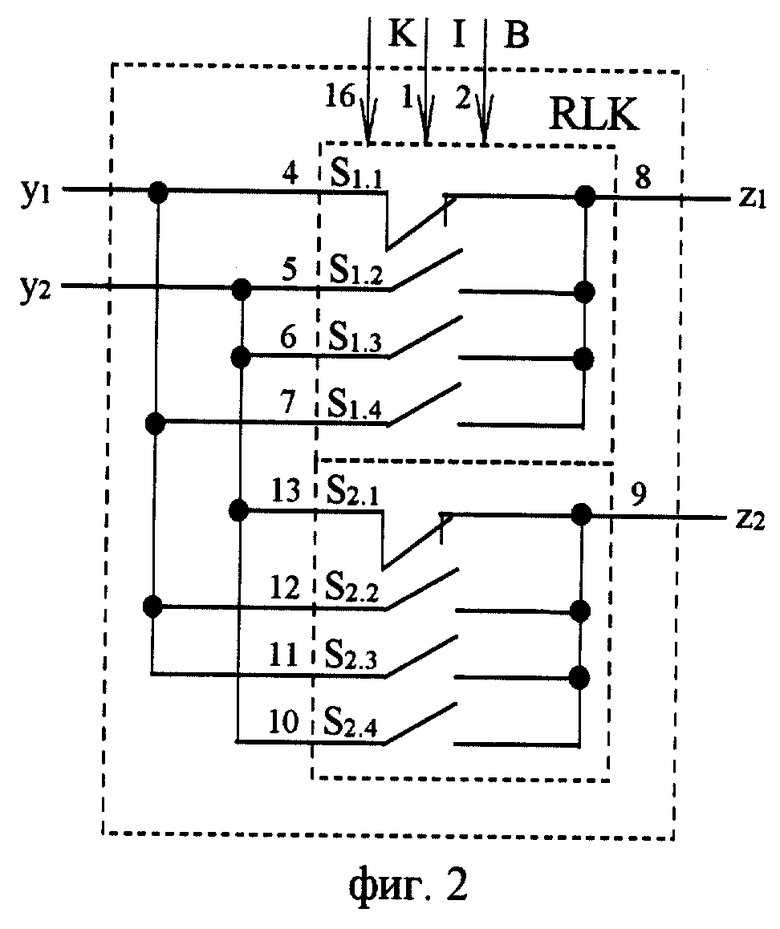

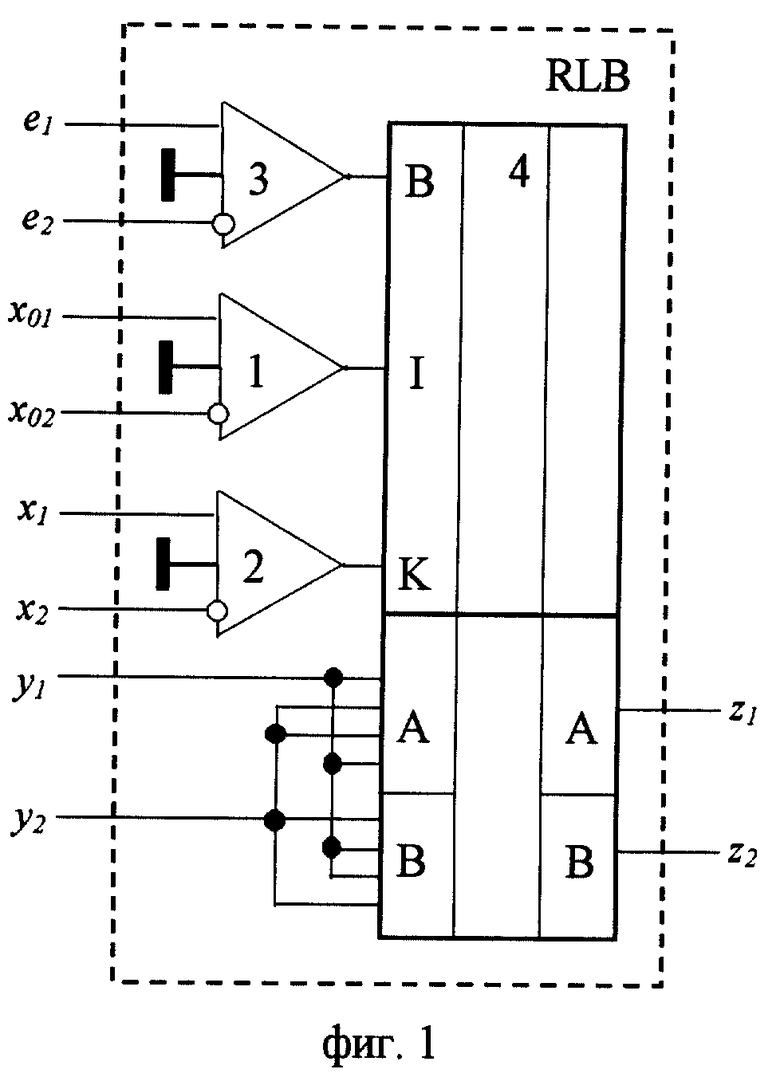

Базовая схема предложенного конъюнктивно-дизъюнктивного релятора с блокировкой RLB приведена на фиг.1, а на фиг.2 представлена электрическая схема переключательного канала релятора (нумерация выводов соответствует интегральной схеме аналогового коммутатора КР590КН3). Устройство содержит три дифференциальных компаратора: 1, 2, 3 и аналоговый коммутатор 4. Входные выводы первого дифференциального компаратора 1 образуют два управляющих входа релятора x01 и х02, входные выводы второго дифференциального компаратора 2 образуют два компараторных входа релятора x1 и х2, входные выводы третьего дифференциального компаратора 3 образуют два дополнительных компараторных входа релятора e1 и е2. Выходной вывод первого дифференциального компаратора 1 соединен с первым управляющим входом аналогового коммутатора 4, выходной вывод второго дифференциального компаратора 2 соединен со вторым управляющим входом аналогового коммутатора 4, выходной вывод третьего дифференциального компаратора 3 соединен с управляющим входом блокировки коммутатора 4. Первый переключательный вход y1 релятора образует вход первого замыкающего ключа первой переключательной группы S1.1, соединенный со входами четвертого размыкающего ключа первой переключательной группы S1.4, второго размыкающего S2.2 и третьего размыкающего S2.3 ключей второй переключательной группы. Второй переключательный вход у2 релятора образует вход второго размыкающего ключа первой переключательной группы S1.2, соединенный со входами третьего размыкающего ключа первой переключательной группы S1.3, первого замыкающего S2.1 и четвертого размыкающего S2.4 ключей второй переключательной группы. Основной и дополнительный выходы релятора z1 и z2, являющиеся выходами аналогового коммутатора, образуют объединенные выходные выводы замыкающих ключей S1.1, S1.2, S1.3, S1.4 и S2.1, S2.2, S2.3, S2.4 в каждой переключательной группе соответственно.

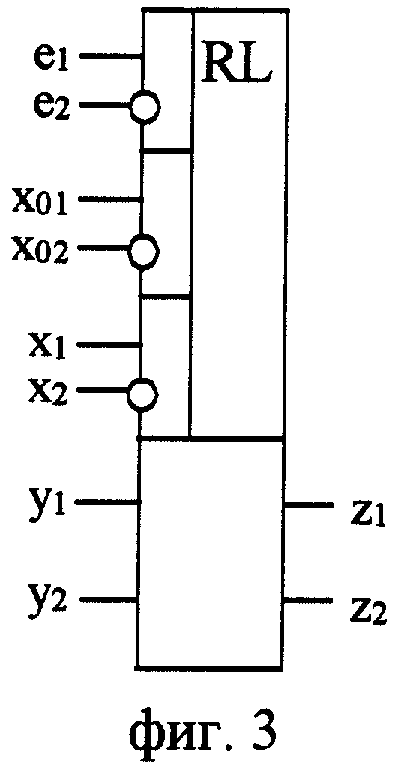

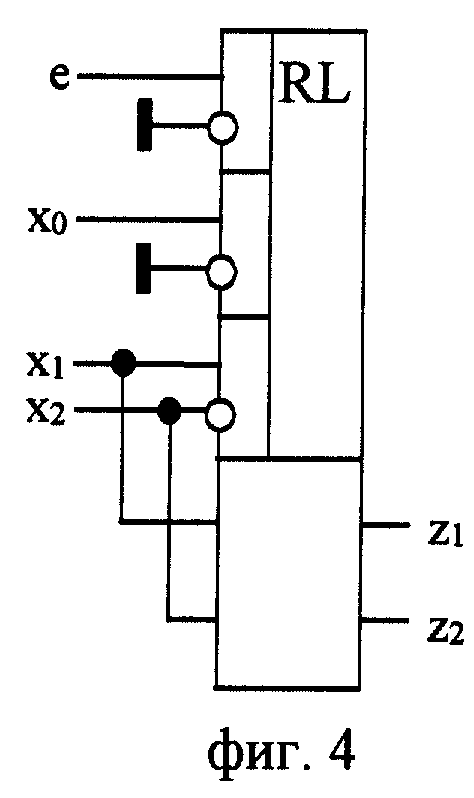

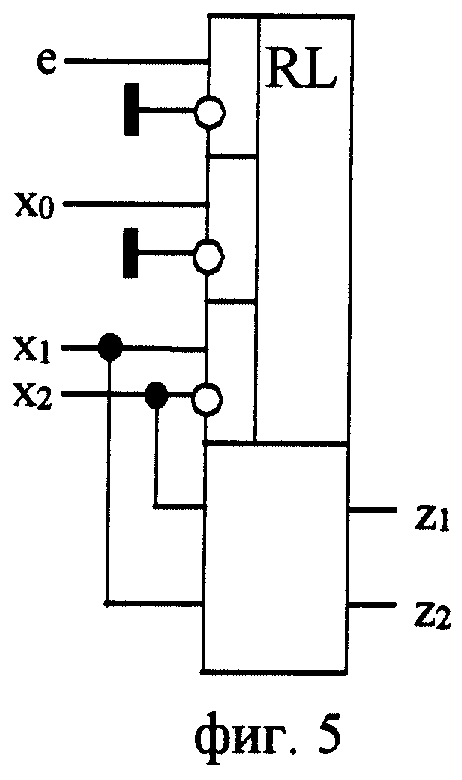

На фиг.3 представлено условное изображение базовой схемы фиг.1, на фиг.4-5 приведены типовые включения конъюнктивно-дизъюнктивного релятора с блокировкой, изображенного на фиг.1.

Работа конъюнктивно-дизъюнктивного (КД) релятора с блокировкой осуществляется следующим образом.

Реляторы являются логическими схемными элементами, воспроизводящими бинарные (базовые) операции импликативной алгебры выбора (см. Волгин Л.И., Зарукин А.И. Развитие элементного базиса реляторной схемотехники// Датчики и системы, 2002, №3. С.2-8)

и сопутствующие им изломные и разрывные элементарные функции.

В (1) I(х) есть единичная функция (оператор Хевисайда), равная нулю при при х<0 и единице при х>0, I(0∈ {0,1}, I=(I12, I21) - кортеж (вектор) весовых коэффициентов, I12=I(x1-x2), I21=1-I12=I(x1-x2), I12+I21=1 (условие комплементарности), y1 и у2 - предметные переменные (в общем случае любые физические и математические объекты, удовлетворяющие условиям мультипликативного выделения уi·1=уi и поглощения уi·0=0), x1 и x2 - предикатные переменные (действительные числа).

Реляторы с блокировкой переключательных каналов воспроизводят операции

где x1, x2 и y1, у2 есть соответственно предикатные и предметные переменные (сигналы), J=I(xБ) - управляющий логический сигнал блокировки, Z1, Z2 - выходные выводы релятора, соответственно прямой и инверсный.

Согласно (2) при I(хБ)=1 релятором воспроизводятся операции по формулам (1а) и (1б). Соответственно при I(хБ)=0 ключи переключательного канала разомкнуты (режим блокировки) и воспроизводится операция "запрет прохождения сигнала".

На управляющие входы КД-релятора (на входы компаратора 1) подаются управляющие сигналы (напряжения) x01 и x02, на его дополнительные компараторные входы релятора (на входы компаратора 3) подаются управляющие сигналы (напряжения) e1 и е2, а на его переключательные входы (на входы компаратора 2) подаются соответственно идентифицирующие аналоговые сигналы y1 и у2. Выходные напряжения компараторов обеспечивают управление аналоговым коммутатором 4. В качестве аналогового коммутатора, например, могут быть использованы серийно выпускаемые аналоговые коммутаторные интегральные схемы типа КР590КН3, К561КП1 и другие аналогичные микросхемы (см. Цифровые и аналоговые интегральные микросхемы: Справочник/ С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др.; Под ред. С.В.Якубовского. - М.: Радио и связь, 1990. - 496 с.: ил. стр. 450 рис.5.162, табл 5.33; Бирюков С.А. Цифровые устройства на МОП-интегральных микросхемах. - М.: Радио и связь, 1990. - 128 с.; ил. - (Массовая радиобиблиотека; Вып.1132, стр.46-47 т.3, рис.82).

Положение ключей на фиг.2 соответствует ситуации, когда e1>e2, x01<x02, x1<x2 - сигнал с y1 проходит на z1, а с у2 проходит на z2. При e1<e2 все ключи размыкаются вне зависимости от соотношения других входных сигналов, что обеспечивается подачей на вход блокировки коммутатора соответствующего логического уровня. При e1>e2, x01<x02, x1>x2 замкнута вторая пара ключей (S1.2 и S2.2) - сигнал с y1 проходит на z2, а с у2 проходит на z1. При e1>e2, x01>x02, x1<x2 замкнута третья пара ключей (S1.3 и S2.3) - сигнал с y1 проходит на z2, а с у2 проходит на z1. При e1>e2, x01>x02, x1>x2 замкнута четвертая пара ключей (S1.4 и S2.4) - сигнал с y1 проходит на z1, а с у2 проходит на z2.

В отличие от прототипа расширены функциональные возможности устройства путем введения дополнительного входного сигнала блокировки прохождения сигнала, совместимого с допустимым диапазоном изменений компараторных сигналов x1 и x2.

В частном случае один из входов управляющих сигналов (x01=0, x02=x0 или x01=x0, x02=0) может быть заземлен. Аналогично в частном случае один из дополнительных компараторных входов релятора (e1=0, e2=e или e1=e, e2=0) может быть заземлен.

При соединении входов КД-релятора (фиг.1) в соответствии с фиг.4 по выходу z1 при х0>0 и е>0, х0<0 и е>0 воспроизводятся соответственно дизъюнкция и конъюнкция непрерывной (бесконечнозначной) логики, а по выходу z2 воспроизводятся соответственно конъюнкция и дизъюнкция непрерывной (бесконечнозначной) логики:

Z1=max (X1, X2), Z2=min(X1, X2) и Z1=min(X1, X2), Z2=max(X1, X2).

При соединении входов КД-релятора в соответствии с фиг.5 по выходам z1 и z2 при е>0 х0>0 воспроизводятся непрерывно-логические функции:

Z1=min(X1, X2), Z2=max(X1, X2);

при е>0 х0<0 воспроизводятся непрерывно-логические функции:

Z1=max (X1,X2), Z2=min(X1, X2),

а по симметричному выходу (выходной сигнал Z=Z1-Z2 снимается между основным z1 и дополнительным z2 несимметричными выходами) воспроизводится модуль-функция разности двух аналоговых сигналов Z=Z1-Z2=|X1-X2|.

При этом для двоичных переменных с логическими уровнями X1, X2∈{0,1) функции для выходов Z1, Z2, Z=Z1-Z2 являются соответственно булевыми дизъюнкцией Z1=X1∨X2, конъюнкцией Z2=X1∧X2 и функцией "исключающее ИЛИ" (сложение по модулю 2).

Устройство прошло лабораторные испытания. Опытные данные показывают достижение цели.

Таким образом, предлагаемое устройство имеет более широкие функциональные возможности по сравнению с прототипом и может выпускаться промышленностью как на дискретных элементах, так и в виде микросхемы.

Изобретение относится к области аналоговой вычислительной техники, автоматики и систем управления. Техническим результатом является расширение функциональных, вычислительных, алгоритмических, адаптационных и комбинаторных возможностей за счет введения в релятор операции блокировки (запрета прохождения сигнала). Устройство содержит три компаратора, аналоговый коммутатор со входом блокировки и двумя группами аналоговых ключей, каждая из которых имеет четыре входа и один выход. 5 ил.

Конъюнктивно-дизъюнктивный релятор с блокировкой, содержащий первый компаратор, инвертирующий и неинвертирующий входы которого являются управляющими входами релятора, второй компаратор, неинвертирующий и инвертирующий входы которого являются компараторными входами релятора, отличающийся тем, что в него введены аналоговый коммутатор со входом блокировки и двумя группами аналоговых ключей, каждая из которых имеет четыре входа и один выход, третий компаратор, входы которого образуют два дополнительных входа релятора, а выход соединен с входом блокировки аналогового коммутатора, выходы первого и второго компараторов соединены соответственно с управляющими входами аналогового коммутатора, вход первого ключа первой переключательной группы соединен со входами четвертого ключа первой переключательной группы, второго и третьего ключей второй переключательной группы и образует первый переключательный вход релятора, вход второго ключа первой переключательной группы соединен со входами третьего ключа первой переключательной группы, первого и четвертого ключей второй переключательной группы и образует второй переключательный вход релятора, объединенные выходы ключей первой и второй переключательной группы образуют соответственно основной и дополнительные выходы релятора.

| КОНЪЮНКТИВНО-ДИЗЪЮНКТИВНЫЙ РЕЛЯТОР | 1999 |

|

RU2143730C1 |

| КОММУТАЦИОННЫЙ РЕЛЯТОР ДЛЯ ВОСПРОИЗВЕДЕНИЯ БАЗОВЫХ ОПЕРАЦИЙ КОМПЛЕМЕНТАРНОЙ АЛГЕБРЫ | 2000 |

|

RU2170456C1 |

| Аналоговый логический элемент для воспроизведения линейно-разрывных функций (его варианты) | 1985 |

|

SU1270777A1 |

| !йСЕСОгОЗНАЯ | 0 |

|

SU369695A1 |

Авторы

Даты

2005-07-27—Публикация

2003-12-05—Подача