Изобретение относится к области автоматики и может быть использовано в системах с дискретным электроприводом с автоматическим обнаружением одиночных отказов на базе трехфазных, четырехфазных и шестифазных шаговых двигателей.

Известно [1] устройство для обнаружения отказов в шаговом электроприводе, содержащее блок синхронизации, реверсивный кольцевой сдвиговый регистр, элемент сравнения кодов, пороговые датчики тока и напряжения, включенные в цепь каждой фазы, при этом выходы датчиков тока подключены к первым входам логических элементов 2И, выходы датчиков напряжения - ко вторым входам, а выходы элементов 2И подключены к разрядным входам кольцевого реверсивного сдвигового регистра и первым входам элемента сравнения, вторые входы которого соединены с разрядными выходами сдвигового регистра. Устройство обнаруживает обрыв или короткое замыкание обмоток четырехфазного шагового двигателя с симметричной парной коммутацией.

Недостатками устройства являются отсутствие указателя адреса неисправности, а также невозможность обеспечения работы шагового двигателя в режиме переменной тактности, управляемой по шинам выбора режима коммутации.

Наиболее близким к заявленному устройству является устройство для управления шаговым двигателем [2], содержащее первую, вторую, третью шины выбора режима коммутации, шину управления, тактовую шину, шину реверса, реверсивный 2/12 счетчик, первый, второй и третий входы которого соединены с шинами управления, тактовой, реверса соответственно, постоянное запоминающее устройство, шину разрешения чтения, при этом первый-четвертый выходы реверсивного счетчика соединены с одноименными входами постоянного запоминающего устройства, пятый, шестой, седьмой, восьмой входы которого соединены с третьей, второй, первой, седьмой шинами выбора режима коммутации и разрешения чтения соответственно, а выходы первый-шестой постоянного запоминающего устройства являются одноименными выходами устройства управления шаговым двигателем.

Это устройство реализует известные режимы коммутации и стоянки для двигателей с различным числом фазных обмоток и обеспечивает работу шагового двигателя в режиме переменной тактности, управляемой по шинам выбора режима коммутации.

Однако данное устройство не обнаруживает неисправности и не указывает их адреса.

Заявляемое изобретение направлено на расширение функциональных возможностей устройства. Это достигается тем, что в устройство дополнительно введены первая, вторая, третья схемы свертки, выходы 10, 11, 12 постоянного запоминающего устройства, представляющие эталонные контрольные разряды кода Хэмминга, индикатор, блок усилителей мощности с датчиками тока и напряжения, при этом входы 1, 2, 4 первой схемы свертки, входы 1, 3, 4 второй схемы свертки, входы 2, 3, 4 третьей схемы свертки соединены с одноименными (логическими) выходами 1, 2, 3, 4 блока усилителей мощности, силовые выходы а, b, с, d которых соединены с фазными обмотками А, В, С, D шагового двигателя, выходы постоянного запоминающего устройства 10, 11, 12 соединены с одноименными входами схем свертки, выходы которых первый, второй, третий соединены с одноименными входами индикатора.

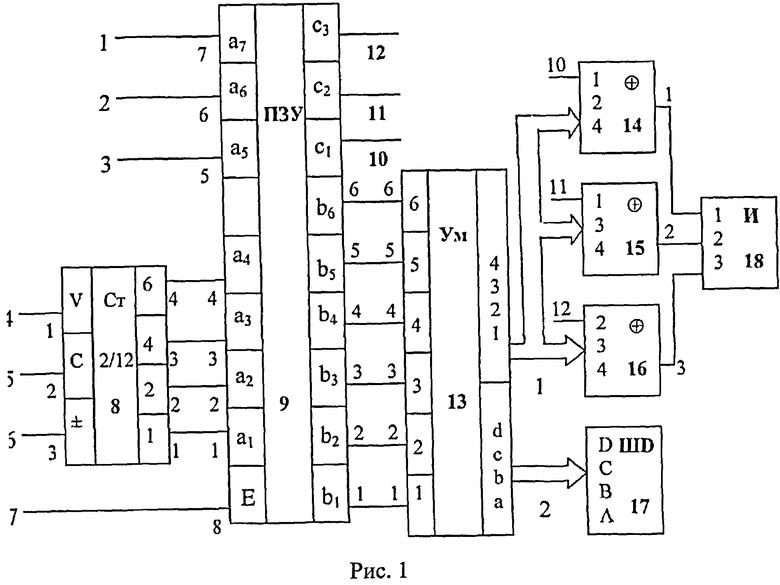

На чертеже приведена блок-схема устройства.

Устройство содержит шины выбора режима коммутации 1-3, шину управления 4, тактовую шину 5, шину реверса 6, шину разрешения чтения 7, реверсивный 2/12 счетчик 8, постоянное запоминающее устройство 9, схемы свертки 14, 15, 16, индикатор 18, блок усилителей мощности 13.

Шины выбора режима коммутации 3, 2, 1 соединены со входами 5, 6, 7 постоянного запоминающего устройства соответственно, шина управления 4 подсоединена к первому входу реверсивного счетчика 8, тактовая шина 5 и шина реверса 6 подключены ко второму и третьему входам реверсивного счетчика соответственно, шина разрешения чтения 7 соединена с восьмым входом постоянного запоминающего устройства 9, выходы 1, 2, 3, 4 реверсивного счетчика соединены с одноименными входами постоянного запоминающего устройства 9, выходы которого 1-6 соединены с одноименными входами блока усилителей мощности 13, вторые (силовые) выходы которого а, b, с, d подключены к фазовым обмоткам А, В, С, D двигателя соответственно, а первые (логические) выходы блока усилителей мощности 1, 2, 3, 4 соединены соответственно со входами 1, 2, 4 первой схемы свертки 14, со входами 1, 3, 4 второй схемы свертки 15, а также со входами 2, 3, 4 третьей схемы свертки 16, выходы 1, 2, 3 которых подключены к одноименным входам индикатора 18, десятый вход первой схемы свертки 14, одиннадцатый вход второй схемы свертки 15, двенадцатый вход третьей схемы свертки 16 соединены соответственно с выходами 10, 11, 12 постоянного запоминающего устройства.

Усилители мощности блока 13 содержат по два канала с общим входом в логических уровнях постоянного запоминающего устройства 9, первый канал (логический) формирует логическую переменную αi=DTi∧DHi, при этом DTi=DHi=1, если ток и напряжение в i фазе соответствуют номиналу, иначе ноль, второй канал (силовой) преобразует входной сигнал управления фазами (таблицы 1-3) до уровня, соответствующего требованиям технических условий на шаговый двигатель.

Устройство работает следующим образом.

При начальной установке устройства выполняется подключение фазных обмоток шагового двигателя к силовым выходам усилителей мощности. Например, выходы а, b, с усилителей мощности подключаются соответственно к обмоткам первой (А), второй (В), третьей (С) фазы трехфазного двигателя (таблица 1), что обеспечивает режимы коммутации трехтактной поочередной (таблица 1, код режима 111), шеститактной поочередной (таблица 2, код режима 011). При подключении четырехфазного двигателя его первая (А) - четвертая (D) обмотки соединяются с соответствующими выходами а, b, с, d усилителей мощности, обеспечивая режимы четырехтактной поочередной (код 101), либо четырехтактной парной (таблица 3, код 001) коммутации.

Коды режимов задаются старшими разрядами адреса a5a6а7 постоянного запоминающего устройства (чертеж), значение младших адресных разрядов которого а1, а2, а3, а4 представлено кодом состояния реверсивного счетчика на его выходах 1-4, старшие разряды кода режима определяются значением логических переменных на первой-третьей шинах выбора режима коммутации.

Значение логической переменной V=1 шины 4 управления разрешает счет импульсов, поступающих по тактовой шине 5 на увеличение или уменьшение кода состояния реверсивного счетчика в зависимости от уровня на шине 6 реверса.

Значение Е=0 устанавливает на выходе постоянного запоминающего устройства нули, обеспечивая режим обесточенной стоянки, значение  задает режим стоянки под током, при Е=1 код содержимого постоянного запоминающего устройства по адресу а1а2а3а4а5а6а7 выводится на его выходные разряды b1-b6 (код управления коммутацией фаз двигателя) и c1-c3 (эталонный код контрольных разрядов по Хэммингу).

задает режим стоянки под током, при Е=1 код содержимого постоянного запоминающего устройства по адресу а1а2а3а4а5а6а7 выводится на его выходные разряды b1-b6 (код управления коммутацией фаз двигателя) и c1-c3 (эталонный код контрольных разрядов по Хэммингу).

В таблицах 1-3 приведены примеры функционирования заявляемого устройства в режимах трехтактной поочередной (код режима 111), шеститактной поочередной (код режима 011), четырехтактной парной (код режима 001) коммутации. В таблице 1 строка 1 соответствует коду счетчика 1000, а слово, считанное из постоянного запоминающего устройства по адресу 1000111, равно 010101 (включение фазы В, фазы А, С обесточены, эталонные контрольные разряды c1=c3=1, c2=0).

Если в устройстве нет неисправностей, то на логических выходах усилителей мощности появится код x3=x6=0, x5=1, а первая-третья схемы свертки сформируют код адреса отказа (синдром) S1=x1⊕x3⊕x5⊕x7=1⊕0⊕1⊕0=0, S2=x2⊕x3⊕x6⊕x7=0⊕0⊕0⊕0=0, S4=x4⊕x5⊕x6⊕x7=1⊕1⊕0⊕0=0, в соответствии с которым индикатор высветит цифру 0, указывающую на отсутствие отказов.

Пусть в фазе В произошел обрыв (DT2=0) или короткое замыкание обмотки двигателя (DH2=0) или замыкание на землю цепи b2 постоянного запоминающего устройства, т.е. x5=0, тогда в соответствии со строкой 4 таблицы 1 код счетчика равен 0010, а слово, считанное из постоянного запоминающего устройства по адресу 0010111, равно 010101, при этом в пятом разряде (x5) из-за отказа 1 заменена 0.

В этом случае код адреса неисправности определяется как S1=x1⊕x3⊕x5⊕x7=1⊕0⊕0⊕0=1, S2=x2⊕x3⊕x6⊕x7=0⊕0⊕0⊕0=0, S4=x4⊕x5⊕x6⊕x7=1⊕0⊕0⊕0=1, в соответствии с которым индикатор высветит цифру 5, указывая адрес отказа. Аналогично срабатывает устройство при отказах x3≡1 (строки 7, 8 таблицы 1), х3≡0 (строки 7, 8, 12 таблицы 2), x6≡1 (строки 13, 14, 15 таблицы 2), x7≡0 (строки 6, 7 таблицы 3), x5≡1 (строки 10, 11 таблицы 3).

Источники информации

1. Авторское свидетельство SU 1415401, H02Р 7/62, опубликованное от 07.08.88. Бюл. №29.

2. Патент RU 2417512, H02P 8/00, опубликован 27.04.2011. Бюл. №12.

РЕЖИМ ТРЕХТАКТНЫЙ ПООЧЕРЕДНЫЙ. КОД РЕЖИМА a5а6а7=111

x1x2c4

РЕЖИМ ШЕСТИТАКТНЫЙ ПООЧЕРЕДНЫЙ. КОД РЕЖИМА a5а6а7=011

x1x2x4

РЕЖИМ ЧЕТЫРЕХТАКТНЫЙ ПАРНЫЙ. КОД РЕЖИМА а5а6а7=001

x1x2x4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 2012 |

|

RU2523047C2 |

| ЧЕТЫРЕХТАКТНЫЙ РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2010 |

|

RU2475933C2 |

| ТРЕХТАКТНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2012 |

|

RU2526859C2 |

| Устройство для программного управления шаговым двигателем | 1986 |

|

SU1352463A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 2009 |

|

RU2417512C9 |

| ТРЕХ-ШЕСТИТАКТНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 2010 |

|

RU2440664C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ РАСПРЕДЕЛИТЕЛЬ ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 2013 |

|

RU2526855C1 |

| Двухрежимный распределитель импульсов для управления трехфазным шаговым двигателем | 1981 |

|

SU1019571A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1981 |

|

SU1001423A1 |

| Устройство для программного управления четырехфазным шаговым двигателем с насыщенной магнитной системой | 1989 |

|

SU1702340A1 |

Изобретение относится к области автоматики и может быть использовано в системах с дискретным электроприводом на базе трехфазных, четырехфазных и шестифазных шаговых двигателей. Техническим результатом является расширение функциональных возможностей за счет обеспечения известных режимов коммутации и стоянки для двигателей с различным числом фазных обмоток и обеспечения работы двигателя в режиме переменной тактности, управляемой по шинам выбора коммутации. Для этого в заявленном устройстве аппаратно реализован алгоритм кодирования Хэмминга, позволяющий обнаруживать и индикатировать адрес одиночного отказа, для чего в устройство введены первая, вторая, третья схемы свертки, шины эталонных контрольных разрядов, индикатор, блок усилителей мощности с датчиками тока и напряжения в каждой фазе. 3 табл., 1 ил.

Устройство для управления шаговым двигателем, содержащее первую, вторую, третью шины выбора режима коммутации, шину управления, тактовую шину, шину реверса, шину разрешения чтения, постоянное запоминающее устройство, реверсивный счетчик, первый, второй, третий входы которого соединены с шинами управления, тактовой, реверса соответственно, а выходы первый, второй, третий, четвертый соединены с одноименными входами постоянного запоминающего устройства, входы которого пятый, шестой, седьмой, восьмой соединены с третьей, второй, первой, седьмой шинами выбора режима коммутации и разрешения чтения соответственно, первый, второй, третий, четвертый, пятый, шестой выходы постоянного запоминающего устройства, отличающееся тем, что в устройство дополнительно введены первая, вторая, третья схемы свертки, индикатор, шины эталонных контрольных разрядов, блок усилителей мощности с датчиками тока и напряжения в каждой фазе, при этом первый, второй, третий, четвертый, пятый, шестой выходы постоянного запоминающего устройства соединены с одноименными входами блока усилителей мощности, второй групповой выход усилителя мощности соединен с фазными обмотками шагового двигателя, а первый групповой выход усилителя мощности соединен со входами схем свертки, выходы которых подключены ко входам индикатора.

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 2009 |

|

RU2417512C9 |

| СПОСОБ УПРАВЛЕНИЯ ШАГОВЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2092964C1 |

| Способ получения бензальдегида | 1926 |

|

SU10440A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1987 |

|

SU1415401A1 |

| Замкнутый шаговый электропривод | 1988 |

|

SU1511840A2 |

Авторы

Даты

2014-05-20—Публикация

2011-10-04—Подача