Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в фотоприемных устройствах, решающих усилителях с малыми значениями входной проводимости).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с комплементарными входными каскадами [1-11]. Такие ОУ имеют предельно простую структуру и характеризуются малым энергопотреблением.

Предлагаемое изобретение относится к классу ОУ на базе комплементарных входных каскадов [1-11].

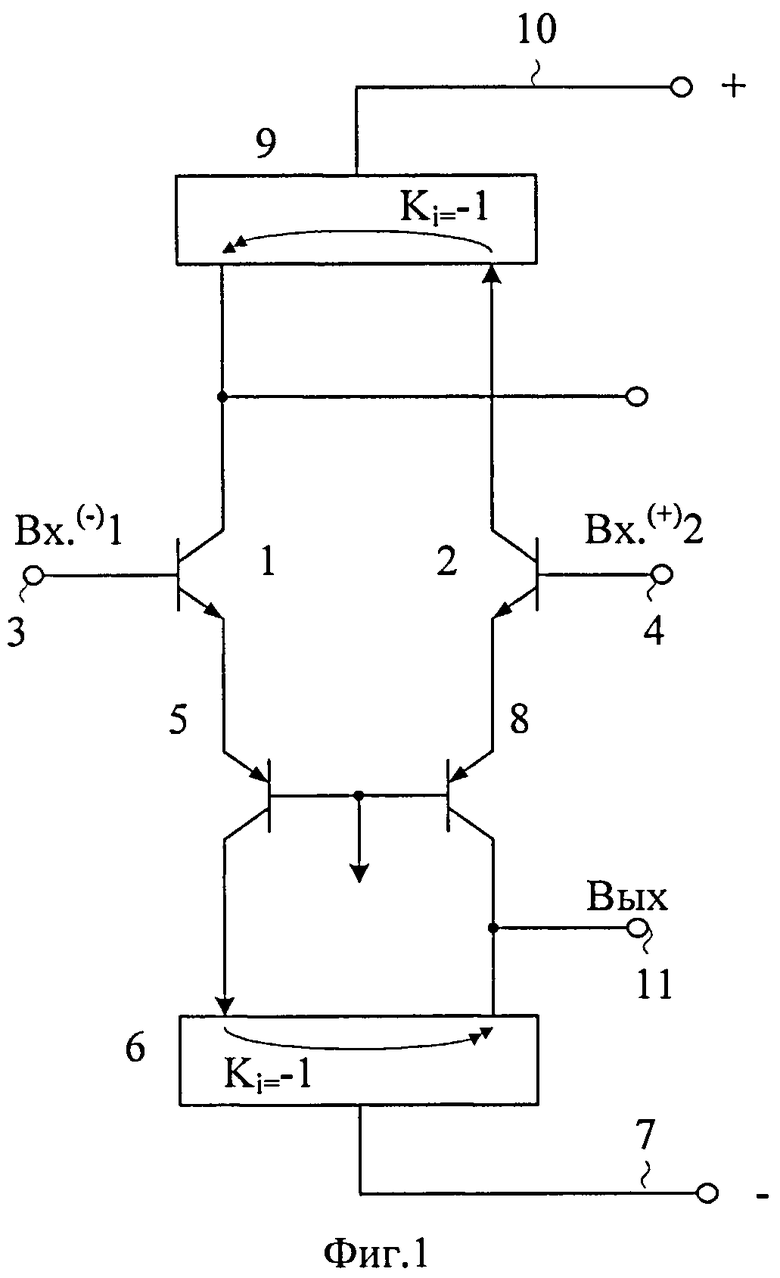

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ОУ, фиг.1, представленная в авт. свид. СССР №603097, которая также присутствует в большом числе других патентов, например [1-11]. ОУ-прототип, фиг.1, содержит первый 1 и второй 2 входные транзисторы, база первого 1 входного транзистора соединена с первым 3 инвертирующим входом устройства, база второго 2 входного транзистора соединена с первым 4 неинвертирующим входом устройства, первый 5 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор подключен ко входу первого 6 токового зеркала, согласованного с первой 7 шиной источника питания, второй 8 выходной транзистор, эмиттер которого связан с эмиттером второго 2 входного транзистора, второе 9 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого связан с коллектором второго 2 входного транзистора, причем выход устройства 11 соединен с выходом первого 6 токового зеркала.

Существенный недостаток известного ОУ, фиг.1, состоит в том, что он имеет только два входа, что не позволяет его использовать в классе достаточно перспективных активных элементов аналоговой схемотехники нового поколения - мультидифференциальных ОУ.

Основная задача предлагаемого изобретения состоит в увеличении числа входов ОУ, т.е. в создании мультидифференциального ОУ. Дополнительная задача - повышение дифференциального и синфазного входных сопротивлений по двум из четырех входов ОУ и создание условий для реализации малых напряжений смещения нуля.

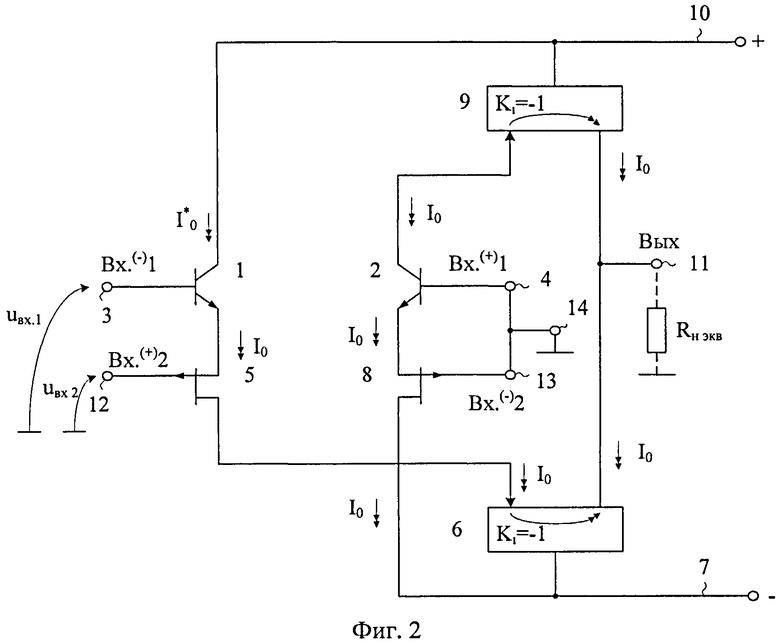

Поставленная задача достигается тем, что в мультидифференциальном операционном усилителе, содержащем первый 1 и второй 2 входные транзисторы, база первого 1 входного транзистора соединена с первым 3 инвертирующим входом устройства, база второго 2 входного транзистора соединена с первым 4 неинвертирующим входом устройства, первый 5 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор подключен ко входу первого 6 токового зеркала, согласованного с первой 7 шиной источника питания, второй 8 выходной транзистор, эмиттер которого связан с эмиттером второго 2 входного транзистора, второе 9 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого связан с коллектором второго 2 входного транзистора, причем выход устройства 11 соединен с выходом первого 6 токового зеркала, предусмотрены новые элементы и связи - в качестве первого 5 и второго 8 выходных транзисторов используются первый и второй полевые транзисторы с управляющим р-n-переходом, затворы которых соответствуют базе, стоки - коллекторам, а истоки - эмиттерам соответствующих первого 5 и второго 8 выходных транзисторов, причем коллектор первого 1 входного транзистора связан со второй 10 шиной источника питания, сток второго 8 выходного полевого транзистора связан с первой 7 шиной источника питания, выход второго 9 токового зеркала подключен к выходу устройства И, затвор первого 5 выходного полевого транзистора соединен со вторым 12 неинвертирующим входом устройства, а затвор второго 8 выходного полевого транзистора соединен со вторым 13 инвертирующим входом устройства.

Схема усилителя-прототипа показана на фиг.1.

На фиг.2 представлена схема заявляемого устройства в соответствии с п.2 формулы изобретения.

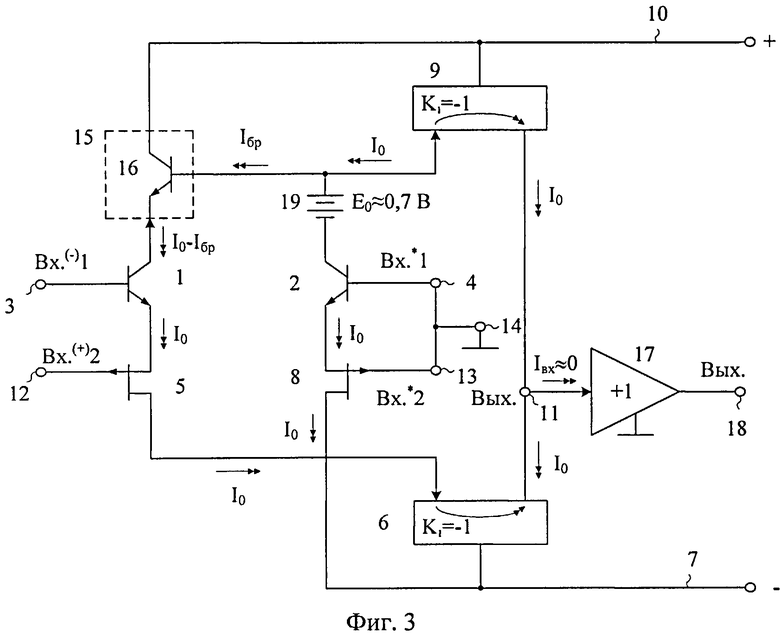

Схема ДУ, соответствующая п.3 и 4 формулы изобретения, показана на фиг.3.

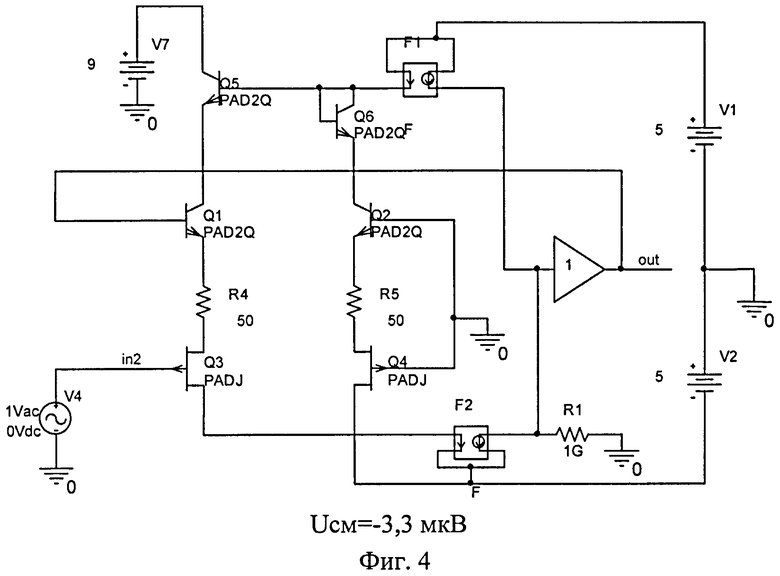

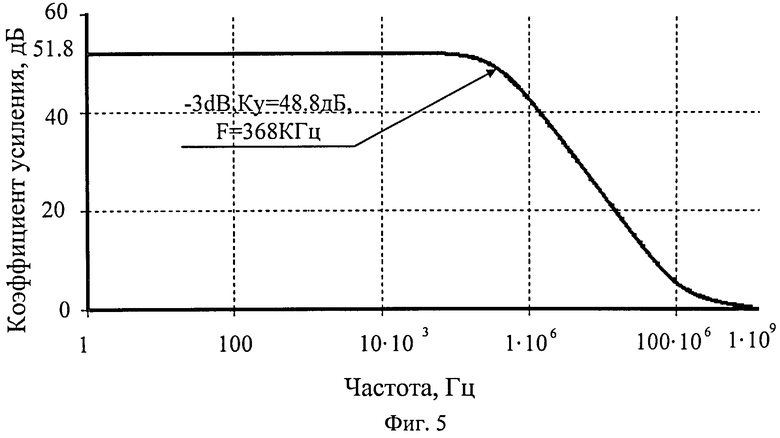

На фиг.4 представлена схема заявляемого ОУ в среде PSpice на моделях транзисторов аналогового базового матричного кристалла АБМК_1_3, соответствующая п.5 формулы изобретения, а на фиг.5 приведена зависимость коэффициента усиления по напряжению от частоты ОУ фиг.4.

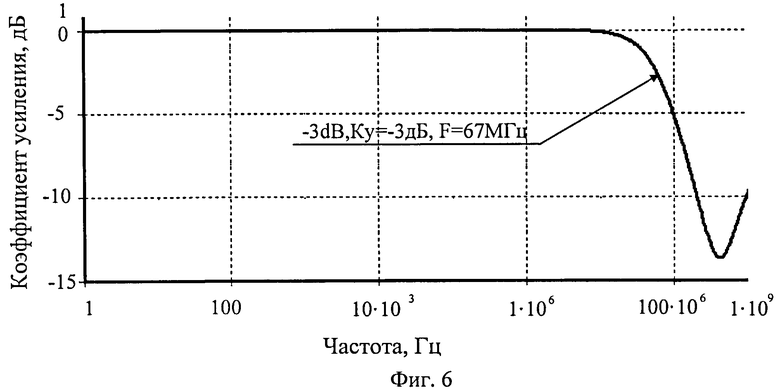

На фиг.6 представлена частотная зависимость коэффициента усиления по напряжению ОУ фиг.4 со 100% отрицательной обратной связью.

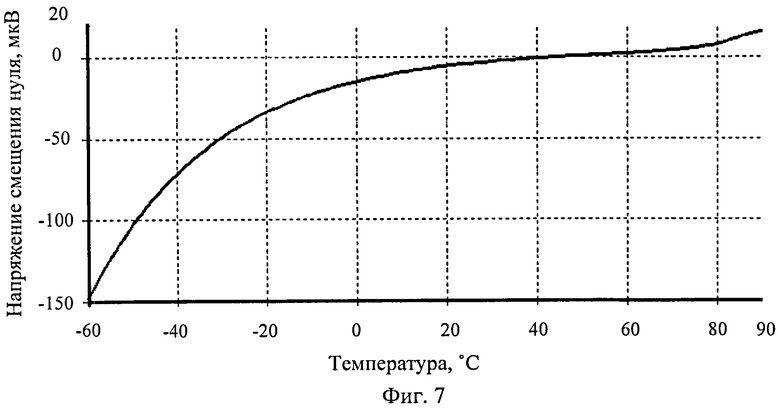

На фиг.7 представлена зависимость напряжения смещения нуля от температуры ОУ фиг.4.

Мультидифференциальный операционный усилитель содержит первый 1 и второй 2 входные транзисторы, база первого 1 входного транзистора соединена с первым 3 инвертирующим входом устройства, база второго 2 входного транзистора соединена с первым 4 неинвертирующим входом устройства, первый 5 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор подключен ко входу первого 6 токового зеркала, согласованного с первой 7 шиной источника питания, второй 8 выходной транзистор, эмиттер которого связан с эмиттером второго 2 входного транзистора, второе 9 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого связан с коллектором второго 2 входного транзистора, причем выход устройства 11 соединен с выходом первого 6 токового зеркала. В качестве первого 5 и второго 8 выходных транзисторов используются первый и второй полевые транзисторы с управляющим р-n-переходом, затворы которых соответствуют базе, стоки - коллекторам, а истоки - эмиттерам соответствующих первого 5 и второго 8 выходных транзисторов, причем коллектор первого 1 входного транзистора связан со второй 10 шиной источника питания, сток второго 8 выходного полевого транзистора связан с первой 7 шиной источника питания, выход второго 9 токового зеркала подключен к выходу устройства 11, затвор первого 5 выходного полевого транзистора соединен со вторым 12 неинвертирующим входом устройства, а затвор второго 8 выходного полевого транзистора соединен со вторым 13 инвертирующим входом устройства.

На фиг.3, в соответствии с п.2 формулы изобретения, первый 4 неинвертирующий и второй 13 инвертирующий входы устройства подключены, в частном случае, к общей шине 14 источников питания.

Кроме этого, на фиг.3, в соответствии с п.3 формулы изобретения, коллектор первого 1 входного транзистора связан со второй 10 шиной источника питания через цепь согласования потенциалов 15, выполненную в виде дополнительного транзистора 16, эмиттер которого соединен с коллектором первого 1 входного транзистора, база соединена со входом второго 9 токового зеркала, а коллектор подключен ко второй 10 шине источников питания.

Следует также заметить, что на фиг.3, в соответствии с п.4 формулы изобретения, выход устройства 11 связан со входом дополнительного буферного усилителя 17, выход которого 18 является дополнительным выходом устройства. Для симметрирования статического режима транзисторов 1 и 2 включен источник напряжения 19, в качестве которого можно использовать р-n-переход.

На фиг.4, в соответствии с п.5 формулы изобретения, в эмиттеры первого 1 и второго 2 входных транзисторов включены соответствующие первый и второй дополнительные резисторы.

Рассмотрим работу ОУ, фиг.2, который за счет новых связей имеет 4 входа 3, 12 и 1, 13, а также определим систематическую составляющую его напряжения смещения нуля Uсм.

Токи истока и стока полевых транзисторов 5 и 8 (Iи=Ic=I0) зависят от крутизны их стоко-затворной характеристики при Uзи.5=Uзи.8≈0,7 B. При идентичных эмиттерных переходах первого 1 и второго 2 входных транзисторов, а также идентичных полевых транзисторах 5 и 8, коллекторный ток транзистора 2 и ток стока транзистора 5 также будут равны величине I0. Следовательно, напряжение смещения нуля рассматриваемого ОУ

так как Uэб.1=Uзи.5, Uэб.2=Uэб.1=UA * B *, Uзи.5=Uзи.8.

Таким образом, в рассматриваемой схеме обеспечивается малое напряжение смещения нуля, который имеет за счет применения полевых транзисторов повышенные входные сопротивления по двум входам 12 и 13 для дифференциального и синфазного сигналов.

Дифференциальный коэффициент усиления по напряжению заявляемого ДУ, фиг.2:

где

S1 - крутизна стоко-затворной характеристики полевого транзистора 5;

φт = 26 мВ - температурный потенциал;

Rн.экв - эквивалентное сопротивление нагрузки ОУ, подключенной к выходу 11.

При изменении температуры (или уровня радиации) изменяется ток стока транзистора 5, который поступает на вход, а затем выход токового зеркала 6. Однако точно так же (в связи с симметрией истоковой цепи) изменяется ток истока транзистора 8 и коллекторный ток транзистора 2, который поступает на вход, а затем выход токового зеркала 9. В результате в цепи выхода 11 происходит взаимная компенсация данных приращений и поэтому Uсм изменяется незначительно.

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая напряжения смещения нуля Uсм и его дрейф.

Заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей современных систем на кристалле, реализуемых, например, по технологии аналоговых базовых матричных кристаллов АБМК_1_3.

Литература

1. Патент US 5.789.949.

2. Патент US 3.660.773.

3. Патент US 4.074.205.

4. Патентная заявка US 2010/0225392.

5. Патент GB 1543361.

6. Патент DE 2633952.

7. Патент US 4.059.808.

8. Патент RU 2.019.019.

9. Патентная заявка US 2006/0091952.

10. Патент US 5.521.553.

11. Патент US 5.010.303.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАССИВНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2012 |

|

RU2517699C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2621287C2 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2627094C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615071C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2583760C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

| ГИБРИДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2519373C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Техническим результатом является повышение входных сопротивлений для дифференциального и синфазного сигналов по двум из четырех входов ОУ. В мультидифференциальном операционном усилителе в качестве первого (5) и второго (8) выходных транзисторов используются первый и второй полевые транзисторы с управляющим р-n-переходом, затворы которых соответствуют базе, стоки - коллекторам, а истоки - эмиттерам соответствующих первого (5) и второго (8) выходных транзисторов, причем коллектор первого (1) входного транзистора связан со второй (10) шиной источника питания, сток второго (8) выходного полевого транзистора связан с первой (7) шиной источника питания, выход второго (9) токового зеркала подключен к выходу устройства (11), затвор первого (5) выходного полевого транзистора соединен со вторым (12) неинвертирующим входом устройства, а затвор второго (8) выходного полевого транзистора соединен со вторым (13) инвертирующим входом устройства. 4 з.п. ф-лы, 7 ил.

1. Мультидифференциальный операционный усилитель, содержащий первый (1) и второй (2) входные транзисторы, база первого (1) входного транзистора соединена с первым (3) инвертирующим входом устройства, база второго (2) входного транзистора соединена с первым (4) неинвертирующим входом устройства, первый (5) выходной транзистор, эмиттер которого связан с эмиттером первого (1) входного транзистора, а коллектор подключен ко входу первого (6) токового зеркала, согласованного с первой (7) шиной источника питания, второй (8) выходной транзистор, эмиттер которого связан с эмиттером второго (2) входного транзистора, второе (9) токовое зеркало, согласованное со второй (10) шиной источника питания, вход которого связан с коллектором второго (2) входного транзистора, причем выход устройства (11) соединен с выходом первого (6) токового зеркала, отличающийся тем, что в качестве первого (5) и второго (8) выходных транзисторов используются первый и второй полевые транзисторы с управляющим р-n-переходом, затворы которых соответствуют базе, стоки - коллекторам, а истоки - эмиттерам соответствующих первого (5) и второго (8) выходных транзисторов, причем коллектор первого (1) входного транзистора связан со второй (10) шиной источника питания, сток второго (8) выходного полевого транзистора связан с первой (7) шиной источника питания, выход второго (9) токового зеркала подключен к выходу устройства (11), затвор первого (5) выходного полевого транзистора соединен со вторым (12) неинвертирующим входом устройства, а затвор второго (8) выходного полевого транзистора соединен со вторым (13) инвертирующим входом устройства.

2. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что первый (4) неинвертирующий и второй (13) инвертирующий входы устройства подключены к общей шине (14) источников питания.

3. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что коллектор первого (1) входного транзистора связан со второй (10) шиной источника питания через цепь согласования потенциалов (15), выполненную в виде дополнительного транзистора (16), эмиттер которого соединен с коллектором первого (1) входного транзистора, база соединена со входом второго (9) токового зеркала, а коллектор подключен ко второй (10) шине источников питания.

4. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что выход устройства (11) связан со входом дополнительного буферного усилителя (17), выход которого (18) является дополнительным выходом устройства.

5. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что в эмиттеры первого (1) и второго (2) входных транзисторов включены соответствующие первый (19) и второй (20) дополнительные резисторы.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2014-07-20—Публикация

2013-01-09—Подача