Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в фотоприемных устройствах, решающих усилителях с малыми значениями входной проводимости).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают комплементарные каскодные ОУ [1-11]. Такие ОУ имеют предельно простую структуру и характеризуются малым энергопотреблением.

Предлагаемое изобретение относится к данному классу устройств.

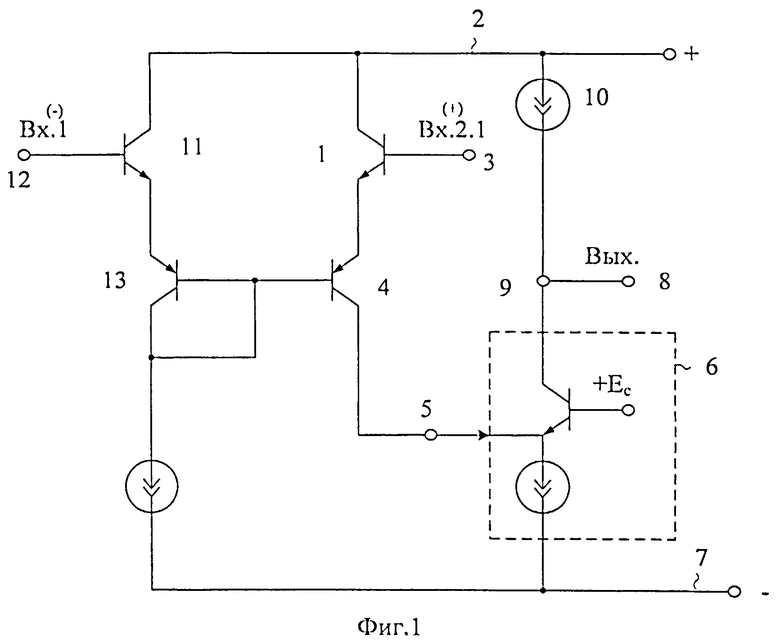

Наиболее близким по сущности к заявляемому техническому решению является классическая схема дифференциального ОУ фиг.1, представленная в патенте США №4.714.894, fig. 1, которая также присутствует в большом числе других патентов и монографий, например, [12-18]. Он содержит первый 1 входной транзистор, коллектор которого соединен с первой 2 шиной источника питания, а база подключена к первому 3 неинвертирующему входу устройства, первый 4 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор соединен с неинвертирующим входом 5 первого 6 неинвертирующего каскада, согласованного со второй 7 шиной источника питания, выход устройства 8, соединенный с токовым выходом 9 первого 6 неинвертирующего каскада и связанный с первой 2 шиной источника питания через источник тока 10, второй 11 входной транзистор, база которого связана с первым 12 инвертирующим входом устройства, а эмиттер подключен к эмиттеру второго 13 выходного транзистора.

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), что связано с несимметрией его архитектуры. Кроме этого, известный ОУ характеризуется только двумя входами, что не позволяет отнести его к подклассу мультидифференциальных ОУ.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм, а также его температурного и радиационного дрейфа.

Дополнительная задача - увеличение числа дифференциальных входов ОУ.

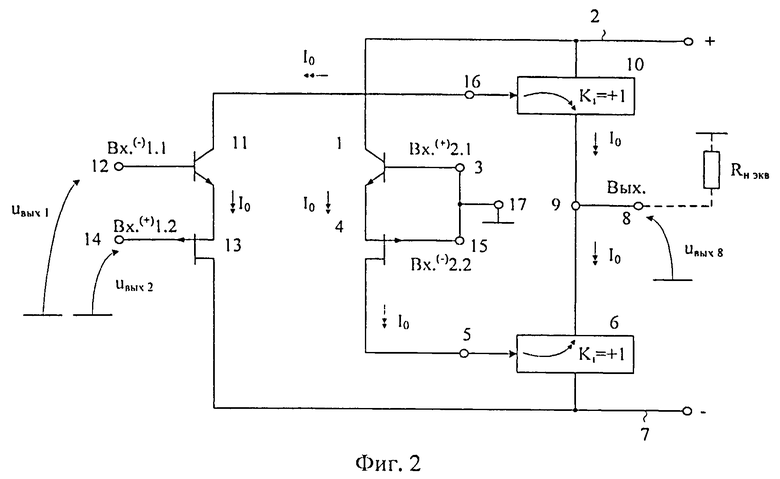

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 входной транзистор, коллектор которого соединен с первой 2 шиной источника питания, а база подключена к первому 3 неинвертирующему входу устройства, первый 4 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор соединен с неинвертирующим входом 5 первого 6 неинвертирующего каскада, согласованного со второй 7 шиной источника питания, выход устройства 8, соединенный с токовым выходом 9 первого 6 неинвертирующего каскада и связанный с первой 2 шиной источника питания через источник тока 10, второй 11 входной транзистор, база которого связана с первым 12 инвертирующим входом устройства, а эмиттер подключен к эмиттеру второго 13 выходного транзистора, предусмотрены новые элементы и связи - в качестве первого 4 и второго 13 выходных транзисторов используются полевые транзисторы с управляющим р-n переходом, затворы которых соответствуют базам, истоки - эмиттерам, а стоки - коллекторам транзисторов, затвор второго 13 выходного транзистора соединен со вторым 14 неинвертирующим входом устройства, а сток подключен ко второй 7 шине источника питания, затвор первого 4 выходного транзистора соединен со вторым 15 инвертирующим входом устройства, причем в качестве источника тока 10 используется управляемый источник тока, неинвертирующий управляющий вход 16 которого соединен с коллектором второго 11 входного транзистора.

Схема усилителя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

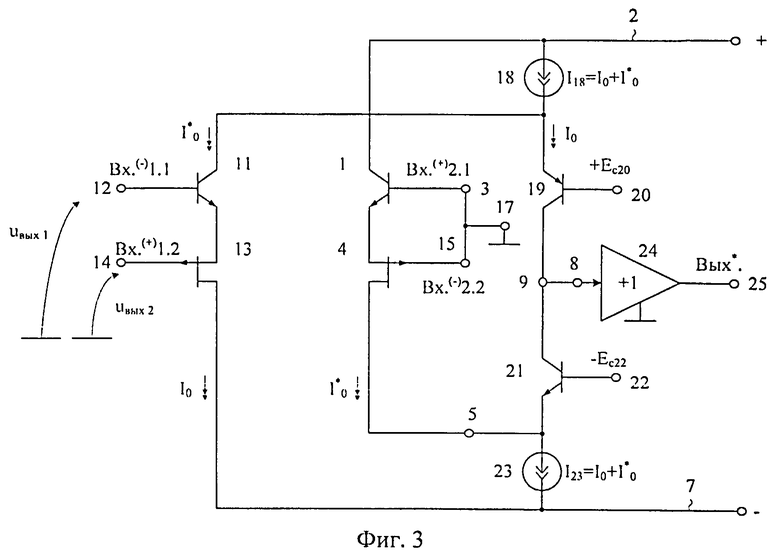

На чертеже фиг.3 показана схема фиг.2 с конкретным выполнением первого 6 неинвертирующего каскада и управляемого источника тока 10.

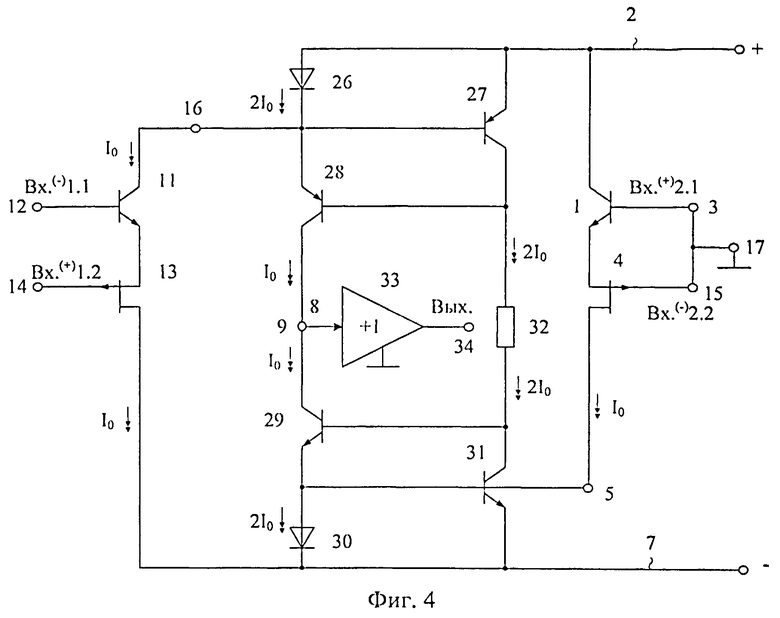

На чертеже фиг.4 показана схема фиг.2 с другим вариантом выполнения первого 6 неинвертирующего каскада и управляемого источника тока 10.

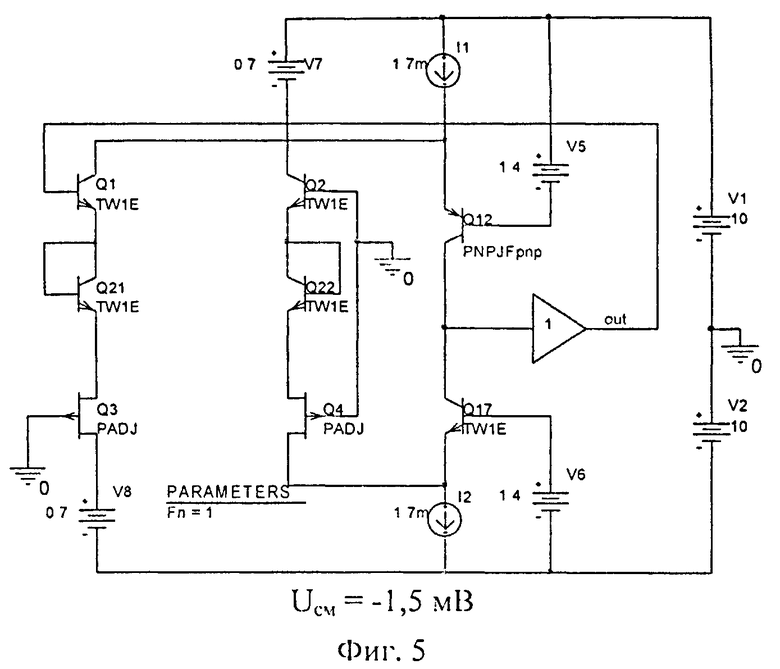

На чертеже фиг.5 представлена схема усилителя фиг.3 в среде PSpice на моделях интегральных транзисторов АБМК_1_3.

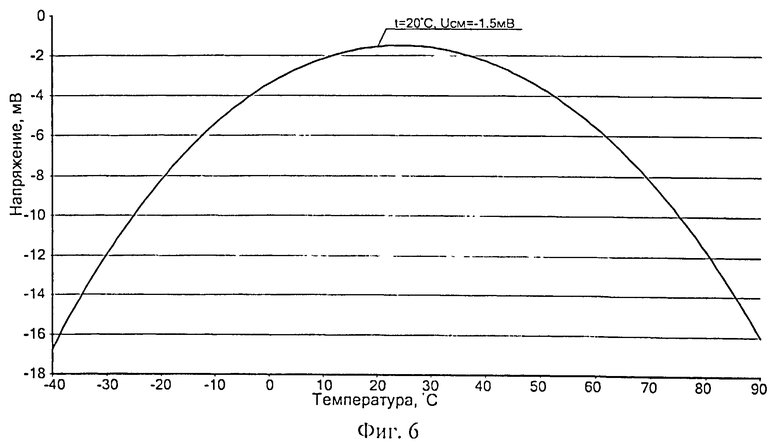

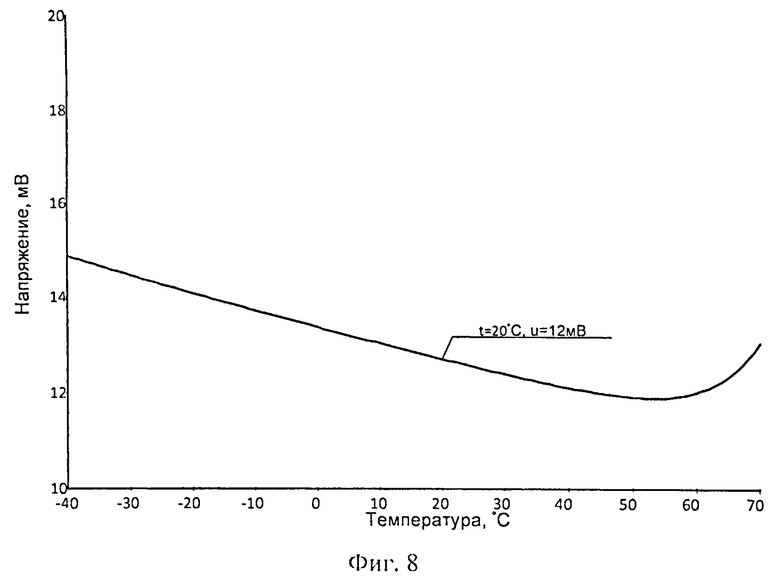

На чертеже фиг.6 показана температурная зависимость напряжения смещения нуля операционного усилителя фиг.5.

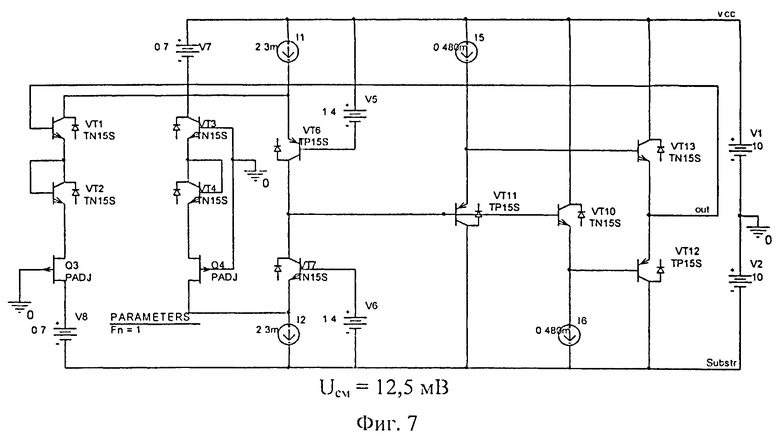

На чертеже фиг.7 приведена схема усилителя фиг.3 в среде PSpice на моделях биполярных транзисторов ФГУП НПП «Пульсар» и полевых транзисторах АБМК_1_3 с конкретным выполнением буферного усилителя 24.

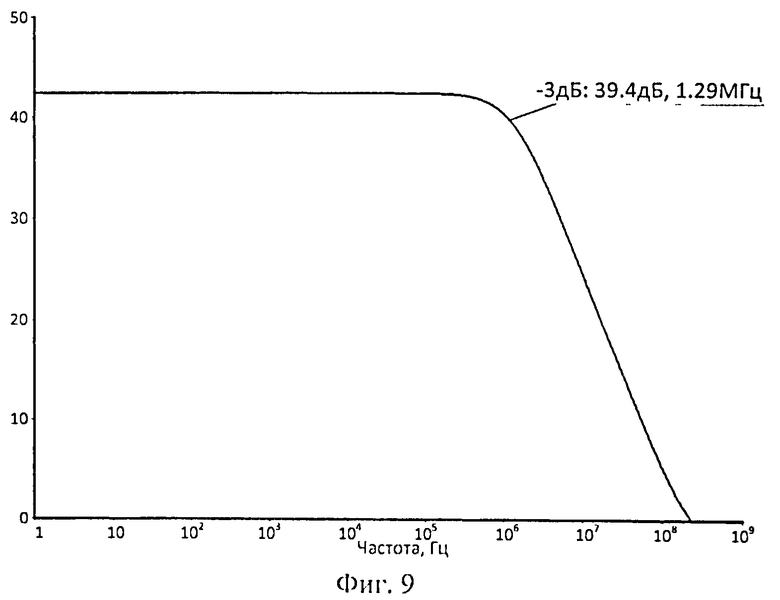

На чертеже фиг.8 представлена температурная зависимость напряжения смещения нуля ОУ фиг.7, а на чертеже фиг.9 - логарифмическая амплитудно-частотная характеристика разомкнутого ОУ фиг.7.

Дифференциальный операционный усилитель с пассивным параллельным каналом фиг.2 содержит первый 1 входной транзистор, коллектор которого соединен с первой 2 шиной источника питания, а база подключена к первому 3 неинвертирующему входу устройства, первый 4 выходной транзистор, эмиттер которого связан с эмиттером первого 1 входного транзистора, а коллектор соединен с неинвертирующим входом 5 первого 6 неинвертирующего каскада, согласованного со второй 7 шиной источника питания, выход устройства 8, соединенный с токовым выходом 9 первого 6 неинвертирующего каскада и связанный с первой 2 шиной источника питания через источник тока 10, второй 11 входной транзистор, база которого связана с первым 12 инвертирующим входом устройства, а эмиттер подключен к эмиттеру второго 13 выходного транзистора. В качестве первого 4 и второго 13 выходных транзисторов используются полевые транзисторы с управляющим р-n переходом, затворы которых соответствуют базам, истоки - эмиттерам, а стоки - коллекторам транзисторов, затвор второго 13 выходного транзистора соединен со вторым 14 неинвертирующим входом устройства, а сток подключен ко второй 7 шине источника питания, затвор первого 4 выходного транзистора соединен со вторым 15 инвертирующим входом устройства, причем в качестве источника тока 10 используется управляемый источник тока, неинвертирующий управляющий вход 16 которого соединен с коллектором второго 11 входного транзистора.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, база первого 1 входного транзистора и затвор первого 4 выходного транзистора соединены с общей шиной источников питания 17. При этом управляемый источник тока 10 реализован на основе двухполюсника 18, транзисторе 19 и цепи смещения потенциалов 20, а первый 6 неинвертирующий каскад выполнен на транзисторе 21, цепи смещения потенциалов 22 и двухполюснике 23.

На чертеже фиг.4 управляемый источник тока 10 реализован на основе р-n перехода 26, транзисторов 27 и 28, а первый 6 неинвертирующий каскад выполнен на транзисторе 29, р-n переходе 30 и транзисторе 31, а также резисторе 32. Схема также содержит буферный усилитель 33, выход которого 34 является выходом устройства.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля UCM в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

Токи истока и стока полевых транзисторов 4 и 13 (IИ=IС=I0) зависят от крутизны их стокозатворной характеристики при Uзи4=Uзи.13 ≈0,7 В. При идентичных р-n переходах первого 1 и второго 11 входных транзисторов, а также идентичных полевых транзисторах 13 и 4, коллекторный ток транзистора 11 и ток истока транзистора 4 также будут равны величине I0. Следовательно, при нулевом «разностном» токе в выходном узле 8 напряжение смещения нуля Uсм рассматриваемого ОУ близко к нулю

так как

Таким образом, в рассматриваемой схеме обеспечивается малое напряжение смещения нуля.

Дифференциальный коэффициент усиления по напряжению заявляемого ДУ фиг.2:

где

S13 - крутизна стокозатворной характеристики полевого транзистора 13;

φТ=26 мВ - температурный потенциал;

Rн.экв - эквивалентное сопротивление нагрузки ОУ, подключаемой к выходу 8.

При изменении температуры (или уровня радиации) изменяется ток стока транзистора 13. Однако точно также (в связи с симметрией эмиттерных цепей транзисторов 11 и 1) изменяется ток истока транзистора 4 и коллекторный ток транзистора 11, которые передаются к выходному узлу 8 и компенсируют друг друга. В результате Uсм схемы фиг.2 изменяется незначительно.

Таким образом, в заявляемом устройстве в связи с симметрией схемы уменьшается систематическая составляющая напряжения смещения нуля UCM и его дрейфа.

В соответствии с п.2 формулы изобретения, входы 3 и 15 могут иногда не использоваться. В этом случае транзисторы 1 и 4 образуют пассивный канал, который не участвует в передаче входного сигнала (Uвх=Uвх.2-Uвх.1) и служит только для компенсации напряжения смещения нуля ОУ. Однако компенсация Uсм сохраняется и в случае использования входов 3 и 15 для подключения к другим входным напряжениям ДУ, который становится мультидифференциальным усилителем.

Таким образом, заявляемое устройство может иметь 4 входа, обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей современных систем на кристалле, реализуемых, например, по технологии аналоговых базовых матричных кристаллов АБМК_1_3.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.415.868 fig.3

2. Патент ФРГ №2928841 fig.3

3. Патент Японии JP 54-34589, кл. 98(5) А014

4. Патент Японии JP 154-10221, кл. H03F 3/45

5. Патент Японии JP 54-102949, кл. 98(5)А21

6. Патент США №4.366.442 fig. 2

7. Патент США №6.426.678

8. Патентная заявка США 2007/0152753 fig. 5 с

9. Патент США №6.531.920, fig.

10.Патент США №4.262.261

11. Ежков Ю.А. Справочник по схемотехнике усилителей. - 2-е изд., перераб. - М: ИП РадиоСофт, 2002. - 272 с. - Рис.9.3 (стр.235).

12. Патент US 4.714.894 fig. 1

13. Патент US 6.492.871 fig. 3b, fig. 5

14. Патент US 4.749.958 fig. 2

15. Патент US 4.749.831

16. Патент US 6.249.153 fig. 9

17. Патентная заявка US 2009/0033423

18. Патент SU 1283946.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГИБРИДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2519373C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2523124C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Техническим результатом является уменьшение абсолютного значения систематической составляющей напряжения смещения нуля и его температурного и радиационного дрейфа. Дифференциальный операционный усилитель с пассивным параллельным каналом содержит два входных транзистора, два выходных транзистора, являющиеся полевыми транзисторами с управляющим p-n переходом, неинвертирующий каскад и управляемый источник тока. 1 з.п. ф-лы, 9 ил.

1. Дифференциальный операционный усилитель с пассивным параллельным каналом, содержащий первый (1) входной транзистор, коллектор которого соединен с первой (2) шиной источника питания, а база подключена к первому (3) неинвертирующему входу устройства, первый (4) выходной транзистор, эмиттер которого связан с эмиттером первого (1) входного транзистора, а коллектор соединен с неинвертирующим входом (5) первого (6) неинвертирующего каскада, согласованного со второй (7) шиной источника питания, выход устройства (8), соединенный с токовым выходом (9) первого (6) неинвертирующего каскада и связанный с первой (2) шиной источника питания через источник тока (10), второй (11) входной транзистор, база которого связана с первым (12) инвертирующим входом устройства, а эмиттер подключен к эмиттеру второго (13) выходного транзистора, отличающийся тем, что в качестве первого (4) и второго (13) выходных транзисторов используются полевые транзисторы с управляющим р-n переходом, затворы которых соответствуют базам, истоки - эмиттерам, а стоки - коллекторам транзисторов, затвор второго (13) выходного транзистора соединен со вторым (14) неинвертирующим входом устройства, а сток подключен ко второй (7) шине источника питания, затвор первого (4) выходного транзистора соединен со вторым (15) инвертирующим входом устройства, причем в качестве источника тока (10) используется управляемый источник тока, неинвертирующий управляющий вход (16) которого соединен с коллектором второго (11) входного транзистора.

2. Дифференциальный операционный усилитель с пассивным параллельным каналом по п.1, отличающийся тем, что база первого (1) входного транзистора и затвор первого (4) выходного транзистора соединены с общей шиной источников питания (17).

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| Дифференциальный усилитель | 1990 |

|

SU1771065A1 |

| Операционный усилитель | 1986 |

|

SU1336201A1 |

| WO 1993017493 A1, 02.09.1993 | |||

| US 4714894 A1, 22.12.1987 | |||

Авторы

Даты

2014-05-27—Публикация

2012-12-24—Подача