Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в фотоприемных устройствах, решающих усилителях с малыми значениями входной проводимости и т.п.).

В современной радиоэлектронной аппаратуре находят применение дифференциальные усилители (ДУ) с существенными различными параметрами.

Особое место занимают комплементарные каскадные дифференциальные усилители [1-11]. Такие ДУ имеют предельно простую структуру и характеризуются наименьшим энергопотреблением.

Предлагаемое изобретение относится к данному классу устройств.

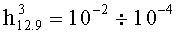

Наиболее близким по сущности к заявляемому техническому решению является классическая схема комплементарного дифференциального каскада фиг.1, представленная в патенте США №6.781.459 fig. 4, которая также присутствует в большом числе других патентов и монографиях, например, [1-11]. Он содержит первый 1 входной транзистор, база которого подключена к неинвертирующему входу 2 устройства, коллектор связан с первой 3 шиной источника питания, а эмиттер - соединен с эмиттером второго 4 входного транзистора, причем база второго 4 входного транзистора соединена с инвертирующим входом 5 устройства, а его коллектор соединен с выходом 6 устройства и связан со второй 7 шиной источника питания через цепь нагрузки 8.

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм=1,4÷1,5 B), что связано с несимметрией его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения UСМ, а также его температурного и радиационного дрейфа.

Поставленная задача достигается тем, что в комплементарном дифференциальном усилителе фиг.1, содержащем первый 1 входной транзистор, база которого подключена к неинвертирующему входу 2 устройства, коллектор связан с первой 3 шиной источника питания, а эмиттер соединен с эмиттером второго 4 входного транзистора, причем база второго 4 входного транзистора соединена с инвертирующим входом 5 устройства, а его коллектор соединен с выходом 6 устройства и связан со второй 7 шиной источника питания через цепь нагрузки 8, предусмотрены новые элементы и связи, в качестве первого 1 входного транзистора используется первый 1 полевой транзистор с управляющим p-n переходом, затвор которого соответствует базе, исток - эмиттеру, а сток - коллектору биполярного транзистора, а цепь нагрузки 8 содержит второй 9 полевой транзистор с управляющим p-n переходом, затвор которого соединен со второй 7 шиной источника питания, сток связан с коллектором второго 4 входного транзистора, а исток связан со второй 7 шиной источника питания через дополнительный p-n переход 10, идентичный эмиттерно-базовому переходу второго 4 входного транзистора.

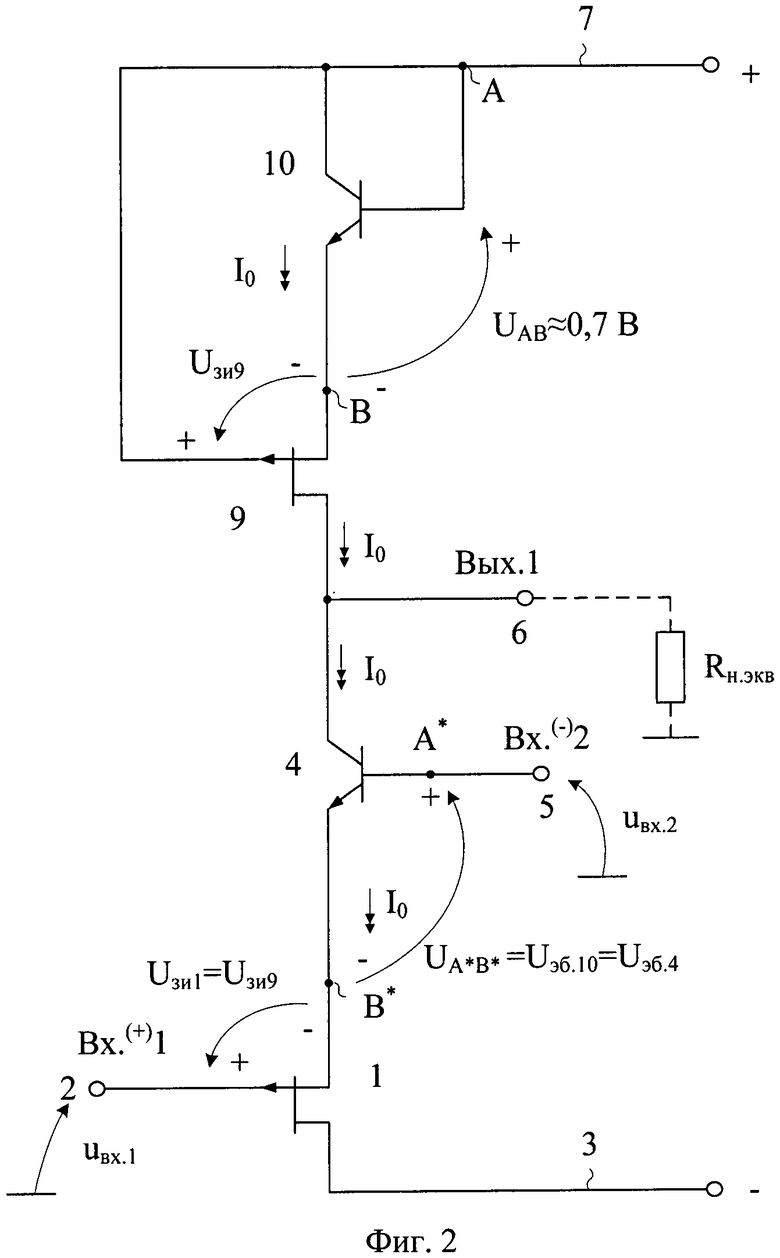

Схема усилителя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

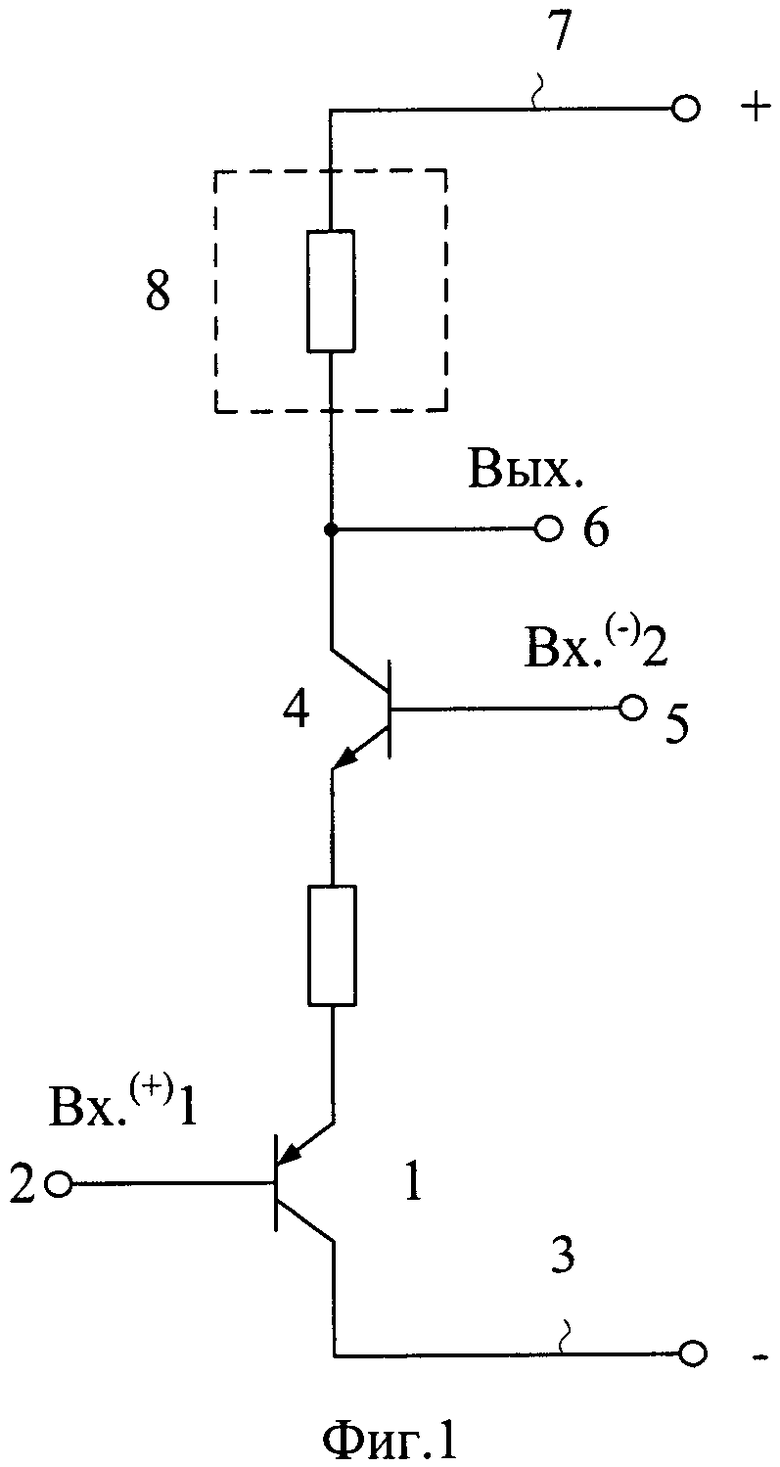

Схема ДУ, соответствующая п.2 формулы изобретения, показана на чертеже фиг.3.

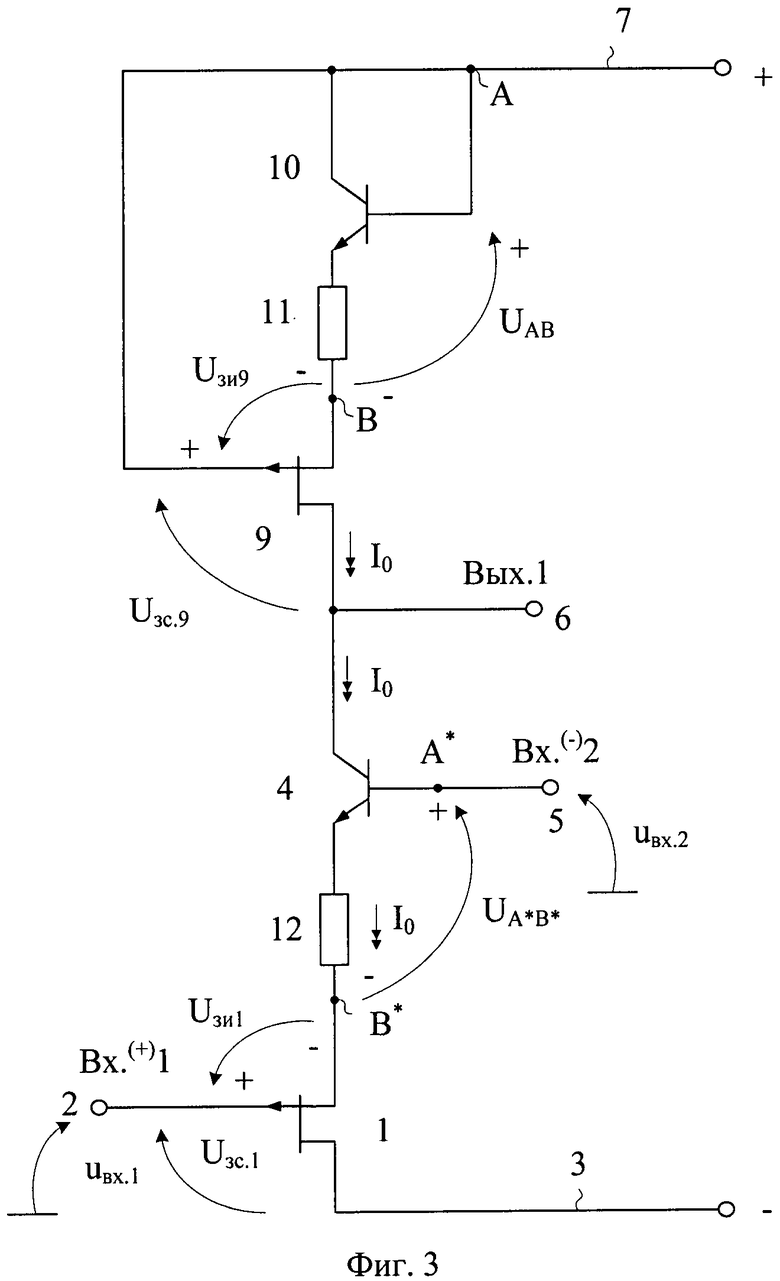

На чертеже фиг.4 приведена схема операционного усилителя на основе заявляемого ДУ, в котором включен дополнительный буферный усилитель на транзисторе 13 и источнике смещения потенциалов 14, а также введена 100% отрицательная обратная связь с выхода 15 на вход 5.

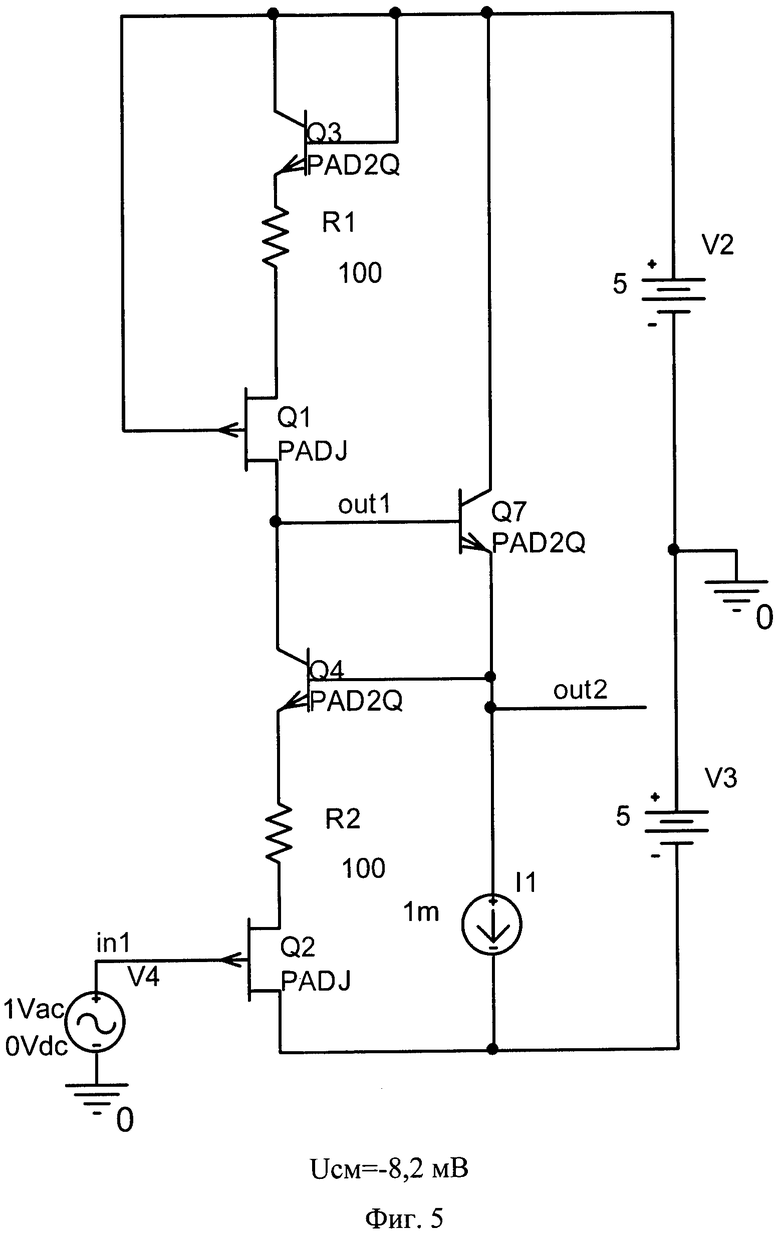

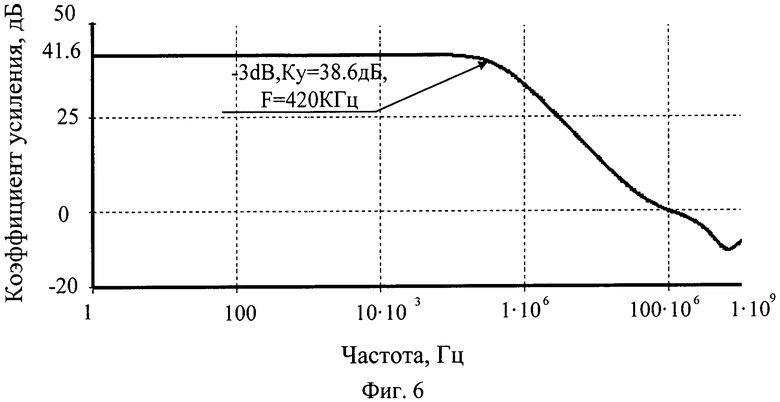

Схема ОУ в среде PSpice на моделях транзисторов аналогового базового матричного кристалла, соответствующая чертежу фиг.4, приведена на чертеже фиг.5, а зависимость коэффициента усиления по напряжению от частоты данного (разомкнутого) ОУ представлена на чертеже фиг.6. Напряжение смещения нуля ОУ фиг.5 соответствует Uсм=-8,2 мВ.

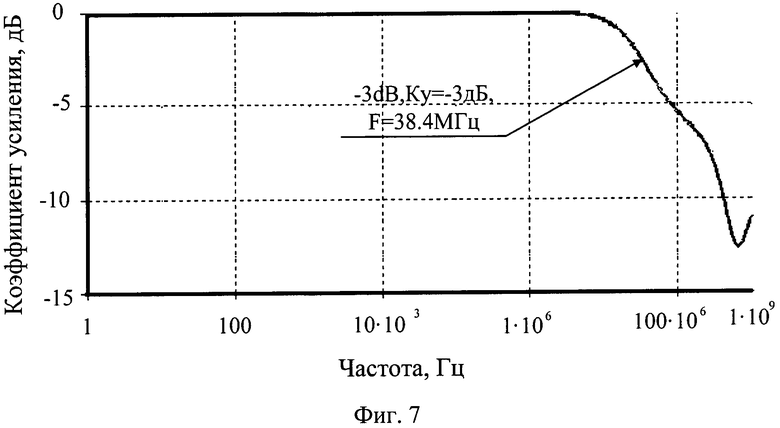

На чертеже фиг.7 приведена зависимость коэффициента усиления по напряжению от частоты ОУ фиг.5 при 100% отрицательной обратной связи.

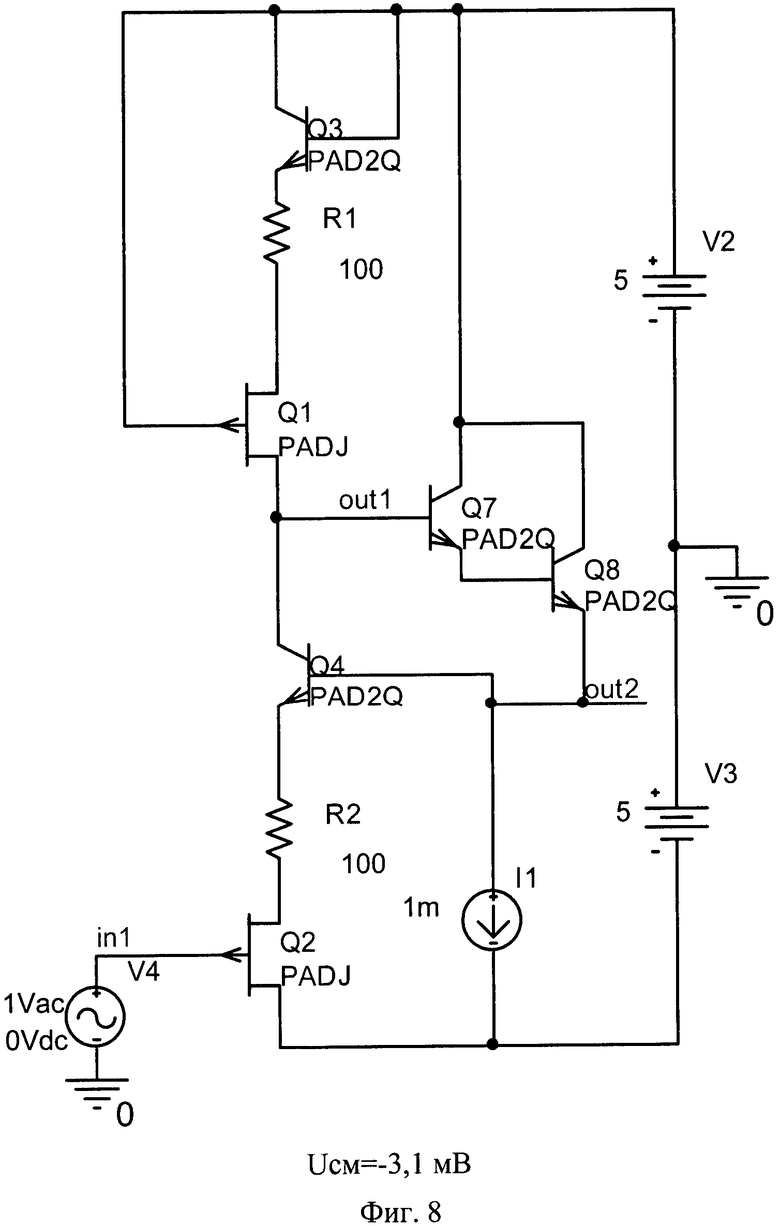

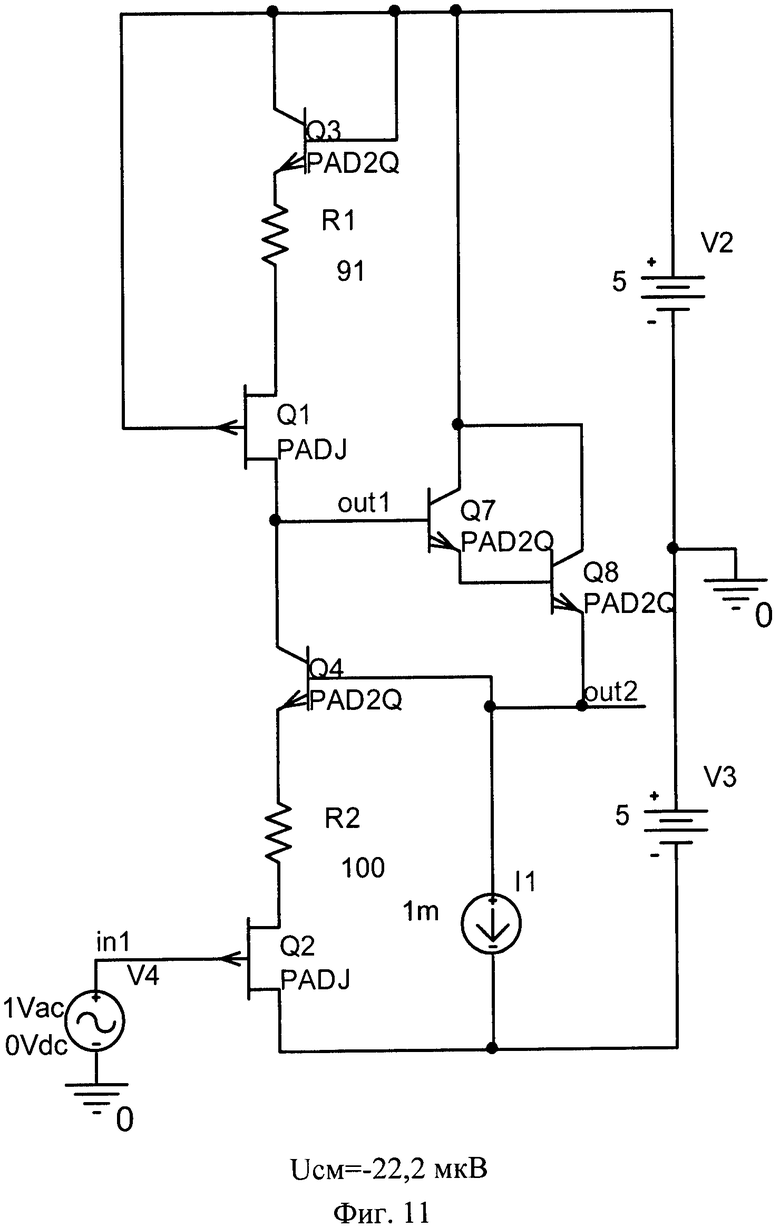

Схема фиг.8 соответствует чертежу фиг.5, однако выходной буферный усилитель выполнен здесь в виде составного транзистора Q7, Q8, а напряжение смещения нуля данного ОУ соответствует Uсм=-3,1 мВ.

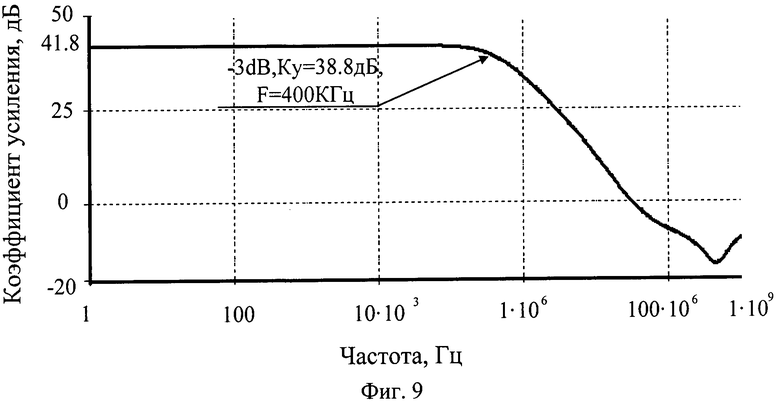

На чертеже фиг.9 представлена частотная зависимость коэффициента усиления по напряжению ОУ фиг.8 без обратной связи.

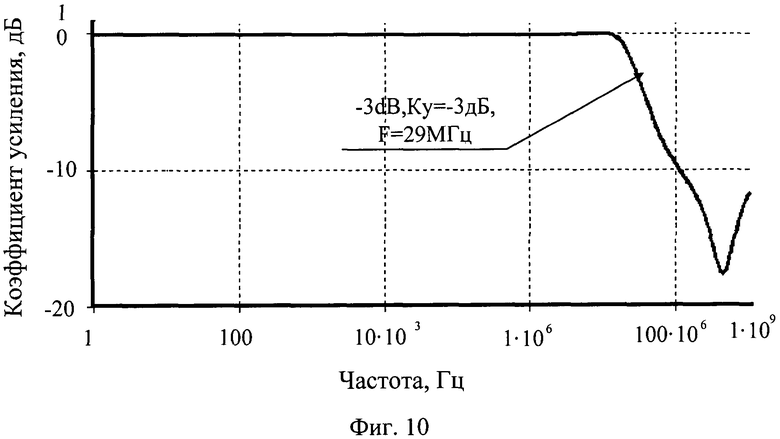

На чертеже фиг.10 приведена зависимость коэффициента усиления по напряжению от частоты ОУ фиг.8 при 100% отрицательной обратной связи.

На чертеже фиг.11 приведена схема ОУ фиг.8, в котором за счет уменьшения резистора R1 обеспечено малое напряжение смещения нуля (Uсм=-22,2 мкВ).

Гибридный дифференциальный усилитель фиг.2 содержит первый 1 входной транзистор, база которого подключена к неинвертирующему входу 2 устройства, коллектор связан с первой 3 шиной источника питания, а эмиттер соединен с эмиттером второго 4 входного транзистора, причем база второго 4 входного транзистора соединена с инвертирующим входом 5 устройства, а его коллектор соединен с выходом 6 устройства и связан со второй 7 шиной источника питания через цепь нагрузки 8. В качестве первого 1 входного транзистора используется первый 1 полевой транзистор с управляющим p-n переходом, затвор которого соответствует базе, исток - эмиттеру, а сток - коллектору биполярного транзистора, а цепь нагрузки 8 содержит второй 9 полевой транзистор с управляющим p-n переходом, затвор которого соединен со второй 7 шиной источника питания, сток связан с коллектором второго 4 входного транзистора, а исток связан со второй 7 шиной источника питания через дополнительный p-n переход 10, идентичный эмиттерно-базовому переходу второго 4 входного транзистора.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, в цепь истока первого 1 и второго 9 полевых транзисторов с управляющим p-переходом включены соответственно первый 11 и второй 12 дополнительные резисторы.

На чертеже фиг.4 в схему включен дополнительный буферный усилитель на транзисторе 13 и источнике напряжения смещения 14, выход которого соединен с выходом устройства 15.

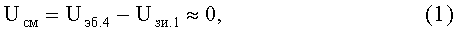

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

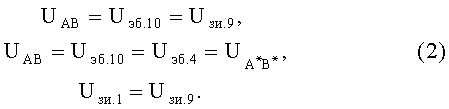

Ток истока и стока полевого транзистора 9 (IИ=IС=I0) зависит от крутизны его стокозатворной характеристики при Uзи.9=UAB≈0,7В. При идентичных p-n переходах второго 4 входного транзистора и дополнительного p-n перехода 10, а также идентичных полевых транзисторах 1 и 9 эмиттерный ток транзистора 4 и ток истока транзистора 1 также будут равны величине I0. Следовательно, напряжение смещения нуля рассматриваемого ДУ в соответствии с его определением [12]

так как

Таким образом, в рассматриваемой схеме обеспечивается малое напряжение смещения нуля.

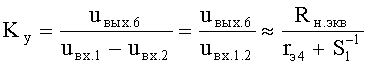

Дифференциальный коэффициент усиления по напряжению заявляемого ДУ фиг.2:

где

S1 - крутизна стокозатворной характеристики полевого транзистора 1;

φт=26 мВ - температурный потенциал;

Rн.экв - эквивалентное сопротивление нагрузки ДУ.

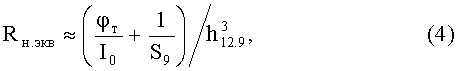

Причем

где S9 - крутизна стокозатворной характеристики полевого транзистора 9;

При изменении температуры (и уровня радиации) изменяется ток стока транзистора 9. Однако точно так же (в связи с симметрией эмиттерной цепи) изменяется ток истока транзистора 1 и коллекторный ток транзистора 4. В результате Uсм схемы изменяется незначительно.

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая напряжения смещения нуля Uсм.

Следовательно, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей современных систем на кристалле, реализуемых, например, по технологии аналоговых базовых матричных кристаллов АБМК_1_3.

Библиографический список

1. Патент США №4.415.868 fig. 3

2. Патент ФРГ №2928841 fig. 3

3. Патент Японии JP 54-34589, кл. 98(5) А014

4. Патент Японии JP 154-10221, кл. H03F 3/45

5. Патент Японии JP 54-102949, кл. 98(5) А21

6. Патент США №4.366.442 fig. 2

7. Патент США №6.426.678

8. Патентная заявка США 2007/0152753 fig. 5 с

9. Патент США №6.531.920, fig.4

10. Патент США №4.262.261

11. Ежков Ю.А. Справочник по схемотехнике усилителей. - 2-е изд., перераб. - М.: ИП РадиоСофт, 2002. - 272 с. - Рис.9.3 (стр.235).

12. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАССИВНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2012 |

|

RU2517699C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2523124C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2621287C2 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Техническим результатом является уменьшение систематической составляющей напряжения смещения нуля, а также его температурного и радиационного дрейфа. Гибридный дифференциальный усилитель содержит первый (1) входной транзистор, база которого подключена к неинвертирующему входу (2) устройства, коллектор связан с первой (3) шиной источника питания, а эмиттер соединен с эмиттером второго (4) входного транзистора, причем база второго (4) входного транзистора соединена с инвертирующим входом (5) устройства, а его коллектор соединен с выходом (6) устройства и связан со второй (7) шиной источника питания через цепь нагрузки (8). В качестве первого (1) входного транзистора используется первый (1) полевой транзистор с управляющим p-n переходом, затвор которого соответствует базе, исток - эмиттеру, а сток - коллектору биполярного транзистора, а цепь нагрузки (8) содержит второй (9) полевой транзистор с управляющим p-n переходом, затвор которого соединен со второй (7) шиной источника питания, сток связан с коллектором второго (4) входного транзистора, а исток связан со второй (7) шиной источника питания через дополнительный p-n переход (10), идентичный эмиттерно-базовому переходу второго (4) входного транзистора. 1 з.п. ф-лы, 11 ил.

1. Гибридный дифференциальный усилитель, содержащий первый (1) входной транзистор, база которого подключена к неинвертирующему входу (2) устройства, коллектор связан с первой (3) шиной источника питания, а эмиттер соединен с эмиттером второго (4) входного транзистора, причем база второго (4) входного транзистора соединена с инвертирующим входом (5) устройства, а его коллектор соединен с выходом (6) устройства и связан со второй (7) шиной источника питания через цепь нагрузки (8), отличающийся тем, что в качестве первого (1) входного транзистора используется первый (1) полевой транзистор с управляющим p-n переходом, затвор которого соответствует базе, исток - эмиттеру, а сток - коллектору биполярного транзистора, а цепь нагрузки (8) содержит второй (9) полевой транзистор с управляющим p-n переходом, затвор которого соединен со второй (7) шиной источника питания, сток связан с коллектором второго (4) входного транзистора, а исток связан со второй (7) шиной источника питания через дополнительный p-n переход (10), идентичный эмиттерно-базовому переходу второго (4) входного транзистора.

2. Гибридный дифференциальный усилитель по п.1, отличающийся тем, что в цепь истока первого (1) и второго (9) полевых транзисторов с управляющим p-n переходом включены соответственно первый (11) и второй (12) дополнительные резисторы.

| US 6781459 B1, 24.08.2004 | |||

| US 4366442, 28.12.1982 | |||

| DE 2928841 A1, 31.01.1980 | |||

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2006 |

|

RU2321157C1 |

Авторы

Даты

2014-06-10—Публикация

2012-12-13—Подача