Изобретение относится к вычислительной технике и может быть использовано для определения технического состояния блоков, вычислительного комплекса, которые через промежутки времени выдают сигнал, свидетельствующий о их работоспособности,

Целью изобретения является повышение достоверности функционирования устройства,

На фиг.1 представлена структурная схема устройства; на фиг 2 - схема блока управления.

Устройство содержит объекты 1-1.,.1-п контроля, регистр 2, элемент 3 задержки, первый 4, второй 5 и третий 6 элементы И, первый 7, второй 8 и третий 9 сумматоры, четрертый 10. пятый 11 и шестой 12 элементы И, дешифратор 13, седьмой элемент И 14, первый элемент ИЛИ 15, четвертый 16 и пятый 17 сумматоры восьмой 18. девятый 19, десятый 20, одиннадцатый 21 и двенадцатый 22 элементы И, генератор 23 импульсов, тринадцатый элемент И 24, второй элемент ИЛИ 25, шестой 26 и седьмой 27о сумматоры, блок 28 управления, четырнадцатый 29, пятнадцатый 30. шестнадцатый 31, семнадцатый 32, восемнадцатый 33 и девятнадцатый 34 элементы И, третий элемент ИЛИ 35, двадцатый элемент И 36, восьмой 37 и девятый 38 сумматоры, счетчик 39 импульсов, двадцать первый 40, двадцать второй 41, двадцать третий 42, двадцать четвертый 43 и двадцать пятый 44 Элементы И. элемент 45 сравнения, элемент НЕ 46. группу 47 элементов И, блок 48 индикации, шину Сброс, информационные выходы ori и аг, управляющий вход Сброс, управляющий вход самопроверки УСп.

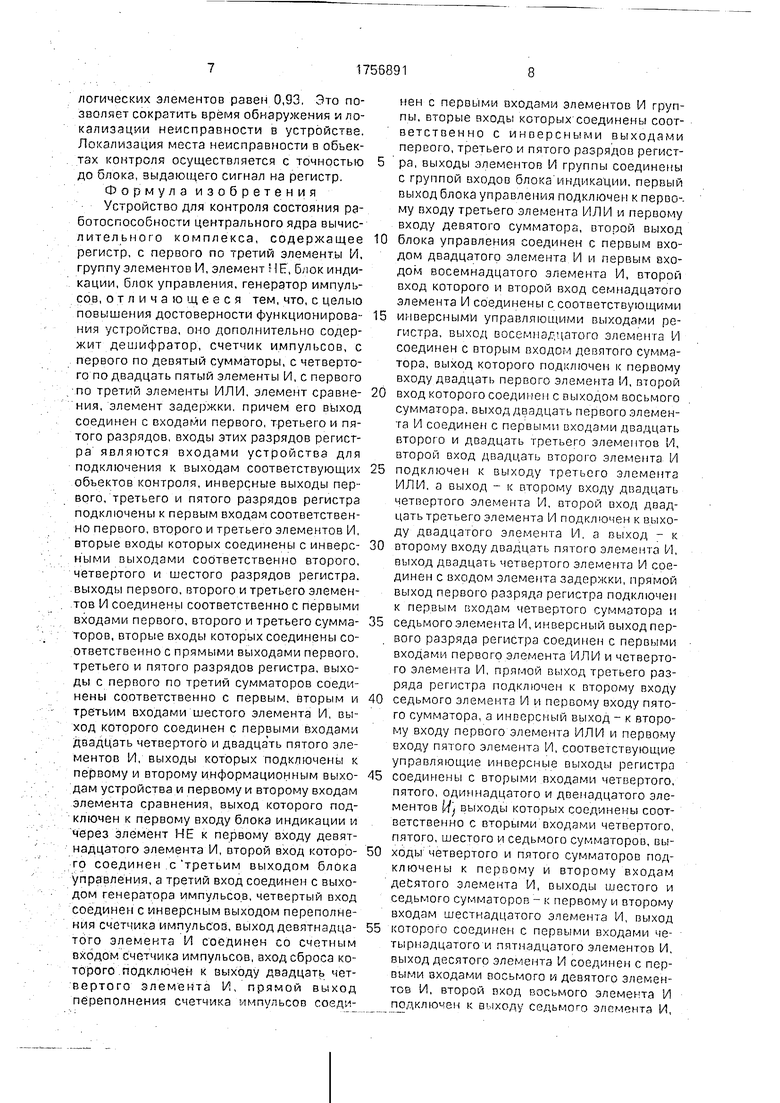

Блок 28 управления (фиг.2) содержит переключатель 29 Питание, переключатель 50 Пуск, первое реле 51, первый замыкающий контакт 52 первого реле 51, второй размыкающий контакт 53 первого реле 51,

XI

ся о ш ю

третий размыкающий контакт БД реле 51, второе реле 55, первый замыкающий контакт 56-реле 55, второй замыкающий контакт 57, реле 55, третий размыкающий контакт 58 реле 55, третье реле 59, замыкающий контакт 60 реле 59.

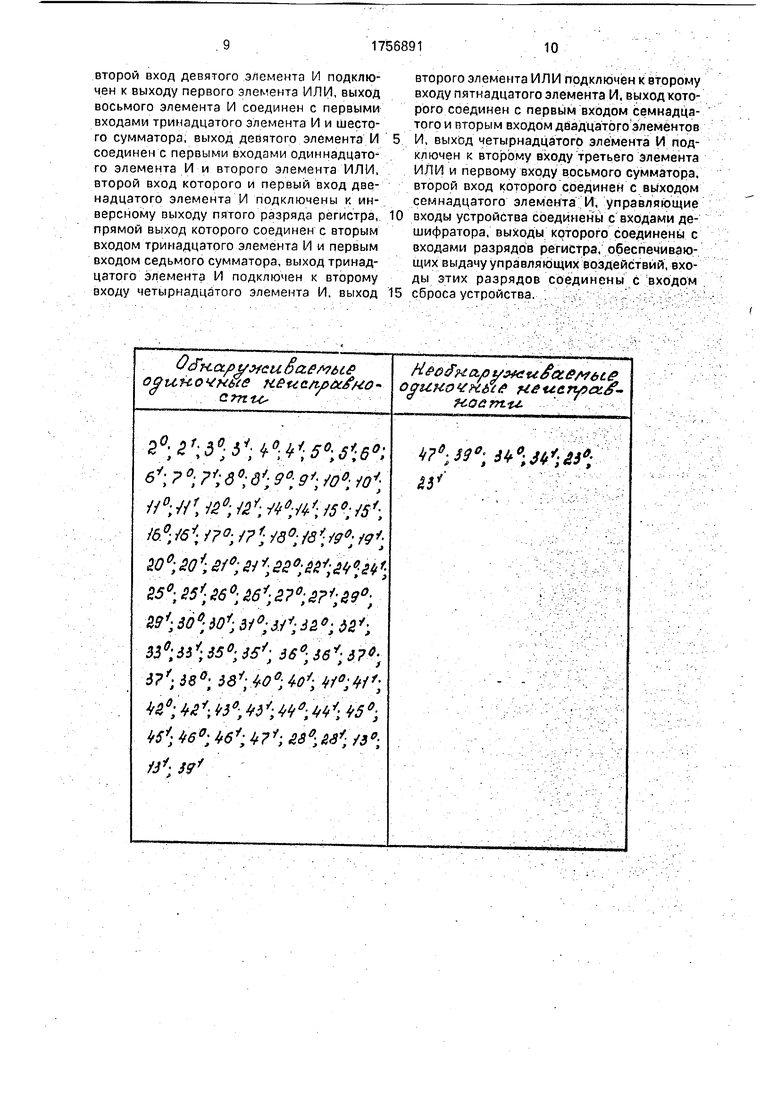

В таблице представлены функции неисправностей для одиночных неисправностей типа const 0 и const Г , выявляемых о устройстве.

Устройство работает следующим образом.

Объекты 1-1 ...1-п контроля должны выдавать через определенное время т сигнал, свидетельствующий о том, что они работоспособны. Исходы из величины г выбирается емкость счетчика 39 импульсов и частота генератора 23 импульсов. Это необходимо, чтобы заданный отрезок временитобъекгы 1-1 ...1-п контроле правильно реализовали заданный участок программы. С обьектов 1-1.,.1-п контроля за время не более чем т поступает в регистр 2 единичный сигнал, если этот объект 1-1...1-п контроля исправен, и ноль - в противном случае Сигнал, поступающий с объектом 1-1... l-n контроля, перебрасывает в единичное состояние свой разряд регистра 2.

Для приведения разрядов регистра 2 в исходное состояние подается сигнал, эквивалентный логической единице, на шину Сброс.

При включении переключателя 49 Питание в блоке 28 управления им выдается сигнал, эквивалентный логической единице с первого выхода. С второго выхода снимается сигнал, эквивалентный логическому нулю. Аналогичный сигнал снимается с третьего выхода блока 28 управления.

На выходе аг в этом случае формируется сигнал, эквивалентный логическому нулю, а на выходе а - сигнал, эквивалентным логической единице.

На выходе RS-триггеров регистра 2, соответствующих объектам 1-1...1-п контроля, формируется код 10 или 01 , т.е. RS- триггеры могут находиться в единичном или в исходном (нулевом) состоянии Если RS- триггер находится в единичном состоянии, то сигнал, эквивалентный логическому нулю, поступает на первый вход соответствующего элемента 14, например первого элемента И 4, на второй вход которого поступает сигнал,эквивалентный логической единице, с инверсного выхода соответствующего RS-триггера регистра 2, Сигнал, эквивалентный логическому нулю, с выхода первого элемента И 4, поступает на второй вход первого сумматора 7, на первый ЧУОД

которого поступает сигнал, эквивалентный логической единице с прямого выхода соответствующего RS-триггера регистра 2. Сигнал, эквивалентный логической единице, с

выхода сумматора 7 поступает на первый вход элемента И 12. Допустим, RS-триггер решстра 2, соответствующий объекту 1-2 контроля, находится в исходном состоянии, тотда с выхода элемента И 5 сигнал, экоива0 лентный логической единице, поступает на второй вход сумматора 8, а на его первый вход поступает сигнал, эквивалентный логическому нулю, с вывода второго сумматора 8 сигнал, эквивалентный логической едини5 це, поступает на второй вход элемента И 12 ил.д Таким образом, на псе входы элемента 1/1 12 поступает сигнал, эквивалентный логической единице. Сигнал, эквивалентный логической единице,с выхода элемента И 12

0 поступает на второй вход элемента И 43. На выходе элемента 14 43 появляется сигнал, эквивалентный лошчеекой единице, который приводит счетчик 39 импульсов в исходное состояние и через элемент 3 задержки

5 приводит соответствующие разряды регистра 2 в исходное состояние, т.е. устройство готово к работе.

При нажзтии кнопки 50 Пуск в блоке 28 управления сработает реле 51, которое

0 своим замыкающим контактом 52 обеспечивает срабатывание реле 55, размыкающим контактом 53 реле 51 разрывается цепь подачи напряжения па роле 59, а размыкающим контактом 54 разрывается цепь подачи сиг5 нала, эквивалентного логической единице, на первый выход блока 28 управления. Реле 55, сработав, своим замыкающим контактом 50 становится на самоблокировку, замыкающим контактом 57 готовится цепь сраба0 тывания реле 59, а размыкающим контактом 58 разрывается цепь срабатывания реле 59, а размыкающим контактом 58 разрывается цепь подачи сигнала, эквивалентного логической единице, на первый выход блока 28

5 управления.

При отпускании кнопки 50 Пуск в блоке 28 управления реле 51 обесточивается, размыкая свой контакт 52 и замыкая свои контакты 53 и 54. Срабатывает реле 59 и

0 своим контактом 60 обеспечивает подачу сигнала, эквивалентного логической единице, на третий выход блока 28 управления. Сигнал, эквивалентный логической единице, через контакт 56 реле 55 подается на

5 аторой выход блока 28 управления. Таким образом, но первом и втором выходах блока 28 упр птечия устанавливается сигнал 01, что приводит к изменению выходного сип эла на выходах а и Л2,он устанавливается в тачальное положение 01

На первый вход схемы 45 сравнения поступает сигнал, эквивалентный логической единице, с выхода «2, а на второй - эквивалентный логическому нулю с выхода «1. С выхода элемента 45 сравнения сигнал, эквивалентный логическому нулю, поступает на вход элемента НЕ 46, а с его выхода сигнал, эквивалентный логической единице, поступает на первый вход элемента И 34, на второй вход которого поступает сигнал, эквивалентный логической единице, с третьего выхода блока 28 управления, что соответствует команде Пуск

Одновременно с запуском в работу обь- ектов 1-1.,.1-п контроля начинает работать генератор 23 импульсов Импульсы с генератора 23 импульсов поступают через элемент И 34 в счетчик 39 импульсов, рассчитанный на заполнение определенного количества импульсов соответствующего времени г

Если со всех обьектов 1-1 1-п контроля поступил сигнал за время менее г об их исправном состоянии в регистр 2, то на выходе элемента И 29 появится сигнал эквивалентный логической единице, а на выходе элемента И 30 - сигнал, эквивалентный логическому нулю Эти сигналы передаются на выходы устройства На выходе а устанавливается сигнал эквивалентный логической единице, а на выходе «2 - сигнал, эквивалентный логическому нулю Сигнал, эквивалентный логической единице, с выхода щ сбрасывает в исходное состояние счетчик 39 импульсов и через элемент 3 задержки соответствующие разряды регистра 2. Далее объекты 1-1 1-п контроля реализуют следующий участок программы

В случае, если в одном или в нескольких объектах 1-1. .1-п контроля появится неисправность, то на выходах ш и ii сигналы не изменятся (они будут соответственно равны 01 ), за время т счетчик 38 импульсов заполняется до переполнения Импульс переполнения через время г поступает на первые входы группы 47 элементов И, на вторые входы группы 47 элементов И сигнал поступает с регистра 2 С выхода группы 47 элементов И сигналы поступают в блок 48 индикации, сигнализируя о наличии неисправности. При этом на инверсном выходе счетчика 39 импульсов появляется сигнал, эквивалентный логическому нулю, который, поступая на четвертый вход элемента И 34, закрывает его и прекращается подача импульсов на счетчик 39 импульсов

Неисправный объект 1-1 1-п контроля устанавливается по информации снимаемой с блока 48 индикации

В случае возникновения неисправности в самом устройстве контроля на выходах «1 и СС2 устанавливаются сигналы 00 или 11 . В этом случае на выходе элемента 45

сравнения появится сигнал, эквивалентный логической единице, который подается на блок 48 индикации, сигнализируя о неисправности в устройстве Одновременно этот сигнал запрещает прохождение импульсов

с генератора 23 импульсов в счетчик 39 импульсов.

Одиночные неисправности типа const О и const 1, выявляемые в устройстве, представлены в таблице, где 2° означает: 2

- номер элемента; 0 - неисправность типз const 0, а З1 : 3 - номер элемента, 1 - неисправность типа const 1.

Неисправности типа const 1 элементов 7-9, 16. 17, 26, 27, 37 и 38 иеравнозначности в процессе функционирования не обнаруживаются С целью обнаружения данного класса неисправностей введен дешифратор 13 и дополнительные разряды в регистре 2 После приведения регистра 2 в

исходное состояние на управляющий вход УСП подается код, обеспечивающий запись единицы в соответствующий разряд регистра 2 Это осуществляется с целью подачи на входы указанных элементов неравнозначности кодов 00 В этом случае не выходах а и (72 формируется код 00 .

Неисправности, необнаруживаег ые в процессе функционирования также представлены в таблице

Коэффициент глубины поиска дефекта

Кг п , характеризующий количество обнаруженных неисправностей, определяется по формуле

40

Кг п R

где F - количество неисправностей заданного класса итипа, обнаруживаемых в процессе диагностирования устройства,

R - общее количество неисправностей заданного класса и типа, в устройстве.

Для одиночных неисправностей типа cosnt 0 и cosn 1 для этого устройства

Кгп 0,93

Преимуществом разработанного устройства является повышение достоверности функционирования устройства. Устройство позволяет выявить все неисправное™, которые приводят к формированию на выходах а и аз. кода 00 или 11 Коэффициент глубины поиска дефекта для одиночного класса неисправностей типа const 0 и const 1 на выходе

логических элементов равен 0,93, Это позволяет сократить время обнаружения и локализации неисправности в устройстве. Локализация места неисправности в объектах контроля осуществляется с точностью до блока, выдающего сигнал на регистр. Формула изобретения Устройство для контроля состояния работоспособности центрального ядра вычислительного комплекса, содержащее регистр, с первого по третий элементы И, группу элементов И, элемент ЧЕ, блок индикации, блок управления, генератор импульсов, отличающееся тем, что, с целью повышения достоверности функционирова ния устройства, оно дополнительно содержит дешифратор, счетчик импульсов, с первого по девятый сумматоры, с четвертого по двадцать пятый элементы И, с первого по третий элементы ИЛИ, элемент сравнения, элемент задержки причем его выход соединен с сходами первого, третьего и пятого разрядов, входы этих разрядов регистра являются входами устройства для подключения к выходам соответствующих объектов контроля, инверсные выходы пер вого, третьего и пятого разрядов регистра подключены к первым входам соответственно первого, второго и третьего элементов И, вторые входы которых соединены с инверсными выходами соответственно второго, четвертого и шестого разрядов регистра, выходы первого, второго и третьего элементов И соединены соответственно с первыми входами первого, второго и третьего сумматоров, вторые входы которых соединены соответственно с прямыми выходами первою, третьего и пятого разрядов регистра, выходы с первого по третий сумматоров соединены соответственно с первым, вторым и третьим входами шестого элемента И, выход которого соединен с первыми входами двадцать четвертого и двадцать пятого элементов И, выходы которых подключены к первому и второму информационным выходам устройства и первому и второму входам элемента сравнения, выход которого подключен к первому входу блока индикации и через элемент НЕ к первому входу девятнадцатого элемента И, второй вход которого соединен с третьим выходом блока управления, а третий вход соединен с выходом генератора импульсов, четвертый вход соединен с инверсным выходом переполнения счетчика импульсов, выход девятнадцатого элемента И соединен со счетным входом счетчика импульсов, вход сброса которого подключен к выходу двадцать четвертого элемента И, прямой выход переполнения счетчика импульсов соединен с первыми входами элементов И группы, вторые входы которых соединены соот- ветственно с инверсными выходами первого, третьего и пятого разрядов регистра, выходы элементов И группы соединены с группой входов блока индикации, первый выход блока управления подключен к первому входу третьего элемента ИЛИ и первому входу девятого сумматора, втооой выход

0 блока управления соединен с первым входом двадцатого элемента И и первым входом восемнадцатого элемента И, второй вход которого и второй вход семнадцатого элемента И соединены с соответствующими

5 инверсными управляющими выходами регистра, выход восемнадцатого элемента И соединен с вторым входом девятого сумматора, выход которого подключен к первому входу двадцать первого элемента И, второй

0 вход которого соединен с выходом восьмого сумматора, выход двадцать первого элемента И соединен с первыми входами двадцать второго и двадцать третье о элементов И, второй вход двадцать второю элемента И

5 подключен к выходу третьего элемента ИЛИ, а выход - к второму входу двадцать четвертого элемента И, второй вход двадцать третьего элемента И подключен к выходу двадцатого элемента И а выход - к

0 второму входу двадцать пятою элемента И, выход двадцать четвертого элемента И соединен с входом элемента задержки, прямой выход первого разряда регистра подключен к первым входам четвертого сумматора и

5 седьмого элемента И, инверсный выход первого разряда регистра соединен с первыми входами первого элемента ИЛИ и четвертого элемента И, прямой выход третьего разряда регистра подключен к второму входу

0 седьмого элемента И и первому входу пятого сумматора а инверсный выход - к второму входу первого элемента ИЛИ и первому входу пятого элемента И, соответствующие управляющие инверсные выходы регистра

5 соединены с вторыми входами четвертого, пятого, одиннадцатого и двенадцатого элементов Ifij выходы которых соединены соответственно с вторыми входами четвертого, пятого, шестого и седьмого сумматоров, вы0 ходы четвертого и пятого сумматоров подключены к первому и второму входам десятого элемента И, выходы шестого и седьмого сумматоров - к первому и второму входам шестнадцатого эпемента И, выход

5 которого соединен с первыми входами четырнадцатого и пятнадцатого элементов И, выход десятого элемента И соединен с первыми входами восьмого и девятого элементов И, второй вход восьмого элемента I/I подключен к ЕЗМХОДУ седьмого элемента И,

второй вход девятого элемента И подключен к выходу первого элемента ИЛИ, выход восьмого элемента И соединен с первыми входами тринадцатого элемента И и шестого сумматора, выход девятого элемента И соединен с первыми входами одиннадцатого элемента И и второго элемента ИЛИ, второй вход которого и первый вход двенадцатого элемента И подключены к инверсному выходу пятого разряда регистра, прямой выход которого соединен с вторым входом тринадцатого элемента И и первым входом седьмого сумматора, выход тринадцатого элемента И подключен к второму входу четырнадцатого элемента И, выход

0

5

второго элемента ИЛИ подключен к второму входу пятнадцатого элемента И, выход которого соединен с первым входом семнадцатого и вторым входом двадцатого элементов И, выход четырнадцатого элемента И подключен к второму входу третьего элемента ИЛИ и первому входу восьмого сумматора, второй вход которого соединен с выходом семнадцатого элемента И, управляющие входы устройства соединены с входами дешифратора, выходы которого соединены с входами разрядов регистра, обеспечивающих выдачу управляющих воздействий, входы этих разрядов соединены с входом сброса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля вычислительных машин | 1983 |

|

SU1134943A1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Устройство для сложения 2 @ чисел | 1985 |

|

SU1307456A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сортировки цифровых сигналов | 1990 |

|

SU1805464A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2018 |

|

RU2706198C1 |

Изобретение относится к вычислительной технике и может быть использовано для определения технического состояния блоков вычислительной комплекса, который через промежутки времени выдает сигнал, свидетельствующий о работоспособности Целью изобретения является повышение достоверности функционирования устройства. Изобретение основано на теории парафазной логики. В процессе функционирования выявляются все неисправности, которые формируют на выходах «1 и О2 код 00 или 11 . Устройство содержит регистр, элемент задержки, 25 элементов И, три элемента ИЛИ девять сумматоров, элемент НЕ, дешифратор, блок управления, счетчик импульсов, элемент сравнения 2 ил. сл С

Оtf-н. аружи одиночные х.Јис.лра/но- 3сти- Г

6 ; 0; ;60;d ; ff ;rt W ;

// ;// # ; # # ;# ;

/6°; /6 / /7 J &

20ff;20 ;Ј/ ;& M ;M+M wt S5e;S5 ;260;46 ;2 °;tf ;aff & ;W ;M M ;M J3°;M -f 330;М ;35°;М ; А6°;36 ;а ; $в°1 ±0°; 4-0 ; Wa;W;

М°; -W; К°; Ы ; М°; М 5°; К, 46°; 46 ; ; ,

/J : 39

.0уж ttЈ zew6L&

OCrttHOVKAtl 4Јit&ns CЈ&коетъ.

to

-

9ие.З

Ј8

| Устройство для обнаружения ошибок в дискретной последовательности | 1988 |

|

SU1589281A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-23—Публикация

1990-08-09—Подача