pa, выходы пятого, третьего, четвертого, второго и первого элементов эквивалентности соединены с входами следующих в порядке возрастания номеров разрядов дешифратора,выходы деши ратора: нулевой, двенадцатый, двадцать второй, тридцать третий соединены как с вторыми входами четвертого, третьего, второго и первого элементов И соответственно, так и с входами первого элемента ИЛИ, выхо: ды дешифратора: седьмой, четвертый,; второй, первый соединены с входами второго элемента ИЛИ, выходы дешифратора: двадцать пятый, шестнадцатый, восьмой, первьй соединены с входами третьего элемента ИЛИ, выходы дешифратора: сорок второй, .тридцать второй, восьмой, второй соеди,нены с входами четвертого элемента ИЛИ, выходы дешифратора: пятьдесят второй, тридцать второй, шестнадцатый, четвертый соединены с входами пятого элемента ИЛИ, выход дешифратора шестьдесят третий соединен с вторым входом прерывания ЭВМ, остальные выходы дешифратора соединены с входами одиннадцатого элемента ИЛИ входы шестого элемента ИЛИ соединены с выходами второго, третьего, четвертого элементов И, а также с выходом третьего элемента ИЛИ, входы седьмого элемента ИЛИ соединены с выходами третьего, четвертого элементов И и выходом четвертого элемента ИЛИ, входы восьмого элемента ИЛИ соединены с выходами второго, четвертого элементов И и пятого элемента ИЛИ, входы десятого элемента ИЛИ соединены с выходами третьего, четвертого, пятого элементов ИЛИ, выход второго элемента ИЛИ соединен с вторым входом девятого элемента ИЛИ, первый вход которого сое|динен с выходом пятого элемента И, а второй вход пятого элемента И сое.динен с выходомдесятого элемента ИЛИ шестьдесят третий выход дешифратора, вход первого элементаИ и выходы шестого седьмого, восьмого, девятого, одиннадцатого элементов ИЛИ соединены с выходными шинами устройств а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического контроля электронных систем | 1981 |

|

SU980027A1 |

| Устройство автоматизированного контроля электронных систем | 1982 |

|

SU1061075A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения канала передачи данных с магистралью | 1986 |

|

SU1444787A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для регенерации информации в динамической памяти | 1983 |

|

SU1193729A1 |

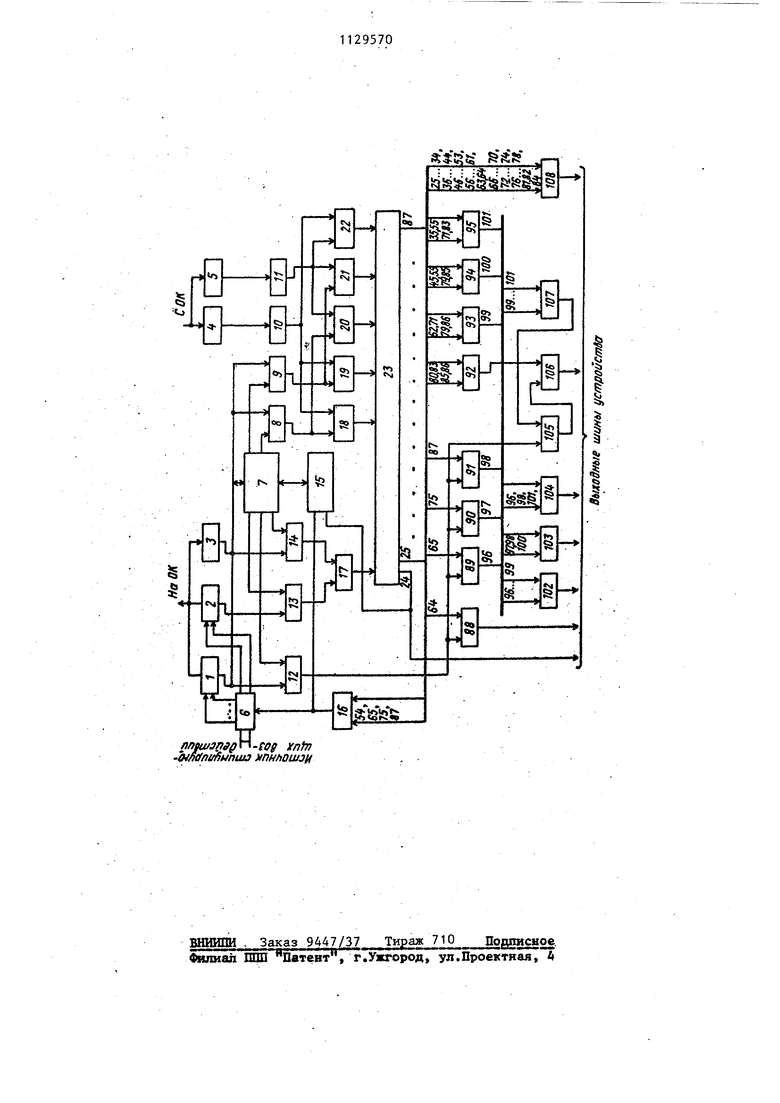

УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТРОЛЯ ЭЛЕКТРОННЫХ СИСТЕМ, содержащее ЭВМ, соединенную через контроллер с управляющим входом первого коммутатора, выходы которого соединены с клеммами для подключения входов объекта контроля и с входами первого шифратора, выход которого соединен с магистральными шинами контроллера,второй и третий шифраторы, входы которых соединены между собой и с клеммами для подключения выходов объекта контроля, . а выходы соединены соответственно с входами пятого и шестого регистров памяти, первьй, второй, третий и четвертьй регистры памяти соединены входами с магистральными и соответствующими адресными шинами контроллера, выходы первого и второго регистров памяти соединены с соответствующими входами первого элемента эквивалентности, выходы третьего и пятого регистров памяти соединены с соответствующими входами второго элемента эквивалентности, выходы четвертого и пятого регистров памяти соединены с соответствующими входами третьего элемента эквивалентности, выходы третьего и шестого регистров памяти соединены с соответствующими .входами четвертого элемента, эквивалентности, выходы четвертого и шестого регистров памяти соединены с соответствующими входами пятого элемента эквивалентности, выходы первого, второго, третьего, четвертого и пятого элементов эквивалентности соединены соответственно с пятью входами дешифратора, одиннадцать логических элементов ИЛИ, отличающееся тем, что, с целью повышения достоверности, в него введены второй коммутатор, переключатель, D-триггер, щестой элемент эквива-; лентности, пять логических элеменi тов И, при этом выходы второго ком(Л мутатора .соединены с соответствующими выходами первого коммутатора, управляющие входы второго коммутатора соединены с магистральными шинами контроллера, а входы второго коммутатора соединены с вторыми выходами переключателя, входы которого соединены с клеммами для подключения источника стимулирующих воздействий, N5 СО первые - выходы переключателя соединены с входами первого коммутатора, :л управляющий вход переключателя динен с выходом первого элемента ИЛИ, о которьш также соединен с hepBbw входом прерывания ЭВМ, D -вход Л -триггера соединен с магистральными шинами контроллера, С -вход Б -триг гера соединен с адресной шиной контроллера, а выход - с первыми входами ; всех логических элементов И, входы шестого элемента эквивалентности соединены с выходами пятого и шестого регистров памяти, а его выход с входом младшего разряда дешифрато

Изобретение относится к автоматичёскому контролю и может быть не- ; пользовано в автоматизированных системах управления и контроля электронных систем различного назначения. -5

. Известна автоматическая система контроля, содержащая ЭВМ, соединен- . ная через блоки, сопряженные с источниками стимулирующих воздействий, с измерителями параметров объектов -10 контроля, с коммутаторами, выходы которых соединены с выходными клеммами системы для подключения объекта контроля (ОК) lj

Недостатком системы является боль-|5 шое время контроля ОК из-за значитель ных .объемов логической обработки в ЭВМ и отсутствия средств дпя повышения достоверности.контроля.

Наиболее близким к предлагаемому .20 является устройство автоматического контроля электронных систем, содержащее ЭВМ, соединенную через контроллер с управляющим входом коммутатора, входы которого соединены с источником стимулирующих сигналов,а выходы - свходами объекта контроля, входы первого шифратора соединены с выходами коммутатора, а выход - с магистральными шинами контроллера, входы второго и третьего шифраторов соединены между собой и с выходами объекта контроля, а выходы соединены соответственно с входами пятого и шестого регистров памяти, входы первого, второго, третьего и четвертого регистров памяти соединены с магистральными и соответствующими адресными щинами контроллера, выходы первого и второго регистров памяти .соединены с соответствующими входами первого элемента эквивалентности, выходы третьего и пятого регистров памяти соединены с соответствующими входами второго элемента эквивалентности, выходы четвертого и пятого регистров памяти сдединены с соответствующими входами третьего элемента эквивалентности,-выходы третьего и шестого регистра памяти соединены с соответствующими входами четвертого элемента эквивалентности выходы четвертого и шестого регистров памяти соединены с соответствую щими входами, пятого элемента эквивалентности, выходы первого, второго третьего, четвертого и пятого элементов эквивалентности соединены COO ветственно с пятью входами дешифратора, начиная с младшего разряда,вы ходы дешифратора с тридцать первого по двадцать восьмой, с двадцать седьмого по двадцать четвертый, с двадцать третьего по двадцатый, с девятнадцатого до шестнадцатый соединены с четырьмя входами первого, второго, третьего и четвертого элементов ИЛИ соответственно, выходы де шифратора с первого по четвертый, седьмой, восьмой, с одиннадцатого по четырнадцатый и выходы первого, второго и третьего элементов ИЛИ сое динены с входами пятого элемента ИПИ а его выход соединен с входом прерывания ЭВМ, выходы дешифратора нулевой, пятый, шестой, девятый, десятый пятнадцатый соединены с входами шестого элемента ИЛИ, выходы дешифратора с первого по пятнадцатый и выходы второго, третьего и четвер того элементов ИЛИ соединены с вхбдами седьмого элемента ИЛИ, выходы дешифратора с первого по третий, сед мой, одиннадцатый соединены с входа ми восьмого элемента ИЛИ, выходы дешифратора четвертый, восьмой, с .двенадцатого по четьфнадцатьй соединены с входами девятого элемента ИЛИ, выходы дешифратора первый, четвертьй, пятый и вькод третьего элемента ИЛИ соединены с входами десятого элемента ИЛИ, выходы дешифратора нулевой, шестой, девятый пятнадцатый соединены с входами один надцатого элемента ИЛИ, выходы дешифратора второй, восьмой, десятый и выход второго элемента ИЛИ соединены с входами двенадцатогоэлемента ИЛИ, выходы дешифратора нулевой, пятый, шестой, девятый, пятнадцатый соединены с входами тринадцатого эле мента ИЛИ, выходы дешифратора с пято го по седьмой, с девятого по одиннад цатьм, с тринадцатого по пятнадцатьй соединены с входами четырнадцатого элемента ИЛИ, выходы логических элементов ИЛИ первого, четвертого, с пятого по четырнадцатый и нулевой выход дешифратора подключены к выходным шинам устройства pj. Однако указанное устройство может принимать достоверное решение о состоянии технических средств как самого. устройства, так и ОК при возникновег ; НИИ неисправности только в одном месте устройства. Цель изобретения - повьш1ение достоверности контроля. , Поставленная цель достигается тем, что в устройство автоматического контроля электронных систем, содержащее ЭВМ, соединенную через контроллер с управляющим входом первого коммутатора, выходы которого соединены с.клеммами для подключения входов объекта контроля и с входами шифратора, выход которого соединен с магистральными шинами контроллера, второй и третий шифраторы, входы которых соединены между собой и с клеммами для подключения выходов объетста контроля, а выходы соединены соответственно с входами пятого и шестого регистров памяти, первый, второй, третий и четвертый регистры памяти соединены входами с магистральными и соответствующими адресными шинами контроллера, выходы первого и второго регист- . ров памяти соединены с соответствующими входами первого элемента эквивалентности, выходы третьего и пятого регистров памяти соединены с соответствующими входами второго элемента эквивалентности,, выходы четвертого и пятого регистров памяти соединены с соответствующими входами третьего элемента эквивалентности, выходы третьего и шестого регистров памяти соединены С соответствующими входами четвертого элемента эквивалентности, выходы четвертого и шестого регистров памяти соединены с соответствующими входают пятого элемента эквивалентности, выходы первого, второго, третьего, четвертого и пятого элементов эквивалентности соединены соответственно с пятью входами дешифратора, одиннадцать логических элементов ИЛИ, введены второй коммутатор, переключатель, р -триггер, шестой элемент эквивален. ности, пять логических элементов И, при этом выходы второго коммутатора соединены с соответствунлцими вы.ходами первого коммутатора, а управляющие входы второго коммутатора соединены с магистральными шинами контроллера, а входы второго ком мутатора соединены с вторыми выхода .ми переключателя, входы которого соединены с клеммами для подключения источника стимулирующих воздействий, первые выходы переключателя соединены с входами первого коммута Тора, управляющий вход переключателя соединен с выходом первого элемента ИЛИ, который также соединенс первым входом прерывания ЭВМ, В -вход D -триггера соединен с магистральными шинами контроллера, С-вход D -триггера соединен с адресной шиной контроллера, а выход .с первыми входами всех логических элементов И, входы шестого элемента .эквивалентности соединены с вых дами пятого и шестого регистров Памяти, его выход - с входом младшего разряда дешифратора, а вь1ходы пятого, третьего, четвертого, второго и первого элементов эквивалент ности соединены с входами Следующих в порядке возрастания номера разрядов дешифратора,выходы дешифратора: нулевой, двенадцатый, двадцать второй, тридцать третий соединены как с вторыми входами четвертого, треть го, второго и первого элементов И соответственно, так и с входами первого элемента ИЛИ, выходы дешифр тора: седьмой, четвертьй, второй, первый соединены с входами второго элемента ИЛИ, выходы дешифратора: двадцать пятый, шестнадцатый, восьмой, первый соединены с входами тре тьего элемента ИЛИ, выходы дешифратора: сорок второй, тридцать второй восьмой, второй соединены с входа. ми четвертого элемента ИЛИ, выходы дешифратора: пятьдесят второй, трид цать второй, шестнадцатый, четвертый соединены с входами пятого элемента ШШ, выход дешифратора шеСть.десят третий соединен с вторым вход прерывания ЭВМ, остальные выходы де шифратора.соединены с входами один;надцатого элемента ИЛИ, входы .шестого элемента ИЛИ соединены с выходами второго, третьего, чет.вертого элементов И, а также с вьссо дом третьего элемента ШШ, входы седьмого элемента ИЛИ соединены с в ходами третьего, четвертого элементов И и выходом четвертого элемента ИЛИ, входы восьмого элемента ИЛИ соединены с выходами второго, четвертого элементов И и пятого элемента ИЛИ, входы десятого элемента ИЛИ соединены с выходами третьего, четвертого, пятого элементов ИЖ выход второго элемецта ИЛИ соединен с вторым входом девятого элемента ШШ, первый вход которого соединен с выходом пятого элемента И, а второй вход пятого, элемента И соединен с выходом десятого элемента ИЛИ, шестьдесят третий выход дешифратора, выход первого элемента И и выходы шестого, седьмого, восьмого, девятого и одиннадцатого элементов ИЛИ соединены с выходными шинами устройства. На,чертеже представлена схема устройства. Устройство содержит коммутаторы 1 и 2, шифраторы 3-5, .переключатель 6, контроллер 7,, третий регистр 8 памяти эталонной реакции ОК . на код воздействия, вьздаваемый ЭВМ, четвертьй регистр 9 памяти эталонной реакции ОК на воздействие, код которого соответствует зарегистрированному шифратором 3, пятьш 10 и .шее- . той 11 регистры памяти реакций ОК, В-тригг ер 12 памяти факта переключения управления ОК с одного коммутатора на другой,сообщаемый ЭВМ, регистр 13 памяти кодов воздействия, вьщаваемого от ЭВМ-, второй регистр 14 памяти контрольного кода воздейств й я, вьщанного на ОК, ЭВМ 15, логический элемент 16 ШШ, первый 17 второй )8, третий 19, четвертый 20, : пятый 21, шестой 22 логические элементы эквивалентности, дешифратор 23 с выходными шинами 24-87, реализую- ; щими выходы дешифратора с шестьдесят третьего по нулевой в, по;рядк е убь1вания номера выхода, логический элемент 88 И логические элемен-; ™ 89-91 И, логический элемент 52 ИЛИ, логические элементы 93-95 где 96-98 - выходы элементов 89-91 соответственно, а 99-101 - выходы элементов 93-95 ИЛИ соответственно, логические элементы 102-104 ШШ, логический элемент 105 И, логические элементы 106-108 ШШ, При этом шифраторы 3-5 фиксируют на своих выходнькшйнйх :коД номера входной шйны Ни котор.Ьй появился 7 или исчез сигнал или на которой изменилась величина сигнала. Входами устройства являются соединенные между собой входы шифраторов 4 и 5. Выходами устройства являются выходы логических элементов 88 и 102, 10,3, -104, 106 и 108 ИЛИ, выходная шина 24 дешифратора 23, которые используются для индикации или управления другими средствами, а также выходы коммутаторов 1 и 2. Управляющие входы коммутаторов 1 и 2 соединены с магистральными шинами контроллера 7, с которыми соединены также выход шифратора 3, вход регистров 8,9,13 и 14 памяти и D-вход триггера 12. Входы коммутаторов соединены с первыми и вторыми выходами переключателя 6, со входом которого соединен источник стимулирующих воздействий, а управляющий вход переключателя соединен с выходом элемента 16 ИЛ и первым входом прерывания ЭВМ 15. Выходы шифраторов 4 и 5 соединены со входами регистров 10 и 11 памяти соответственно. . Адресные (стробируемые) входы регистров 8,9,13 и14 памяти и триггера 12 соединены с соответствующими адресными шинами контроллера 7. Информационные выходы регистров 13 и 14 памяти соединены поразрядно со входами элемента 17 эквивалентнос ти. Информационные выходы регистров 8 и 9 памяти соединены поразрядно с объединенными входами элементов 18,2 и .19,21 эквивалентности соответствен но.. Выходы регистра 10 памяти соединены поразрядно .со вторыми входами элементов 18,19 и 22 эквивалентности Выходы регистра 11 памяти соединены поразрядно со вторыми входами элемен тов 20.и 21 эквивалентности и первым входом элемента 22 эквивалентности. Прямой выход триггера 12 памяти соединен с первыми входами логических элементов 88-91 и 105 И. Выходы элементов 22, 21, 19, 20, 18 и 17 эквивалентности соответственно соед нены со входами дешифратора 23, нач

ная с младшего. . .. . ... .,

:. .; .. , . С .выходовпервого .регистра. 13 и Выходная шина-.24 дешифратора: 3.. .. втррого регистра . 14 кодовые сообщесоединена со .вгорымвхрДом.й эёрывани1 - «йя i йортуг1ают на входы первбгоэлемен. ЭВМ 15. Выхрдныё;.шинь1.5,65,- 75:и:87 (/.эквивалентности. дешифрат6р.а23 Соединены со.вторьп , . .При совпадении кодов на входах, входами элементов 88-91 И соответ- .элемента 17 на его В14ходе появляется 70 ственно, а также со входами элемента 16 ИЛИ. От дешифратора 23 выходные шины 80,83, 85 и 86, выходные шины 62 71. 79 и 86,выходные шины 45, 55, 79 и 85 и выходные шины 35, 55, 71 и 83 соединены с входами элементов . 92-95 ИЛИ соответственно.: Выходные шины 25-34, 36-44, 46-53i 56-61, 63, 64, 66-70, 72-74, 76-78, 81,82 и 84 дешифратора 23 соединены со входами элемента 108 ИЛИ. ; Входы элемента 102 ИЛИ соединены ; с выходами элементов 89-91 И, а также с выходом элемента 93 ИЛИ. Входы элемента 103 .ИЛИ соединены с выходами элементов 90 и 91 И, а также с выходом элемента 94 ИЛИ. Входы элемента 104 ИЛИ соединены с выходамиэлементов 89 и 91 И, а также с выходом элемента 95 ИЛИ. Входы элемента ; . : 107 ИЛИ соединены с выходами элементов 93-95 ИЛИ. Выход элемента 107 ИЛИ соединен со вторым входом элемента 105 И, выход ксггорого соединей со входом элемента 106 ИЛИ. Второй вход элемента соединен с выходом элемента 92 ИДИ. Устройство работает следующим образом. ЭВМ 15 содержит в своей памяти последовательность вьщачи воздействий на ОК и его логическую модель, которая обеспечивает возможность формирования эталонной реакции ОК при вы-. даче на него любого воздействия из именяцего перечня. ЭВМ 15 через контроллер 7 вьздаст коммутатору 1 или 2 код стимулирующего воздействия, который также вьщается в первьй , регистр 13.j Источник стимулирующих воздействий посредством переключателя 6 подклю- ;. чен только к коммутатору 2. Стимулирующее воздействие с выхода этого коммутатора поступает на ОК Г и на вход шифратора 3, с выхода которого контрольный код, соответствующий зарегистрированному стимулирующему воздействию, поступает на вход второго регистра 14 и через контроллер 7 на ЭВМ 15. сигнал Логической единицы, что свидетельствует о соответствии выданног на ОК воздействия, заданному от ЭВМ 15. После выдачи воздействия на ОК ЭВМ 15 формирует два кодовых сообщения. Первое сообщение соответствует эталонному состоянию ОК при условиивьщачи на него запланированного воздействия. Второе сообщение соответствует эталонному состоянию ОК при условии вьщачи на него воздействия,, соответствующего коду, зарегистрированному шифратором 3. Сообщения вьщаются через контроллер 7 на третий 8 и четвертый 9 регистры соответственно. Реакции объекта контроля на вьщан ное воздействие воспринимаются двумя пшфраторами 4 и 5. С их выходов кодо вые сообщения поступают на выходы пя того 10 и шестого 11 регистров. С вы хода третьего регистра 8 код поступает на входы второго элемента 18 и четвертого элемента 20 эквивалентно ти. С выхода четвертого регистра 9 код поступает на входы третьего эле мента 19 и пятого элемента 21 эквивалентности. На вторые входы элементов 18,19 и 22 эквивалентности поступает код регистра 10. Код от шестого регистр 11 поступает на вторые входы четвертого 20 ипятого 21 элементов эк вивалентности и первый вход шестого .элемента 22 эквивалентности. Совпадение кодов на входах элементов 18 и 20 эквивалентности свидетельствует о том, что реакция ОК, принятая шифратором 4 и принятая шифратором 5, соответствует эталонному состоянию ОК при вьщаче запланированного воздействия. Совпадение кодов на входах третьего элемента 1 и пятого элемента 21 эквивалентност свидетельствуют о соответствии реак .ции ОК стимулирующему воздействию, зарегистрированному шифратором 3. Совпадение кодов на входах шестого элемента 22 эквивалентности свидетельствует об идентичности реакций зарегистрированных шифраторами 4 и 5. Комбинация состояний выходов лог ческих элементов 17-22 эквивалентно ти позволяет сделатьзаключение о состоянии Норма, Не норма каждо го элемента системы и ОК как в случае наличия неисправности в одном месте системы, так. и в двух - трех местах одновременно. Неисправности в двух местах могут быть скоррелированы (т.е. давать при сравнении кодов на регистрах положительньй результат, соответствующий исправным состояниям источников кодов сравнения) и нескоррелированы. Поскольку каждый элемент 17-22 эквивалентности имеет на выходе два логических состояния, то всего имеется 26 решений. Сигнал с выходов элементов эквивалентности поступает на входы да- шифратора 23, причем с элемента 22 эквивалентности - на вход младшего разряда дешифратора, а на входы с второго по шестой разряд включительно - с элементов 21, -19, 20,18 и 17 эквивалентности соответственно. Вы-ходные шины 25-53, 55-64, 66-74, 76-87 дешифратора 23 соединены с входами элементов 92-95 ИЛИ и эле- мента 108 ИЛИ по принципу аналогичности заключений о состоянии соот- , ветствующих элементов устройства азтоматического контроля и ОК. Появление логической единицы хотя бы на одном из выходов 99-101 соответственно .элементов 93-95 ИЛИ формирует на выходе элемента 107 ИЛИ ; сигнал, который подается на вход элемента 105 И.. л....« и. При наличии скоррелированных неисправностей логическая единица появляется на одной из выходных шин 54, 65 и 75 дешифратора 23, а при наличии неисправности в трех местах на выходной шине 87. Одновременно логическая единица поступает на второй вход соответствующего логического элемента 88-91 и на вход элемента 16 ИЛИ. С выхода элемента 16 ИЛИ сигнал подается на вход прерывания ЭВМ 15 и на вход переключателя 6, который отключает комМутатор 1 или 2 и подключает коммутатор 2 или 1 к источнику стимулирующих воздействий. После обра-ботки этого прерывания ЭВМ 15 повторяет выдачу воздействий на ОК, а также через контроллер 7 логической единицей на выходе триггера 12 зафиксирует факт переключения с одного коммутатора на другой. . Если отключенный коммутатор 1 или 2 исправен, то логическая едини ца на одном из выходов 54, 65, 75 и 87 дешифратора 23 при повторении воздействия возобновляется. В результате возобновления логической единицы на одном из выходов 54,65,73,87 дешифратора и появлении ее, на выходе триггера 12 появ ляется логическая единица на выходе соответствующего элемента 88-91 И. Если отключенньй коммутатор 1 или 2 неисправен, то логическая еди ница на выходах 54,65,75,87 дешифра тора 23 исчезает, но появляется на выходе элемента 105 И вследствие появления определенной комбинации сигналов на выходах элементов 17-22 эквивалентности, соединенных со вхо дами дешифратора 23 что вызывает появление логической единицы на выходе элемента 105 И. Выходы элемента 92 ИЛИ и элемента 105 И соединены со входами элемента 106 ИЛИ. а выходы элементов 89-91 И и элементов 93-101 ИЛИ соединены со входами элементов 102-104 И по принципу аналогичности заключений ,о состоянии соответствуклдих элемёнт устройства автоматического контро7012ля следующим образом: элемент 102 ИЛИ Шифратор 3 неисправен, элемент 103 ИЛИ - Шифратор 4 неисправен, элемент 104 ИЛИ - Шифратор 5 неисрг равен, элемент 106 ИЛИ - Отключенный коммутатор неисправен, элемент 108 ИЛИ - Элементы эквивалентности и регистры памяти неисправны, элемент 88 И - ОК неисправен, выход 24 дешифратора 23 - ОК и устройство норма. С выхода 24 дешифратора 23 сигнал подается на вход прерывания ЭВМ Т5.. При появлении на выходе 24 дешифратора 23 сигнала ОК и устройство норма ЭВМ 15 получает через систему прерьшания уведомление об успешном завершении контроля состояния ОК по данному (Стимулирующему, воздействию и формирует выдачу следующих воздействий. Таким образом, предлагаемое устройство, обеспечивая локализацию мест неисправности, позволяет в де-. сятки раз сократить время Восстановления устройства при эксплуатации по сравнению с прототипом за счет обнаружения неисправностей в двух и трех местах.

nnswsps r.tos xn -tNMffti Hnua )inMOWJtt

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЭПИСКОП | 1927 |

|

SU6000A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство автоматического контроля электронных систем | 1981 |

|

SU980027A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-12-15—Публикация

1982-08-23—Подача