Предлагаемое изобретение относится к области широкополосных систем радиосвязи (ШСС) и может быть использовано, в частности, в мобильных и стационарных станциях систем связи с шумоподобными сигналами (ШПС) для формирования опорного сигнала и корректировки его параметров (частоты и фазы) в системе автоподстройки частоты (АПЧ) и в системе фазовой автоподстройки частоты (ФАПЧ) вычислительными (программными) средствами.

Важным вопросом в процессе выполнения процедур поиска и синхронизации в широкополосных системах связи является выбор компромиссного способа реализации (исполнения) источников опорных сигналов на основе аппаратных или программных средств. В настоящее время приоритетным направлением является создание и расширение перечня универсальных средств обработки на основе программных принципов «умного» радио при одновременном сокращении доли узкоспециализированных аппаратных средств. Такой подход позволяет получить универсальные платформы, которые организуют обработку сигнала в соответствии с требуемыми алгоритмами в большей мере на основе перепрограммирования и обеспечивают уменьшение габаритов используемой аппаратуры и средств на ее разработку и производство.

Известны следующие основные методы генерации опорных сигналов в системах автоматического управления.

Традиционный (классический) метод формирования опорного сигнала в системах автоматического управления заключается в непосредственном использовании аппаратных средств, таких как управляемые генераторы тактовой частоты, генераторы гармонического сигнала, управляемые напряжением (ГУН), и др. [Шахгильдян В.В., Ляховкин А.А. Системы фазовой автоподстройки частоты / В.В. Шахгильдян, А.А. Ляховкин. - М.: «Связь», 1972. - 447 с., Первачев С.В. Радиоавтоматика / С.В. Первачев. - М.: - «Радио и связь», 1982. - 296 с., Журавлев В.И. Поиск и синхронизация в широкополосных системах / В.И. Журавлев. - М.: - «Радио и связь», 1986. - 240 с., Жодзишский М.И. Цифровые системы фазовой синхронизации / М.И. Жодзишский, Сила-Новицкий С.Ю., Прасолов В.А. и др., под ред. М.И. Жодзишского. - М.: «Сов.Радио», 1980. - 208 с. и др.].

Основными недостатками этого подхода являются достаточно ограниченная область управления параметрами и формой генерируемого сигнала, низкая скорость перестройки, временная и частотная нестабильность параметров, совокупность специфических особенностей применения.

В различных областях электроники и цифровой обработки сигналов широко используется другой подход генерации опорных сигналов методом прямого цифрового синтеза (Direct Digital Synthesizer - DDS) [Блог Чиповода www.chipovod.ru,, Ридико Леонид Иванович wubblick@yahoo.com и др.].

DDS генераторы позволяют формировать:

- сигналы с большим диапазоном перестройки частоты (от нуля до сотен МГц) и малым шагом перестройки (сотые доли герца);

- квадратурные сигналы и сигналы с произвольным сдвигом фазы;

- перестройку частоты выходных сигналов с большой скоростью переходных процессов;

- периодические сигналы произвольной формы.

Такие широкие возможности сделали привлекательными цифровые DDS синтезаторы сигналов для применения в самых различных приложениях, в том числе в системах автоматического управления. Для реализации генератора DDS можно использовать программируемую логику (ПЛИС, Field Programmable Gate Array (FPGA), например, типа Virtex-7) или микропроцессоры (например, 1892 ВМ3Т (Multicore), 1892 ВМ10Я (NVcom) и их перспективные версии).

На примере получения в цифровом виде гармонического синусоидального сигнала с заданными параметрами основной принцип DDS синтезатора сигналов заключается в следующем. Предварительно формируют дискретные значения для N точек синусоиды с равномерным временным шагом, равным периоду дискретизации Δ=1/fT0, где fT0 - опорная системная тактовая частота. Далее сформированные дискретные значения синусоиды размещают по адресам в ячейки памяти таблицы. Для генерации выходного сигнала из ячеек памяти таблицы в нужной последовательности считывают дискретные значения синусоиды с помощью счетчика адресов с заданной опорной тактовой частотой.

Такой метод работает качественно, если необходимая частота выходного сигнала меньше опорной тактовой частоты в N раз. Для генерации другой выходной частоты необходимо либо изменять шаг перебора адресов ячеек памяти таблицы, либо перестраивать опорную тактовую частоту и размерность таблицы, что технически выполнить довольно проблематично.

Известна полезная для упрощения реализации модификация процедуры генерации сигнала, которая предполагает следующие операции. Запись дискретных значений синусоиды в ячейки памяти таблицы и их считывание выполняют не через одинаковые промежутки времени, равные периоду дискретизации Δ=1/fT0, а через промежутки, соответствующие заданному значению изменения фазы выходного сигнала. Это позволяет за счет линейности фазы и периодичности выходного сигнала рационально реализовать данную процедуру формирования. В этом случае выходной сигнал можно восстановить, беря выборки из таблицы значений через промежутки, пропорциональные выходной частоте.

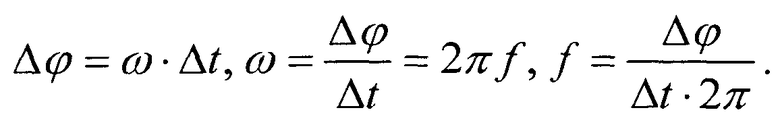

Аналитическое представление выходного синусоидального сигнала имеет вид x(t)=Asin(ωt+φ0), где ω - циклическая частота, φ0 - начальная фаза, А - амплитуда. Тогда величина циклической частоты задает скорость изменения полной фазы φ=φt+φ0, и имеют место следующие соотношения:  Таким образом, существует связь между выходной частотой f и фазой сигнала Δφ.

Таким образом, существует связь между выходной частотой f и фазой сигнала Δφ.

Основные недостатки данного метода следующие.

Невозможность независимой и качественной подстройки текущей частоты и фазы генерируемого опорного сигнала, так как минимальный шаг перестройки частоты непосредственно зависит от соотношения выходной и опорной тактовой частот. При приближении частоты выходного сигнала к опорной тактовой частоте шаг перестройки частоты и начальной фазы становится недопустимо грубым. Получение меньшего шага перестройки частоты и фазы за счет изменения опорной тактовой частоты - трудно решаемая задача.

Наиболее близкими по технической сущности к предлагаемому способу формирования (генерирования) и корректировки параметров опорного сигнала в системе автоподстройки частоты (АПЧ) и в системе фазовой автоподстройки частоты (ФАПЧ) и устройству, его реализующему, являются способ и устройство, описанные в [Mohamed К. Nesami, Ph.D., K14CUA. RF Architektures and Digital Signal Processing Aspects of Digital Wireless Transceivers. © 2003. - 511 с., Mohamed_nezami@msn.com], которые приняты за прототип способа и устройства предлагаемого технического решения.

Способ генерации опорного сигнала и корректировки (подстройки) его параметров, предложенный в прототипе, заключается в том, что:

- Непрерывный входной широкополосный сигнал на радиочастоте предварительно преобразуют в квадратурный комплексный дискретный широкополосный сигнал на промежуточной частоте, выполняют процедуру синхронизации по времени и выделяют в результате фазовой демодуляции ШПС дискретный гармонический комплексный сигнал на промежуточной частоте.

- Путем сравнения параметров комплексного дискретного гармонического сигнала на промежуточной частоте с параметрами сформированного опорного дискретного сигнала вырабатывают оценку относительной расстройки (ошибки) фазы и частоты опорного сигнала.

- Выполняют корректировку соответствующих параметров опорного сигнала на величину полученных оценок расстройки (ошибки) фазы и частоты.

- Далее на каждом последующем шаге анализа выполняют процедуру сравнения параметров текущего входного комплексного дискретного гармонического сигнала на промежуточной частоте и текущего дискретного опорного сигнала, вырабатывают оценку относительной расстройки (ошибки) фазы и частоты и осуществляют корректировку текущих значений соответствующих параметров текущего опорного сигнала.

Таким образом реализуют итерационную процедуру генерации опорного сигнала и корректировки (подстройки) его текущих параметров.

Описание способа-прототипа генерации опорного сигнала и корректировки (подстройки) его параметров в полной мере соответствует формальной математической модели, приведенной, например, на стр.94-98 в [Mohamed К. Nesami, Ph.D., K14CUA. RF Architektures and Digital Signal Processing Aspects of Digital Wireless Transceivers. © 2003.-511 с., Mohamed_nezami@msn.com].

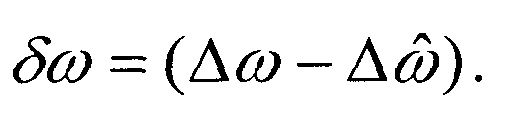

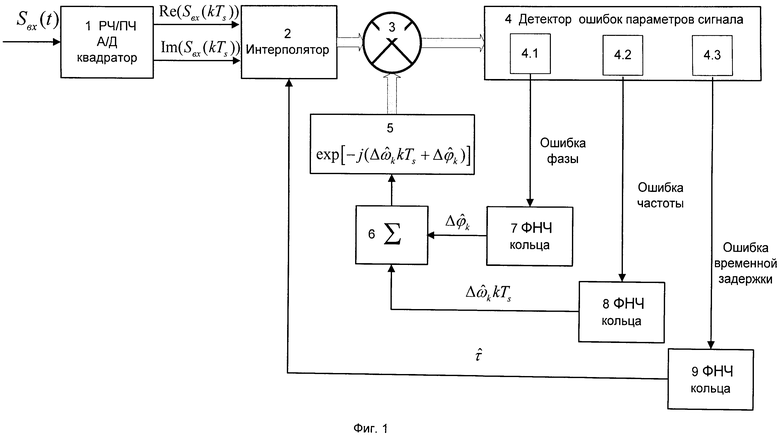

Для реализации способа-прототипа может быть использовано устройство-прототип, общая структурная схема которого в части АПЧ (AFC - automatic frequency control) и ФАПЧ (phase lock loop - PLL) представлена на фиг.1, где обозначено:

1 - стандартный блок следящего приемника ШПС;

2 - интерполятор (коррелятор);

3 - комплексный перемножитель;

4 - детектор ошибок параметров сигнала;

4.1 - управляемый детектор фазовой ошибки;

4.2 - управляемый детектор частотной ошибки;

4.3 - детектор временной ошибки;

5 - численно управляемый осциллятор (вычислитель);

6 - сумматор фазовой и частотной ошибок;

7 - фильтр низких частот (ФНЧ) кольца фазовой ошибки;

8 - ФНЧ кольца частотной ошибки;

9 - ФНЧ кольца ошибки временной задержки.

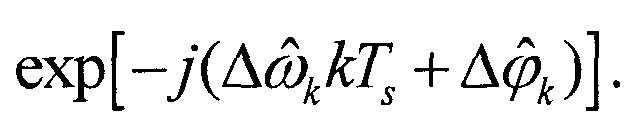

Для наглядности структурную схему фиг.1 условно разделим на две обобщенные функциональные части: стандартный блок следящего приемника ШПС 1 и схему процедур временной, частотной и фазовой синхронизации ШПС. Стандартный блок следящего приемника ШПС 1 включает схему преобразования несущей радиочастоты входного широкополосного сигнала на промежуточную частоту (РЧ/ПЧ) и схемы преобразования сигнала из аналогового вида в квадратурное дискретное представление (А/Д, квадратор). Схема процедур временной, частотной и фазовой синхронизации ШПС состоит из интерполятора (коррелятора) 2, комплексного перемножителя 3, детектора ошибок параметров сигнала 4, фильтра низких частот (ФНЧ) кольца фазовой ошибки 7, ФНЧ кольца частотной ошибки 8, ФНЧ кольца ошибки временной задержки 9, сумматора фазовой и частотной ошибок 6 и численно управляемого осциллятора (вычислителя-генератора) 5. В качестве численно управляемого генератора гармонического сигнала (numerically controlled oscillator - NCO), формирующего в прототипе опорный сигнал, используют комплексный вычислитель  Причем детектор ошибок параметров сигнала 4 состоит из детекторов фазовой 4.1, частотной 4.2 и временной 4.3 ошибки.

Причем детектор ошибок параметров сигнала 4 состоит из детекторов фазовой 4.1, частотной 4.2 и временной 4.3 ошибки.

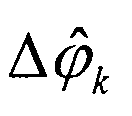

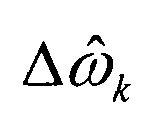

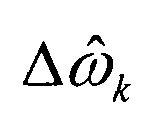

На структурной схеме фиг.1 используются следующие обозначения: Sвх(t) - входной радиочастотный аналоговый ШПС, Re(Sвх(kTs)) и Im(Sвх(kTs)) - соответственно синфазная и квадратурная составляющие дискретного ШПС на промежуточной частоте,  - оценка текущей фазовой ошибки (расстройки),

- оценка текущей фазовой ошибки (расстройки),  - оценка текущей частотной ошибки (расстройки),

- оценка текущей частотной ошибки (расстройки),  - оценка ошибки временной задержки, k - номер шага дискретизации, Ts - временной интервал дискретизации.

- оценка ошибки временной задержки, k - номер шага дискретизации, Ts - временной интервал дискретизации.

Вход стандартного блока следящего приемника ШПС 1 является первым входом устройства-прототипа входного аналогового широкополосного радиосигнала. Первый и второй квадратурные выходы блока 1 соединены с соответствующими первым и вторым квадратурными входами широкополосного дискретного сигнала на промежуточной частоте интерполятора (коррелятора) 2, на третий вход которого через ФНЧ кольца ошибки временной задержки 9 с третьего выхода детектора ошибок параметров сигнала 4 поступает широкополосный сигнал копии на промежуточной частоте с оцененной временной задержкой  . Выход интерполятора 2 комплексного гармонического сигнала на промежуточной частоте соединен с первым квадратурным входом комплексного перемножителя 3, второй квадратурный вход которого соединен с квадратурным выходом численно управляемого осциллятора (вычислителя) (NCO) 5, вход которого через сумматор 6 фазовой и частотной ошибок и через ФНЧ кольца фазовой ошибки 7 и ФНЧ кольца частотной ошибки 8 соединен с первым и вторым выходами сигналов фазовой и частотной ошибок детектора ошибок параметров сигнала 4. Выход комплексного перемножителя 3 соединен с квадратурным входом детектора ошибок параметров сигнала 4.

. Выход интерполятора 2 комплексного гармонического сигнала на промежуточной частоте соединен с первым квадратурным входом комплексного перемножителя 3, второй квадратурный вход которого соединен с квадратурным выходом численно управляемого осциллятора (вычислителя) (NCO) 5, вход которого через сумматор 6 фазовой и частотной ошибок и через ФНЧ кольца фазовой ошибки 7 и ФНЧ кольца частотной ошибки 8 соединен с первым и вторым выходами сигналов фазовой и частотной ошибок детектора ошибок параметров сигнала 4. Выход комплексного перемножителя 3 соединен с квадратурным входом детектора ошибок параметров сигнала 4.

Работает устройство-прототип следующим образом.

На первый вход стандартного блока следящего приемника ШПС 1 поступает аналоговый широкополосный сигнал Sвх(t). В данном блоке несущую частоту входного широкополосного радиосигнала переносят на промежуточную частоту, выполняют дискретизацию сигнала и формируют квадратурные составляющие дискретного входного широкополосного сигнала. Далее с учетом оценки сформированной ошибки временной задержки  с третьего выхода детектора ошибок параметров сигнала 4 в интерполяторе (корреляторе) 2 реализуют процедуру временной синхронизации и снятие широкополосной модуляции (как правило, фазовой манипуляции). В результате формируют комплексный дискретный гармонический сигнал на промежуточной частоте. По результатам сравнения параметров комплексного дискретного гармонического сигнала на промежуточной частоте с параметрами сформированного опорного сигнала в цепях:

с третьего выхода детектора ошибок параметров сигнала 4 в интерполяторе (корреляторе) 2 реализуют процедуру временной синхронизации и снятие широкополосной модуляции (как правило, фазовой манипуляции). В результате формируют комплексный дискретный гармонический сигнал на промежуточной частоте. По результатам сравнения параметров комплексного дискретного гармонического сигнала на промежуточной частоте с параметрами сформированного опорного сигнала в цепях:

1. комплексный перемножитель 3, детектор ошибок параметров 4, ФНЧ кольца фазовой ошибки 7,

2. комплексный перемножитель 3, детектор ошибок параметров 4, ФНЧ кольца частотной ошибки 8,

в сумматоре фазовой и частотной ошибок 6 по сигналу оценки ошибки фазы  и сигналу оценки ошибки частоты

и сигналу оценки ошибки частоты  вырабатывают суммарную оценку текущей относительной расстройки (ошибки) фазы и частоты опорного сигнала. Далее в соответствие с сигналом оценки суммарной текущей относительной расстройки на выходе численно управляемого осциллятора (вычислителя) (NCO) 5 формируют квадратурный опорный сигнал и осуществляют в нем адаптивное изменение текущих параметров.

вырабатывают суммарную оценку текущей относительной расстройки (ошибки) фазы и частоты опорного сигнала. Далее в соответствие с сигналом оценки суммарной текущей относительной расстройки на выходе численно управляемого осциллятора (вычислителя) (NCO) 5 формируют квадратурный опорный сигнал и осуществляют в нем адаптивное изменение текущих параметров.

Данную процедуру корректировки (подстройки) параметров опорного сигнала в устройстве-прототипе выполняют периодически с временным дискретным шагом Tα.

Задача, которую решает предлагаемое техническое решение, - формирование опорного сигнала и корректировка его параметров (частоты и фазы) вычислительными (программными) средствами, в том числе при значительной расстройке частоты и неопределенности начальной фазы.

Поставленная задача решается на основе универсального способа формирования опорного сигнала вычислительными средствами и оригинальной процедуры управления в процессе формирования опорного сигнала и корректировки его параметров, которые выполнены в едином изобретательском замысле и позволяют при реализации получить эквивалентный технический эффект.

Согласно предлагаемому техническому решению способ формирования опорного сигнала и корректировки его параметров (частоты и фазы) вычислительными средствами в системе автоподстройки частоты и фазы заключается в том, что:

- Непрерывный входной широкополосный сигнал на радиочастоте предварительно преобразуют в квадратурный комплексный дискретный широкополосный сигнал на промежуточной частоте, выполняют процедуру синхронизации по времени и выделяют в результате фазовой демодуляции ШПС дискретный гармонический комплексный сигнал на промежуточной частоте.

- В соответствии с сигналами управления выполняют пошаговую вычислительную процедуру формирования опорного сигнала и корректировку (подстройку) его частоты и фазы для этого:

- Предварительно, используя вычислительную процедуру, формируют начальный дискретный опорный квадратурный (комплексный) гармонический сигнал с нулевой частотой и нулевой начальной фазой.

- В течение первого шага процедуры формирования опорного сигнала сравнивают параметры входного комплексного дискретного гармонического сигнала на промежуточной частоте с параметрами сформированного опорного квадратурного (комплексного) гармонического дискретного сигнала с нулевой частотой и нулевой начальной фазой.

- В конце первого шага процедуры формирования опорного сигнала оценивают суммарный набег фазы и среднюю частоту входного дискретного гармонического комплексного сигнала на промежуточной частоте.

- Используя в качестве начальной фазы - оценку суммарного набега фазы и в качестве частоты - оценку средней частоты входного дискретного гармонического комплексного сигнала на промежуточной частоте, вычислительными средствами формируют опорный сигнал с данными параметрами. Вследствие этого в начале второго шага вычислительной процедуры формирования опорного сигнала создают квазисинхронный режим между входным и опорным сигналом.

- На втором шаге вычислительной процедуры оценивают относительную фазовую расстройку и ошибку оценки частоты входного дискретного гармонического комплексного сигнала на промежуточной частоте и опорного сигнала.

- Полученные на втором шаге оценки относительной фазовой расстройки и ошибки оценки частоты используют соответственно в качестве начальной фазы и поправки к оценке частоты первого шага при вычислении опорного сигнала для третьего шага.

- Далее на третьем и на каждом последующем шаге вычислительной процедуры при формировании опорного сигнала процедура корректировки его параметров по начальной фазе и текущей частоте идентична и включает следующие операции:

- В течение времени текущего шага вычислительной процедуры выполняют оценку набега фазы, которую используют в качестве начальной фазы опорного сигнала на последующем шаге.

- Используя оценку набега фазы на текущем шаге и оценку набега фазы на предыдущем шаге, вычисляют оценку ошибки расстройки частоты на текущем шаге.

- Полученную оценку ошибки расстройки частоты на текущем шаге используют для корректировки текущей частоты при вычислении опорного сигнала.

- Оценку текущего набега фазы и вычисленную оценку текущей частоты используют в качестве параметров для вычисления текущего опорного сигнала на последующем шаге.

Таким образом, при последовательном пошаговом выполнении процедуры формирования и корректировки текущей частоты и начальной фазы в итоге формируют опорный сигнал, синхронный входному сигналу.

Способ формирования опорного сигнала и корректировки его параметров предлагаемого технического решения соответствует следующей формальной математической модели.

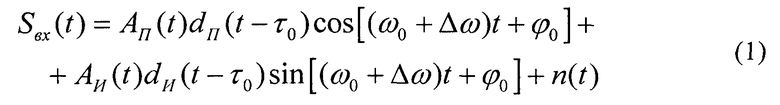

Пусть на вход системы частотно-фазовой синхронизации приемника ШПС поступает широкополосный радиосигнал Sвх(t) с нестабильной несущей частотой и случайной начальной фазой, включающий, как правило, ортогональные информационную и пилот компоненту:

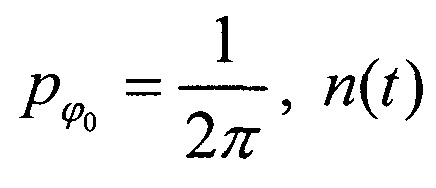

Здесь АП(t), АИ(t) - амплитуда пилот и информационной составляющей, dП(t), dИ(t) - кодовые пилот и информационные последовательности, τ0 - истинное временное положение входного ШПС, ω0 - круговая несущая частота, Δω - нестабильность несущей частоты, φ0 - случайная начальная фаза, распределенная чаще всего по равномерному закону,  - аддитивный белый гауссовский шум.

- аддитивный белый гауссовский шум.

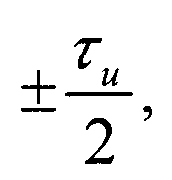

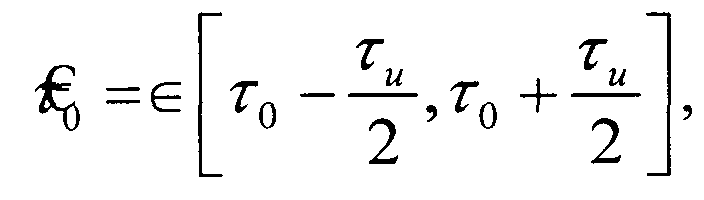

Следует отметить, что для выполнения процедуры частотно-фазовой синхронизации в ШСС в силу синхронности по времени, ортогональности и слабой коррелированности пилот и информационного сигнала автоподстройку частоты и фазы достаточно производить только по известному пилот сигналу. По причине случайности начальной фазы входного ШПС на начальном этапе в системах автоматического управления (синхронизации) необходимо обеспечить некогерентный режим, инвариантный к значению фазы, и реализовать квадратурную обработку сигнала. При этом предполагается, что предварительно реализована процедура поиска входного широкополосного пилот сигнала по времени. Чаще всего процедура поиска обеспечивает оценку истинного временного положения ШПС τ0 с точностью  то есть

то есть  где τu - длительность элементарного символа (чипа) псевдослучайной последовательности (ПСП),

где τu - длительность элементарного символа (чипа) псевдослучайной последовательности (ПСП),  - оценка временного положения ШПС.

- оценка временного положения ШПС.

Известно, что процедура синхронизации качественнее реализуется для сигналов, дискретизированных по времени. Поэтому после выполнения операции дискретизации, формирования квадратур и переноса их на промежуточную частоту комплексное представление пилот составляющей входного широкополосного сигнала на промежуточной частоте имеет вид:

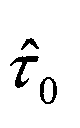

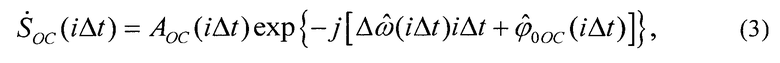

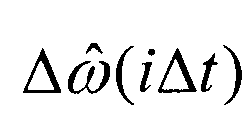

а выходной вычисляемый опорный комплексный дискретный сигнал можно представить как:

где  и

и  - оценки текущей частоты и начальной фазы входного широкополосного сигнала на промежуточной частоте, AOC(iΔt) - амплитуда опорного сигнала, АГ(iΔt) - амплитуда гетеродина, φГ - фаза гетеродина, i - номер текущей временной позиции, Δt - шаг временного дискрета.

- оценки текущей частоты и начальной фазы входного широкополосного сигнала на промежуточной частоте, AOC(iΔt) - амплитуда опорного сигнала, АГ(iΔt) - амплитуда гетеродина, φГ - фаза гетеродина, i - номер текущей временной позиции, Δt - шаг временного дискрета.

В данном случае предполагается, что перенос на промежуточную частоту выполняется с помощью гетеродина. Далее в результате фазовой демодуляции пилот составляющей входного широкополосного сигнала формируют комплексное представление входного дискретного гармонического сигнала системы частотно-фазовой синхронизации на промежуточной частоте:

где A2(iΔt)=AП(iΔt)АГ(iΔt)dП(iΔt-τ0),  - сигнал генератора ПСП пилот составляющей на временной позиции

- сигнал генератора ПСП пилот составляющей на временной позиции  полученной в результате предварительно реализованной процедуры поиска и синхронизации входного широкополосного пилот сигнала по времени. Данный входной дискретный комплексный гармонический сигнал используют для реализации процедуры формирования опорного сигнала.

полученной в результате предварительно реализованной процедуры поиска и синхронизации входного широкополосного пилот сигнала по времени. Данный входной дискретный комплексный гармонический сигнал используют для реализации процедуры формирования опорного сигнала.

Предлагаемый способ формирования опорного сигнала и корректировки его параметров заключается в выполнении следующей многошаговой вычислительной процедуры, которая на каждом шаге формирует оценку относительной фазовой и частотной расстройки входного и опорного сигналов и реализует соответствующую корректировку параметров опорного сигнала.

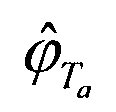

На первом шаге процедуры формирования опорного сигнала оценивают суммарную относительную фазовую расстройку входного гармонического сигнала на промежуточной частоте (4) и опорного сигнала с учетом нестабильности частоты Δω и случайности начальной фазы φ0. При этом в качестве опорного сигнала используют квадратурный (комплексный) сигнал (3) с нулевой частотой и нулевой начальной фазой. Такой подход (учет таких начальных условий) позволяет в конце первого шага оценить суммарный набег фазы  и среднюю частоту нестабильности входного ШПС

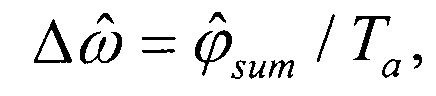

и среднюю частоту нестабильности входного ШПС  где Tα - время анализа, которое согласно теоретическим и экспериментальным оценкам должно быть Tα≤Т/2. Здесь Т - период сигнала с частотой биений Δf=Δω/2π, равной частоте нестабильности Δω, то есть Т=1/Δf.

где Tα - время анализа, которое согласно теоретическим и экспериментальным оценкам должно быть Tα≤Т/2. Здесь Т - период сигнала с частотой биений Δf=Δω/2π, равной частоте нестабильности Δω, то есть Т=1/Δf.

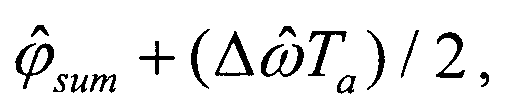

Используя для формирования (вычисления) опорного сигнала (3) в качестве начальной фазы оценку суммарного набега фазы  полученную на первом шаге, и в качестве текущей частоты оценку средней частоты нестабильности входного сигнала

полученную на первом шаге, и в качестве текущей частоты оценку средней частоты нестабильности входного сигнала  в начале второго шага подстройки создают квазисинхронный режим. Узкополосный входной сигнал и опорный сигнал в этой точке синхронны по фазе. При этом текущая частота опорного сигнала на втором шаге подстройки равна оценке средней частоты нестабильности входного узкополосного гармонического сигнала.

в начале второго шага подстройки создают квазисинхронный режим. Узкополосный входной сигнал и опорный сигнал в этой точке синхронны по фазе. При этом текущая частота опорного сигнала на втором шаге подстройки равна оценке средней частоты нестабильности входного узкополосного гармонического сигнала.

Необходимость учета поправки начальной фазы  возникает в случае использования в системе в качестве фильтра сумматора.

возникает в случае использования в системе в качестве фильтра сумматора.

Далее в течение второго шага процедуры формирования опорного сигнала относительная фазовая расстройка узкополосного входного гармонического сигнала и опорного сигнала пропорциональна ошибке оценки промежуточной частоты

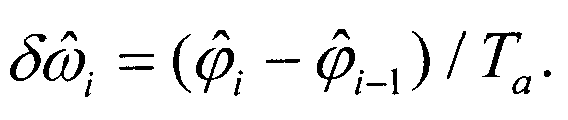

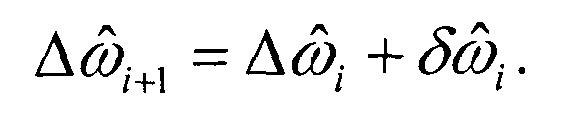

Третий и последующие шаги формирования и корректировки параметров опорного сигнала по частоте и фазе идентичны и включают следующие операции. По окончании, например, i-го шага выполняют оценку текущего набега фазы  которую применяют в качестве начальной фазы опорного сигнала на следующем (i+1)-м шаге. Используя оценку фазы i-го шага

которую применяют в качестве начальной фазы опорного сигнала на следующем (i+1)-м шаге. Используя оценку фазы i-го шага  и оценку фазы на предыдущем (i-1)-м шаге

и оценку фазы на предыдущем (i-1)-м шаге  вычисляют оценку ошибки расстройки частоты входного сигнала и опорного сигнала i-го текущего шага

вычисляют оценку ошибки расстройки частоты входного сигнала и опорного сигнала i-го текущего шага  Полученную оценку используют для вычисления текущей частоты опорного сигнала на следующем (i+1)-м шаге

Полученную оценку используют для вычисления текущей частоты опорного сигнала на следующем (i+1)-м шаге

Таким образом, при последовательном пошаговом выполнении процедуры корректировки текущей частоты и начальной фазы в итоге формируют опорный сигнал, синхронный входному сигналу.

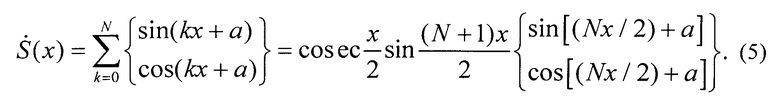

Необходимо отметить, что в предлагаемом способе в качестве фильтра при оценке относительной фазовой расстройки дискретных сигналов чаще всего используют сумматор. При этом, например, выполняют последовательное суммирование отсчетов регулярного гармонического сигнала на интервале анализа Tα. Такой подход дает возможность представить среднюю оценку набега фазы дискретного комплексного гармонического сигнала в аналитическом виде.

Для регулярного аргумента квадратурные компоненты гармонического сигнала на выходе сумматора [Двайт Г.Б. Таблицы интегралов и другие математические формулы / Г.Б. Двайт. - М.: Наука, 1978. - 228 с., С.82., Прудников А.П., Брычков Ю.А., Маричев О.И. Интегралы и ряды. В 3 т. Т.1 Элементарные функции / А.П. Прудников, Ю.А Брычков, О.И. Маричев. - М.: ФИЗМАТЛИТ, 2002. - 632 с., С.515]] имеют вид:

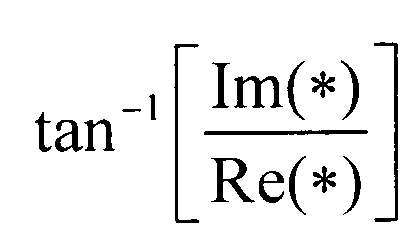

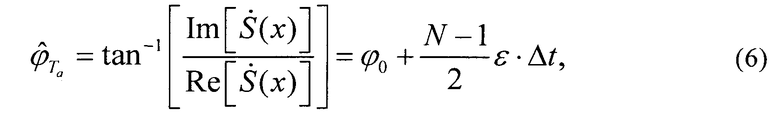

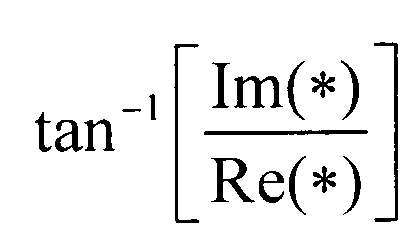

Здесь α=φ0 - начальная фаза, х=ε·Δt=Δφ - фазовый набег в течение интервала временного дискрета Δt, ε - текущая частотная расстройка. Тогда оценка фазового набега  в течение интервала анализа Tα=(N-1)Δt с использованием функционального преобразователя

в течение интервала анализа Tα=(N-1)Δt с использованием функционального преобразователя  имеет вид

имеет вид

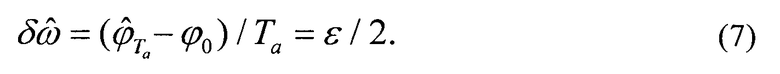

а оценка относительной ошибки частоты входного сигнала и опорного сигнала

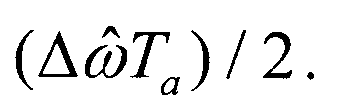

Из выражения (7) следует, что при данном алгоритме оценка ошибки частоты входного сигнала со случайной начальной фазой вдвое меньше истинного значения. Вследствие этого для создания корректных квазикогерентных начальных условий обработки на втором шаге процедуры частотно-фазовой синхронизации важно ввести необходимую поправку оценки при назначении начальной фазы опорного сигнала. В качестве поправки начальной фазы на втором шаге подстройки используют набег

Набег фазы при использовании квадратурной обработки чаще всего оценивают с использованием функционального преобразователя  и вычисляют по главному значению аргумента с учетом периодичности функции arctg(x)=arctg(x±kπ), k=0, 1, 2 …

и вычисляют по главному значению аргумента с учетом периодичности функции arctg(x)=arctg(x±kπ), k=0, 1, 2 …

Существует много способов формирования опорного гармонического сигнала (3). Основными требованиями к этим способам являются, во-первых, достаточная точность представления и, во-вторых, минимальные аппаратурные и программные (вычислительные) затраты.

При формировании опорного сигнала вычислительными средствами существует большое количество разнообразных методов получения элементарных функций [Байков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в ЦВМ / В.Д. Байков В.Б. Смолов. - Л.: Изд-во Ленингр. ун-та, 1975. - 96 с., Теслер Г.С. Обобщенные адаптивные аппроксимации функций / Г.С. Теслер // Математические машины и системы. - 1998. - №2], в том числе гармонического сигнала. Из них в цифровой технике нашли применение: методы разложения в ряд по ортогональным многочленам, методы аппроксимации с помощью наилучшего приближения, методы представления в виде цепных дробей, методы рациональных приближений, методы итерации, табличные методы, специализированные методы CORDIC [Jack E. Voider. The CORDIC Trigonometric Computing Technique / Reprinted, with permission, from IRE Trans. Electron. Comput. EC-W. 8, 1959, p.330-334] и другие.

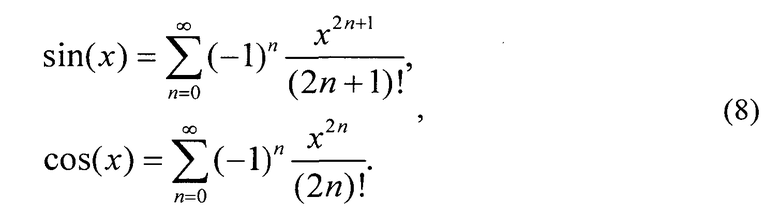

Чаще всего [Байков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в ЦВМ / В.Д. Байков В.Б. Смолов. - Л.: Изд-во Ленингр. ун-та, 1975. - 96 с.] используют представление гармонического сигнала в виде степенного ряда Тейлора [Двайт Г.Б. Таблицы интегралов и другие математические формулы / Г.Б. Двайт. - М.: Наука, 1978. - 228 с., с.79]:

Как правило, для упрощения реализации ряд ограничивают конечным числом членов (отсчетов сигнала), обеспечивающих требуемую точность представления. Для одинаковой точности представления объем вычислительных затрат (степень полинома) в значительной мере зависит от свойств используемой функции и интервала представления.

В соответствии с выполненной сравнительной оценкой для одинаковой (удовлетворительной) точности представления функций sin(x) и cos(x) на интервале периода удобнее использовать их разложения в ряд Тейлора на интервале х1∈[-π, π]. В этом случае на интервале х1∈[-π, π] достаточно учитывать полином 9-й степени. В то же время для представления этих функций на интервале х∈[0,2π] требуется полином 17-й степени. Это связано с центральной симметрией функции sin(x) и зеркальной симметрией функции cos(x) относительно начала координат на интервале х1∈[-π, π]. С другой стороны, выбор интервала изменения аргумента x1∈[-π, π] с учетом периодичности функций sin(x) и cos(x) позволяет значительно сократить вычислительные затраты и увеличить возможности процессора.

Связь переменных х и x1 из интервалов представления х1∈[-π, π] и х∈[0,2π] функций sin(x) и cos(x) при учете периодичности имеет вид: x1=х, если 0≤x≤π, и х1=(x-2π), если π<x≤2π.

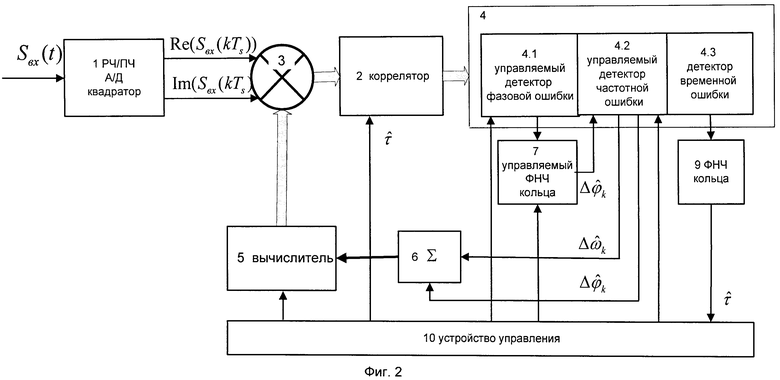

Для осуществления предлагаемого способа в устройство формирования опорного сигнала вычислительными средствами в системах частотной и фазовой синхронизации широкополосных систем связи, содержащее стандартный блок следящего приемника широкополосного сигнала (ШПС), включающий схему преобразования несущей радиочастоты входного широкополосного сигнала на промежуточную частоту; схему преобразования сигнала из аналогового вида в квадратурное дискретное представление, а также систему временной, частотной и фазовой синхронизации ШПС, включающую коррелятор, комплексный перемножитель, детектор ошибок параметров сигнала, состоящий из детекторов фазовой, частотной и временной ошибки, причем выход детектора фазовой ошибки соединен с входом фильтра низких частот (ФНЧ) кольца фазовой ошибки, а выход детектора временной ошибки соединен с входом ФНЧ кольца ошибки временной задержки, кроме того, последовательно соединенные сумматор фазовой и частотной ошибок и численно управляемый вычислитель, выход которого соединен шиной с соответствующим входом комплексного перемножителя, вход стандартного блока следящего приемника ШПС является входом устройства, согласно изобретению, введено устройство управления, соответствующие выходы которого соединены с управляющими входами вычислителя, коррелятора, ФНЧ кольца фазовой ошибки, кроме того, выход ФНЧ кольца временной ошибки подключен к соответствующему входу устройства управления, при этом детекторы фазовой и частотной ошибки выполнены управляемыми, их управляющие входы подсоединены к соответствующим выходам устройства управления; выходы управляемого детектора частотной ошибки соединены с соответствующими входами сумматора; выход ФНЧ кольца фазовой ошибки подключен к входу управляемого детектора частотной ошибки; квадратурные выходы стандартного блока следящего приемника ШПС соединены с соответствующими входами комплексного перемножителя, выход которого соединен шиной с входом коррелятора, выход которого соединен шиной с соответствующим входом детектора ошибок параметров сигнала.

Общая структурная схема предлагаемого устройства представлена на фиг.2, где обозначено:

1 - стандартный блок следящего приемника ШПС;

2 - коррелятор (интерполятор);

3 - комплексный перемножитель;

4 - детектор ошибок параметров сигнала;

4.1 - управляемый детектор фазовой ошибки;

4.2 - управляемый детектор частотной ошибки;

4.3 - детектор временной ошибки;

5 - численно управляемый вычислитель (осциллятор);

6 - сумматор фазовой и частотной ошибок;

7 - управляемый фильтр низких частот (ФНЧ) кольца фазовой ошибки;

9 - ФНЧ кольца ошибки временной задержки;

10 - устройство управления.

Устройство для реализации технического решения заявляемого способа содержит: стандартный блок следящего приемника ШПС 1, включающий схему преобразования несущей радиочастоты входного широкополосного сигнала на промежуточную частоту (РЧ/ПЧ) и схемы преобразования сигнала из аналогового вида в квадратурное дискретное представление (А/Д, квадратор), и схему временной, частотной и фазовой синхронизации ШПС, состоящей из последовательно соединенных комплексного перемножителя 3, коррелятора (интерполятора) 2, детектора ошибок параметров сигнала 4, состоящего из управляемых детекторов фазовой 4.1, частотной 4.2 ошибки и детектора временной ошибки 4.3, выход которого через кольцо ФНЧ 9 соединен с соответствующим входом устройства управления 10, соответствующие выходы которого соединены с управляющими входами коррелятора 2, управляемых детекторов фазовой 4.1 и частотной 4.2 ошибки, а также с входом управляемого ФНЧ кольца 7, выход которого соединен с соответствующим входом управляемого детектора частотной ошибки 4.2. Выход управляемого детектора фазовой ошибки 4.1 подключен к другому входу управляемого ФНЧ кольца 7. Выход детектора временной ошибки 4.3 подключен к входу ФНЧ кольца ошибки временной задержки 9, выход которого соединен с соответствующим входом устройства управления 10. Кроме того, выходы управляемого детектора частотной ошибки 4.2 соединены с соответствующими входами сумматора фазовой и частотной ошибок 6, выход которого соединен с входом вычислителя 5, управляемый вход которого соединен с соответствующим выходом устройства управления 10, выход вычислителя 5 соединен шиной с соответствующим входом перемножителя 3. Квадратурные выходы стандартного блока следящего приемника ШПС 1 подсоединены к соответствующим входам перемножителя 3. Вход стандартного блока следящего приемника ШПС 1 является входом устройства. Причем соединения перемножителя 3 с коррелятором 2 и коррелятора 2 с детектором ошибок параметров сигнала 4 выполнены шиной.

В качестве численно управляемого вычислителя 5 гармонического сигнала, формирующего в заявляемом устройстве опорный сигнал, используется вычислитель, выполненный, например, на базе ПЛИС или DSP, реализующий процедуру представления сигнала в виде разложения в степенной ряд Тейлора.

Работает предлагаемое устройство следующим образом.

Описание работы предлагаемого устройства достаточно полно рассмотрено ранее при анализе общей математической модели предложенного технического решения в части формирования опорного сигнала и корректировки его параметров. Последовательность операций работы заявляемого устройства в полной мере соответствует алгоритму выполнения предложенного способа. При этом следует учесть, что изменение порядка осуществления последовательных линейных операций в предложенном устройстве не приводит к изменению конечного результата обработки.

Пошаговая вычислительная процедура, которая реализована в предлагаемом устройстве, может быть использована при значительных величинах относительной частотной и фазовой расстройки. Она эффективна как на начальном этапе (в режиме захвата частоты), так и при последующем режиме слежения. В отличие от прототипа предлагаемая процедура обладает более высокой помехоустойчивостью, т.к. дополнительно используют управление процедурой генерации опорного сигнала и корректировки его параметров.

Представленное решение проблемы автоподстройки частоты сочетает в себе способность точной подстройки частоты при умеренных аппаратных затратах на его реализацию. Вариант реализации предлагаемого устройства позволяет универсальными вычислительными средствами проводить с заданной точностью подстройку частоты опорного сигнала даже при достаточно низком входном отношении сигнал-шум.

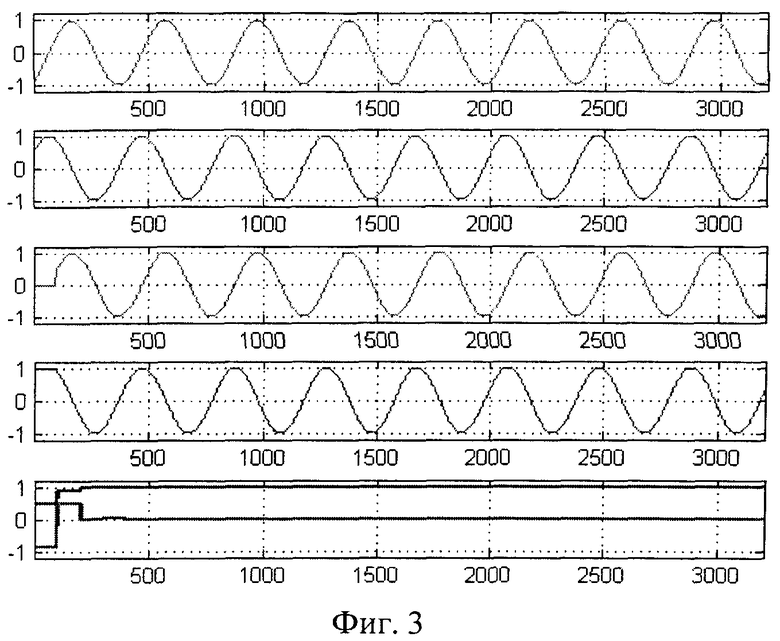

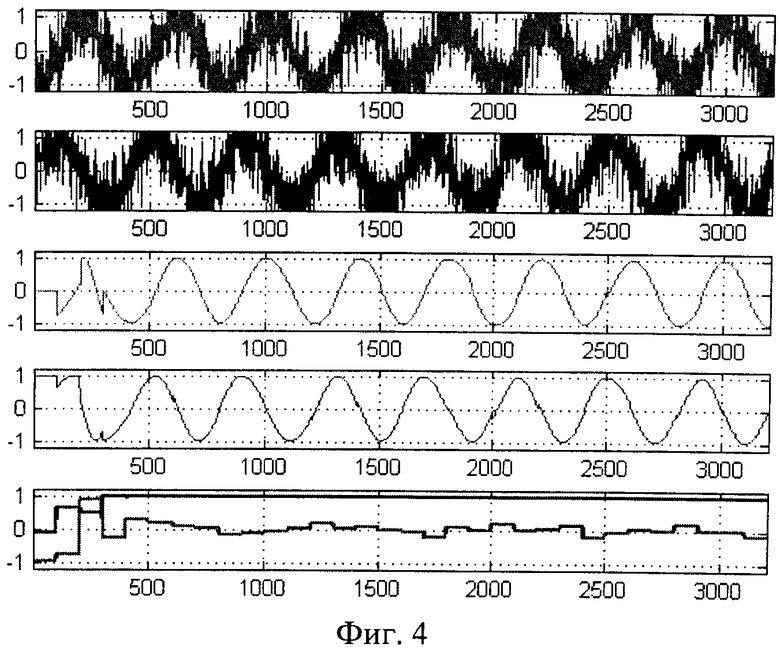

В качестве иллюстрации для предложенной системы частотно-фазовой синхронизации на фиг.3 и фиг.4 представлены временные эпюры (диаграммы) сигналов вычислительной процедуры формирования опорного сигнала, полученные в результате компьютерного моделирования. Опорный сигнал получен методом разложения в степенной ряд Тейлора. На фиг.3 представлены диаграммы при отсутствии шумов во входном сигнале и на фиг.4 - для отношения сигнал-шум на входе, равном 5 дБ. Здесь на первом и на втором графике сверху каждой фигуры представлены эпюры сигналов синусной и косинусной составляющих входного сигнала на промежуточной частоте, на третьем и на четвертом графике показана последовательная процедура формирования соответствующих квадратурных составляющих опорного сигнала системы. На последнем графике фиг.3 и фиг.4 представлены переходные процессы подстройки ошибки фазы квадратурных составляющих выходного опорного сигнала.

Сравнение заявляемых объектов с известными техническими решениями в данной области техники не позволило выявить совокупность заявляемых признаков, и поэтому они обеспечивают заявляемому техническому решению соответствие критериям «новизна», «существенные отличия» и «изобретательский уровень».

Графические материалы, используемые при описании изобретения

Фиг.1 - общая структурная схема устройства-прототипа.

Фиг.2 - общая структурная схема заявляемого устройства.

Фиг.3 - эпюры сигналов вычислительной процедуры формирования опорного сигнала в отсутствии шумов на входе системы частотно-фазовой подстройки.

Фиг.4 - эпюры сигналов вычислительной процедуры формирования опорного сигнала для отношения сигнал-шум на входе системы частотно-фазовой подстройки, равном 5 Дб.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство высокоточной оценки несущей частоты сигнала в широкополосных системах связи | 2018 |

|

RU2691380C1 |

| Способ высокоточной оценки несущей частоты сигнала в широкополосных системах связи | 2018 |

|

RU2691972C1 |

| Способ высокоточного слежения за временной задержкой широкополосного сигнала и устройство для его реализации | 2016 |

|

RU2667483C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНЫХ УСТРОЙСТВ ПО НЕСУЩЕЙ И ТАКТОВОЙ ЧАСТОТАМ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ В УСЛОВИЯХ БОЛЬШОЙ НЕСТАБИЛЬНОСТИ ЧАСТОТ В КАНАЛЕ СВЯЗИ | 2011 |

|

RU2450446C1 |

| СПОСОБ АДАПТИВНОГО И СОГЛАСОВАННОГО ПОДАВЛЕНИЯ ФЛУКТУАЦИОННЫХ ШУМОВ И СОСРЕДОТОЧЕННЫХ ПОМЕХ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2013 |

|

RU2539573C1 |

| Устройство синхронизации широкополосных псевдослучайных сигналов | 1985 |

|

SU1415445A1 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2353064C1 |

| Способ обнаружения и оценивания характеристик широкополосных сигналов и устройство для его реализации | 2023 |

|

RU2814220C1 |

| Приемное устройство широкополосного сигнала | 1982 |

|

SU1109915A1 |

| СПОСОБ АВТОПОДСТРОЙКИ ЧАСТОТЫ ОПОРНОГО СИГНАЛА ПРИЕМНОЙ СТАНЦИИ, СПОСОБ ОЦЕНИВАНИЯ РАССТРОЙКИ ЧАСТОТЫ СИГНАЛОВ ЛУЧЕЙ ОТНОСИТЕЛЬНО ЧАСТОТЫ ОПОРНОГО СИГНАЛА, УСТРОЙСТВО АВТОПОДСТРОЙКИ ЧАСТОТЫ ОПОРНОГО СИГНАЛА ПРИЕМНОЙ СТАНЦИИ | 2005 |

|

RU2286015C1 |

Изобретение относится к области широкополосных систем радиосвязи и может быть использовано для генерации опорного сигнала и адаптивной корректировки его параметров в стационарных и мобильных станциях. Технический результат - генерирование и корректировка опорного сигнала в широком диапазоне расстроек частоты и отношения сигнал-шум. Устройство формирования опорного сигнала вычислительными средствами в системах частотной и фазовой синхронизации широкополосных систем связи включает устройство управления, к входу которого подключен выход ФНЧ кольца временной ошибки, а соответствующие выходы которого соединены с управляющими входами вычислителя, коррелятора, ФНЧ кольца фазовой ошибки. Детекторы фазовой и частотной ошибки выполнены управляемыми, их управляющие входы подсоединены к соответствующим выходам устройства управления, выходы управляемого детектора частотной ошибки соединены с соответствующими входами сумматора, выход ФНЧ кольца фазовой ошибки подключен к входу детектора частотной ошибки. Квадратурные выходы стандартного блока следящего приемника ШПС соединены с соответствующими входами комплексного перемножителя, выход которого соединен шиной с входом коррелятора, выход которого соединен шиной с соответствующим входом детектора ошибок параметров сигнала. 2 н. и 2 з.п. ф-лы, 4 ил.

1. Способ формирования опорного сигнала вычислительными средствами в системах частотной и фазовой синхронизации широкополосных систем связи, заключающийся в том, что непрерывный входной широкополосный сигнал на радиочастоте предварительно преобразуют в квадратурный комплексный дискретный широкополосный сигнал на промежуточной частоте, выполняют процедуру синхронизации по времени и выделяют в результате фазовой демодуляции ШПС дискретный гармонический комплексный сигнал на промежуточной частоте, в соответствии с сигналами управления выполняют пошаговую вычислительную процедуру формирования опорного сигнала и корректировку (подстройку) его частоты и фазы, для этого: предварительно, используя вычислительную процедуру, формируют начальный дискретный опорный квадратурный (комплексный) гармонический сигнал с нулевой частотой и нулевой начальной фазой, в течение первого шага процедуры формирования опорного сигнала сравнивают параметры входного комплексного дискретного гармонического сигнала на промежуточной частоте с параметрами сформированного опорного квадратурного (комплексного) гармонического дискретного сигнала с нулевой частотой и нулевой начальной фазой, в конце первого шага процедуры формирования опорного сигнала оценивают суммарный набег фазы и среднюю частоту входного дискретного гармонического комплексного сигнала на промежуточной частоте, используя в качестве начальной фазы - оценку суммарного набега фазы и в качестве частоты - оценку средней частоты входного дискретного гармонического комплексного сигнала на промежуточной частоте, вычислительными средствами формируют опорный сигнал с данными параметрами и вследствие этого в начале второго шага вычислительной процедуры формирования опорного сигнала создают квазисинхронный режим между входным и опорным сигналом, на втором шаге вычислительной процедуры оценивают относительную фазовую расстройку и ошибку оценки частоты входного дискретного гармонического комплексного сигнала на промежуточной частоте и опорного сигнала, полученные на втором шаге оценки относительной фазовой расстройки и ошибки оценки частоты используют соответственно в качестве начальной фазы и поправки к оценке частоты первого шага при вычислении опорного сигнала для третьего шага, далее на третьем и на каждом последующем шаге вычислительной процедуры при формировании опорного сигнала процедура корректировки его параметров по начальной фазе и текущей частоте идентична и включает следующие операции: в течение времени текущего шага вычислительной процедуры выполняют оценку набега фазы, которую используют в качестве начальной фазы опорного сигнала на последующем шаге, используя оценку набега фазы на текущем шаге и оценку набега фазы на предыдущем шаге, вычисляют оценку ошибки расстройки частоты на текущем шаге, полученную оценку ошибки расстройки частоты на текущем шаге используют для корректировки текущей частоты при вычислении опорного сигнала, оценку текущего набега фазы и вычисленную оценку текущей частоты используют в качестве параметров для вычисления текущего опорного сигнала на последующем шаге.

2. Устройство формирования опорного сигнала вычислительными средствами в системах частотной и фазовой синхронизации широкополосных систем связи, содержащее стандартный блок следящего приемника широкополосного сигнала (ШПС), включающий схему преобразования несущей радиочастоты входного широкополосного сигнала на промежуточную частоту; схему преобразования сигнала из аналогового вида в квадратурное дискретное представление, а также систему временной, частотной и фазовой синхронизации ШПС, включающую коррелятор, комплексный перемножитель, детектор ошибок параметров сигнала, состоящий из детекторов фазовой, частотной и временной ошибки, причем выход детектора фазовой ошибки соединен с входом фильтра низких частот (ФНЧ) кольца фазовой ошибки, а выход детектора временной ошибки соединен с входом ФНЧ кольца ошибки временной задержки, кроме того, последовательно соединенные сумматор фазовой и частотной ошибок и численно управляемый вычислитель, выход которого соединен шиной с соответствующим входом комплексного перемножителя, вход стандартного блока следящего приемника ШПС является входом устройства, отличающееся тем, что введено устройство управления, соответствующие выходы которого соединены с управляющими входами вычислителя, коррелятора, ФНЧ кольца фазовой ошибки, кроме того, выход ФНЧ кольца временной ошибки подключен к соответствующему входу устройства управления, при этом детекторы фазовой и частотной ошибки выполнены управляемыми, их управляющие входы подсоединены к соответствующим выходам устройства управления; выходы управляемого детектора частотной ошибки соединены с соответствующими входами сумматора; выход ФНЧ кольца фазовой ошибки подключен к входу детектора частотной ошибки; квадратурные выходы стандартного блока следящего приемника ШПС соединены с соответствующими входами комплексного перемножителя, выход которого соединен шиной с входом коррелятора, выход которого соединен шиной с соответствующим входом детектора ошибок параметров сигнала.

3. Устройство по п.2, отличающееся тем, что численно управляемый вычислитель выполнен на ПЛИС или DSP, реализующих процедуру, которая использует разложение в ряд Тейлора.

4. Устройство по п.2, отличающееся тем, что устройство управления выполнено на ПЛИС или DSP, реализующих многошаговую вычислительную процедуру управления при формировании опорного сигнала и корректировки его параметров.

| MOHAMED К | |||

| NESAMI RF Architektures and Digital Signal Processing Aspects of Digital Wireless Transceivers | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| СПОСОБ АВТОПОДСТРОЙКИ ЧАСТОТЫ ОПОРНОГО СИГНАЛА ПРИЕМНОЙ СТАНЦИИ, СПОСОБ ОЦЕНИВАНИЯ РАССТРОЙКИ ЧАСТОТЫ СИГНАЛОВ ЛУЧЕЙ ОТНОСИТЕЛЬНО ЧАСТОТЫ ОПОРНОГО СИГНАЛА, УСТРОЙСТВО АВТОПОДСТРОЙКИ ЧАСТОТЫ ОПОРНОГО СИГНАЛА ПРИЕМНОЙ СТАНЦИИ | 2005 |

|

RU2286015C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНЫХ УСТРОЙСТВ ПО НЕСУЩЕЙ И ТАКТОВОЙ ЧАСТОТАМ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ В УСЛОВИЯХ БОЛЬШОЙ НЕСТАБИЛЬНОСТИ ЧАСТОТ В КАНАЛЕ СВЯЗИ | 2011 |

|

RU2450446C1 |

| US 8094767 B1, 10.01.2012. | |||

Авторы

Даты

2014-12-10—Публикация

2013-10-03—Подача