Изобретение относится к области радиотехники и может использоваться в широкополосных системах радиосвязи и радионавигации с шумоподобными сигналами с минимальной частотной манипуляцией и дополнительной ВОС-модуляцией (Binary Offset Carrier).

Известно устройство для приема шумоподобных сигналов, содержащее блок линейной части, согласованный фильтр, сумматор, линию задержки, детектор, ключ, опорный генератор, решающее устройство, синхронизатор и схему выделения [патент RU 2385542 C2, МПК H04L 27/14, 2006.01]. Недостатком устройства является низкая точность синхронизации.

Известно устройство для корреляционного приема сложных фазоманипулированных сигналов, содержащее первый и второй перемножители, сигнальные входы которых объединены, а выходы подключены к блоку некогерентной обработки ортогональных сигналов и сумматору, к выходу которого подключены последовательно соединенные полосовой фильтр, третий перемножитель и блок слежения за задержкой, выход которого подключен к синхронизирующему входу блока некогерентной обработки ортогональных сигналов [авт. св. SU 1046943 A, МПК H04B 1/10, 07.10.83].

Однако известное устройство обладает невысокой помехоустойчивостью.

Наиболее близким техническим решением к предлагаемому является корреляционный приемник шумоподобных сигналов с минимальной частотной манипуляцией, содержащий блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, третий, четвертый, пятый и шестой перемножители, вычитатель и сумматор, первый и второй интеграторы, входы которых подключены к выходам сумматора и вычитателя соответственно, решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы третьего и четвертого, пятого и шестого перемножителей объединены соответственно через вычитатель и сумматор, блок кодовой синхронизации, включающий временнóй дискриминатор, к выходу которого подключены последовательно соединенные второй петлевой фильтр и управляемый фазовращатель, другой вход которого подключен к выходу делителя частоты, входом соединенного с первым квадратурным выходом подстраиваемого генератора несущей частоты, а также генератор кода, дешифратор, подключенный к дополнительным выходам генератора кода, синтезатор опорных квадратурных сигналов, подключенный по входу к прямому выходу генератора кода, инверсный выход которого соединен с опорным входом временного дискриминатора, включающего последовательно соединенные восьмой перемножитель, сигнальный вход которого подключен к выходу сумматора, а опорный вход является опорным входом временного дискриминатора, третий интегратор, синхронизирующий вход которого соединен с синхронизирующими входами первого и второго интеграторов и подключен к выходу дешифратора, девятый перемножитель, опорный вход которого подключен к выходу решающего блока, при этом выходы синтезатора опорных квадратурных сигналов соединены соответственно с попарно объединенными опорными входами третьего и шестого, четвертого и пятого перемножителей, а выход решающего блока является выходом корреляционного приемника [патент RU 2374776 C2, МПК H04L 27/14, 2006.01].

Недостаток известного устройства - невысокая точность кодовой синхронизации, обусловленная аномальными ошибками вследствие периодичности характеристики дискриминатора системы слежения за задержкой шумоподобного сигнала с минимальной частотной манипуляцией и дополнительной ВОС-модуляцией.

Предлагаемое изобретение призвано решить задачу повышения точности кодовой синхронизации корреляционного приемника шумоподобного сигнала.

Поставленная задача решается тем, что в корреляционном приемнике шумоподобных сигналов, содержащем блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, третий, четвертый, пятый и шестой перемножители, первый вычитатель и сумматор, первый и второй интеграторы, входы которых подключены к выходам сумматора и первого вычитателя соответственно, решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы третьего и четвертого, пятого и шестого перемножителей объединены соответственно через первый вычитатель и сумматор, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные восьмой перемножитель, сигнальный вход которого подключен к выходу сумматора, третий интегратор и девятый перемножитель, опорный вход которого подключен к выходу решающего блока, а к выходу которого подключен второй петлевой фильтр, последовательно соединенные управляемый фазовращатель, генератор кода и синтезатор квадратурных сигналов, а также дешифратор, входы которого подключены к дополнительным выходам генератора кода, а к выходам которого подключены синхронизирующие входы первого, второго и третьего интеграторов, согласно изобретению в блок кодовой синхронизации введены управляемый тактовый генератор, вход которого соединен с выходом второго петлевого фильтра, а выход которого подключен к сигнальному входу управляемого фазовращателя, формирователь опорных сигналов, содержащий последовательно соединенные первый знаковый элемент, вход которого подключен к первому выходу синтезатора квадратурных сигналов, первый, второй и третий элементы задержки, последовательно соединенные второй знаковый элемент, вход которого подключен к второму выходу синтезатора квадратурных сигналов, четвертый и пятый элементы задержки, синтезатор частот, вход которого подключен к выходу управляемого тактового генератора, десятый, одиннадцатый, двенадцатый перемножители, сигнальные входы которых подключены соответственно к выходам первого, второго и третьего элементов задержки, а опорные входы которых соединены с первым выходом синтезатора частот, тринадцатый, четырнадцатый и пятнадцатый перемножители, сигнальные входы которых подключены соответственно к выходам второго знакового элемента, четвертого и пятого элементов задержки, а опорные входы которых соединены со вторым выходом синтезатора частот, третий и четвертый знаковые элементы, входы которых соединены соответственно с объединенными опорными входами третьего и шестого, четвертого и пятого перемножителей блока фазовой синхронизации и подключены соответственно к выходам одиннадцатого и четырнадцатого перемножителей, а выходы которых соединены со входами шестнадцатого перемножителя, к выходу которого подключен семнадцатый перемножитель, другой вход которого подключен к второму выходу синтезатора частот через пятый знаковый элемент, а выход которого соединен с опорным входом восьмого перемножителя временного дискриминатора, блок устранения неоднозначности, содержащий восемнадцатый, девятнадцатый, двадцатый, двадцать первый перемножители, последовательно соединенные второй вычитатель, четвертый интегратор, четвертый вычитатель и первый фильтр нижних частот, последовательно соединенные третий вычитатель, пятый интегратор, пятый вычитатель и второй фильтр нижних частот, а также командный блок, входы которого соединены с выходами первого и второго фильтров нижних частот, а выход которого подключен к управляющему входу управляемого фазовращателя, при этом сигнальные входы восемнадцатого и двадцатого, девятнадцатого и двадцать первого перемножителей попарно объединены и подключены соответственно к выходам первого и второго перемножителей блока фазовой синхронизации, опорные входы восемнадцатого и девятнадцатого, двадцатого и двадцать первого перемножителей подключены соответственно к выходам десятого и тринадцатого, двенадцатого и пятнадцатого перемножителей формирователя опорных сигналов, а выходы восемнадцатого и девятнадцатого, двадцатого и двадцать первого перемножителей объединены соответственно через второй и третий вычитатели, синхронизирующие входы четвертого и пятого интеграторов подключены к выходу дешифратора, другие входы четвертого и пятого вычитателей соединены с выходом первого интегратора блока фазовой синхронизации.

Введение перечисленных узлов с описанными связями позволяет по сравнению с прототипом повысить точность кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной манипуляцией и дополнительной BOC-модуляцией.

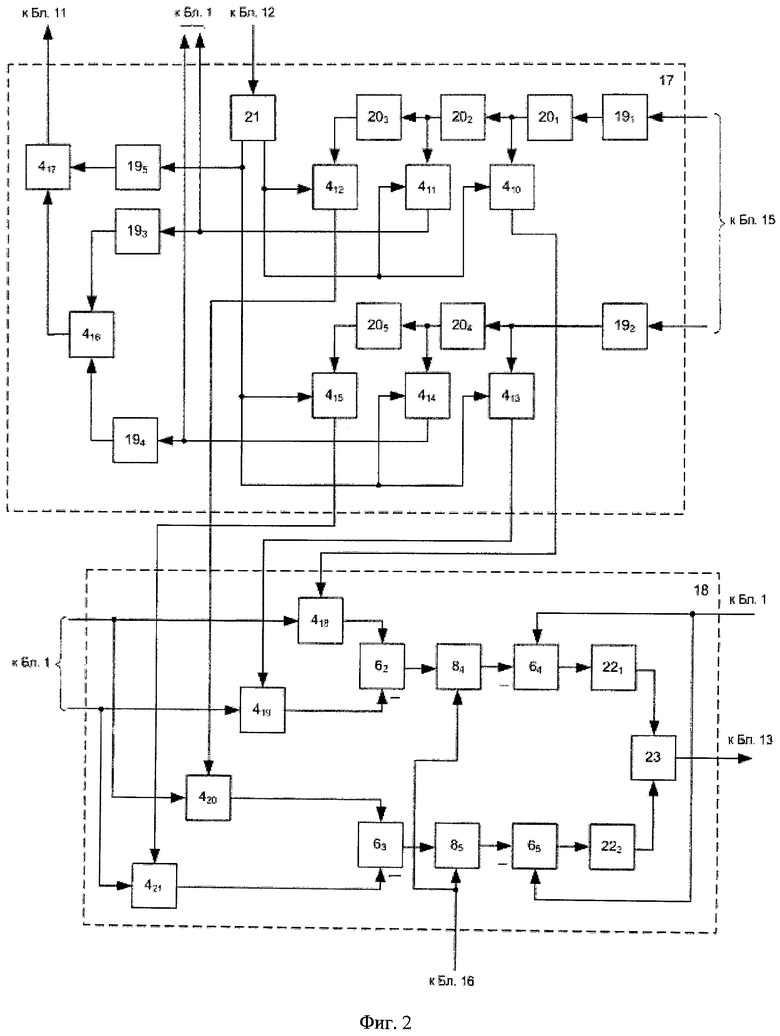

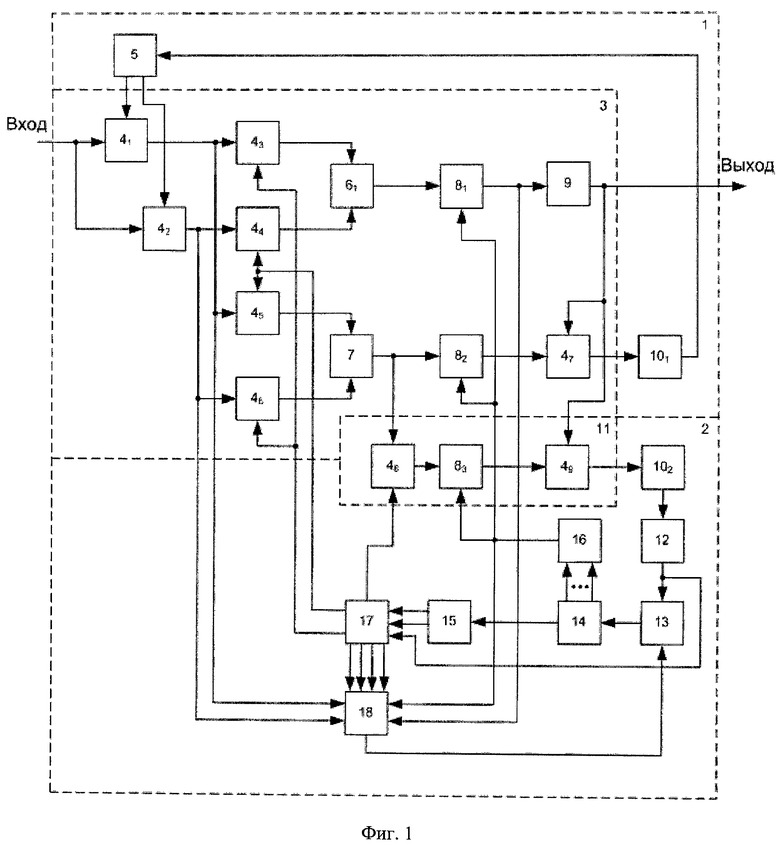

На фиг.1 приведена функциональная схема заявляемого устройства. На фиг.2 приведены функциональные схемы формирователя опорных сигналов и блока устранения неоднозначности.

Корреляционный приемник шумоподобных сигналов содержит блок 1 фазовой синхронизации и блок 2 кодовой синхронизации. Блок 1 фазовой синхронизации содержит фазовый дискриминатор 3, включающий первый 41 и второй 42 перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, а опорные входы подключены соответственно к квадратурным выходам подстраиваемого генератора 5 несущей частоты. Фазовый дискриминатор 3 содержит также третий 43, четвертый 44, пятый 45, шестой 46 и седьмой 47 перемножители, первый вычитатель 61 и сумматор 7, первый и второй интеграторы 81 и 82, решающий блок 9. В блок 1 фазовой синхронизации входит первый петлевой фильтр 101, вход которого подключен к выходу седьмого перемножителя 47, а выход соединен со входом подстраиваемого генератора 5 несущей частоты. При этом сигнальные входы третьего 43 и пятого 45, четвертого 44 и шестого 46 перемножителей попарно объединены и подключены соответственно к выходам первого 41 и второго 42 перемножителей. Выходы третьего 43 и четвертого 44, пятого 45 и шестого 46 перемножителей объединены соответственно через вычитатель 61 и сумматор 7, к выходам которых подключены соответственно первый и второй интеграторы 81 и 82. Сигнальный вход седьмого перемножителя 47 подключен к выходу второго интегратора 82, опорный вход перемножителя 47 подключен к выходу решающего блока 9, входом соединенного с выходом первого интегратора 81, при этом выход решающего блока 9 является и выходом корреляционного приемника.

Блок 2 кодовой синхронизации содержит последовательно соединенные временнóй дискриминатор 11, второй петлевой фильтр 102, управляемый тактовый генератор 12, управляемый фазовращатель 13, генератор 14 кода, синтезатор 15 квадратурных сигналов, а также дешифратор 16, формирователь 17 опорных сигналов и блок 18 устранения неоднозначности. Временной дискриминатор 11 включает последовательно соединенные восьмой перемножитель 48, сигнальный вход которого соединен с выходом сумматора 7, третий интегратор 83 и девятый перемножитель 49. Синхронизирующий вход интегратора 83 соединен с синхронизирующими входами интеграторов 81 и 82 и подключен к выходу дешифратора 16 и к одному из входов блока 18 устранения неоднозначности. Дешифратор 16 подключен к дополнительным выходам генератора 14 кода. Опорный вход перемножителя 49 соединен с опорным входом перемножителя 47 и подключен к выходу решающего блока 9, а выход перемножителя 49 соединен со входом петлевого фильтра 102. Управляющий вход управляемого фазовращателя 13 подключен к выходу блока 18 устранения неоднозначности.

Формирователь 17 опорных сигналов (фиг.2) содержит последовательно соединенные первый знаковый элемент 191, первый 201, второй 202 и третий 203 элементы задержки, последовательно соединенные второй знаковый элемент 192, четвертый 204 и пятый 205 элементы задержки, а также перемножители 410, 411, 412, 413, 414, 415 и синтезатор 21 частот. Входы знаковых элементов 191 и 192 подключены соответственно к выходам синтезатора 15 квадратурных сигналов. Сигнальные входы перемножителей 410, 411, 412 подключены соответственно к выходам первого 201, второго 202 и третьего 203 элементов задержки, а опорные входы перемножителей 410, 411, 412 соединены с первым выходом синтезатора 21 частот. Сигнальные входы перемножителей 413, 414, 415 подключены соответственно к выходам второго знакового элемента 192, четвертого 204 и пятого 205 элементов задержки, а опорные входы перемножителей 413, 414, 415 соединены со вторым выходом синтезатора 21 частот, вход которого подключен к выходу управляемого тактового генератора 12. Выходы перемножителей 411 и 412 соединены соответственно с объединенными опорными входами перемножителей 43 и 46, 44 и 45 блока 1 фазовой синхронизации.

Формирователь 17 опорных сигналов содержит также третий 193, четвертый 194 и пятый 195 знаковые элементы. Входы знаковых элементов 193 и 194 подключены к выходам перемножителей 411 и 414 соответственно, а выходы соединены с входами перемножителя 416, к выходу которого подключен перемножитель 417, выход которого подключен к опорному входу перемножителя 48 временного дискриминатора 11. Вход знакового элемента 195 соединен со вторым выходом синтезатора 21 частот, а выход соединен с другим входом перемножителя 417.

Блок 18 устранения неоднозначности (фиг.2) содержит два канала, каждый из которых включает соответственно перемножители 418, 419 и 420, 421, вычитатели 62, 64 и 63, 65, интеграторы 84 и 85 и фильтры 221 и 222 нижних частот, а также командный блок 23. Сигнальные входы перемножителей 418 и 420, 419 и 421 попарно объединены и подключены соответственно к выходам перемножителей 41 и 42 блока 1 фазовой синхронизации, а опорные входы перемножителей 418 и 419, 420 и 421 подключены соответственно к выходам перемножителей 410 и 413, 412 и 415 формирователя 17 опорных сигналов.

Выходы перемножителей 418 и 419, 420 и 421 объединены через вычитатели 62 и 63 соответственно, к выходам которых подключены интеграторы 84 и 85, синхронизирующие входы которых подключены к выходу дешифратора 16, а выходы которых соединены с входами вычитателей 64 и 65 соответственно, другими входами соединенных с выходом интегратора 81 блока 1 фазовой синхронизации. К выходам вычитателей 64 и 65 подключены входы фильтров 221 и 222 нижних частот соответственно, выходы которых соединены со входами командного блока 23, выход которого является выходом блока 18 устранения неоднозначности и соединен с управляющим входом управляемого фазовращателя 13.

Корреляционный приемник шумоподобных сигналов (ШПС) работает следующим образом. Входной шумоподобный сигнал поступает на перемножители 41 и 42, где перемножается с опорными квадратурными сигналами соответственно cos(ω0t) и sin(ω0t) частоты ω0, равной средней частоте ШПС. Указанные сигналы вырабатываются подстраиваемым генератором 5 несущей частоты блока 1 фазовой синхронизации. Квадратурные видеочастотные сигналы с выходов перемножителей 41 и 42 поступают на попарно объединенные сигнальные входы перемножителей 43 и 45, 44 и 46 соответственно, где перемножаются с опорными видеочастотными сигналами, вырабатываемыми формирователем 17 опорных сигналов блока 2 кодовой синхронизации. При идеальной кодовой синхронизации опорные квадратурные сигналы I0(t) и Q0(t) являются точными копиями квадратурных видеочастотных компонентов принимаемого ШПС.

Результаты перемножения квадратурных составляющих входного и опорных сигналов объединяются в вычитателе 61 и сумматоре 7, образуя соответственно «косинусную» и «синусную» квадратурные составляющие, пропорциональные cosφ(t) и sinφ(t), где φ(t) - фазовая ошибка системы синхронизации (составляющие удвоенной частоты ω0 подавляются при последующей обработке). Интеграторы 81 и 83 в квадратурных каналах фазового дискриминатора 3 осуществляют интегрирование поступающих на их входы квадратурных составляющих сжатого по спектру сигнала на интервалах, равных периоду Тп повторения ШПС. Сброс интеграторов 81 и 82 осуществляется с шагом Тп синхроимпульсами, вырабатываемыми дешифратором 16 блока 2 кодовой синхронизации.

Результаты z1 и z2 интегрирования в квадратурных каналах фазового дискриминатора 3 (не зависящие от времени в установившемся режиме) поступают на выходной перемножитель 47, формирующий сигнал ошибки zд(φ), пропорциональный фазовому рассогласованию принимаемого ШПС и опорных сигналов частоты ω0. При этом составляющая z2 поступает на сигнальный вход перемножителя 47 непосредственно, а составляющая z1 поступает на опорный вход перемножителя 47 через решающий блок 9, осуществляющий преобразование вида sign(z1) (знаковая функция), благодаря чему исключается влияние цифровой модуляции ШПС D(t)∈[1, -1] на формирование сигнала ошибки zд(φ). Выход решающего блока 9 является выходом корреляционного приемника (выход демодулятора цифрового сообщения D(t)).

Выходной сигнал петлевого фильтра 101, сглаживающего флуктуации сигнала ошибки zд(φ), обусловленные действием шума, используется для управления частотой и фазой опорных сигналов, формируемых подстраиваемым генератором 5 несущей частоты.

Блок 2 кодовой синхронизации работает следующим образом. Сигнал с выхода сумматора 7 поступает на вход перемножителя 48, где перемножается с опорной кодовой последовательностью d(t), вырабатываемой формирователем 17 опорных сигналов. Выходной сигнал перемножителя 48 интегрируется на интервалах, равных периоду Тп повторения ШПС, в результате чего на выходе интегратора 83 образуется сигнал ошибки, поступающий на сигнальный вход перемножителя 49. С помощью перемножителя 49 исключается влияние цифровой модуляции ШПС на формирование сигнала ошибки, пропорционального временному рассогласованию входного ШПС и опорных квадратурных сигналов I0(t) и Q0(t). Достигается это путем подачи на опорный вход перемножителя 49 оценки информационного символа с выхода решающего блока 9. Петлевой фильтр 102 сглаживает флуктуации сигнала ошибки, формируя управляющий сигнал для управляемого тактового генератора 12, вырабатывающего сигнал тактовой частоты fT=1/T, поступающий на вход генератора 14 кода через управляемый фазовращатель 13. Формируемая генератором 14 кода кодовая последовательность поступает на вход синтезатора 15 квадратурных сигналов.

Дешифратор 16, подключенный к генератору 14 кода, формирует синхроимпульсы с частотой повторения Fп=1/Тп для интеграторов 81, 82 и 83 фазового и временного дискриминаторов 3 и 11.

Формирователь 17 опорных сигналов работает следующим образом. На входы знаковых элементов 191 и 192 поступают видеочастотные сигналы I4T(t) и Q4T(t) соответственно с выходов синтезатора 15 квадратурных сигналов. Сигналы I4T(t) и Q4T(t) представляют собой действительную и мнимую составляющие комплексной огибающей ШПС с минимальной частотной манипуляцией (МЧМ). Элементы каждого из сигналов имеют вид полуволны косинуса частоты fT/4, причем каждый k-й элемент сигнала Q4T(t) запаздывает на Т относительно k-го элемента сигнала I4T(t). На выходах знаковых элементов 191 и 192 выделяются кодовые последовательности C(t) и S(t) с элементами длительности 2T, принимающими значения 1 или (-1). Для формирования квадратурных сигналов I(t) и Q(t) с дополнительной BOC-модуляцией необходимо обеспечить временной сдвиг сигнала Q(t) относительно сигнала I(t) на четверть периода Тм модулирующего колебания, вырабатываемого синтезатором 21 частот. Для этого в канал формирования I-сигнала включен элемент 201 задержки на T-TM/4. Элементы 202, 203, 204 и 205 задержки вносят запаздывание на Тм каждый и служат для формирования синхронной и запаздывающей на Тм копий каждого из квадратурных сигналов. Для этого сигналы с выходов элементов 202 и 204 задержки поступают соответственно на перемножители 411 и 414, на другие входы которых подаются косинусная и синусная составляющие модулирующего колебания с соответствующих выходов синтезатора 21 частот. На выходах перемножителей 411 и 414 формируются квадратурные опорные сигналы I0(t) и Q0(t) соответственно, которые подаются на опорные входы перемножителей 43 и 46 фазового дискриминатора 3 блока 1 фазовой синхронизации. Аналогично формируются опережающие на Тм и запаздывающие на Тм копии указанных сигналов: I+(t) и Q+(t) - на выходах перемножителей 410 и 413, I-(t) и Q-(t) - на выходах перемножителей 412 и 415 соответственно. Указанные сигналы поступают в блок 18 устранения неоднозначности.

Кроме того, в блоке 17 формируется опорная кодовая последовательность d0(t) с элементами dk=±1, синхронная с кодом d(t) принимаемого ШПС. Для этого квадратурные опорные сигналы I0(t) и Q0(t) с выходов перемножителей 411 и 414 подаются на знаковые элементы 193 и 194, выделяющие кодовые последовательности С0м(t) и S0м(t), синхронные с кодами См(t) и Sм(t) квадратурных видеочастотных составляющих принимаемого ШПС (с формой элементов в виде полуволны косинуса частоты fм модуляции). Результат перемножения кодов С0м(t) и S0м(t) с выхода перемножителя 416 поступает на перемножитель 417. Опорная кодовая последовательность d0(t) формируется на выходе перемножителя 417, на другой вход которого поступает меандровый сигнал частоты fм, формируемый знаковым элементом 195 из выходного сигнала синтезатора 21 частот (второй выход). С выхода перемножителя 417 кодовая последовательность d0(t) поступает на опорный вход перемножителя 48 временного дискриминатора 11.

Блок 18 устранения неоднозначности (фиг.2) работает следующим образом. На сигнальные входы перемножителей 418 и 420, 419 и 421 поступают квадратурные видеочастотные сигналы I(t) и Q(t) соответственно с выходов перемножителей 41 и 42 блока 1 фазовой синхронизации. На опорные входы перемножителей 418 и 419, 420 и 421 подаются опорные сигналы I+(t) и Q+(t), I-(t) и Q-(t) с выходов перемножителей 410 и 413, 412 и 415 формирователя 17 опорных сигналов. Выходные сигналы перемножителей 414 и 419, 420 и 421 объединяются через вычитатели 62 и 63 соответственно, выходные сигналы которых поступают в интеграторы 84 и 85, аналогичные интеграторам 81, 82 и 83 фазового 3 и временного 11 дискриминаторов. Вычитатели 64 и 65 формируют разности результатов интегрирования наблюдений в фазовом дискриминаторе 3 (выход интегратора 81) и каждом из двух каналов блока 18 устранения неоднозначности: ΔZ1=Z0-Z+ и ΔZ2=Z0-Z-, где Z0, Z+ и Z- - соответственно результат интегрирования в фазовом дискриминаторе 3, «опережающем» и «задержанном» каналах (выходы интеграторов 84 и 85).

Фильтры 221 и 222 осуществляют сглаживание флуктуаций величин ΔZ1 и ΔZ2, обусловленных действием шума. Командный блок 23 формирует одну из трех команд для управления фазовращателем 13: «0» - сдвиг сигнала тактовой частоты не производится, если ΔZ1>0 и ΔZ2>0; «1» - сдвиг сигнала тактовой частоты на Тм в сторону опережения, если ΔZ1>0 и ΔZ2<0; «-1» - сдвиг сигнала тактовой частоты на Тм в сторону запаздывания, если ΔZ1<0 и ΔZ2>0 (благодаря применению фильтров 221 и 222 нижних частот вероятность события ΔZ1<0 и ΔZ2<0 пренебрежимо мала).

Пример реализации синтезатора квадратурных сигналов с использованием накапливающего сумматора (аккумулятора фазы) и постоянного запоминающего устройства для хранения отсчетов квадратурных сигналов приведен в монографии [Цифровые системы фазовой синхронизации / М.И.Жодзишский, С.Ю.Сила-Новицкий, В.А.Прасолов и др. Под ред. М.И.Жодзишского. - М.: Сов. Радио, 1980. - с.55-57].

Предлагаемое устройство позволяет повысить точность кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной манипуляцией и дополнительной BOC-модуляцией благодаря исключению аномальных ошибок, связанных с периодичностью дискриминационной характеристики временного дискриминатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2012 |

|

RU2486683C1 |

Изобретение относится к области радиотехники и может использоваться в широкополосных системах радиосвязи и радионавигации с щумоподобными сигналами с минимальной частотной манипуляцией. Достигаемый технический результат - повышение точности кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной манипуляцией. Устройство содержит блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий семь перемножителей, вычитатель, сумматор, два интегратора и решающий блок, подстраиваемый генератор несущей частоты, петлевой фильтр, блок кодовой синхронизации, который содержит временной дискриминатор, петлевой фильтр, управляемый тактовый генератор, формирователь опорных сигналов, управляемый фазовращатель, генератор кода, дешифратор, синтезатор квадратурных сигналов и блок устранения неоднозначности, который содержит четыре перемножителя, четыре вычитателя, два интегратора, два фильтра нижних частот и командный блок. 2 ил.

Корреляционный приемник шумоподобных сигналов, содержащий блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, третий, четвертый, пятый и шестой перемножители, первый вычитатель и сумматор, первый и второй интеграторы, входы которых подключены к выходам первого вычитателя и сумматора соответственно, решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы третьего и четвертого, пятого и шестого перемножителей объединены соответственно через первый вычитатель и сумматор, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные восьмой перемножитель, сигнальный вход которого подключен к выходу сумматора, третий интегратор и девятый перемножитель, опорный вход которого подключен к выходу решающего блока, а к выходу которого подключен второй петлевой фильтр, последовательно соединенные управляемый фазовращатель, генератор кода и синтезатор квадратурных сигналов, а также дешифратор, входы которого подключены к дополнительным выходам генератора кода, а к выходам которого подключены синхронизирующие входы первого, второго и третьего интеграторов, отличающийся тем, что в блок кодовой синхронизации введены управляемый тактовый генератор, вход которого соединен с выходом второго петлевого фильтра, а выход которого подключен к сигнальному входу управляемого фазовращателя, формирователь опорных сигналов, содержащий последовательно соединенные первый знаковый элемент, вход которого подключен к первому выходу синтезатора квадратурных сигналов, первый, второй и третий элементы задержки, последовательно соединенные второй знаковый элемент, вход которого подключен к второму выходу синтезатора квадратурных сигналов, четвертый и пятый элементы задержки, синтезатор частот, вход которого подключен к выходу управляемого тактового генератора, десятый, одиннадцатый, двенадцатый перемножители, сигнальные входы которых подключены соответственно к выходам первого, второго и третьего элементов задержки, а опорные входы которых соединены с первым выходом синтезатора частот, тринадцатый, четырнадцатый и пятнадцатый перемножители, сигнальные входы которых подключены соответственно к выходам второго знакового элемента, четвертого и пятого элементов задержки, а опорные входы которых соединены со вторым выходом синтезатора частот, третий и четвертый знаковые элементы, входы которых соединены соответственно с объединенными опорными входами третьего и шестого, четвертого и пятого перемножителей блока фазовой синхронизации и подключены соответственно к выходам одиннадцатого и четырнадцатого перемножителей, а выходы которых соединены со входами шестнадцатого перемножителя, к выходу которого подключен семнадцатый перемножитель, другой вход которого подключен к второму выходу синтезатора частот через пятый знаковый элемент, а выход которого соединен с опорным входом восьмого перемножителя временного дискриминатора, блок устранения неоднозначности, содержащий восемнадцатый, девятнадцатый, двадцатый, двадцать первый перемножители, последовательно соединенные второй вычитатель, четвертый интегратор, четвертый вычитатель и первый фильтр нижних частот, последовательно соединенные третий вычитатель, пятый интегратор, пятый вычитатель и второй фильтр нижних частот, а также командный блок, входы которого соединены с выходами первого и второго фильтров нижних частот, а выход которого подключен к управляющему входу управляемого фазовращателя, при этом сигнальные входы восемнадцатого и двадцатого, девятнадцатого и двадцать первого перемножителей попарно объединены и подключены соответственно к выходам первого и второго перемножителей блока фазовой синхронизации, опорные входы восемнадцатого и девятнадцатого, двадцатого и двадцать первого перемножителей подключены соответственно к выходам десятого и тринадцатого, двенадцатого и пятнадцатого перемножителей формирователя опорных сигналов, а выходы восемнадцатого и девятнадцатого, двадцатого и двадцать первого перемножителей объединены соответственно через второй и третий вычитатели, синхронизирующие входы четвертого и пятого интеграторов подключены к выходу дешифратора, другие входы четвертого и пятого вычитателей соединены с выходом первого интегратора блока фазовой синхронизации.

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 2001 |

|

RU2204885C2 |

| СПОСОБ КОМПЕНСАЦИИ ВНУТРИКАНАЛЬНЫХ АДДИТИВНЫХ РАДИОПОМЕХ В ПРИЕМНИКАХ АМПЛИТУДНО-МОДУЛИРОВАННЫХ, ЧАСТОТНО- И ФАЗОМАНИПУЛИРОВАННЫХ РАДИОСИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100903C1 |

| US 6140869 A, 31.10.2000 | |||

| US 5881107 A, 09.03.1999. | |||

Авторы

Даты

2011-10-20—Публикация

2010-09-15—Подача