Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, рис. в пятой строке табл.18.2 на стр.312 в книге Каяцкас А.А. Основы радиоэлектроники: Учеб. пособие для студентов вузов по спец. «Констр. и производство радиоаппаратуры». М.: Высш. шк., 1988 г.), которые реализуют логическую функцию «Эквивалентность», зависящую от двух аргументов - входных двоичных сигналов.

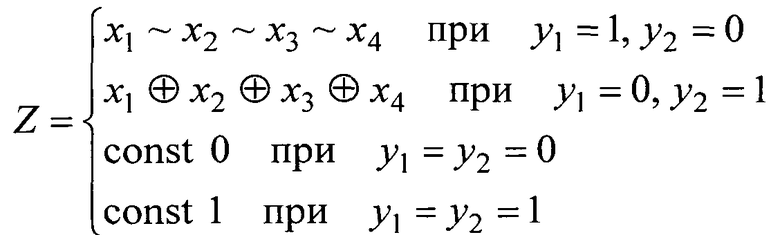

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4, const 0, const 1.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (рис. в шестой строке табл.18.2 на стр.312 в книге Каяцкас А.А. Основы радиоэлектроники: Учеб. пособие для студентов вузов по спец. «Констр. и производство радиоаппаратуры». М.: Высш. шк., 1988 г.), который содержит выход и реализует логическую функцию «Исключающее ИЛИ», зависящую от двух аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4, const 0, const 1.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4, const 0, const 1, где x1, x2, x3, x4∈{0,1} и ~, ⊕ есть соответственно входные двоичные сигналы и символы операций «Эквивалентность», «Исключающее ИЛИ».

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем выход, особенность заключается в том, что в него введены четырнадцать ключей, которые сгруппированы в четыре группы так, что i-я

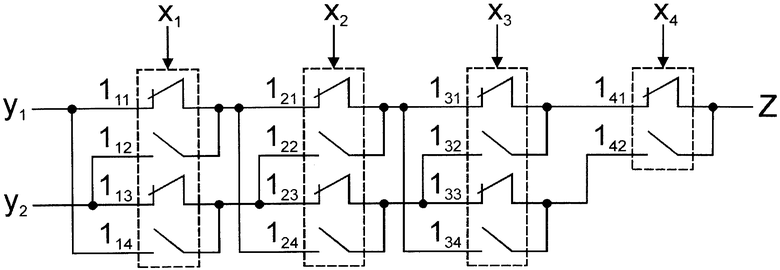

На фигуре представлена схема предлагаемого логического модуля.

Логический модуль содержит четырнадцать ключей 111, …, 142, которые сгруппированы в четыре группы так, что i-я

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый, второй, третий, четвертый информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы x1, x2, x3, x4∈{0,1} и y1, y2∈{0,1}. Если xj=1 либо xj=0

С учетом данных, приведенных в таблице, имеем

где ~ и ⊕ есть символы операций «Эквивалентность» и «Исключающее ИЛИ».

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4⊕, const 0, const 1, где x1, x2, x3, x4∈{0,1} и ~, ⊕ есть соответственно входные двоичные сигналы и символы операций «Эквивалентность», «Исключающее ИЛИ».

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2011 |

|

RU2440601C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2011 |

|

RU2446462C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2012 |

|

RU2497181C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2383052C2 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2710878C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2004 |

|

RU2260205C1 |

| РЕЛЯТОРНЫЙ КОММУТАТОР АНАЛОГОВЫХ СИГНАЛОВ С АДРЕСНЫМ УПРАВЛЕНИЕМ | 2004 |

|

RU2256220C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2005 |

|

RU2292586C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2011 |

|

RU2445678C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2013 |

|

RU2518664C1 |

Изобретение предназначено для реализации логических функций и может быть использовано в системах цифровой вычислительной техники как средство обработки двоичных кодов. Техническим результатом является расширение функциональных возможностей устройства за счет реализации любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4, const 0, const 1. Устройство содержит четырнадцать ключей (111, …, 142). 1 ил., 1 табл.

Логический модуль, предназначенный для реализации любой из логических функций x1~x2~x3~x4, x1⊕x2⊕x3⊕x4, const 0, const 1, содержащий выход и отличающийся тем, что в него введены четырнадцать ключей, которые сгруппированы в четыре группы так, что i-я  и четвертая группы содержат соответственно четыре и два ключей, причем четные и нечетные ключи образованных групп выполнены соответственно замыкающими и размыкающими, в каждой группе выход нечетного ключа соединен с выходом последующего ключа, в i-й группе входы первого и второго ключей соединены соответственно с входами четвертого и третьего ключей, выходы первого и третьего ключей i-й группы соединены соответственно с входами первого и второго ключей (i+1)-й группы, а выход первого ключа четвертой и входы первого, второго ключей первой групп соединены соответственно с выходом и первым, вторым настроечными входами логического модуля, j-й

и четвертая группы содержат соответственно четыре и два ключей, причем четные и нечетные ключи образованных групп выполнены соответственно замыкающими и размыкающими, в каждой группе выход нечетного ключа соединен с выходом последующего ключа, в i-й группе входы первого и второго ключей соединены соответственно с входами четвертого и третьего ключей, выходы первого и третьего ключей i-й группы соединены соответственно с входами первого и второго ключей (i+1)-й группы, а выход первого ключа четвертой и входы первого, второго ключей первой групп соединены соответственно с выходом и первым, вторым настроечными входами логического модуля, j-й  информационный вход которого соединен с управляющим входом всех ключей j-й группы.

информационный вход которого соединен с управляющим входом всех ключей j-й группы.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2012 |

|

RU2497181C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303283C1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1288686A1 |

| JP 61127227 A, 14.06.1986 | |||

| US 8255440 B1, 28.08.2012 | |||

Авторы

Даты

2015-04-10—Публикация

2013-12-03—Подача