Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, патент РФ 2262733, кл. G06F 7/00, 2005 г.), которые реализуют любую из трех простых симметричных булевых функций x1∨x2∨x3, х1х2∨x1x3∨x2x3, х1х2х3, зависящих от трех аргументов - входных двоичных сигналов х1, х2, x3∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация функции х1⊕х2⊕х3.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (патент РФ 2249844, кл. G06F 7/38, 2005 г.), который содержит два настроечных, три информационных входа, выход и реализует любую из трех простых симметричных булевых функций x1∨x2∨x3, х1х2∨x1x3∨x2x3, х1х2х3,, зависящих от трех аргументов - входных двоичных сигналов х1, х2, x3∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация функции х1⊕х2⊕х3.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов, либо сложения по модулю 2 тех же трех аргументов.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем выход, два настроечных и три информационных входа, особенность заключается в том, что в него введены шесть замыкающих и шесть размыкающих ключей, которые сгруппированы в три группы так, что i-я ( ) группа содержит 4-i замыкающих и 4-i размыкающих ключей, в каждой группе выходы одноименных замыкающего и размыкающего ключей объединены, в j-й (

) группа содержит 4-i замыкающих и 4-i размыкающих ключей, в каждой группе выходы одноименных замыкающего и размыкающего ключей объединены, в j-й ( ) группе вход предыдущего размыкающего ключа соединен с входом последующего замыкающего ключа, управляющий вход всех ключей первой группы и управляющий вход всех ключей второй группы соединены соответственно с входом первого замыкающего и входом третьего размыкающего ключей первой группы, выход первого замыкающего ключа предыдущей группы соединен с входом первого замыкающего ключа последующей группы, а выходы второго, третьего размыкающих ключей первой группы и выход второго размыкающего ключа второй группы соединены соответственно с входами первого, второго размыкающих ключей второй группы и входом первого размыкающего ключа третьей группы, подсоединенного выходом к выходу логического модуля, i-й информационный и j-й настроечный входы которого соединены соответственно с управляющим входом всех ключей i-й группы и входом j-го размыкающего ключа первой группы.

) группе вход предыдущего размыкающего ключа соединен с входом последующего замыкающего ключа, управляющий вход всех ключей первой группы и управляющий вход всех ключей второй группы соединены соответственно с входом первого замыкающего и входом третьего размыкающего ключей первой группы, выход первого замыкающего ключа предыдущей группы соединен с входом первого замыкающего ключа последующей группы, а выходы второго, третьего размыкающих ключей первой группы и выход второго размыкающего ключа второй группы соединены соответственно с входами первого, второго размыкающих ключей второй группы и входом первого размыкающего ключа третьей группы, подсоединенного выходом к выходу логического модуля, i-й информационный и j-й настроечный входы которого соединены соответственно с управляющим входом всех ключей i-й группы и входом j-го размыкающего ключа первой группы.

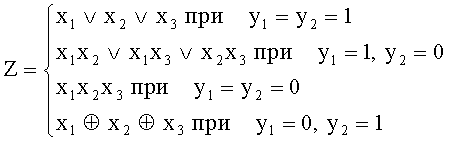

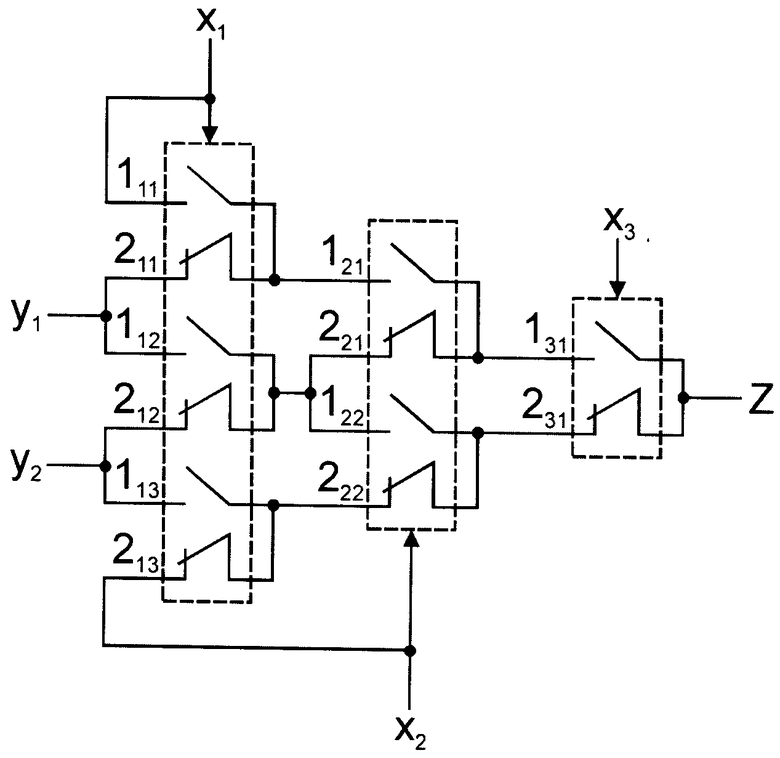

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит шесть замыкающих и шесть размыкающих ключей 111, …, 131 и 211, …, 231, которые сгруппированы в три группы так, что i-я ( ) группа содержит ключи 1i1, …, 1i(4-i) и 2i1, …, 2i(4-i), в каждой группе выходы одноименных замыкающего и размыкающего ключей объединены, в j-й (

) группа содержит ключи 1i1, …, 1i(4-i) и 2i1, …, 2i(4-i), в каждой группе выходы одноименных замыкающего и размыкающего ключей объединены, в j-й ( ) группе вход предыдущего размыкающего ключа соединен с входом последующего замыкающего ключа, управляющие входы ключей 111, 112, 113, 211, 212, 213 и 121, 122, 221, 222 соединены соответственно с входами ключей 111 и 213, выходы ключей 212, 213 и 222 соединены соответственно с входами ключей 221, 222 и 231, а выходы ключей 1j1 и 131 соединены соответственно с входом ключа 1(j+1)1 и выходом логического модуля, i-й информационный и j-й настроечный входы которого соединены соответственно с управляющим входом всех ключей i-й группы и входом ключа 21j.

) группе вход предыдущего размыкающего ключа соединен с входом последующего замыкающего ключа, управляющие входы ключей 111, 112, 113, 211, 212, 213 и 121, 122, 221, 222 соединены соответственно с входами ключей 111 и 213, выходы ключей 212, 213 и 222 соединены соответственно с входами ключей 221, 222 и 231, а выходы ключей 1j1 и 131 соединены соответственно с входом ключа 1(j+1)1 и выходом логического модуля, i-й информационный и j-й настроечный входы которого соединены соответственно с управляющим входом всех ключей i-й группы и входом ключа 21j.

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый, второй, третий информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы х1, х2, x3∈{0,1} и y1, y2∈{0,1}. Если хi=1 либо xi=0 ( ), то ключи 1i1, …, 1i(4-i) соответственно замкнуты либо разомкнуты, а ключи 2i1, …, 2i(4-i) соответственно разомкнуты либо замкнуты. Следовательно, сигнал на выходе предлагаемого логического модуля определяется выражением

), то ключи 1i1, …, 1i(4-i) соответственно замкнуты либо разомкнуты, а ключи 2i1, …, 2i(4-i) соответственно разомкнуты либо замкнуты. Следовательно, сигнал на выходе предлагаемого логического модуля определяется выражением

,

,

где ∨, •, - есть символы операций ИЛИ, И, НЕ. Таким образом, предлагаемый логический модуль будет воспроизводить операцию

.

.

При этом он, как и прототип, имеет два настроечных входа и использует константную настройку.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов, либо сложения по модулю 2 тех же трех аргументов. Дополнительным достоинством предлагаемого логического модуля является более однородный по сравнению с прототипом аппаратурный состав.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2004 |

|

RU2260205C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303282C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2011 |

|

RU2445697C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303283C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2004 |

|

RU2262733C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2005 |

|

RU2281545C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2012 |

|

RU2504826C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2005 |

|

RU2286594C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2475814C1 |

Изобретение предназначено для реализации симметричных логических функций и может быть использовано в системах цифровой вычислительной техники как средство преобразования кодов. Техническим результатом является обеспечение реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов, либо сложения по модулю 2 тех же трех аргументов. Логический модуль содержит шесть замыкающих и шесть размыкающих ключей. 1 ил.

Логический модуль, предназначенный для реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов, либо сложения по модулю 2 тех же трех аргументов, содержащий выход, два настроечных и три информационных входа, отличающийся тем, что в него введены шесть замыкающих и шесть размыкающих ключей, которые сгруппированы в три группы так, что i-я (

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303283C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2003 |

|

RU2249844C2 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2004 |

|

RU2262733C1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1990 |

|

SU1789978A1 |

| JP 61127227 A, 14.06.1986 | |||

| US 2008021942 A1, 24.01.2008. | |||

Авторы

Даты

2013-10-27—Публикация

2012-07-03—Подача