Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, патент РФ 2249844, кл. G06F 7/38, 2005 г.), которые реализуют любую из трех простых симметричных булевых функций τ1=x1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относится ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из трех фундаментальных симметричных булевых функций

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (патент РФ 2262733, кл. G06F 7/00, 2005 г.), который содержит выход и реализует любую из трех простых симметричных булевых функций τ1=x1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из трех фундаментальных симметричных булевых функций

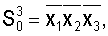

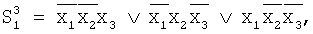

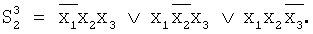

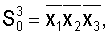

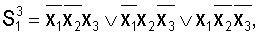

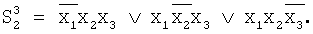

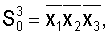

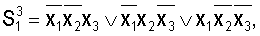

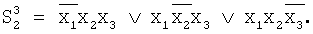

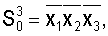

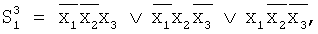

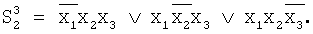

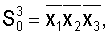

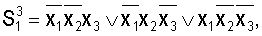

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из трех простых симметричных булевых функций τ1=x1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3 и из трех фундаментальных симметричных булевых функций

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем выход, особенность заключается в том, что в него введены первый, третий, пятый ключи, выполненные замыкающими, и второй, четвертый, шестой ключи, выполненные размыкающими, причем вход пятого, вход и выход шестого ключей соединены соответственно с объединенными выходами первого, второго, объединенными выходами третьего, четвертого ключей и объединенными выходом пятого ключа, выходом логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления первого-четвертого, входу управления пятого, шестого ключей и входу первого, входу четвертого ключей, объединенным входам второго, третьего ключей.

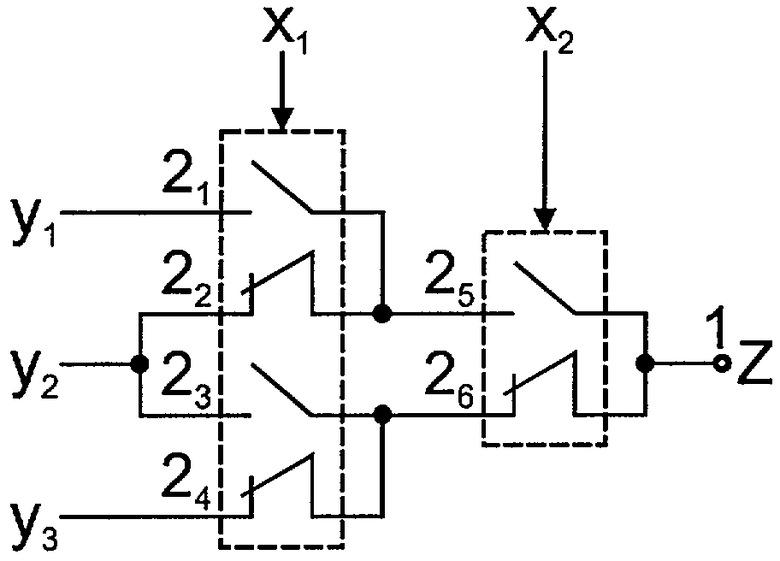

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит выход 1 и ключи 21, ..., 26, причем ключи 21, 23, 25 и 22, 24, 26 выполнены соответственно замыкающими и размыкающими, вход ключа 25, вход и выход ключа 26 соединены соответственно с объединенными выходами ключей 21, 22, объединенными выходами ключей 23, 24 и объединенными выходом ключа 25, выходом 1 логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления ключей 21, ..., 24, входу управления ключей 25, 26 и входу ключа 21, входу ключа 24, объединенным входам ключей 22, 23.

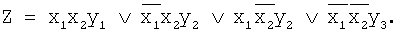

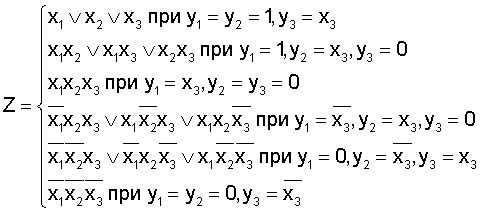

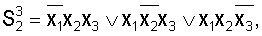

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый, второй информационные и первый, второй, третий настроечные входы подаются соответственно двоичные сигналы х1, х2∈{0,1} и y1, y2, y3∈{0,1}. Если x1=1 (x1=0), то ключи 21, 23 замкнуты (разомкнуты), а ключи 22, 24 разомкнуты (замкнуты). Если x2=1 (x2=0), то ключ 25 замкнут (разомкнут), а ключ 26 разомкнут (замкнут). Тогда сигнал на выходе 1 определяется выражением

Таким образом, предлагаемый модуль будет воспроизводить операцию

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию любой из трех простых симметричных булевых функций τ1=x1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3 и из трех фундаментальных симметричных булевых функций

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2417404C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2518669C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2004 |

|

RU2262733C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2005 |

|

RU2281545C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2284567C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2005 |

|

RU2286594C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2324219C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2383052C2 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из трех простых симметричных булевых функций τ1=х1∨х2∨х3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3 и из трех фундаментальных симметричных булевых функций

Для этого в логическом модуле, содержащем выход, особенность заключается в том, что в него введены первый, третий, пятый ключи, выполненные замыкающими, и второй, четвертый, шестой ключи, выполненные размыкающими, причем вход пятого, вход и выход шестого ключей соединены соответственно с объединенными выходами первого, второго, объединенными выходами третьего, четвертого ключей и объединенными выходом пятого ключа, выходом логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления первого-четвертого, входу управления пятого, шестого ключей и входу первого, входу четвертого ключей, объединенным входам второго, третьего ключей. 1 ил.

Для этого в логическом модуле, содержащем выход, особенность заключается в том, что в него введены первый, третий, пятый ключи, выполненные замыкающими, и второй, четвертый, шестой ключи, выполненные размыкающими, причем вход пятого, вход и выход шестого ключей соединены соответственно с объединенными выходами первого, второго, объединенными выходами третьего, четвертого ключей и объединенными выходом пятого ключа, выходом логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления первого-четвертого, входу управления пятого, шестого ключей и входу первого, входу четвертого ключей, объединенным входам второго, третьего ключей. 1 ил.

Логический модуль, предназначенный для реализации любой из трех простых симметричных булевых функций τ1=x1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3 и из трех фундаментальных симметричных булевых функций

содержащий выход, отличающийся тем, что в него введены первый, третий, пятый ключи, выполненные замыкающими, и второй, четвертый, шестой ключи, выполненные размыкающими, причем вход пятого, вход и выход шестого ключей соединены соответственно с объединенными выходами первого, второго, объединенными выходами третьего, четвертого ключей и объединенными выходом пятого ключа, выходом логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления первого-четвертого, входу управления пятого, шестого ключей и входу первого, входу четвертого ключей, объединенным входам второго, третьего ключей.

содержащий выход, отличающийся тем, что в него введены первый, третий, пятый ключи, выполненные замыкающими, и второй, четвертый, шестой ключи, выполненные размыкающими, причем вход пятого, вход и выход шестого ключей соединены соответственно с объединенными выходами первого, второго, объединенными выходами третьего, четвертого ключей и объединенными выходом пятого ключа, выходом логического модуля, подсоединенного первым, вторым информационными и первым, третьим, вторым настроечными входами соответственно к входу управления первого-четвертого, входу управления пятого, шестого ключей и входу первого, входу четвертого ключей, объединенным входам второго, третьего ключей.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2004 |

|

RU2262733C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2003 |

|

RU2249844C2 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2004 |

|

RU2264645C1 |

| Управляемый арифметический модуль | 1985 |

|

SU1309017A1 |

| JP 61127227, 14.06.1986. | |||

Авторы

Даты

2007-07-20—Публикация

2006-03-21—Подача