Заявляемое техническое решение относится к области телекоммуникаций, а более конкретно - к устройствам для преобразования цифровых сигналов в аналоговые сигналы, и может найти применение в системах обработки и передачи данных.

Широкое распространение устройств, работающих с данными, представленными в цифровом формате, привело к необходимости создания инструментов для преобразования такого формата в ранее использовавшийся и часто более удобный аналоговый формат и наоборот.

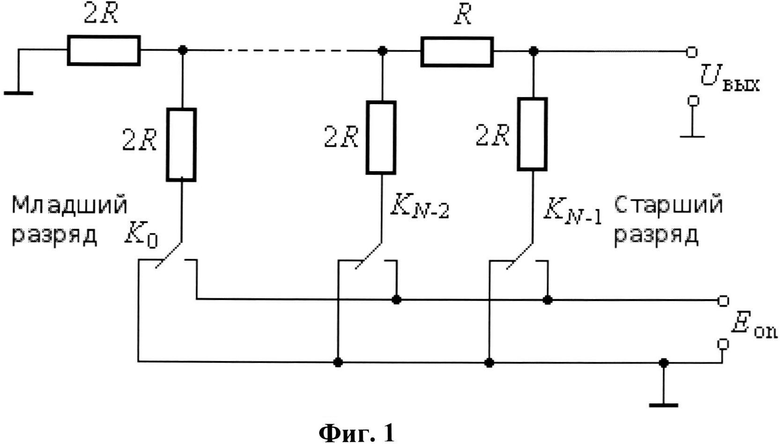

Из уровня техники известны различные подходы к решению этой задачи. В частности, следует упомянуть технические решения, описанные, например, в патенте РФ №2240649 [1], в котором предложено устройство преобразования аналогового сигнала в цифровой, содержащее делитель опорного напряжения на основе резисторной матрицы R-2R, блок ключей, аналоговый сумматор, компаратор напряжения, регистр, генератор тактовых импульсов, триггер, формирователь кодов. Обратное преобразование (цифро-аналоговое) на основе резисторных матриц R-2R описано в патентах США №5,008,676 [2], 7,336,211 [3] и 7,468,686 [4]. Примечательно, что основные идеи этих технических решений можно найти в статье B.D. Smith, Coding by feedback methods. Proceedings of the IRE, Volume: 41, Issue: 8, August 1953, pp.1053-1058 [5]. В этой статье описана простейшая резистивная лестница R-2R (см. Фиг.1). Предполагается, что на вход ЦАП приходит цифровой код [KN-1, K0] в двоичной кодировке, где KN-1 - старший бит, а K0 - младший разряд. В идеале, биты переключается между 0 вольт (логический 0) и Еоп (логические 1). Благодаря конфигурации резистивной лестницы R-2R каждый бит вносит взвешенный вклад в выходное напряжение Uвых. В представленной схеме показаны 5 битов (биты 4-0), что дает (25) или 32 возможных аналоговых уровней напряжения на выходе. В зависимости от того, какой бит установлен в единицу, а какой в ноль, выходное напряжение будет соответствующим ступенчатым значениям от 0 вольт и до Еоп минус значение минимального шага. Фактическое значение Еоп (и 0 В) зависит от типа технологии, используемой для генерации цифровых сигналов.

Эти идеи были реализованы в патенте США №3755807 [6], описана точная резистивная лестница с использованием ключей на полевых транзисторах. Сопротивления открытого канала полевых транзисторов соединены друг с другом так, что каждый бит входного сигнала вносит взвешенный вклад в выходное напряжение, благодаря чему совокупное сопротивление указанной лестницы производит точное цифро-аналоговое преобразование. Существенно, что значения связанных сопротивлений транзисторов таковы, что схема реализуема в интегральной схемотехнике. Благодаря использованию «зеркальной» схемы соединения переключателей, вредное воздействие токов утечки сведено к минимуму.

Недостатком указанного решения является то, что для получения амплитуды выходного сигнала, которая не совпадает с напряжением питания, нам необходим дополнительный источник тока (Еоп) или преобразователь напряжения на выходе ЦАП. Патент США №3755807 [6] выбран в качестве прототипа заявляемого изобретения.

Задачей, на решение которой направлено заявляемое изобретение, состоит в разработке более технологичной конструкции цифро-аналогового преобразователя, не нуждающегося ни в дополнительных источниках тока, ни в преобразователе напряжения на выходе, ни в дополнительных уровнях напряжения.

Технический результат достигается за счет разработки усовершенствованной схемы цифро-аналогового преобразователя, содержащего первую резистивную лестницу, где резисторы соединены с ключами, которые управляются входным сигналом в двоичной кодировке, и дополнительную (вторую) резистивную лестницу, в которой резисторы соединены с ключами, которые управляются инвертированным входным сигналом в двоичной кодировке, и обе лестницы соединены между собой таким образом, что резисторы в перемычках включены параллельно; отношение сопротивлений первой и второй лестницы выбирается в соответствии с выражением: (m+1)/(m-1), где m - отношение напряжения питания к двойной амплитуде (размаху) выходного сигнала.

В альтернативном варианте реализации заявляемого изобретения функцию ключей выполняют инверторы. При этом инвертированные сигналы К [N-1:0] связаны с сопротивлениями 2r (т.е. второй резистивной лестницы), а усиленные сигналы K [N-1:0] связаны с 2R (т.е. сопротивлениями первой резистивной лестницы).

Для лучшего понимания существа заявляемого изобретения оно поясняется далее с привлечением графических материалов.

Фиг.1 - Прототип.

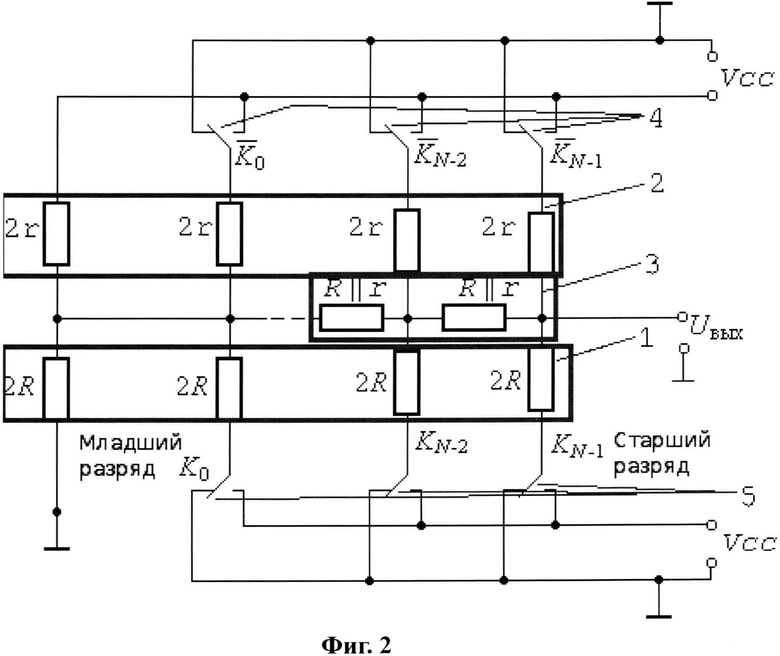

Фиг.2 - Схема согласно заявляемому изобретению.

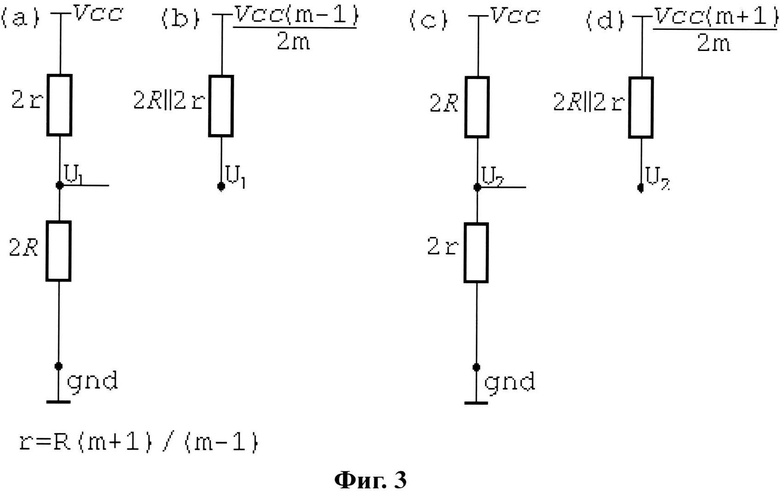

Фиг.3 - Принцип работы схемы заявляемого изобретения.

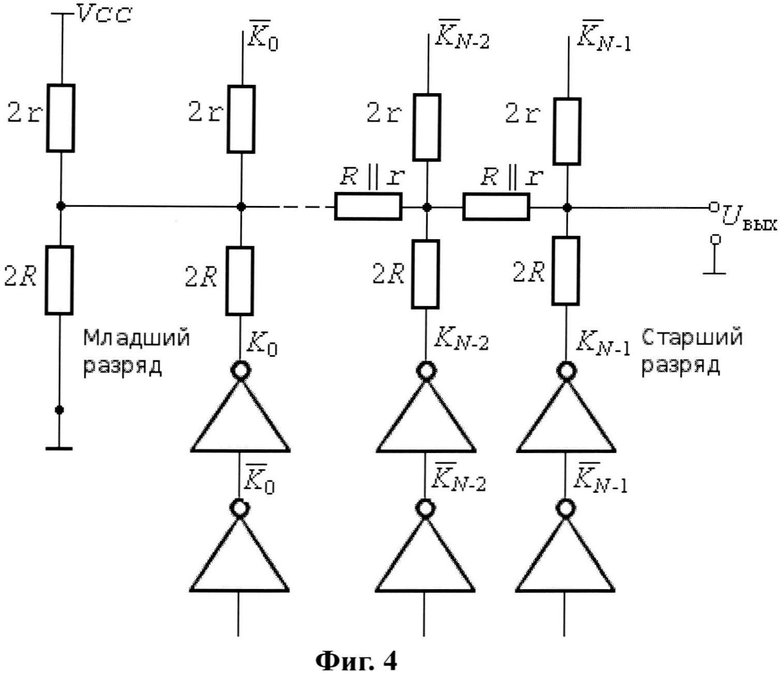

Фиг.4 - Предпочтительный вариант реализации заявляемого изобретения.

Схема, предложенная в заявляемом изобретении (Фиг.2), состоит из двух резистивных лестниц R-2R и r-2r. Резистивная лестница R-2R, обозначенная как 1, управляется входным двоичным кодом K [N-1:0]. Резистивная лестница r-2r, обозначенная как 2, управляется инвертированным входным двоичным кодом K [N-1:0]. Упомянутые резистивные лестницы 1 и 2 соединены параллельным подключением резисторов r и R, обозначенных на схеме как 3. Соотношения сопротивлений резисторов r и R зависит от желаемого усиления ЦАП. Если амплитуда выходного сигнала Vcc/2m, то r=R(m+1)/(m-1). Общий уровень напряжения будет Vcc/2. Таким образом, схема согласно заявляемому изобретению состоит из N+1 резисторов R, где N является разрядностью входной шины, N+1 резисторов r, N-1 резисторов Rr/(R+r). N резисторов 2R связаны с N ключами, обозначенными на схеме как 5, каждый из которых управляется входным двоичным кодом K [N-1:0]. N резисторов 2 г связаны с N ключами 4, каждый из которых управляется инвертированным входным двоичным кодом К [N-1:0].

Принцип формирования лестницы показан на Фиг.3. Цепи (а) и (b) будут эквивалентны, если r=R(m+1)/(m-1). То есть из равенства напряжений в узле U1 в обеих цепях следует равенство тока через резистор 2R||2r сумме токов через резисторы 2R и 2r. Действительно, из равенства токов следует: (Vcc-U1)/2r-U1/2R=(Vcc(m-1)-2mU1)(R+r)/4mRr. После несложных преобразований получаем: r=R(m+1)/(m-1).

Аналогично, цепи (с) и (d) будут эквивалентны, если r=R(m+1)/(m-1). Таким образом, в новой цепи (а) и (с), вместо исходных уровней мы используем дополнительный резистор r=R(m+1)/(m-1).

На Фиг.4 представлен предпочтительный вариант реализации заявляемого изобретения. При этом ключи заменены на инверторы. Инвертированные сигналы K [N-1:0] связаны с сопротивлениями второй резистивной лестницы (2r). Усиленные сигналы K [N-1:0] связаны с сопротивлениями первой резистивной лестницы (2R).

Заявляемое изобретение может быть использовано в системах передачи данных в качестве части аналого-цифровых преобразователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2568323C2 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2824647C1 |

| Цифро-аналоговый перемножитель | 1975 |

|

SU598233A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU1035788A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ УРОВНЯ ГРОМКОСТИ | 2014 |

|

RU2562371C1 |

| Преобразователь "код-напряжение | 1978 |

|

SU777811A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Стабилизированный источник тока с изменяющейся полярностью | 1984 |

|

SU1176314A1 |

Изобретение относится к области телекоммуникаций и может быть использовано для преобразования цифровых сигналов в аналоговые сигналы. Техническим результатом является повышение технологичности конструкции преобразователя. Устройство содержит первую резистивную лестницу, образованную резисторами, соединенными с ключами, управляющимися входным сигналом в двоичной кодировке, вторую резистивную лестницу, образованную резисторами, соединенными с ключами, управляющимися инвертированным входным сигналом в двоичной кодировке, причем обе лестницы соединены между собой таким образом, что резисторы в перемычках включены параллельно; отношение сопротивлений первой и второй лестницы выбрано в соответствии с выражением: (m+1)/(m-1), где m - отношение напряжения питания к двойной амплитуде выходного сигнала. 1 з.п. ф-лы, 4 ил.

1. Цифро-аналоговый преобразователь, содержащий первую резистивную лестницу, образованную резисторами, соединенными с ключами, управляющимися входным сигналом в двоичной кодировке, отличающийся тем, что дополнительно содержит вторую резистивную лестницу, образованную резисторами, соединенными с ключами, управляющимися инвертированным входным сигналом в двоичной кодировке, причем обе лестницы соединены между собой таким образом, что резисторы в перемычках включены параллельно; отношение сопротивлений первой и второй лестницы выбрано в соответствии с выражением: (m+1)/(m-1), где m - отношение напряжения питания к двойной амплитуде выходного сигнала.

2. Цифро-аналоговый преобразователь по п.1, отличающийся тем, что функция ключей выполняется инверторами, при этом инвертированные сигналы связаны с сопротивлениями второй резистивной лестницы, а усиленные сигналы соединены с сопротивлениями первой резистивной лестницы.

| US 3755807 A, 28.08.1973 | |||

| Экономайзер | 0 |

|

SU94A1 |

| US 2007132622 A1, 14.06.2007 | |||

| US 5008676 A, 16.04.1991 | |||

| Умножающий цифро-аналоговый преобразователь | 1985 |

|

SU1312738A1 |

Авторы

Даты

2015-04-10—Публикация

2013-07-08—Подача