Изобретение относится к аналого-цифровой технике и может быть использовано в устройствах преобразования цифровых величин - кодов в пропорциональные аналоговые величины.

Наиболее близким по технической сущности является выбранный в качестве прототипа цифроаналоговый преобразователь с поразрядно взвешенными резисторами [Т.С. Ратхор. Цифровые измерения. Методы и схемотехника. Москва: Техносфера, 2004. - 376 с., рис. 5.13, стр. 178], содержащий источник постоянного опорного напряжения, электронные ключи, управляющие входы которых образуют вход для подачи цифрового кода, резистивную матрицу и сумматор токов на операционном усилителе, выход которого образует выход цифроаналогового преобразователя.

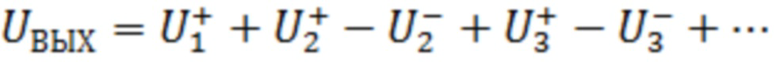

Функциональная схема цифроаналогового преобразователя-прототипа приведена на фиг. 1.

Схема содержит:

1. Источник опорного напряжения E0;

2. N поразрядно взвешенных резисторов R, 2R,…, 2N-1R, объединенных с одной стороны в одну точку и подключенных к источнику опорного напряжения. Другие концы взвешенных резисторов подключены к входам ключей;

3. N переключающих ключей, управляемых входным цифровым двоичным кодом ANAN-1…A1, где AN - старший разряд. Один из выходов каждого ключа присоединен к общей шине, подключенной к инвертирующему входу операционного усилителя. Другой выход каждого ключа присоединен к общей заземленной шине, подключенной к неинвертирующему входу операционного усилителя;

4. Операционный усилитель, включенный по схеме инвертирующего усилителя с обратной связью, образуемой резистором Roc.

Схема работает следующим образом.

Каждый i-й ключ подключает соответствующее сопротивление 2N-iR взвешенных резисторов к общей шине, присоединенной к инвертирующему входу операционного усилителя, когда значение Ai=1, или подключает это сопротивление к заземленной общей шине, когда значение Ai = 0.

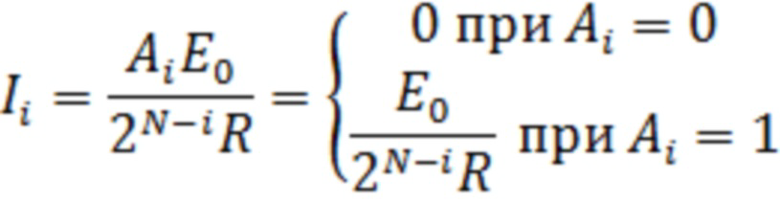

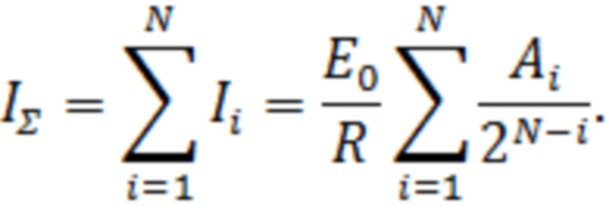

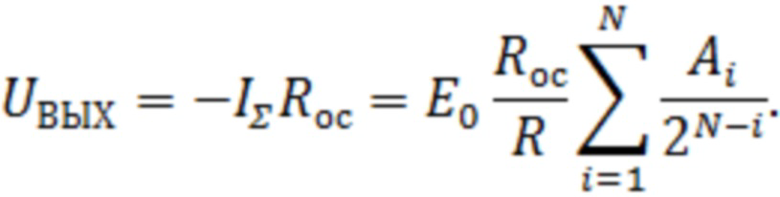

Таким образом, с помощью матрицы, состоящей из взвешенных резисторов R-2N-1R, формируется набор взвешенных токов Ii, величины которых будут возрастать с увеличением веса соответствующего разряда. Величина Ii взвешенного тока определяется формулой

В результате, общий ток I∑ на входе операционного усилителя будет равен сумме токов Ii, протекающих через замкнутые ключи, и пропорционален значению входного кода

Напряжение UВЫХ на выходе ЦАП также будет пропорционально значению входного кода

Недостатком описанного цифроаналогового преобразователя-прототипа является сложность построения ЦАП большой разрядности ввиду высокого значения верхнего номинала взвешенных резисторов R-2N-1R, а также невозможность получения двухполярного напряжения на выходе устройства при одной полярности опорного напряжения.

Задачей изобретения является возможность увеличения разрядности ЦАП с поразрядно взвешенными резисторами и получение двухполярного напряжения на выходе устройства при одной полярности опорного напряжения.

Технический результат заключается в уменьшении верхнего диапазона номиналов взвешенных резисторов, что позволит реализовать более высокоразрядный ЦАП, а также возможность инверсии выходного напряжения для получения двухполярного напряжения на выходе устройства при одной полярности опорного напряжения.

Технический результат достигается тем, что в цифроаналоговом преобразователе, содержащем N-1 взвешенных резисторов с диапазоном сопротивлений

R, R, 2R, 4R, …, 2N-3R,

где N - разрядность ЦАП, N переключающих ключей, управляемых входным цифровым двоичным кодом ANAN-1…A1, где AN - старший разряд N-разрядного цифроаналогового преобразователя, усилитель, предусмотрены новые элементы и связи - в качестве усилителя используется мультидифференциальный операционный усилитель с N-1 входными дифференциальными каскадами. Все взвешенные резисторы соединены последовательно, начиная с меньшего и заканчивая максимальным, в виде резистивного делителя напряжения. К концам резистивного делителя подключено опорное напряжение E0, при этом подключение при наименьшем сопротивлении R заземлено. Резистивный делитель имеет N выводов по одному, начиная от узла соединения двух наименьших сопротивлений R и R. В точке присоединения источника опорного напряжения с наибольшим сопротивлением 2N-3R имеется 2 вывода. Каждый вывод присоединен к одному из выходов управляемого переключающего ключа. Вторые выходы всех ключей подключены общей заземленной шине. Подключение осуществляется таким образом, чтобы при подаче управляющего сигнала, соответствующего логической 1, вход каждого ключа подключатся к выходу, присоединенного к соответствующему выводу резистивного делителя. При подаче управляющего сигнала, соответствующего логическому 0, вход каждого ключа подключатся к выходу, присоединенного к заземленной общей шине. Входы N-1 ключей начиная с первого, подключенного к узлу соединения двух наименьших сопротивлений R и R, и кончая N-1 ключом, подключенным к точке присоединения источника опорного напряжения с наибольшим сопротивлением 2N-3R, присоединены к каждому из N-1 неинвертирующих входов мультидифференциального операционного усилителя с N-1 входными дифференциальными каскадами. Инвертирующий вход первого дифференциального каскада мультидифференциального операционного усилителя образует единичную обратную связь с его выходом. Инвертирующие входы со второго по N-3 дифференциальный каскад заземлены. Инвертирующие входы N-2 и N-1 дифференциальных каскадов объединены и подключены к входу N-ого ключа.

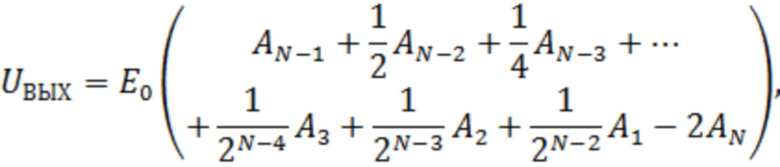

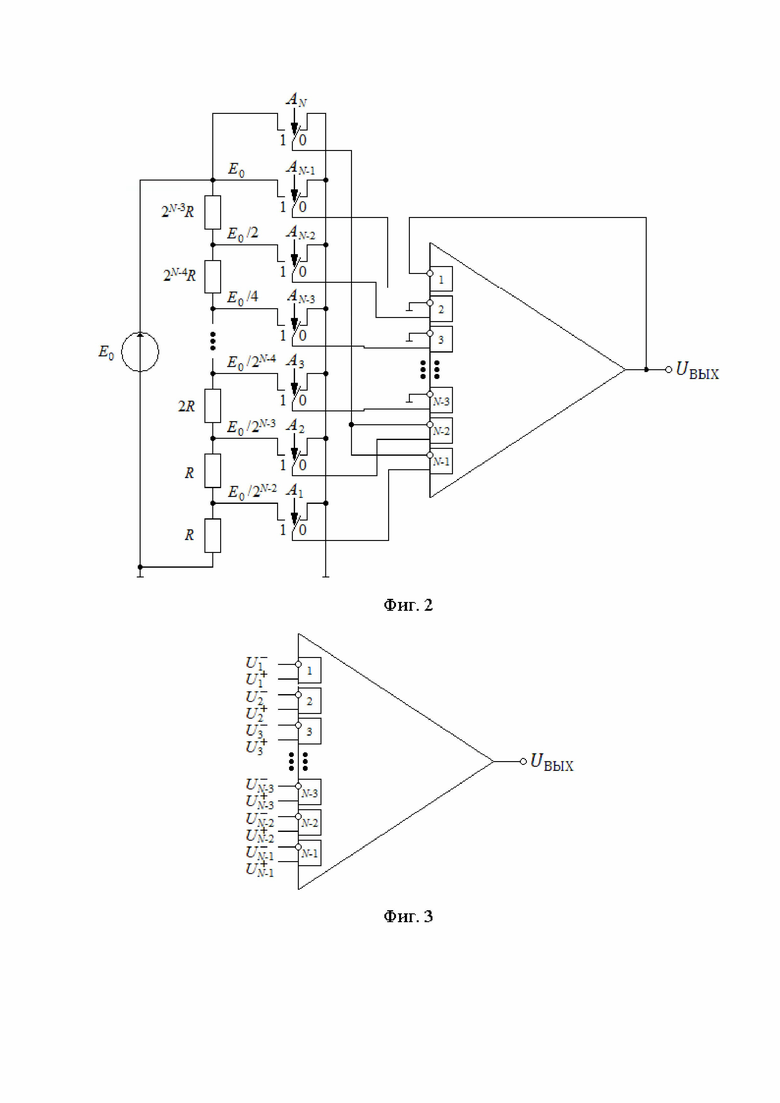

Схема цифроаналогового преобразователя представлена на фиг. 2.

Цифроаналоговый преобразователь содержит:

1. Источник опорного напряжения E0;

2. Резистивный делитель, содержащий N-1 резистор, сопротивления которых принимают следующие значения R, R, 2R, 4R, …, 2N-3R, где N - разрядность ЦАП;

3. N переключающих ключей, управляемых двоичным кодом ANAN-1…A1;

4. Мультидифференциальный операционный усилитель с N-1 входным дифференциальным каскадом. Инвертирующий вход первого дифференциального каскада мультидифференциального операционного усилителя образует единичную обратную связь с его выходом.

Цифроаналоговый преобразователь работает следующим образом.

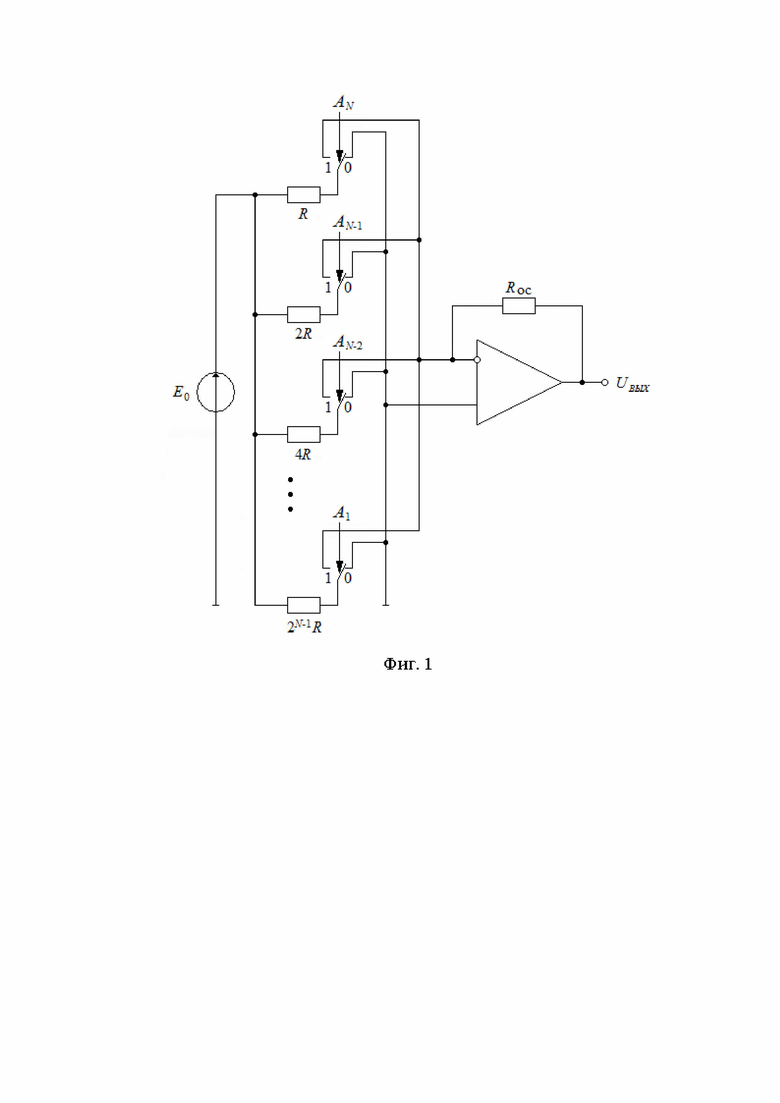

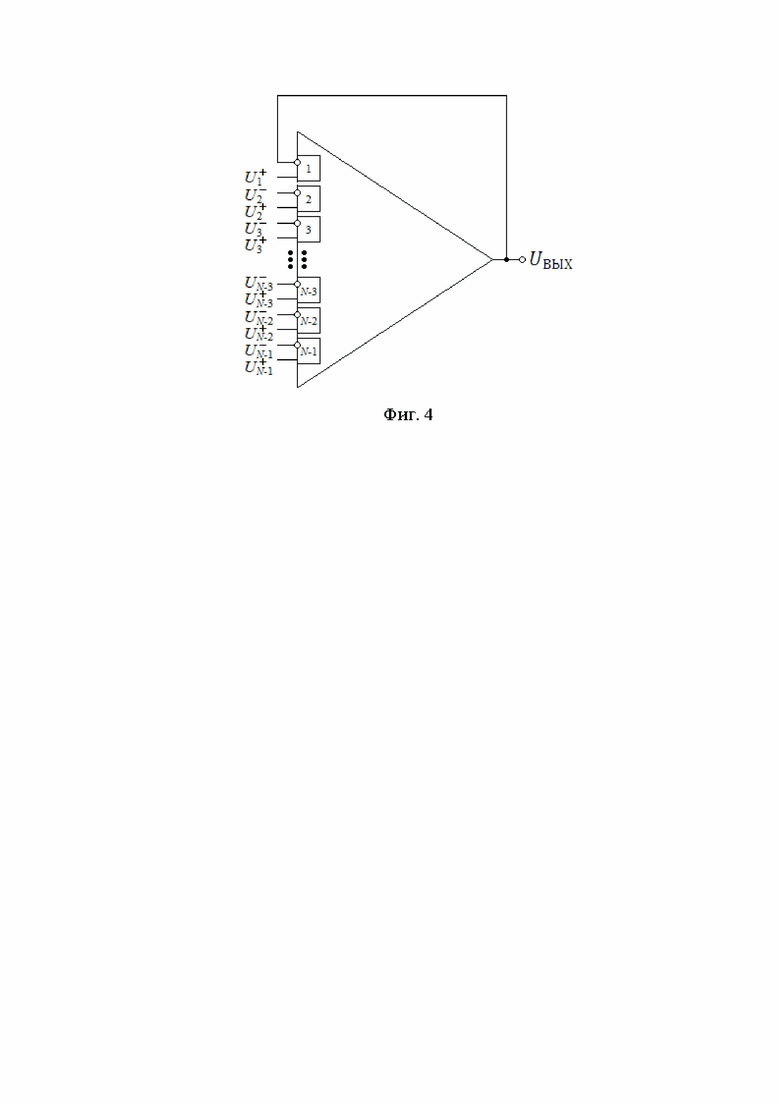

Структурная схема мультидифференциального усилителя с N-1 входными дифференциальными каскадами приведена на фиг. 3.

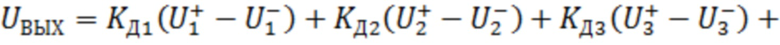

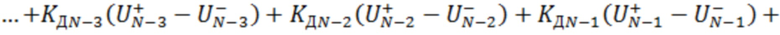

На основании исследований, проведенных в работах [Крутчинский С.Г., Титов А.Е. Оптимизация структур инструментальных усилителей с мультидифференциальными операционными усилителями // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). - 2014. - № 3. - С. 9-14.; Федоров, С. В. Структурный синтез схем инструментальных усилителей на основе мультидифференциальных операционных усилителей / С. В. Федоров // Информационные технологии в проектировании и производстве. - 2022. - № 2(186). - С. 29-35. - DOI 10.52190/2073-2597_2022_2_29. - EDN CSHKVM.], можно записать уравнение выходного напряжения мультидифференциального операционного усилителя

,

,

где

- напряжение на неинвертирующем и инвертирующем входе первого дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе первого дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе второго дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе второго дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе третьего дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе третьего дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-3 дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-3 дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-2 дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-2 дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-1 дифференциального каскада;

- напряжение на неинвертирующем и инвертирующем входе N-1 дифференциального каскада;

- коэффициенты усиления дифференциальных сигналов для каскадов 1, 2,…, N-1;

- коэффициенты усиления дифференциальных сигналов для каскадов 1, 2,…, N-1;

- синфазное входное напряжение первого дифференциального каскада;

- синфазное входное напряжение первого дифференциального каскада;

- синфазное входное напряжение второго дифференциального каскада;

- синфазное входное напряжение второго дифференциального каскада;

K СФ1 - коэффициент усиления синфазного сигнала для первого каскада;

K СФ2 - коэффициент усиления синфазного сигнала для второго каскада;

- напряжение сдвига.

- напряжение сдвига.

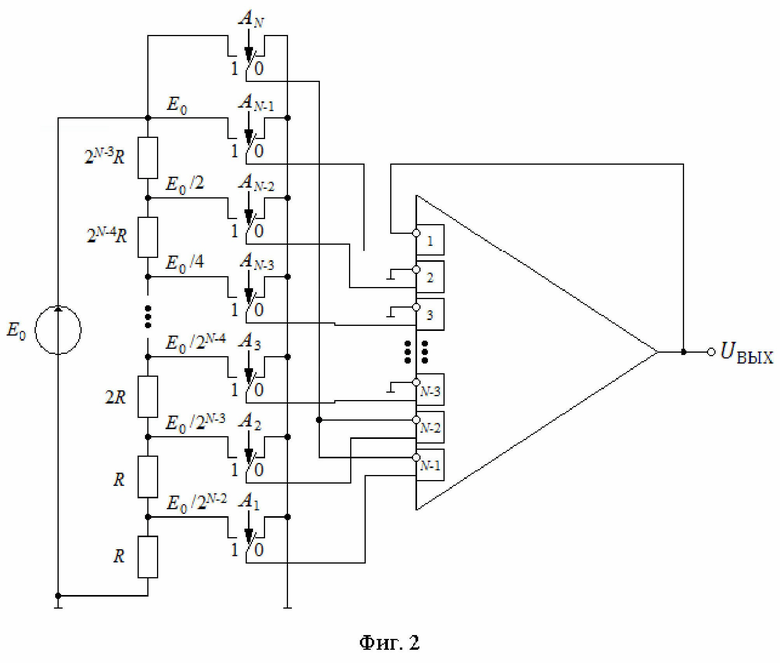

Инвертирующий вход первого дифференциального каскада мультидифференциального операционного усилителя образует единичную обратную связь с его выходом (фиг. 4).

Уравнение мультидифференциального операционного усилителя, приведенного на фиг. 4, при условии его идеальности, т.е. KД1=KД2=KД3=…=KДN-1→∞ и отсутствия синфазных сигналов, а также напряжения сдвига

.

.

Источник опорного напряжения E0 подключен к резистивному делителю напряжения, образуемому резисторами R, R, 2R, 4R, …, 2N-3R, где N - разрядность ЦАП. При этом точка подключения опорного напряжения с резистором R заземлена. Резистивный делитель предназначен для создания N-1 значения выходного напряжения E0/2N-2, E0/2N-1,…, E0/4, E0/2, E0. Выводы резистивного делителя с помощью N-1 ключей позволяют при подаче управляющего сигнала в виде логической 1 подключать выходные напряжения резистивного делителя к неинвертирующим входам мультидифференциального операционного усилителя. При поступлении управляющих сигналов в виде логического 0 на данные ключи, неинвертирующие входы мультидифференциального операционного усилителя заземляются.

Все инвертирующие входы мультидифференциального операционного усилителя кроме первого, образующего обратную связь, и входов N-2 и N-1 каскадов заземляются. Инвертирующие входы N-2 и N-1 дифференциальных каскадов объединены и подключены к входу N-ого ключа. Данный ключ при подаче управляющего сигнала в виде логической 1 подключает источник опорного напряжения E0 к данным инвертирующим входам мультидифференциального операционного усилителя. При поступлении управляющего сигнала в виде логического 0 на данный ключ инвертирующие входы мультидифференциального операционного усилителя заземляются.

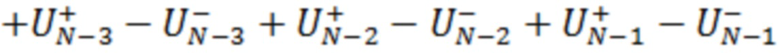

Таким образом, уравнение выходного напряжения ЦАП примет следующий вид

где ANAN-1…A1 - управляющий ключами двоичный код.

При подаче на ключ старшего управляющего разряда AN=0 на выходе ЦАП получаем N-1 разрядное положительное напряжение, имеющее следующие значения

0, E0/2N-2, 2E0/2N-2, 3E0/2N-2,…, (2N-1 -2)E0/2N-2, (2N-1 -1)E0/2N-2.

При подаче на ключ старшего управляющего разряда AN=1 на выходе ЦАП получаем N-1 разрядное отрицательное напряжение, имеющее следующие значения

-E0/2N-2, -2E0/2N-2, -3E0/2N-2,…, -(2N-1 -1)E0/2N-2, -2N-1 E0/2N-2.

В итоге на выходе ЦАП получаем N-разрядное двухполярное напряжение при одной полярности опорного напряжения.

При этом для создания N-разрядного ЦАП использовался резистивный делитель с верхним диапазоном номинала сопротивления 2N-3R. Для создания N-разрядного выходного напряжения в цифроаналоговом преобразователе-прототипе необходим резистор с верхним диапазоном номинала сопротивления 2N-1R. Т.е., использование одного и того же резистора с наибольшим сопротивлением позволяет увеличить разрядность схемы на 2 разряда.

Таким образом, достигается заявленный технический результат, заключающийся в уменьшении верхнего диапазона номиналов взвешенных резисторов, что позволит реализовать более высокоразрядный ЦАП, а также получения двухполярного напряжения на выходе устройства при одной полярности опорного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2821422C1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2713758C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2066924C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2335844C2 |

| Цифроаналоговый преобразователь | 1988 |

|

SU1543546A1 |

Изобретение относится к аналого-цифровой технике и может быть использовано в устройствах преобразования цифровых величин - кодов в пропорциональные аналоговые величины. Техническим результатом изобретения является уменьшение верхнего диапазона номиналов взвешенных резисторов для реализации более высокоразрядного цифроаналогового преобразователя (ЦАП), а также возможность инверсии выходного напряжения устройства для получения двухполярного напряжения на выходе устройства при одной полярности опорного напряжения. Цифроаналоговый преобразователь содержит N-1 поразрядно взвешенных резисторов с диапазоном сопротивлений R, R, 2R, 4R, …, 2N-3R, где N - разрядность ЦАП, N переключающих ключей, управляемых входным цифровым двоичным кодом ANAN-1…A1, где AN - старший разряд N-разрядного ЦАП и мультидифференциальный операционный усилитель с N-1 входными дифференциальными каскадами. К концам резистивного делителя подключено опорное напряжение E0, при этом подключение при наименьшем сопротивлении R заземлено. Инвертирующий вход первого дифференциального каскада мультидифференциального операционного усилителя образует единичную обратную связь с его выходом. Все неинвертирующие входы мультидифференциального операционного усилителя через ключи подключены к узлам соединенных последовательно, в виде резистивного делителя напряжения, поразрядно взвешенных резисторов. Инвертирующие входы мультидифференциального операционного усилителя со второго по N-3 дифференциальный каскад заземлены, инвертирующие входы N-2 и N-1 дифференциальных каскадов объединены и подключены к входу N-го ключа, присоединенного непосредственно к источнику опорного напряжения. Вторые выходы всех ключей подключены к общей заземленной шине. 4 ил.

Цифроаналоговый преобразователь, содержащий источник опорного напряжения, усилитель, N-1 поразрядно взвешенных резисторов, N переключающих ключей, управляемых входным цифровым двоичным кодом ANAN-1…A1, где AN - старший разряд N-разрядного цифроаналогового преобразователя, отличающийся тем, что диапазон сопротивлений поразрядно взвешенных резисторов R, R, 2R, 4R, …, 2N-3R, в качестве усилителя используется мультидифференциальный операционный усилитель с N-1 входными дифференциальными каскадами, инвертирующий вход первого дифференциального каскада мультидифференциального операционного усилителя образует единичную обратную связь с его выходом, все неинвертирующие входы мультидифференциального операционного усилителя через ключи подключены к узлам соединенных последовательно, в виде резистивного делителя напряжения, поразрядно взвешенных резисторов, инвертирующие входы мультидифференциального операционного усилителя со второго по N-3 дифференциальный каскад заземлены, инвертирующие входы N-2 и N-1 дифференциальных каскадов объединены и подключены к входу имеющегося N-го ключа, присоединенного непосредственно к источнику опорного напряжения, при этом общая точка подключения источника опорного напряжения и резистора с наименьшим сопротивлением на конце резистивного делителя напряжения заземлена, а вторые выходы всех ключей подключены к общей заземленной шине.

| WO 9817004 A1, 23.04.1998 | |||

| WO 2013177363 A1, 28.11.2013 | |||

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2568323C2 |

| КРУТЧИНСКИЙ С.Г., ТИТОВ А.Е | |||

| Структурный синтез инструментальных усилителей на базе мультидифференциальных операционных усилителей (МОУ) // Известия ЮФУ | |||

| Технические науки | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| С | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| ИНТЕГРАЛЬНЫЙ N-РАЗРЯДНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЦАП) (ВАРИАНТЫ) | 1995 |

|

RU2113055C1 |

| WO 9955006 A1, 28.10.1999 | |||

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

Авторы

Даты

2024-08-12—Публикация

2023-10-15—Подача