т.

Р .

1

00

Изобретение относится к автоматике И может быть использовано в цифро аналоговых устройствах, в которых требуется сформировать аналоговый сигнал, величина которого равна произведению двух сигналов, представленных в виде цифровых двоичных кодов.

Цель изобретения - повьппение быстродействия .

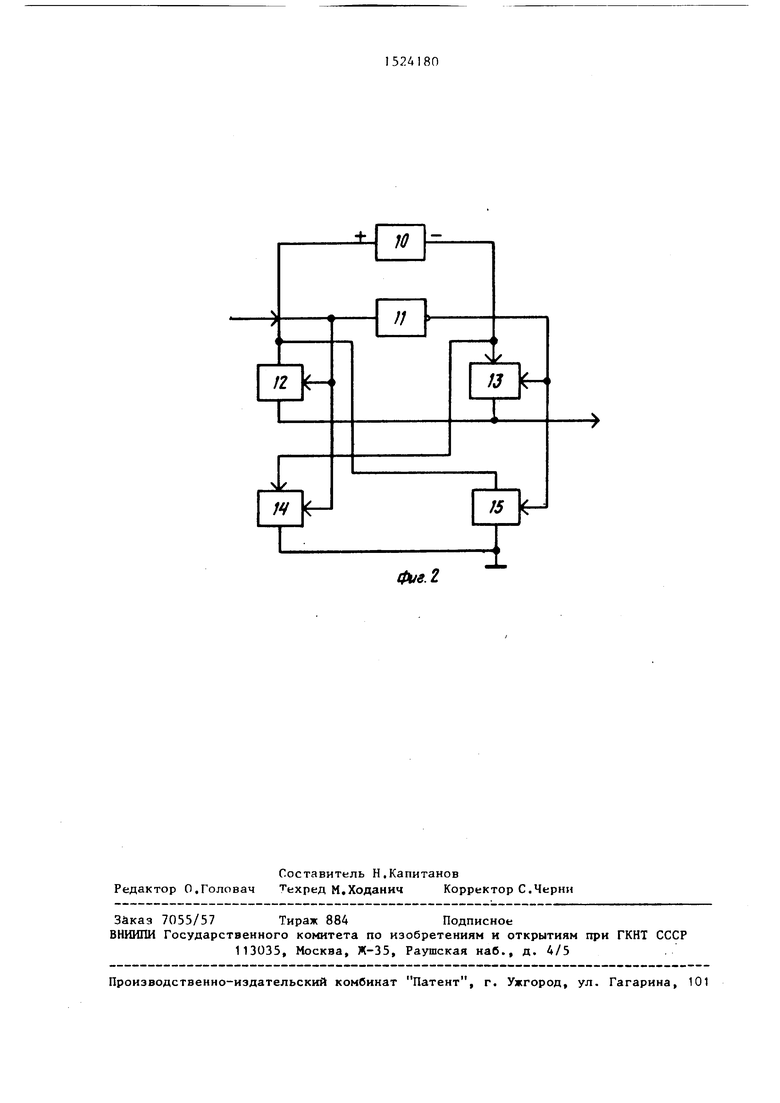

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема переключателя полярности опорного напряжения.

Устройство цифроаналогового преобразования (фиг.1) содержит га п-раз- рядных преобразователей ( - 1) код - напряжение, выполненных в виде групп из п переключателей 2,, - 2 п-разрядных резистивных матриц 3i - 3 типа R-2R и усилителей 4 - , постоянного тока, перемножитель 5 знаковых разрядов, переключатель 6 полярности опорного напряжения, группу из m Переключателей 7 - 7, га-разрядную резистивную матрицу 8 типа R-2R и выходной усилитель 9 постоянного тока. Переключатель 6 полярности опорного напряжения (фиг.2) выполнен в виде источника 10 опорного напряжения, инвертора 11 и четырех ключей 12-15.

Устройство цифроаналогового преобразования работает следующим образом.

Первый перемнож мый сигнал в виде параллельного двоичного кода разрядности п поступает на управляющие входы всех п-разрядных преобразователей 1 код - напряжение. Первый сигнал в виде параллельного двоичного кода разрядности п по параллельным шинам поступает на управляющие входы соответствующих переключателей 2 - . . На сигйальные входы этих переключателей подается опорный сигнал. Переключатели, на управляющих входах которых появляется единица кода, подключают опорное напряжение к соответствующему входу резистивной матрицы 3 , производящей операцию нормирования выходного аналогового уровня, пропорционально поступившему коду. Выходной сигнал преобразователя 1 формируется усилителем 4 постоянного тока, в качестве которого используется операционный усилитель. Поскольку каждый из цифро аналоговых преобразователей должен

работать с опорными сигналами разной полярности, то такие функции могут быть возложены только на умножающий преобразователь код - напряжение, который использует в качестве опорного не непрерывно изменяющийся сигнал, а только два его фиксированных значения .

Q Преобразователи 1 - 1 код - напряжение вырабатывают на своих выходах аналоговые напряжения, уровни которых пропорциональны коду первого сигнала. Поскольку двоичный код по5 ступает одновременно на первые цифровые входы всех преобразователей код - напряжение, а опорные напряжения, подаваемые на преобразователи, одинакового уровня (подаются от одного

0 и того же прецизионного источника 10 напряжения +R или -Е), то и выходные уровни преобразованных напряжений одинаковы. Однако преобразованные напряжения появляются на выходах

5 только тех преобразователей, на которые в данный момент поступает опорный сигнал. Управление подачей опорного сигнала достигается с помощью переключателей 7, - 7. Командой к

п включению опорного напряжения (с помощью переключателей 7 - 7) на тот или иной преобразователь код - напряжение служит появление на соответствующих вторых цифровых входах

устройства единиц кода (появление кодовых импульсов). Считается, что на цифровых входах устройства обеспечивается одновременная подача кодовых импульсов двух перемножаемых

0 сигналов.

ВьЕходные уровни преобразованных напряжений поступают на общую резистивную матрицу 8 с выходным усилителем 9 постоянного тока, на выходе

5 которого формируется аналоговое напряжение, пропорциональное коду второго сигнала. Но оно одновременно пропорционально коду первого сигнала или, иначе говоря, пропорционально произведению кодов первого и второго сигналов. Фактически это означает, что для преобразования ресового суммирования) используются такие единичные значения кодов первого и второго сигналов, которые находятся как бы на пересечении столбцов, образованных кодами первого сигнала, и строк, образованных KogaNai второго сигнала. Совпадение

0

5

515

единиц кода на пересечении соответ- ствующих столбцов и строк фиксируется появлением в данном месте опорного напряжения. Если коды первого и второго сигналов поступают одновременно, то их совпадение отвечает логике схемы И, что при наличии двух нормированных по амплитуде сигналов соответствует произведению этих сигналов. Таким образом, выходной сигнал есть результат суммирования с весами произведений двух чисел.

Преобразователи код - напряжение, используемые в предлагаемом устройстве, должны работать с опорными сигналами разной полярности в зависимости от полярности произведения двух сигналов. Полярность произведения задается перемножителем 5 знака, на входы которого подаются два знаковых разряда, принадлежащих кодам первого и второго сигналов. На выходе Перемножителя 5 по правилу булевой алгебры вырабатывается импульс единицы кода при совпадении значений кодов знаковых разрядов (нулей или единиц). При единичном (нулевом) коде на выходе перемножителя 5 с помощью Переключателя 6 полярности опорного напряжения к переключателям 7 - 1 подключается положительное (отрицательное) опорное напряжение.

При подаче в качестве управляющего сигнала с признаком 1 электронные ключи 12 и 14 замыкаются, причем ключ 12 пропускает на выход положительное опорное напряжение от источника 10. При этом ключ 14, второй вывод источника 10 опорного напряжения (-Е) замыкает на корпус. Поскольку управляющий сигнал поступает на ключи 13 и 15 через инвертор 11, то эти ключи находятся в закрытом состоянии. При появлении сигнала с признаком о (благодаря инвертированию) ключи 13 и 15 открываются, пропуская на выход отрицательное опорное напряжение, а ключи 12 и 14 при этом закрываются.

Переключатели 2 и 7 могут быть выполнены на двух электронных ключах и инверторе. На вход первого ключа поступает опорное напряжение, выход первого ключа объединен с выходом второго ключа и является первым выходом переключателя. Вход второго

06

ключа, являюпщйся вторым выходом переключателя, соединен с тиной нулевого потенциала. Управляющий сигнал поступает на управляющий вход второго ключа и вход инвертора, выход которого соединен с управляющим входом первого ключа.

Электронный аналоговый ключ рабоQ тает следующим образом.

Управляющее напряжение поступает на объединенные между собой выводы затворов обоих транзисторов, а коммутируемое - на вывод истока пер-

5 вор транзистора. При появлении коммутируемого напряжения определенной (положительной или отрицательной) полярности и при подаче управляющего напряжения переключает только тот

0 транзистор, который в данный момент Не зашунтирован открытым диодом. Шунтируется при этом транзистор, который не согласован с данной полярностью коммутируемого напряжения.

5 Реализация цифроаналогового преобразователя в виде матричной структуры позволяет повысить быстродействие преобразования цифровой информации в аналоговую.

0

Формула изоб ретения

1. Устройство цифроаналогового преобразования, содержащее первый п-разрядный преобразователь кОд - напряжение, выполненный в виде первой п-разрядной резистивной матрицы типа R - 2Р из п - 1 последовательно соединенных резисторов связи, п разрядных резисторов и согласуюQ щего резистора, усилителя постоянного тока и группы из п-разрядных переключателей, управляющие входы которых являются управляющими входами первого п-разрядного преобразос вателя код - напряжение и являются входной тиной п-разрядного кода, первый вывод i-ro разрядного резистора является входом i-ro разряда первой п-разрядной резистивной матрицы

0 типа R - 2R и соединен с первым выходом i-ro разрядного переключателя , где , 2, ...,п-1, второй вывод i-ro разрядного резистора соединен с первым выводом i-ro

, резистора связи, первый вывод п-го разрядного резистора является входом п-го разряда первой п-разрядной резистивной матрицы типа R - 2R и подключен к первому выходу п-го раз5

рядного переключателя, второй выход которого соединен с одноименными выходами остальных п - 1 разрядных переключателей и является шиной нулевого потенциала, первый вывод согласующего резистора соединен с шиной нулевого потенциала, а второй вьшод объединен с вторым выводом п-го разрядного резистора и подключен к второму выводу (п - 1)-го резистора связи, первый вывод первого резистора связи является выходом первой п-разрядной резистивной матрицы типа R - 2R и соединен с входом усилителя постоянного тока, выход которого является выходом первого п-разрядного преобразователя код - напряжение, а также группу из m разрядных переключателей, управляющие входы которых являются входной шиной т-разрядного кода, вторую т-разрядную резистивную матрицу типа R - 2R, выполненную аналогично первой, выход второй т-разрядной резистивной матрицы соединен с входом выходного усилителя постояного тока, выход которого является выходной шиной, отличающееся тем что, с целью повышения быстродействия, в него введены m - 1 п-раз- рядных преобразователей код - напряжение, переключатель полярности опорного напряжения и перемножитель знаковых разрядов, первый и второй входы которого являются входными шинами знаковых разрядов соответственно п-разрядного и ш-разрядного преобразуемых кодов, выход перемножителя знаковых разрядов через переключатель полярности опорного напряжения подключен к информационным входам переключателей группы из га- разрядных переключателей, первые выходы которых подключены к щине нулевого потенциала, второй выход j-ro разрядного переключателя группы из

т-разрядных переключателей, где j 1, 2, ..., ш, подключен к информационным входам п-разрядных переключателей группы из п-разрядных переключателей, управляющие входы первого

п-разрядного преобразователя код - напряжение объединены с соответствующими управляющими входами остальных (т - 1) п-разрядных преобразователей код - напряжение, выходы всех

п-разрядных преобразователей код - напряжение соединены с соответствующими входами второй т-разрядной резистивной матрицы типа R - 2R,

2. Устройство по п., о тличающееся тем, что переключатель полярности опорного напряжения выполнен в виде источника опорного напряжения, четырех ключей и инвертора, выход первого ключа объединен с выходом второго ключа и является выходом переключателя полярности опорного напряжения, вход инвертора объединен с управляющими входами первого и третьего ключей и

является входом переключателя полярности опорного напряжения, информационный вход первого ключа объединен с информационным входом четвертого ключа и подключен к выводу положительной полярности источника опорного напряжения, вывод отрицательной полярности которого подключен к информационным входам второго и третьего ключей, выход последнего из которьк объединен с выходом четвертого ключа и подключен к шине нулевого потенциала, выход инвертора соединен с управляющими входами второго и четвертого ключей.

Фие.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый перемножитель | 1975 |

|

SU598233A1 |

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| Стабилизированный источник тока с изменяющейся полярностью | 1984 |

|

SU1176314A1 |

| Устройство для цифроаналогового преобразования | 1986 |

|

SU1501302A1 |

| Цифро-аналоговый преобразователь | 1989 |

|

SU1644384A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2066924C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2824647C1 |

| Преобразователь двоичного кода в двухполярное напряжение | 1981 |

|

SU980274A1 |

| Биполярный цифроаналоговый преобразователь | 1985 |

|

SU1305862A1 |

Изобретение относится к автоматике и может быть использовано в цифроаналоговых устройствах, в которых требуется сформировать аналоговый сигнал, величина которого равна произведению двух сигналов, представленных в виде цифровых двоичных кодов. Цель изобретения - повышение быстродействия. Матричный умножающий цифроаналоговый преобразователь содержит M N-разрядных преобразователей 11-1M код-напряжение, выполненных в виде групп из N переключателей 211-2NM N-разрядных резистивных матриц 31-3M типа R-2R и усилителей 41-4M постоянного тока, перемножитель 5 знаковых разрядов, переключатель 6 полярности опорного напряжения, группу из M переключателей 71-7M, M-разрядную резистивную матрицу 8 типа R-2R и выходной усилитель 9 постоянного тока. Переключатель 6 полярности опорного напряжения выполнен в виде источника 10 опорного напряжения, инвертора 11 и четырех ключей 12-15. Положительный эффект достигается за счет введения перемножителя 5 знаковых разрядов и переключателя полярности опорного напряжения, а также дополнительных (N-1) M-разрядных преобразователей 1 код-напряжение. 1 з.п. ф-лы, 2 ил.

| Шило В.Л | |||

| Линейные интегральные схемы | |||

| - М.: Советское радио, 1979 | |||

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| - М.: Радио и связь, 1982, с | |||

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Фотореле для аппарата, служащего для передачи на расстояние изображений | 1920 |

|

SU224A1 |

Авторы

Даты

1989-11-23—Публикация

1987-07-15—Подача