Предлагаемое изобретение относится к области электронной техники и может быть использовано при создании устройств для контроля амплитуды и длительности сигналов от нескольких независимых источников.

Известен селектор импульсов по длительности, см., например, описанный в [1], содержащий первый и второй счетчики, генератор, выход которого соединен с синхровходом первого счетчика, дешифратор, вход селектора импульсов по длительности, элемент И, выход которого является выходом селектора импульсов по длительности, при этом выходы второго счетчика соединены с соответствующими входами дешифратора.

Недостаток этого селектора импульсов по длительности состоит в том, что он может контролировать длительность только одного импульсного сигнала. И поэтому для контроля сигналов от нескольких источников необходимо использовать соответствующее количество селекторов.

Наиболее близким техническим решением к предлагаемому является селектор импульсов по длительности [2], содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, элемент И, выход селектора импульсов по длительности, мультиплексор, постоянное запоминающее устройство, коммутатор, оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, постоянного запоминающего устройства и оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами коммутатора, с первыми входами которого соединены соответствующие выходы постоянного запоминающего устройства, входы мультиплексора являются входами селектора импульсов по длительности, выходы коммутатора соединены с соответствующими D-входам второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t3 генератора тактов и вторым входом элемента И, первый вход которого соединен с входом управления коммутатора, при этом выходы второго счетчика также соединены с соответствующими D-входами оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов.

Однако селектор импульсов по длительности позволяет проводить контроль длительности сигналов от нескольких источников, но не может быть использован для контроля превышения напряжения от каждого источника в течение упомянутой длительности.

Задача изобретения - расширение функциональных возможностей, а именно возможность одновременного контроля напряжения от нескольких источников (например, датчиков тока, стоящих в цепи нагрузок) и времени, в течение которого измеряемое напряжение превышает заданный уровень, что в свою очередь при использовании селектора импульсов по длительности в схемах защиты от перегрузки по току позволяет осуществлять защиту одновременно по двум критериям: по току и по длительности.

Эта задача достигается тем, что в селектор импульсов по длительности, содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, элемент И, выходы селектора импульсов по длительности, мультиплексор, входы которого являются входами селектора импульсов по длительности, первое запоминающее устройство, коммутатор, оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, первого запоминающего устройства и оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами коммутатора, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства, выходы коммутатора соединены с соответствующими D-входами второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t3 генератора тактов и вторым входом элемента И, первый вход которого соединен с входом управления коммутатора, при этом выходы второго счетчика соединены с соответствующими D-входами оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, дополнительно введены аналогово-цифровой преобразователь, второе запоминающее устройство, компаратор и демультиплексор, при этом выход мультиплексора соединен с входом аналогово-цифрового преобразователя, выходы которого соединены с соответствующими А-входами компаратора, В-входы которого соединены с соответствующими выходами второго запоминающего устройства, выход компаратора соединен с первым входом элемента И, выход которого соединен с входом демультиплексора, а выходы последнего являются выходами селектора импульсов по длительности, адресные входы второго запоминающего устройства и демультиплексора соединены с шиной адреса селектора импульсов по длительности, выход переноса второго счетчика соединен с третьим входом элемента И, выход tп генератора тактов соединен с входом запуска аналогово-цифрового преобразователя.

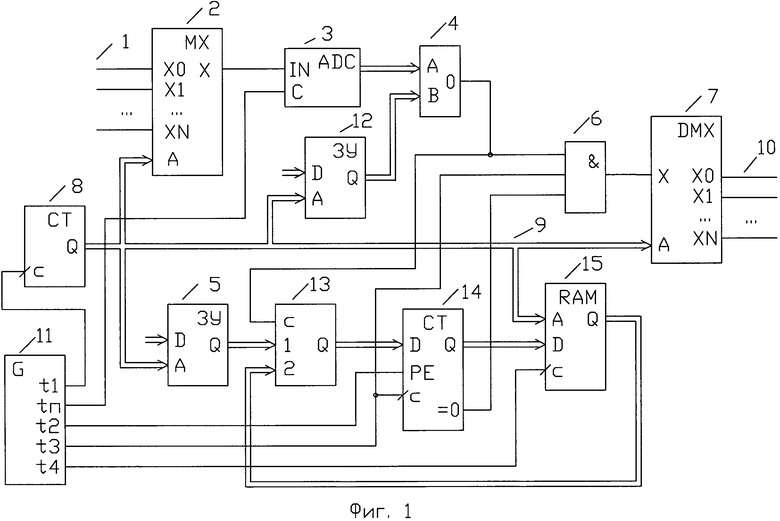

На фиг.1 приведена блок-схема селектора импульсов по длительности, где 1 - входы селектора импульсов по длительности, 2 - мультиплексор, 3 - аналогово-цифровой преобразователь, 4 - компаратор, 5 - первое запоминающее устройство, 6 - элемент И, 7 - демультиплексор, 8 - первый счетчик, 9 - шина адреса, 10 - выходы селектора импульсов по длительности, 11 - генератор тактов, 12 - второе запоминающее устройство, 13 - коммутатор, 14 - второй счетчик, 15 - оперативное запоминающее устройство.

В селекторе импульсов по длительности выход t1 генератор тактов 11 соединен с синхровходом первого счетчика 8, при этом выходы первого счетчика 8 являются шиной адреса 9 селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора 2, первого запоминающего устройства 5, второго запоминающего устройства 12, оперативного запоминающего устройства 15 и демультиплексора 7. Входы мультиплексора 2 являются входами селектора импульсов по длительности. Выходы оперативного запоминающего устройства 15 соединены с соответствующими вторыми входами коммутатора 13, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства 5, выходы коммутатора соединены с соответствующими D-входами второго счетчика 14, вход предварительной установки которого соединен с выходом t2 генератора тактов 11. Синхровход второго счетчика 14 соединен с выходом t3 генератора тактов 11 и вторым входом элемента И 6, первый вход которого соединен с входом управления коммутатора 13 и выходом компаратора 4. Выходы второго счетчика 14 соединены с соответствующими D-входами оперативного запоминающего устройства 15, синхровход которого соединен с выходом t4 генератора тактов 11. Выход мультиплексора 2 соединен с входом аналогово-цифрового преобразователя 3, выходы которого соединены с соответствующими А-входами компаратора 4, В-входы которого соединены с соответствующими выходами второго запоминающего устройства 12. Выход элемента И 6 соединен с входом демультиплексора 7, а выходы последнего являются выходами селектора импульсов по длительности. Выход переноса второго счетчика 14 соединен с третьим входом элемента И 6. Выход tп генератора тактов 11 соединен с входом запуска аналогово-цифрового преобразователя 3.

Первое запоминающее устройство 5 и второе запоминающее устройство 12 выдает на своем выходе код, соответствующий установленному на его адресном входе адресу. Коммутатор 13, при низком уровне на его входе управления, соединяет первые входы с соответствующими выходами, а при высоком уровне на его входе управления - вторые входы с соответствующими выходами. Второй счетчик 14 уменьшает свое состояние на единицу по переднему фронту импульса на синхровходе и осуществляет запись кода, установленного на D-входах, по появлению импульса на входе предварительной установки. На выходе переноса второго счетчика 14 высокий уровень появляется, когда счетчик находится в нулевом состоянии. Оперативное запоминающее устройство 15 осуществляет запись кода, установленного на D-входах, по появлению импульса на синхровходе и выдает его на своем выходе для соответствующего адреса хранения. Генератор тактов 9 формирует последовательность импульсов на своих выходах t1, tп, t2, t3 и t4. Вначале появляется импульс на выходе t1, после его окончания, через определенную задержку, появляется импульс на выходе tп, после его окончания через время, не меньшее, чем время преобразования в аналогово-цифровом преобразователе 3 на выходе t2, после его окончания - на выходе t3 и т.д., после окончания импульса на выходе t4 вновь следует импульс на выходе t1. Аналогово-цифровой преобразователь 3 по импульсу на входе запуска осуществляет преобразование входного напряжения. У компаратора 4 на выходе высокий уровень, когда число на А-входе больше, чем число на его В-входе.

Селектор импульсов по длительности работает следующим образом. По каждому такту, поступающему с выхода t1 генератора тактов 11 на синхровход первого счетчика 8 (счетчика адреса), его состояние увеличивается на единицу, в результате первый счетчик 8 последовательно устанавливает на своем выходе адреса, соответствующие источникам напряжения. Код с выхода первого счетчика 8 поступает на шину адреса 9, в результате чего мультиплексор 2 подсоединяет соответствующий вход селектора импульсов по длительности 1 к входу аналогово-цифрового преобразователя 3. По такту tп, поступающему с выхода генератора тактов 11, на аналогово-цифровой преобразователь 3, последний преобразует входное напряжение в цифровую форму (число), которое поступит на А-вход компаратора 4. В это время на В-входе компаратора 4 код, поступающий с выхода второго запоминающего устройства 12, соответствующий адресу установленному на шине адреса 9.

В случае если напряжение, подаваемое на вход селектора импульсов по длительности 1 (например, на вход n, которому соответствует адрес NN), меньше, чем пороговый уровень - число на А-входе компаратора 4 меньше, чем число на его В-входе, на выходе компаратора 4 низкий уровень. Таким образом, во втором запоминающем устройстве 12 хранится информация о пороговых уровнях по напряжению, с которыми сравниваются сигналы, поступающие на входы селектора импульсов по длительности 1. Низкий уровень с выхода компаратора 4 поступит на вход управления коммутатора 13, в результате чего выходы первого запоминающего устройства 5 будут подсоединены (через первые входы коммутатора 13) к соответствующим D-входам второго счетчика 14. Очередной такт с выхода t2 генератора тактов 11, поступив на вход предварительной установки второго счетчика 14, запишет в него соответствующий адресу NN код из первого запоминающего устройства 5. Следующий тактовый импульс с выхода t3 генератора тактов 11, поступив на синхровход второго счетчика 14, уменьшит его состояние на единицу, одновременно с этим тактовый импульс поступит на второй вход элемента И 6, однако низкий логический уровень на первом входе элемента И 3, поступающий с выхода компаратора 4, не пропустит этот тактовый импульс на вход демультиплексора 7 и соответственно на выход n селектора импульсов по длительности 10. Очередной такт с выхода t4 генератора тактов 11, поступив на синхровход оперативного запоминающего устройства 15, перепишет в него код из второго счетчика 14. Таким образом, в оперативном запоминающем устройстве 15, при низком (меньше, чем пороговый уровень) уровне напряжения на n входе селектора импульсов по длительности 1, по адресу NN будет храниться уменьшенное на единицу содержимое первого запоминающего устройства 5.

В случае появления высокого напряжения (выше, чем пороговый уровень, записанный во втором запоминающем устройстве 12) на n входе селектора импульсов по длительности 1, высокий уровень с выхода компаратора 4 (А>В) поступит на вход управления коммутатора 13, в результате чего выходы оперативного запоминающего устройства 15 будут подсоединены (через вторые входы коммутатора 13) к соответствующим D-входам второго счетчика 14. Очередной такт с выхода t2 генератора тактов 11, поступив на вход предварительной установки второго счетчика 14, запишет в него код из оперативного запоминающего устройства 15, хранящийся там по адресу NN. Следующий тактовый импульс с выхода t3 генератора тактов 11, поступив на синхровход второго счетчика 14, уменьшит его состояние на единицу, одновременно с этим тактовый импульс поступит на второй вход элемента И 6, однако низкий логический уровень на третьем входе элемента И 6, поступающий с выхода переноса второго счетчика 14, не пропустит этот тактовый импульс на вход демультиплексора 7 и соответственно на выход n селектора импульсов по длительности 10. Очередной такт с выхода t4 генератора тактов 11, поступив на синхровход оперативного запоминающего устройства 15, перепишет в него код из второго счетчика 14. Таким образом, в оперативном запоминающем устройстве 15, при наличии высокого напряжения на n входе селектора импульсов по длительности 1, хранящийся по адресу NN код будет уменьшаться на единицу в моменты следования тактовых импульсов с выхода t4 генератора тактов 11 при состоянии NN шины адреса 9.

В случае если контролируемое напряжение на n входе селектора импульсов по длительности 1 станет ниже порогового уровня до окончания допустимого (контролируемого) времени Тn, то низкое напряжение с выхода мультиплексора 2, поступив на вход аналогово-цифрового преобразователя 3, уменьшит код на А-входе компаратора 4. В результате чего низкий уровень с выхода компаратора 4 поступит на вход управления коммутатора 13, и коммутатор 13 подсоединит выходы первого запоминающего устройства 5 к соответствующим D-входам второго счетчика 14. Очередные такты с выходов t2, t3, t4 генератора тактов 11 приведут селектор импульсов по длительности в исходное состояние (в оперативном запоминающем устройстве 15 по адресу NN будет записан код на единицу меньше, чем код, хранящийся в первом запоминающем устройстве 5). А в случае если контролируемое напряжение на n входе селектора импульсов по длительности 1 не уменьшится (ниже порогового уровня) до окончания контролируемого времени Тn, то по очередному такту с выхода t3 генератора тактов 11 состояние второго счетчика 14 станет нулевым. В результате этого высокий уровень с выхода переноса второго счетчика 14 поступит на третий вход элемента И 6 и позволит такту с выхода t3 генератора тактов 11 пройти на вход демультиплексора 7 и далее на n выход селектора импульсов по длительности 10, сформировав таким образом сообщение: «на n входе селектора импульсов по длительности 1 напряжение, превышающее допустимый порог, присутствует дольше допустимого времени Тn». Код Мn, предварительно записываемый в первое запоминающее устройство 5, определяет какое количество импульсов t3 генератора тактов 11 должно быть сформировано при состоянии NN шины адреса 9 для получения интервала времени Тn. Таким образом, в первом запоминающем устройстве 5 хранится информация о пороговых уровнях по длительности с которыми сравниваются сигналы, поступающие на входы селектора импульсов по длительности 1.

Эффект от использования предлагаемого селектора импульсов по длительности в том, что он обладает расширенными функциональными возможностями, позволяет проводить контроль напряжения от нескольких источников одновременно и при этом контролировать время, в течение которого напряжение превышает заданный пороговый уровень. А прототип позволяет контролировать только длительность сигнала от нескольких источников.

В случае использования предлагаемого селектора импульсов по длительности в многоканальных коммутаторах напряжения он позволяет осуществлять защиту нескольких нагрузок (потребителей), источника и силовых элементов коммутаторов напряжения от перегрузки, анализируя сигналы с датчиков тока (в виде напряжения) в цепи каждой нагрузки.

При использовании прототипа в режиме защиты нескольких нагрузок и источника от перегрузки с одновременным контролем напряжения (с датчиков тока) и времени, в течение которого эти токи протекают через нагрузки, необходимо снабдить прототип компараторами (на каждом входе) для контроля превышения допустимого уровня напряжения, что потребует гораздо больших аппаратных затрат по сравнению с предлагаемым решением.

Предлагаемый селектор импульсов может быть легко перенастроен для изменения порогов по времени и по напряжению за счет внесения в первое 5 и второе 12 запоминающие устройства других значений.

Запоминающее устройство в прототипе позволяет проводить перенастройку по времени, но в нем отсутствует возможность изменения пороговых значений по амплитуде (по напряжению). Реализации такой возможности в отдельных компараторах напряжения для селектора прототипа приведет к усложнению и увеличению аппаратных затрат.

Это позволяет говорить об упрощении, повышении надежности и снижении стоимости электронных устройств, использующих предлагаемый селектор импульсов по длительности.

Предлагаемая совокупность признаков в рассмотренных автором решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать программируемые логические матрицы или логические элементы цифровых микросхем и микросхемы аналогово-цифровых преобразователей.

Литература

1. Патент Российской Федерации №2010422, кл. Н03K 5/26, Н03H 17/00 от 16. 12. 91. Селектор импульсов по длительности.

2. Патент Российской Федерации №2332783, кл. Н03K 5/26 от 24.07.2006. Селектор импульсов по длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2014 |

|

RU2565532C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332783C2 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство контролируемого пункта системы телемеханики | 1986 |

|

SU1374266A1 |

| Устройство пункта управления системы телемеханики | 1986 |

|

SU1374265A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332784C2 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

Изобретение относится к области электронной техники. Технический результат - возможность одновременного контроля напряжения от нескольких источников и времени, в течение которого измеряемое напряжение превышает заданный уровень, что в свою очередь, при использовании селектора импульсов по длительности в схемах защиты от перегрузки по току, позволяет осуществлять защиту одновременно по двум критериям: по току и по длительности. Для этого селектор импульсов по длительности содержит: два счетчика, генератор тактов, элемент И, мультиплексор, два запоминающих устройства, коммутатор, оперативное запоминающее устройство, шину адреса, аналогово-цифровой преобразователь, компаратор и демультиплексор, выходы которого являются выходами селектора импульсов по длительности. 1 ил.

Селектор импульсов по длительности, содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, элемент И, выходы селектора импульсов по длительности, мультиплексор, входы которого являются входами селектора импульсов по длительности, первое запоминающее устройство, коммутатор, оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, первого запоминающего устройства и оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами коммутатора, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства, выходы коммутатора соединены с соответствующими D-входами второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t3 генератора тактов и вторым входом элемента И, первый вход которого соединен с входом управления коммутатора, при этом выходы второго счетчика соединены с соответствующими D-входами оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, отличающийся тем, что в него дополнительно введены аналогово-цифровой преобразователь, второе запоминающее устройство, компаратор и демультиплексор, при этом выход мультиплексора соединен с входом аналогово-цифрового преобразователя, выходы которого соединены с соответствующими А-входами компаратора, В-входы которого соединены с соответствующими выходами второго запоминающего устройства, выход компаратора соединен с первым входом элемента И, выход которого соединен с входом демультиплексора, а выходы последнего являются выходами селектора импульсов по длительности, адресные входы второго запоминающего устройства и демультиплексора соединены с шиной адреса селектора импульсов по длительности, выход переноса второго счетчика соединен с третьим входом элемента И, выход tп генератора тактов соединен с входом запуска аналогово-цифрового преобразователя.

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332783C2 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332784C2 |

| Селектор пачки импульсов по длительности | 1978 |

|

SU790248A2 |

| US 4339723, 13.07.1982 | |||

| US 3970845, 20.07.1976 | |||

Авторы

Даты

2015-10-20—Публикация

2014-03-18—Подача