Предлагаемое изобретение относится к области электронной техники и может быть использовано при создании устройств для контроля амплитуды и длительности сигналов от нескольких независимых источников.

Известен селектор импульсов по длительности, см., например, описанный в [1], содержащий первый и второй счетчики, генератор, выход которого соединен с синхровходом первого счетчика, дешифратор, вход селектора импульсов по длительности, элемент И, выход которого является выходом селектора импульсов по длительности, при этом выходы второго счетчика соединены с соответствующими входами дешифратора.

Недостаток этого селектора импульсов по длительности состоит в том, что он может контролировать длительность только одного импульсного сигнала. И поэтому для контроля сигналов от нескольких источников необходимо использовать соответствующее количество селекторов.

Наиболее близким техническим решением к предлагаемому является селектор импульсов по длительности [2], содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, элемент И, выход селектора импульсов по длительности, мультиплексор, постоянное запоминающее устройство, коммутатор, оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, постоянного запоминающего устройства и оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами коммутатора, с первыми входами которого соединены соответствующие выходы постоянного запоминающего устройства, входы мультиплексора являются входами селектора импульсов по длительности, выходы коммутатора соединены с соответствующими D-входам второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t3 генератора тактов и вторым входом элемента И, первый вход которого соединен с входом управления коммутатора, при этом выходы второго счетчика соединены с соответствующими D-входами оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов.

Однако селектор импульсов по длительности позволяет проводить контроль длительности сигналов от нескольких источников, но не может быть использован для контроля превышения напряжения от каждого источника в течение упомянутой длительности.

Задача изобретения - расширение функциональных возможностей, а именно возможность одновременного контроля напряжения от нескольких источников (например, датчиков тока, стоящих в цепи нагрузок) и времени, в течение которого измеряемое напряжение превышает заданный уровень, при этом контролировать время, в течение которого напряжение превышает два заданных пороговых уровня (для каждого источника), что в свою очередь при использовании селектора импульсов по длительности в схемах защиты от перегрузки по току позволяет осуществлять защиту одновременно по двум критериям: по току и по длительности.

Эта задача достигается тем, что в селектор импульсов по длительности, содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, первый элемент И, выходы селектора импульсов по длительности, мультиплексор, входы которого являются входами селектора импульсов по длительности, первое запоминающее устройство, первый коммутатор, первое оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, первого запоминающего устройства и первого оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами первого коммутатора, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства, выходы первого коммутатора соединены с соответствующими D-входам второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t31 генератора тактов и вторым входом первого элемента И, первый вход которого соединен с входом управления первого коммутатора, при этом выходы второго счетчика, соединены с соответствующими D-входами первого оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, дополнительно введены аналогово-цифровой преобразователь, второе, третье и четвертое запоминающие устройства, первый и второй компараторы, второй коммутатор, третий счетчик, второе оперативное запоминающее устройство, второй элемент И, элемент ИЛИ и демультиплексор, при этом выход мультиплексора соединен с входом аналогово-цифрового преобразователя, выходы которого соединены с соответствующими А-входами первого и второго компаратора, В-входы первого компаратора соединены с соответствующими выходами второго запоминающего устройства, выход первого компаратора соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, а выход последнего соединен с входом демультиплексора, выходы демультиплексора являются выходами селектора импульсов по длительности, адресные входы второго, третьего, четвертого запоминающего устройства, второго оперативного запоминающего устройства и демультиплексора соединены с шиной адреса селектора импульсов по длительности, выход переноса второго счетчика соединен с третьим входом первого элемента И, выход tп генератора тактов соединен с входом запуска аналогово-цифрового преобразователя, выходы второго оперативного запоминающего устройства соединены с соответствующими вторыми входами второго коммутатора, с первыми входами которого соединены соответствующие выходы третьего запоминающего устройства, выходы второго коммутатора соединены с соответствующими D-входами третьего счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход третьего счетчика соединен с выходом t32 генератора тактов и вторым входом второго элемента И, первый вход которого соединен с входом управления второго коммутатора и выходом второго компаратора, при этом выходы третьего счетчика соединены с соответствующими D-входами второго оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, выход переноса третьего счетчика соединен с третьим входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, а выходы четвертого запоминающего устройства соединены с соответствующими В-входами второго компаратора.

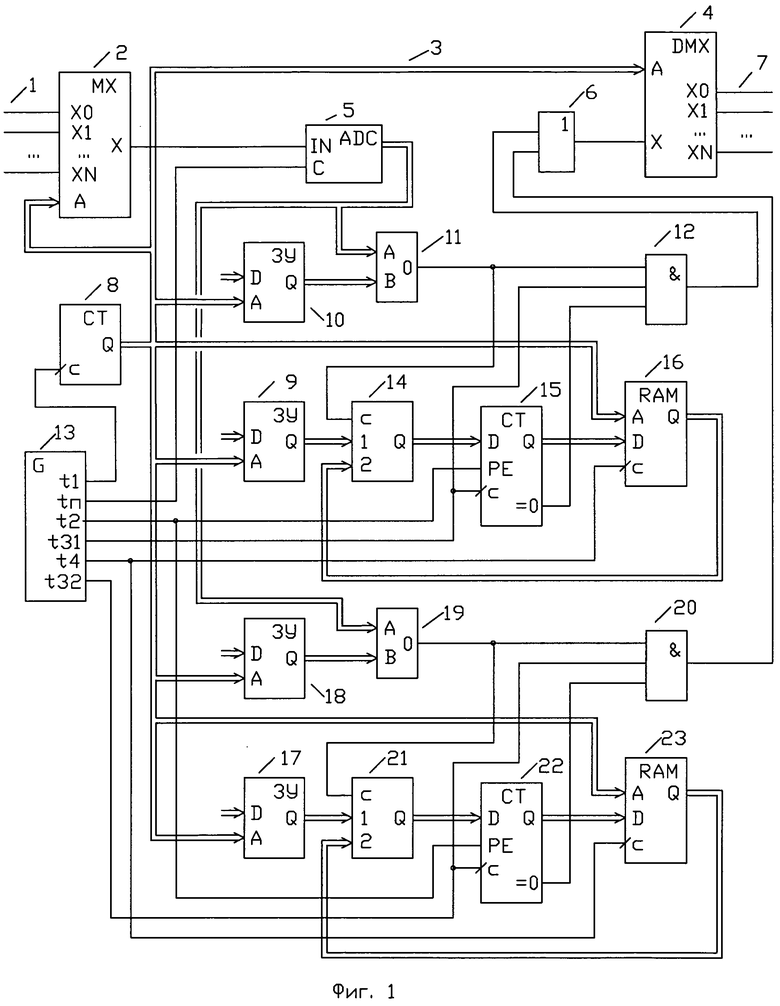

На фиг.1 приведена блок-схема селектора импульсов по длительности, где 1 - входы селектора импульсов по длительности, 2 - мультиплексор, 3 - шина адреса, 4 - демультиплексор, 5 - аналогово-цифровой преобразователь, 6 - элемент ИЛИ, 7 - выходы селектора импульсов по длительности, 8 - первый счетчик, 9 - первое запоминающее устройство, 10 - второе запоминающее устройство, 11 - первый компаратор, 12 - первый элемент И, 13 - генератор тактов, 14 - первый коммутатор, 15 - второй счетчик, 16 - первое оперативное запоминающее устройство, 17 - третье запоминающее устройство, 18 - четвертое запоминающее устройство, 19 - второй компаратор, 20 - второй элемент И, 21 - второй коммутатор, 22 - третий счетчик, 23 - второе оперативное запоминающее устройство.

В селекторе импульсов по длительности выход t1 генератор тактов 13 соединен с синхровходом первого счетчика 8, при этом выходы первого счетчика 8 являются шиной адреса 3 селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора 2, первого запоминающего устройства 9, второго запоминающего устройства 10, третьего запоминающего устройства 17, четвертого запоминающего устройства 18, первого оперативного запоминающего устройства 16, второго оперативного запоминающего устройства 23 и демультиплексора 4. Входы мультиплексора 2 являются входами селектора импульсов по длительности 1. Выходы первого оперативного запоминающего устройства 16 соединены с соответствующими вторыми входами первого коммутатора 14, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства 9, выходы первого коммутатора 14 соединены с соответствующими D-входам второго счетчика 15, вход предварительной установки которого соединен с выходом t2 генератора тактов 13. Синхровход второго счетчика 15 соединен с выходом t31 генератора тактов 13 и вторым входом первого элемента И 12, первый вход которого соединен с входом управления первого коммутатора 14 и выходом первого компаратора 11. Выходы второго счетчика 15 соединены с соответствующими D-входами первого оперативного запоминающего устройства 16, синхровход которого соединен с выходом t4 генератора тактов 13.

Выход мультиплексора 2 соединен с входом аналогово-цифрового преобразователя 5, выходы которого соединены с соответствующими А-входами первого компаратора 11 и А-входами второго компаратора 19. В-входы первого компаратора 11 соединены с соответствующими выходами второго запоминающего устройства 10. Выходы первого элемента И 12 и второго элемента И 20 соединены, соответственно, с первым и вторым входами элемента ИЛИ 6, выход которого соединен с входом демультиплексора 4, а выходы последнего являются выходами селектора импульсов по длительности 7. Выход переноса второго счетчика 15 соединен с третьим входом первого элемента И 12. Выход tп генератора тактов 13 соединен с входом запуска аналогово-цифрового преобразователя 5. Выходы второго оперативного запоминающего устройства 23 соединены с соответствующими вторыми входами второго коммутатора 21, с первыми входами которого соединены соответствующие выходы третьего запоминающего устройства 17.

Выходы второго коммутатора 21 соединены с соответствующими D-входами третьего счетчика 22, вход предварительной установки которого соединен с выходом t2 генератора тактов 13, а синхровход третьего счетчика 22 соединен с выходом t32 генератора тактов 13 и вторым входом второго элемента И 20, первый вход которого соединен с входом управления второго коммутатора 21 и выходом второго компаратора 19. Выходы третьего счетчика 22 соединены с соответствующими D-входами второго оперативного запоминающего устройства 23, синхровход которого соединен с выходом t4 генератора тактов 13. Выход переноса третьего счетчика 22 соединен с третьим входом второго элемента И 20. Выходы четвертого запоминающего устройства 18 соединены с соответствующими В-входами второго компаратора 19.

Первое 9, второе 10, третье 17 и четвертое 18 запоминающие устройства выдают на своем выходе код, соответствующий установленному на его адресном входе адресу. Первый 14 и второй 21 коммутатор, при низком уровне на его входе управления, соединяет первые входы с соответствующими выходами, а при высоком уровне на его входе управления - вторые входы с соответствующими выходами. Второй счетчик 15 и третий счетчик 22 уменьшают свое состояние на единицу по переднему фронту импульса на синхровходе и осуществляют запись кода, установленного на D-входах, по появлению импульса на входе предварительной установки. На выходе переноса второго 15 и третьего 22 счетчиков высокий уровень появляется, когда счетчики находятся в нулевом состоянии. Первое 16 и второе 23 оперативные запоминающие устройства осуществляют запись кода, установленного на D-входах, по появлению импульса на синхровходе и выдают его на своем выходе для соответствующего адреса хранения. Генератор тактов 13 формирует последовательность импульсов на своих выходах t1, tп, t2, t31, t4 и t32. Вначале появляется импульс на выходе t1, после его окончания появляется импульс на выходе tп, после его окончания, через время, не меньшее, чем время преобразования в аналогово-цифровом преобразователе 5, на выходе t2, после его окончания - на выходе t31, после его окончания импульс на выходе t4, и затем после окончания импульса на выходе t4 вновь следует импульс на выходе t1 и так далее. Импульс на выходе t32 генератора тактов 13, как и импульс на выходе t31, появляется между импульсами на выходах t2 и t4, при этом импульс с выхода t32 следует в m раз реже, чем импульс с выхода t31. Аналогово-цифровой преобразователь 5 по импульсу на входе запуска осуществляет преобразование входного напряжения. У первого 11 и второго 19 компараторов на выходе высокий уровень, когда число на А-входе больше чем число на его В-входе.

Селектор импульсов по длительности работает следующим образом. По каждому такту, поступающему с выхода t1 генератора тактов 13 на синхровход первого счетчика 8 (счетчика адреса), его состояние увеличивается на единицу, в результате первый счетчик 8 последовательно устанавливает на своем выходе адреса соответствующие источникам напряжения. Код с выхода первого счетчика 8 поступает на шину адреса 3, в результате чего мультиплексор 2 подсоединяет соответствующий вход селектора импульсов по длительности 1 к входу аналогово-цифрового преобразователя 5. По такту tп, поступающему с выхода генератора тактов 13 на аналогово-цифровой преобразователь 5, последний преобразует входное напряжение в цифровую форму (число), которое поступит на А-входы первого 11 и второго 19 компараторов. В это время на В-входе первого компаратора 11 код, поступающий с выхода второго запоминающего устройства 10, соответствует адресу, установленному на шине адреса 3.

В случае, если напряжение, подаваемое на вход селектора импульсов по длительности 1 (например, на вход n, которому соответствует адрес NN), меньше, чем пороговый уровень - число на А-входе первого компаратора 11 меньше, чем число на его В-входе, на выходе первого компаратора 11 низкий уровень. Таким образом, во втором запоминающем устройстве 10 хранится информация о пороговых уровнях по напряжению, с которыми сравниваются сигналы, поступающие на входы селектора импульсов по длительности 1. Низкий уровень с выхода первого компаратора 11 поступит на вход управления первого коммутатора 14, в результате чего выходы первого запоминающего устройства 9 будут подсоединены (через первые входы первого коммутатора 14) к соответствующим D-входам второго счетчика 15. Очередной такт с выхода t2 генератора тактов 13, поступив на вход предварительной установки второго счетчика 15, запишет в него соответствующий адресу NN код из первого запоминающего устройства 9. Следующий тактовый импульс с выхода t31 генератора тактов 13, поступив на синхровход второго счетчика 15, уменьшит его состояние на единицу, одновременно с этим тактовый импульс поступит на второй вход первого элемента И 12, однако низкий логический уровень на первом входе первого элемента И 12, поступающий с выхода первого компаратора 11, не пропустит этот тактовый импульс на первый вход элемента ИЛИ 6 и соответственно через демультиплексор 4 на n выход селектора импульсов по длительности 7. Очередной такт с выхода t4 генератора тактов 13, поступив на синхровход первого оперативного запоминающего устройства 16, перепишет в него код из второго счетчика 15. Таким образом, в первом оперативном запоминающем устройстве 16, при низком (меньше, чем пороговый уровень) уровне напряжения на n входе селектора импульсов по длительности 1, по адресу NN будет храниться уменьшенное на единицу содержимое первого запоминающего устройства 9.

В случае появления высокого напряжения (выше, чем пороговый уровень, записанный во втором запоминающем устройстве 10) на n входе селектора импульсов по длительности 1, высокий уровень с выхода первого компаратора 11 (А>В) поступит на вход управления первого коммутатора 14, в результате чего выходы первого оперативного запоминающего устройства 16 будут подсоединены (через вторые входы первого коммутатора 14) к соответствующим D-входам второго счетчика 15. Очередной такт с выхода t2 генератора тактов 13, поступив на вход предварительной установки второго счетчика 15, запишет в него код из первого оперативного запоминающего устройства 16, хранящийся там по адресу NN. Следующий тактовый импульс с выхода t31 генератора тактов 13, поступив на синхровход второго счетчика 15, уменьшит его состояние на единицу, одновременно с этим тактовый импульс поступит на второй вход первого элемента И 12, однако низкий логический уровень на третьем входе первого элемента И 12, поступающий с выхода переноса второго счетчика 15, не пропустит этот тактовый импульс через первый вход элемента ИЛИ 6 на вход демультиплексора 4 и соответственно на n выход селектора импульсов по длительности 7. Очередной такт с выхода t4 генератора тактов 13, поступив на синхровход первого оперативного запоминающего устройства 16, перепишет в него код из второго счетчика 15. Таким образом, в первом оперативном запоминающем устройстве 16, при наличии высокого напряжения на n входе селектора импульсов по длительности 1, хранящийся по адресу NN код будет уменьшаться на единицу в моменты следования тактовых импульсов с выхода t4 генератора тактов 13 при состоянии NN шины адреса 3.

В случае, если контролируемое напряжение на n входе селектора импульсов по длительности 1 станет ниже порогового уровня до окончания допустимого (контролируемого) времени Tn1, то низкое напряжение с выхода мультиплексора 2, поступив на вход аналогово-цифрового преобразователя 5, уменьшит код на А-входе первого компаратора 11. В результате чего низкий уровень с выхода первого компаратора 11 поступит на вход управления первого коммутатора 14 и первый коммутатор 14 подсоединит выходы первого запоминающего устройства 9 к соответствующим D-входам второго счетчика 15. Очередные такты с выходов t2, t31, t4 генератора тактов 13 приведут селектор импульсов по длительности в исходное состояние (в первом оперативном запоминающем устройстве 16 по адресу NN будет записан код на единицу меньше, чем код, хранящийся в первом запоминающем устройстве 9). А в случае, если контролируемое напряжение на n входе селектора импульсов по длительности 1 не уменьшится (ниже порогового уровня) до окончания контролируемого времени Tn1, то по очередному такту с выхода t31 генератора тактов 13 состояние второго счетчика 15 станет нулевым. В результате этого высокий уровень с выхода переноса второго счетчика 15 поступит на третий вход первого элемента И 12 и позволит такту с выхода t31 генератора тактов 13 пройти через первый вход элемента ИЛИ 6 на вход демультиплексора 4 и далее на n выход селектора импульсов по длительности 7, сформировав таким образом сообщение: «на n входе селектора импульсов по длительности 1 напряжение, превышающее допустимый порог, присутствует дольше допустимого времени Tn1». Код Mn1, предварительно записываемый в первое запоминающее устройство 9, определяет какое количество периодов следования импульсов с выхода t31 генератора тактов 13 при состоянии NN шины адреса 3 необходимо для получения интервала времени Tn1.

Схема, реализованная на элементах: третье 17 и четвертое 18 запоминающие устройства, второй компаратор 19, второй элемент И 20, второй коммутатор 21, третий счетчик 22 и второе оперативное запоминающее устройство 23, работает аналогично схеме, реализованной на элементах: первое 9 и второе 10 запоминающие устройства, первый компаратор 11, первый элемент И 12, первый коммутатор 14, второй счетчик 15 и первое оперативное запоминающее устройство 16 за следующим исключением - уменьшение состояния третьего счетчик 22 происходит по импульсам, поступающим с выхода t32 генератора тактов 13. Код Mn2, предварительно записываемый в третье запоминающее устройство 17, определяет какое количество периодов следования импульсов с выхода t32 генератора тактов 13 при состоянии NN шины адреса 3 необходимо для получения интервала времени Tn2. Таким образом, в первом 9 и третьем 17 запоминающих устройствах хранится информация о пороговых уровнях, по длительности с которыми сравниваются сигналы, поступающие на входы селектора импульсов по длительности 1 и имеющие напряжение больше пороговых уровней, хранящихся во втором 10 и четвертом 18 запоминающих устройствах соответственно.

Как видно, введение соотношения:

Т32=m×Т31

между периодами следования Т32, Т31 импульсов с выходов t32, t31 генератора тактов 13 позволяет уменьшить разрядность третьего запоминающего устройства 17, второго коммутатора 21, третьего счетчика 22 и второго оперативного запоминающего устройства 23. Это позволяет не увеличивать аппаратные затраты при настройках третьего запоминающего устройства 17 на большие (чем первого запоминающего устройства 9) интервалы контролируемого времени.

Эффект от использования предлагаемого селектора импульсов по длительности в том, что он обладает расширенными функциональными возможностями - позволяет проводить контроль напряжения от нескольких источников одновременно и при этом контролировать время, в течение которого напряжение превышает два заданных пороговых уровня (для каждого источника). А прототип позволяет контролировать только длительность сигнала от нескольких источников.

В случае использования предлагаемого селектора импульсов по длительности в многоканальных коммутаторах напряжения он позволяет осуществлять защиту нескольких нагрузок (потребителей), источника и силовых элементов коммутаторов напряжения от перегрузки, анализируя сигналы с датчиков тока (в виде напряжения) в цепи каждой нагрузки.

Учитывая, что параметры защиты определяются допустимой выделяемой энергией на защищаемом объекте, а энергия пропорциональна произведению квадрата тока на время действия этого тока, видно, что допустимое время действия перегрузки зависит от тока в цепи, соответственно, возникает задача быстро проводить отключение при большой перегрузке и сравнительно долго «терпеть» небольшую перегрузку. Предлагаемый селектор импульсов по длительности позволяет одновременно контролировать два режима перегрузки, так как в нем используются два компаратора (первый 11 и второй 19) и две пары запоминающих устройств (первое 9, второе 10, третье 17, четвертое 18) с двумя вариантами настроек. Например, второе 10 и первое 9 запоминающие устройства хранят информацию о допустимом пороге для пускового тока и допустимом времени, в течение которого ток через нагрузку может превышать этот порог, и предназначены для защиты от короткого замыкания в цепи нагрузки (настройка на большой ток и малое время действия тока), а другая пара (четвертое 18 и третье 17 запоминающие устройства) может содержать настройки для обеспечения защиты при длительном превышении номинального режима работы.

При использовании прототипа в режиме защиты нескольких нагрузок и источника от перегрузки с одновременным контролем напряжения (с датчиков тока) и времени, в течение которого эти токи протекают через нагрузки, необходимо снабдить прототип компараторами (на каждом входе) для контроля превышения допустимого уровня напряжения, что потребует гораздо больших аппаратных затрат по сравнению с предлагаемым решением.

Предлагаемый селектор импульсов может быть легко перенастроен для изменения порогов по времени и по напряжению за счет внесения в первое 9, второе 10, третье 17 и четвертое 18 запоминающие устройства других значений. Запоминающее устройство в прототипе позволяет проводить перенастройку по времени, но в нем отсутствует возможность изменения пороговых значений по амплитуде (по напряжению). Реализации такой возможности в отдельных компараторах напряжения для селектора прототипа приведет к усложнению и увеличению аппаратных затрат.

Это позволяет говорить об упрощении, повышении надежности и снижении стоимости электронных устройств, использующих предлагаемый селектор импульсов по длительности.

Предлагаемая совокупность признаков, в рассмотренных автором решениях, не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям “новизна” и “изобретательский уровень”. В качестве элементов для реализации устройства можно использовать программируемые логические матрицы или логические элементы цифровых микросхем и микросхемы аналогово-цифровых преобразователей.

Литература

1. Патент Российской Федерации №2010422, кл. H03K 5/26, Н03Н 7/00 от 16.12.91. Селектор импульсов по длительности.

2. Патент Российской Федерации №2332783, кл. H03K 5/26, от 24.07.2006. Селектор импульсов по длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2014 |

|

RU2565531C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332783C2 |

| Устройство пункта управления системы телемеханики | 1986 |

|

SU1374265A1 |

| Устройство контролируемого пункта системы телемеханики | 1986 |

|

SU1374266A1 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Устройство для измерения характеристик синусоидального сигнала | 1990 |

|

SU1758575A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332784C2 |

Изобретение относится к области электронной техники и может быть использовано в многоканальных источниках питания с защитой от перегрузки по току для защиты нагрузок, ключей коммутатора и источника напряжения. Техническим результатом является обеспечение защиты от перегрузок по току и по длительности сигналов. Селектор импульсов по длительности содержит первый и второй счетчики, генератор тактов, первый элемент И, выходы селектора импульсов по длительности, мультиплексор, первое запоминающее устройство, первый коммутатор, первое оперативное запоминающее устройство и шину адреса, а также дополнительно аналогово-цифровой преобразователь, второе, третье и четвертое запоминающие устройства, первый и второй компараторы, второй коммутатор, третий счетчик, второе оперативное запоминающее устройство, второй элемент И, элемент ИЛИ и демультиплексор. 1 ил.

Селектор импульсов по длительности, содержащий первый и второй счетчики, генератор тактов, выход t1 которого соединен с синхровходом первого счетчика, первый элемент И, выходы селектора импульсов по длительности, мультиплексор, входы которого являются входами селектора импульсов по длительности, первое запоминающее устройство, первый коммутатор, первое оперативное запоминающее устройство и шину адреса, при этом выходы первого счетчика являются шиной адреса селектора импульсов по длительности и соединены с соответствующими адресными входами мультиплексора, первого запоминающего устройства и первого оперативного запоминающего устройства, выходы которого соединены с соответствующими вторыми входами первого коммутатора, с первыми входами которого соединены соответствующие выходы первого запоминающего устройства, выходы первого коммутатора соединены с соответствующими D-входами второго счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход второго счетчика соединен с выходом t31 генератора тактов и вторым входом первого элемента И, первый вход которого соединен с входом управления первого коммутатора, при этом выходы второго счетчика соединены с соответствующими D-входами первого оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, отличающийся тем, что в него дополнительно введены аналогово-цифровой преобразователь, второе, третье и четвертое запоминающие устройства, первый и второй компараторы, второй коммутатор, третий счетчик, второе оперативное запоминающее устройство, второй элемент И, элемент ИЛИ и демультиплексор, при этом выход мультиплексора соединен с входом аналогово-цифрового преобразователя, выходы которого соединены с соответствующими А-входами первого и второго компаратора, В-входы первого компаратора соединены с соответствующими выходами второго запоминающего устройства, выход первого компаратора соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, а выход последнего соединен с входом демультиплексора, выходы демультиплексора являются выходами селектора импульсов по длительности, адресные входы второго, третьего, четвертого запоминающего устройства, второго оперативного запоминающего устройства и демультиплексора соединены с шиной адреса селектора импульсов по длительности, выход переноса второго счетчика соединен с третьим входом первого элемента И, выход tп генератора тактов соединен с входом запуска аналогово-цифрового преобразователя, выходы второго оперативного запоминающего устройства соединены с соответствующими вторыми входами второго коммутатора, с первыми входами которого соединены соответствующие выходы третьего запоминающего устройства, выходы второго коммутатора соединены с соответствующими D-входам третьего счетчика, вход предварительной установки которого соединен с выходом t2 генератора тактов, а синхровход третьего счетчика соединен с выходом t32 генератора тактов и вторым входом второго элемента И, первый вход которого соединен с входом управления второго коммутатора и выходом второго компаратора, при этом выходы третьего счетчика, соединены с соответствующими D-входами второго оперативного запоминающего устройства, синхровход которого соединен с выходом t4 генератора тактов, выход переноса третьего счетчика соединен с третьим входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, а выходы четвертого запоминающего устройства соединены с соответствующими В-входами второго компаратора.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| RU 2003226 C1, 15.11.1993 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

2015-10-20—Публикация

2014-03-19—Подача