10

11363467

Изобретение относится к измерительной технике, а именно к устройствам аналого-цифрового преобразования большого числа динамических аналоговых сигналов, и может быть ис- цользовано в автоматизированных системах сбора информации от большого числа датчиков аналоговых сигналов.

Цель изобретения - повьшение частоты дискретизации по каждому каналу за счет совмещения процесса одновременного преобразования текущих значений всех входных сигналов с процессом считывания цифровых эквивалентов их предьщущих значений.

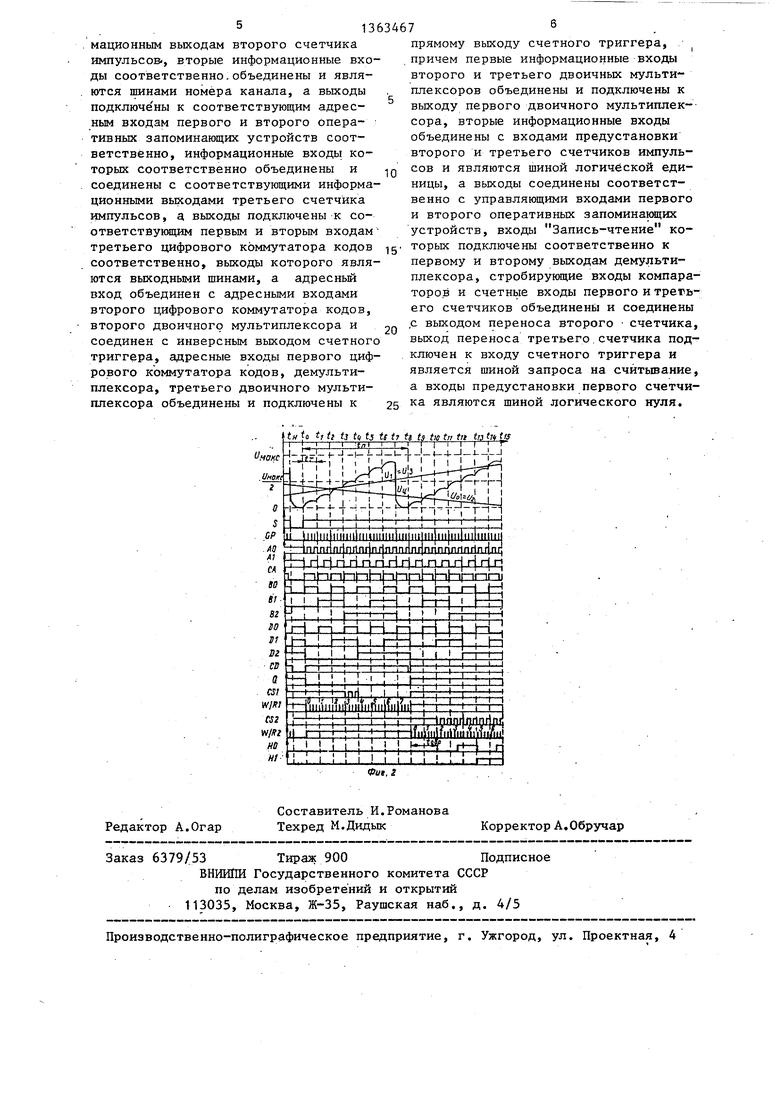

На фиг. 1 приведена функциональ ная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит группу 1 из двух аналоговых компараторов по числу каналов устройства, первый двоичный мультиплексор 2, цифроаналоговый преобразователь (ЦАП) 3, первый 4, второй 5 и третий 6 счетчики импульсов, первый 7 и второй 8 оперативные запоминающие устройства (ОЗУ), первьй 9 и второй 10 цифровые коммутаторы кодов, демультиплексор 11, третий 12 и второй 13 двоичные мультиплексоры, третий цифровой коммутатор 14 кодов, счетньш триггер 15, ключ 16 и такто- вьй генератор 17.

На фиг.2 приведены временные диаг- граммы сигналов 4-канального 3-разрядного устройства, на которых отмечены моменты t. изменения кодов на выходах счетчиков 4 и 6, где , 1, ..., момент

на первых групповых входах коммутаторов 9 и 10.

Устройство работает следующим обг- разом.

На вход счетчика 5 поступают через элемент И 16 импульсы GP генератора 17, частоты которых не превьша- ют допустимой частоты обращения к ОЗУ 7 и 8. На выходе переноса счетчика 5 при этом вырабатываются импульсы СА с частотой в 2 раз меньшей частоты генератора 17, которые дос- тупают на входы суммирования счетчи15 ков 4 и б и стробирования памяти - компараторов 1.0 -. 1.2 . По каждому из этих импульсов в памяти компараторов 1.0 - .1. запоминаются на время одного такта результаты од-

20 новременного сравнения всех входньк сигналов и - , с сигналом Пц ЦАП 3, которьй ступенчато нарастает в цикле преобразования от нуля до величины и.. ()/2 в соответстАЛЯ КС

25 ВИИ с содержимым счетчика 4, которое с запаздыванием на один такт повторяется в счетчике 6. В течение каждого такта установления следующего значения сигнала U счетчик 5 вырабатывает

30

на адресных входах мультиплексора 2 и первых информационных входах коммутаторов 9 и 10 последовательность, всех 2 двоичных номеров каналов устройства. В соответствии с вькодными og сигналами триггера 15 в одном цикле преобразования эта последовательность номеров каналов поступает на адрес- ные входы ОЗУ 7 через коммутатор 9, и одновременно с этими кодами номеначальной установки перед серией цик- 40 ров каналов на управляющий вход этого лов преобразования и показаны величи- же ОЗУ 7 поступают выходные сигналы ны t и t соответственно времени компараторов соответствующих каналов одного такта и времени одного цикла через мультиплексоры 2 и 12, каждый преобразования всех входных сигналов из которых разрешает запись в соот- и - Uj, время t обработки запроса 45 ветствующую его номеру я.чейку ОЗУ 7 на считьшание данных, -

t., прихода импульса S

п

амплитудньш

выходного кода счетчика 6 по импульсам- записи на входе Запись-чтение ОЗУ 7 До тех пор, пока сигнал Uj меньше измеряемого сигнала в данном канале, а в другом цикле преобразования состояние триггера 15 изменяется на противоположное и, соответственно, эта последовательность номеров каналов постзшает на адресные входы ОЗУ 8 через коммутатор 10, на управляющий вход этого же ОЗУ 8 поступают выходные сигналы компараторов чербз мультиплексоры 2 и 13 и на его вход Запись-чтение поступают импульсы

диапазон U

Ма КС

и выходной сигнал И

ЦАП 3, тактовые импульсы GP на выходе ключа 16, выходной код АО, А1 двухразрядного счетчика 5 и сигнал СА на его выходе переноса, выходные коды ВО, В1, В2 иОО, D1,D2 на выходах трехразрядных счетчиков 4 и 6 соответственно, сигнал CD на выходе переноса счетчика 6, сигнал Q на прямом выходе триггера 15, сигналы CS1 и CS2 на упр-авля.ющих входах и W/Rt и- W/R2 на входах Запись-чтение ОЗУ 7 и 8 соответственно и код НО, HI

на первых групповых входах коммутаторов 9 и 10.

Устройство работает следующим обг- разом.

На вход счетчика 5 поступают через элемент И 16 импульсы GP генератора 17, частоты которых не превьша- ют допустимой частоты обращения к ОЗУ 7 и 8. На выходе переноса счетчика 5 при этом вырабатываются импульсы СА с частотой в 2 раз меньшей частоты генератора 17, которые дос- тупают на входы суммирования счетчи5 ков 4 и б и стробирования памяти - компараторов 1.0 -. 1.2 . По каждому из этих импульсов в памяти компараторов 1.0 - .1. запоминаются на время одного такта результаты од-

0 новременного сравнения всех входньк сигналов и - , с сигналом Пц ЦАП 3, которьй ступенчато нарастает в цикле преобразования от нуля до величины и.. ()/2 в соответстАЛЯ КС

5 ВИИ с содержимым счетчика 4, которое с запаздыванием на один такт повторяется в счетчике 6. В течение каждого такта установления следующего значения сигнала U счетчик 5 вырабатывает

0

на адресных входах мультиплексора 2 и первых информационных входах коммутаторов 9 и 10 последовательность, всех 2 двоичных номеров каналов устройства. В соответствии с вькодными g сигналами триггера 15 в одном цикле преобразования эта последовательность номеров каналов поступает на адрес- ные входы ОЗУ 7 через коммутатор 9, и одновременно с этими кодами номеров каналов на управляющий вход этого же ОЗУ 7 поступают выходные сигналы компараторов соответствующих каналов через мультиплексоры 2 и 12, каждый из которых разрешает запись в соот- ветствующую его номеру я.чейку ОЗУ 7 -

выходного кода счетчика 6 по импульсам- записи на входе Запись-чтение ОЗУ 7 До тех пор, пока сигнал Uj меньше измеряемого сигнала в данном канале, а в другом цикле преобразования состояние триггера 15 изменяется на противоположное и, соответственно, эта последовательность номеров каналов постзшает на адресные входы ОЗУ 8 через коммутатор 10, на управляющий вход этого же ОЗУ 8 поступают выходные сигналы компараторов чербз мультиплексоры 2 и 13 и на его вход Запись-чтение поступают импульсы

записи с генератора 17 через элемент И 16 и демулЬтиплексор 11. Таким: образом, в одном цикле преобразования в режим записи устанавливается ОЗУ 7 и в нем формируются цифровые эквиваленты всех измеряемьк сигналов путем их одновременного сравнения в каждом такте с эталонным сигналом ЦАП 3, а с последовательностью кодов, поступающих на его адресные входы с входных шин номеров каналов через коммутатор 10, содержимое его ячеек поступает через коммутатор 14 на вькодные шины. По импульсу переноса счетчика 6 в конце цикла преобразования вьфа- батывается запрос на считывание массива результатов преобразования в 2 слов и изменяется, состояние триггера 15. Соответственно, режимы ОЗУ 7 и 8 .изменяются на противоположные, т.е. в другом цикле преобразования ОЗУ 7 устанавливается в режим чтения и его содержимое поступает через коммутатор 14 на выходные шины в соответствии с кодами, поступающими на его адресные входы через коммутатор 9 с шин номеров каналов, а ОЗУ 8 устанавливается в режим записи и в нем формируются цифровые эквиваленты текущих значений всех измеряемых сигналов. Это позволяет за время одного цикла преобразования сформировать цифровые эквиваленты текущих значений всех измеряемых сигналов и - Ujt. и считывать цифровые эквиваленты их предьщущих значений. Так, на фиг.2 показаны временные диаграммы, сигналов в 4-канальном 3-разрядном

устройстве при измерении входных сиг- 40 сигналов с процессом считывания

цифровых эквивалентов их предьщущих значений, в него введены второй и третий двоичные мультиплексоры, тре тий счетчик импульсов, счетный триг гер, первый и второй оперативные запоминающие устройства, первый, втор и третий цифровые коммутаторы кодов и демультиплексор, информационньй вход которого объединен со счетным входом второго счетчика импульсов и подключен к выходу ключа, управляющ вход которого объединен с входами з писи предустановки первого, второго и третьего счетчиков импульсов и яв ляется шиной начальной установки,, при этом первые информационные входы первого и второго цифровых коммутато ров кодов соответственно объединены и подключены к соответствугацим инфо

налов Ug - Uj

Перед серией циклов преобразования производится начальная установка в течение одного такта сигналом S для временной привязки последукщих результатов преобразования к моменту tjj. В первом цикле tg - t(j ОЗУ 7 установлено в режим записи и в нем формируются цифровые эквиваленты сигналов. 0,, и U, к момен с, и о

ту tj И сигналов U и U к моменту t4. S момент tg начала следующего цикла преобразования всех сигналов иJ состояние триггера 15 изменяется на противоположное и, соответственно, ОЗУ 7 устанавливается в режим чтения, а ОЗУ 8 - в режим записи. В течение этого цикла t - t в ОЗУ 8 формиру-. ются цифровые эквиваленты текущих значений измеряемых сигналов Uo - Uj,

а цифровые эквиваленты их предьщущих значений начинают считываться через время t|jf обработки запроса на прерывание ЭВМ из ячеек ОЗУ 7 через коммутатор 14 на выходные шины в .соответствии с поступающим на его адресные входы кодами НО, Ht с входов номеров каналов через коммутатор 9. Во всех последующих циклах преобразования серии измерений происходят аналогичные процессы.

Формула изобретения

0

5

0

5

Многоканальный аналого-цифровой преобразователь, содержащий 2 аналоговых компараторов по числу каналов устройства, первые информационные входы которых являются соответственно входными шинами, а вторые информационные входы объединены и подключены к выходу цифроаналогового преобразователя, входы которого соединены с соответствующими выходами первого счетчика импульсов, информационные выходы второго счетчика импульсов соединены с соответствующими адресными входами первого двоичного мультиплексора, информационные входы которого подключены к выходам соответствующих аналоговых компараторов, выход тактового генератора соединен с информационным входом ключа, отличающийся тем, что, с целью повышения частоты дискретизации по каждому каналу за счет совмещения процесса одновременного преобразования текущих значений всех вход сигналов с процессом считывания

цифровых эквивалентов их предьщущих значений, в него введены второй и третий двоичные мультиплексоры, третий счетчик импульсов, счетный триггер, первый и второй оперативные запоминающие устройства, первый, второй и третий цифровые коммутаторы кодов и демультиплексор, информационньй вход которого объединен со счетным входом второго счетчика импульсов и подключен к выходу ключа, управляющий вход которого объединен с входами записи предустановки первого, второго и третьего счетчиков импульсов и является шиной начальной установки,, при этом первые информационные входы первого и второго цифровых коммутаторов кодов соответственно объединены и подключены к соответствугацим информационным выходам второго счетчика импульсов-, вторые информационные входы соответственно.объединены и являются шинами номера канала, а выходы подключе ны к соответствующим адресным входам первого и второго оперативных запоминающих устройств соответственно, информационные входы которых соответственно объединены и соединены с соответствующими информационными выходами третьего счетчика импульсов, а выходы подключены к со- ответстйукицим первым и вторым входам третьего цифрового коммутатора кодов соответственно, выходы которого являются выходными шинами, а адресньй вход объединен с адресными входами второго цифрового коммутатора кодов.

второго двоичного мультиплексора и соединен с инверсным выходом счетного триггера, адресные входы первого цифрового коммутатора кодов, демульти- плексора, третьего двоичного мультиплексора объединены и подключены к

прямому выходу счетного триггера, причем первые информационные входы второго и третьего двоичных мультиплексоров объединены и подключены к выходу первого двоичного мультиплек-- сора, вторые информационные входы объединены с входами предустановки второго и третьего счетчиков импульсов и являются шиной логической единицы, а выходы соединены соответственно с управляющими входами первого и второго оперативных запоминакщих устройств, входы Запись-чтение которых подключены соответственно к первому и второму выходам демульти- плексора, стробирующие входы компараторов и счетные входы первого и трегь- его счетчиков объединены и соединены ,с выходом переноса второго счетчика, выход переноса третьего.счетчика подключен к входу счетного триггера и является шиной запроса на счйтьшание, а входы предустановки первого счетчика являются шиной логического нуля.

tH fa tl tl tj tl, fj tS jj tj ts tin tn tn tfj tts

At CA

во

в 82 10

at

SZ

CB

a

CS IKl CS2

/w

HB HI

r j Л-Н-П-П гЩ-Г1-П Г1г| г|

s

nhnhhnpb

I I

3ta

II Ц

гтIjr.™ .r.T,™.T ,„ ,,..|-i-jT - -

d ГШ Hj гш m

I I

I I

I I I

a

I I I I

ртрпг), .1 I г iin niiiiiiinitimiiniiliii

1 1 1 1 1 I

3ta

II Ц

тщ

T,™.T ,„ ,,

T

гш

I I I

I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

Изобретение относится к измерительной технике и может использоватьi ся в системах сбора информации - от большого числа датчиков дина.- мических аналоговых сигналов. В устройство, содержащее группу компараторов 1.0-1., первьм двоич- ньй мультиплексор 2, цифроаналоговый преобразователь 3, первый и второй счетчики 4. и 5 импульсов, элемент И 16 и тактовый генератор 17, с целью повышения частоты дискретизации по каждому каналу за счет совмещения процесса одновременного преобразования текущих значений всех входных сигналов с процессом считывания цифровых эквивалентов их предыдущих значений, введены первый и второй оперативные запоминающие устройства 7 и 8, три цифровых коммутатора 9,ТО,14 кодов, демультиплексор 11, второй и третий двоичные мультиплексоры 12 и 13, третий счетчик 6 .импульсов, счетный триггер 15. 2 ил. о- (Л со Q5 СО 4 О IPuf.t

Редактор А.Огар

Составитель И.Романова Техред М.Дидык

Заказ 6379/53 Тираж 900Подписное

ВНИИЙИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор А.Обручар

| Сенченко В.Р | |||

| и др | |||

| Многоканальный аналого-цифровой преобразователь | |||

| - Приборы и техника эксперимента, 1985, № 2, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| М.: Радио и связь, 1982, с | |||

| ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ СКОРОСТИ ТЕЧЕНИЯ ВОДЫ И ОДНОВРЕМЕННОГО ПОЛУЧЕНИЯ ПРОБ ЕЕ | 1925 |

|

SU425A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-14—Подача